Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 25MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6310-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                               | Pin Number | Pin           | Buffer                 | Description                                                                                                                                                                                                           |

|----------------------------------------|------------|---------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре                   | Description                                                                                                                                                                                                           |

|                                        |            |               |                        | PORTF is a bidirectional I/O port.                                                                                                                                                                                    |

| RF0/AN5<br>RF0<br>AN5                  | 24         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 5.                                                                                                                                                                                       |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 23         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                                                                                                                                                               |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 18         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                                                                                                                                                               |

| RF3/AN8<br>RF3<br>AN8                  | 17         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 8.                                                                                                                                                                                       |

| RF4/AN9<br>RF4<br>AN9                  | 16         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 9.                                                                                                                                                                                       |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 15         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.                                                                                                                                              |

| RF6/AN11<br>RF6<br>AN11                | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 11.                                                                                                                                                                                      |

| RF7/SS<br>RF7<br>SS                    | 13         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                                                                                                                                                               |

| ST = Schn<br>I = Input<br>P = Powe     | er         | with CN       |                        | CMOS = CMOS compatible input or output<br>s Analog = Analog input<br>O = Output<br>I <sup>2</sup> C = ST with I <sup>2</sup> C <sup>™</sup> or SMB levels<br>ration bit. CCP2MX is closed (all operating modes except |

## TABLE 1-3: PIC18F8310/8410 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for CCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for CCP2 when CCP2MX is cleared (Microcontroller mode only).

# 4.0 POWER-MANAGED MODES

PIC18F6310/6410/8310/8410 devices offer a total of seven operating modes for more efficient power management. These modes provide a variety of options for selective power conservation in applications where resources may be limited (i.e., battery-powered devices).

There are three categories of power-managed modes:

- · Sleep mode

- Idle modes

- Run modes

These categories define which portions of the device are clocked and sometimes, what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or INTOSC multiplexer); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features. One of these is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC<sup>®</sup> devices, where all device clocks are stopped.

### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires deciding if the CPU is to be clocked or not and selecting a clock source. The IDLEN bit controls CPU clocking, while the SCS<1:0> bits select a clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

## 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock, as defined by the FOSC<3:0> Configuration bits

- The secondary clock (the Timer1 oscillator)

- The internal oscillator block (for RC modes)

### 4.1.2 ENTERING POWER-MANAGED MODES

Entering power-managed Run mode, or switching from one power-managed mode to another, begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or ldle mode is being used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in Section 4.1.3 "Clock Transitions and Status Indicators" and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

|          | 101121               |              | MODLO   |             |                                                                                                           |  |  |  |  |

|----------|----------------------|--------------|---------|-------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Mada     | OSCCON<              | :7,1:0> Bits | Module  | Clocking    | Ausilable Cleak and Ossillator Source                                                                     |  |  |  |  |

| Mode     | IDLEN <sup>(1)</sup> | SCS<1:0>     | CPU     | Peripherals | Available Clock and Oscillator Source                                                                     |  |  |  |  |

| Sleep    | 0                    | N/A          | Off     | Off         | None – All clocks are disabled.                                                                           |  |  |  |  |

| PRI_RUN  | N/A                  | 00           | Clocked | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC, INTRC <sup>(2)</sup><br>This is the normal Full-Power Execution mode |  |  |  |  |

| SEC_RUN  | N/A                  | 01           | Clocked | Clocked     | Secondary – Timer1 Oscillator                                                                             |  |  |  |  |

| RC_RUN   | N/A                  | 1x           | Clocked | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                  |  |  |  |  |

| PRI_IDLE | 1                    | 00           | Off     | Clocked     | Primary – LP, XT, HS, HSPLL, RC, EC                                                                       |  |  |  |  |

| SEC_IDLE | 1                    | 01           | Off     | Clocked     | Secondary – Timer1 Oscillator                                                                             |  |  |  |  |

| RC_IDLE  | 1                    | 1x           | Off     | Clocked     | Internal Oscillator Block <sup>(2)</sup>                                                                  |  |  |  |  |

TABLE 4-1: POWER-MANAGED MODES

Note 1: IDLEN reflects its value when the SLEEP instruction is executed.

2: Includes INTOSC and INTOSC postscaler, as well as the INTRC source.

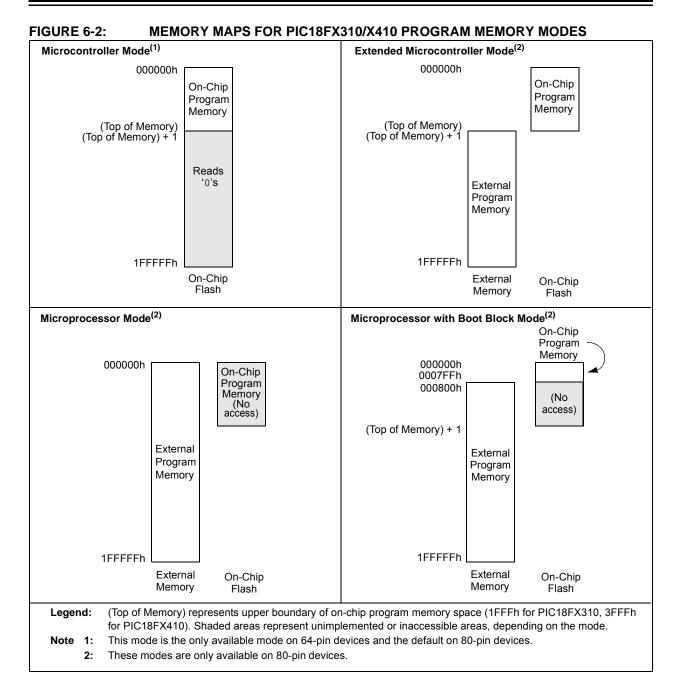

| TABLE 6-1: | MEMORY ACCESS FOR PIC18F8310/8410 PROGRAM MEMORY MODES |

|------------|--------------------------------------------------------|

|------------|--------------------------------------------------------|

| Organsting                     | Inter             | nal Program Me     | mory           | External Program Memory |                    |                   |  |  |

|--------------------------------|-------------------|--------------------|----------------|-------------------------|--------------------|-------------------|--|--|

| Operating<br>Mode              | Execution<br>From | Table Read<br>From | Table Write To | Execution<br>From       | Table Read<br>From | Table Write<br>To |  |  |

| Microcontroller                | Yes               | Yes                | Yes            | No Access               | No Access          | No Access         |  |  |

| Extended<br>Microcontroller    | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes               |  |  |

| Microprocessor                 | No Access         | No Access          | No Access      | Yes                     | Yes                | Yes               |  |  |

| Microprocessor<br>w/Boot Block | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes               |  |  |

© 2010 Microchip Technology Inc.

### 6.1.3.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 4L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

### 6.1.4 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 6-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL | SUB1, FAST  | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|------|-------------|---------------------------------------------------------|

|      | •           |                                                         |

| SUB1 | •           |                                                         |

|      | RETURN FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

### 6.1.5 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 6.1.5.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the Return Address Stack is required.

### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, | W |

|-------|-------|---------|---|

|       | CALL  | TABLE   |   |

| ORG   | nn00h |         |   |

| TABLE | ADDWF | PCL     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | RETLW | nnh     |   |

|       | •     |         |   |

|       | •     |         |   |

|       | •     |         |   |

|       |       |         |   |

### 6.1.5.2 Table Reads

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word while programming. The Table Pointer (TBLPTR) register specifies the byte address and the Table Latch (TABLAT) register contains the data that is read from the program memory. Data is transferred from program memory one byte at a time.

Table read operation is discussed further in **Section 7.1 "Table Reads and Table Writes**".

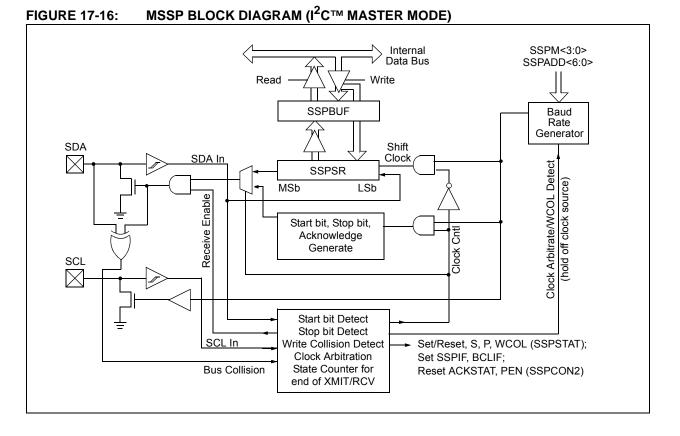

### 17.4.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON1 and by setting the SSPEN bit. In Master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set or the bus is Idle, with both the S and P bits clear.

In Firmware Controlled Master mode, user code conducts all  $I^2C$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDA and SCL.

- 2. Assert a Repeated Start condition on SDA and SCL.

- 3. Write to the SSPBUF register initiating transmission of data/address.

- 4. Configure the I<sup>2</sup>C port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDA and SCL.

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

The following events will cause MSSP Interrupt Flag bit, SSPIF, to be set (MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- Repeated Start

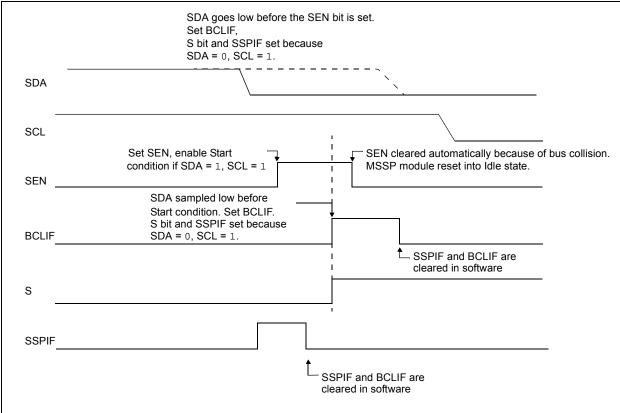

### 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to '0' and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

| R/W-0         | R-1                                              | R/W                                                                                                                         | -0    |         | R/W-0     | R/W-0                      |          | U-0         | R/W-0             | R/W-0            |  |

|---------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------|---------|-----------|----------------------------|----------|-------------|-------------------|------------------|--|

| ABDOVF        | RCIDL                                            | RXD                                                                                                                         | ΓP    | ٦       | TXCKP     | BRG16                      |          | _           | WUE               | ABDEN            |  |

| bit 7         | I                                                |                                                                                                                             |       |         |           |                            |          |             |                   | bit              |  |

| Legend:       |                                                  |                                                                                                                             |       |         |           |                            |          |             |                   |                  |  |

| R = Readable  | bit                                              | W = Wri                                                                                                                     | table | bit     |           | U = Unimp                  | lement   | ed bit. rea | ad as '0'         |                  |  |

| -n = Value at |                                                  | '1' = Bit is set                                                                                                            |       |         |           | '0' = Bit is               |          |             | x = Bit is unk    | nown             |  |

|               |                                                  |                                                                                                                             |       |         |           |                            |          |             |                   |                  |  |

| bit 7         | 1 = A BR0                                        | Auto-Baud /<br>G rollover ha<br>RG rollover h                                                                               | s oco | curre   | d during  |                            | ate De   | tect mode   | e (must be cleare | ed in software   |  |

| bit 6         | RCIDL: Re                                        | eceive Opera                                                                                                                | ation | Idle S  | Status bi | t                          |          |             |                   |                  |  |

|               |                                                  | ve operation<br>ve operation                                                                                                |       |         |           |                            |          |             |                   |                  |  |

| bit 5         | <b>RXDTP</b> : R                                 | eceived Dat                                                                                                                 | a Pol | larity  | Select b  | it                         |          |             |                   |                  |  |

|               | 1 = Receiv                                       | <u>ious mode:</u><br>/e data (RXx<br>/e data (RXx                                                                           |       |         |           |                            |          |             |                   |                  |  |

|               | <u>Synchrono</u><br>No affect.                   | ous mode:                                                                                                                   |       |         |           |                            |          |             |                   |                  |  |

| bit 4         | TXCKP: C                                         | lock and Da                                                                                                                 | ta Po | olarity | Select b  | pit                        |          |             |                   |                  |  |

|               | 1 = Idle sta                                     | Asynchronous mode:<br>. = Idle state for transmit (TXx) is a low level<br>) = Idle state for transmit (TXx) is a high level |       |         |           |                            |          |             |                   |                  |  |

|               |                                                  | ous mode:<br>ate for clock<br>ate for clock                                                                                 |       |         |           |                            |          |             |                   |                  |  |

| bit 3         | <b>BRG16:</b> 1                                  | 6-Bit Baud F                                                                                                                | ate F | Regis   | ter Enab  | ole bit                    |          |             |                   |                  |  |

|               |                                                  |                                                                                                                             |       |         |           | GH1 and SP<br>G1 only (Com |          | mode); S    | PBRGH1 value      | ignored          |  |

| bit 2         | Unimplem                                         | nented: Rea                                                                                                                 | d as  | '0'     |           |                            |          |             |                   |                  |  |

| bit 1         | WUE: Wal                                         | ke-up Enable                                                                                                                | e bit |         |           |                            |          |             |                   |                  |  |

|               | 1 = EUSA<br>hardw                                | nous mode:<br>NRT will cont<br>vare on follow<br>pin not monit                                                              | ving  | rising  | edge      | -                          | terrupt  | generated   | d on falling edge | e; bit cleared i |  |

|               | <u>Synchronous mode:</u><br>Unused in this mode. |                                                                                                                             |       |         |           |                            |          |             |                   |                  |  |

| bit 0         | ABDEN: A                                         | uto-Baud D                                                                                                                  | etect | Enat    | ole bit   |                            |          |             |                   |                  |  |

|               | 1 = Enabl<br>cleare<br>0 = Baud                  | ed in hardwa<br>rate measur                                                                                                 | re up | on co   | ompletio  | n.                         | acter. F | Requires r  | eception of a Sy  | nc field (55h    |  |

|               | <u>Synchronc</u><br>Unused in                    | <u>bus mode:</u><br>this mode.                                                                                              |       |         |           |                            |          |             |                   |                  |  |

## REGISTER 18-3: BAUDCON1: BAUD RATE CONTROL REGISTER 1

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 0, BRG            | <b>G16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |                |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |            |                             |                       |            |                             | _                     |                | _                           | _                     | _          |                             |

| 1.2         | —                     | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16           | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16           | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73           | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73           | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58          | 2                           | —                     | _          | _                           |

| 115.2       | 125.000               | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18         | 1                           | —                     | _          | _                           |

### TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODES

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD        | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |  |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3         | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |  |

| 1.2         | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |  |

| 2.4         | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | —                     | _          | _                           |  |  |  |  |

| 9.6         | 8.929                 | -6.99                         | 6                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 19.2        | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 57.6        | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2       | 62.500                | -45.75                        | 0                           | —                     | _          | —                           | _                     | —          |                             |  |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |     |                   |            |       |                   |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----|-------------------|------------|-------|-------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |     | Fosc = 20.000 MHz |            |       | Fosc = 10.000 MHz |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | Rate % value Rate             |     |                   | %<br>Error | value |                   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | —                     | _                             | _   | —                 | _          | _     | _                 | _          | _                           | _                     | _          | _                           |  |  |

| 1.2          | —                     | —                             | —   | —                 | —          | —     | —                 | —          | —                           | —                     | —          | —                           |  |  |

| 2.4          | —                     | _                             | _   | —                 | _          | _     | 2.441             | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |  |

| 9.6          | 9.766                 | 1.73                          | 255 | 9.615             | 0.16       | 129   | 9.615             | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |

| 19.2         | 19.231                | 0.16                          | 129 | 19.231            | 0.16       | 64    | 19.531            | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |

| 57.6         | 58.140                | 0.94                          | 42  | 56.818            | -1.36      | 21    | 56.818            | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |

| 115.2        | 113.636               | -1.36                         | 21  | 113.636           | -1.36      | 10    | 125.000           | 8.51       | 4                           | _                     | —          | —                           |  |  |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD<br>RATE | Foso                          | = 4.000    | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3          | _                             |            | _                           | _                     | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |  |

| 1.2          | 1.202                         | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |

| 2.4          | 2.404                         | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |

| 9.6          | 9.615                         | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |

| 19.2         | 19.231                        | 0.16       | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 57.6         | 62.500                        | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

| 115.2        | 125.000                       | 8.51       | 1                           | _                     | _          | —                           | _                     | —          | —                           |  |  |  |

### 18.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 18-6. The data is received on the RX1 pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

The RXDTP bit (BAUDCON<5>) allows the RX signal to be inverted (polarity reversed). Devices that buffer signals from RS-232 to TTL levels also perform an inversion of the signal (when RS-232 = positive, TTL = 0). Inverting the polarity of the RXx pin data by setting the RXDTP bit allows for the use of circuits that provide buffering without inverting the signal.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If the signal at the RXx pin is to be inverted, set the RXDTP bit.

- 4. If interrupts are desired, set enable bit, RCIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. Enable the reception by setting bit, CREN.

- Flag bit, RCIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCIE, was set.

- 8. Read the RCSTA register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing enable bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 18.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGH:SPBRG registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If the signal at the RXx pin is to be inverted, set the RXDTP bit. If the signal from the TXx pin is to be inverted, set the TXCKP bit.

- 4. If interrupts are required, set the RCEN bit and select the desired priority level with the RCIP bit.

- 5. Set the RX9 bit to enable 9-bit reception.

- 6. Set the ADDEN bit to enable address detect.

- 7. Enable reception by setting the CREN bit.

- The RCIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCIE and GIE bits are set.

- 9. Read the RCSTA register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 10. Read RCREG to determine if the device is being addressed.

- 11. If any error occurred, clear the CREN bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

### REGISTER 19-2: RCSTA2: AUSART2 RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                                                                             | R/W-0                                     | R/W-0                 | R/W-0             | R-0            | R-0               | R-x       |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|-------------------|----------------|-------------------|-----------|--|--|--|

| SPEN          | RX9                                                                                               | SREN                                      | CREN                  | ADDEN             | FERR           | OERR              | RX9D      |  |  |  |

| bit 7         |                                                                                                   |                                           |                       |                   |                |                   | bit       |  |  |  |

|               |                                                                                                   |                                           |                       |                   |                |                   |           |  |  |  |

| Legend:       |                                                                                                   |                                           |                       |                   |                |                   |           |  |  |  |

| R = Readabl   |                                                                                                   | W = Writable                              |                       | U = Unimpler      |                |                   |           |  |  |  |

| -n = Value at | POR                                                                                               | '1' = Bit is set                          | t                     | '0' = Bit is clea | ared           | x = Bit is unkr   | iown      |  |  |  |

| bit 7         | SPEN: Seria                                                                                       | al Port Enable bi                         | it                    |                   |                |                   |           |  |  |  |

|               |                                                                                                   | oort is enabled (o<br>oort is disabled (l |                       |                   | CKx pins as s  | serial port pins) |           |  |  |  |

| bit 6         | RX9: 9-Bit F                                                                                      | Receive Enable I                          | bit                   |                   |                |                   |           |  |  |  |

|               |                                                                                                   | 9-bit reception<br>8-bit reception        |                       |                   |                |                   |           |  |  |  |

| bit 5         | SREN: Sing                                                                                        | le Receive Enal                           | ole bit               |                   |                |                   |           |  |  |  |

|               | <u>Asynchrono</u><br>Don't care.                                                                  | <u>us mode</u> :                          |                       |                   |                |                   |           |  |  |  |

|               | <u>Synchronou</u>                                                                                 | s mode – Maste                            | er:                   |                   |                |                   |           |  |  |  |

|               |                                                                                                   | s single receive                          |                       |                   |                |                   |           |  |  |  |

|               |                                                                                                   | s single receive<br>eared after rece      |                       | ete               |                |                   |           |  |  |  |

|               |                                                                                                   | s mode – Slave                            |                       |                   |                |                   |           |  |  |  |

|               | Don't care.                                                                                       |                                           | <u>-</u>              |                   |                |                   |           |  |  |  |

| bit 4         | CREN: Con                                                                                         | tinuous Receive                           | Enable bit            |                   |                |                   |           |  |  |  |

|               | <u>Asynchrono</u>                                                                                 |                                           |                       |                   |                |                   |           |  |  |  |

|               | 1 = Enables                                                                                       |                                           |                       |                   |                |                   |           |  |  |  |

|               | 0 = Disable                                                                                       |                                           |                       |                   |                |                   |           |  |  |  |

|               | <u>Synchronou</u>                                                                                 |                                           | oivo until ona        | hla hit CREN i    | e cleared (CE  | EN overrides SF   |           |  |  |  |

|               |                                                                                                   | s continuous red                          |                       | DIE DIL, CINEN, I | s cleared (Cr  | LIN OVERINGES OF  | (LIN)     |  |  |  |

| bit 3         | ADDEN: Address Detect Enable bit                                                                  |                                           |                       |                   |                |                   |           |  |  |  |

|               | Asynchronous mode 9-Bit (RX9 = 1):                                                                |                                           |                       |                   |                |                   |           |  |  |  |

|               | 1 = Enables address detection, enables interrupt and loads the receive buffer when RSR<8> are set |                                           |                       |                   |                |                   |           |  |  |  |

|               | 0 = Disables address detection, all bytes are received and ninth bit can be used as a parity bit  |                                           |                       |                   |                |                   |           |  |  |  |

|               | Asynchrono<br>Don't care.                                                                         | us mode 9-Bit (F                          | <del>RX9 = 0)</del> : |                   |                |                   |           |  |  |  |

| bit 2         |                                                                                                   | ning Error bit                            |                       |                   |                |                   |           |  |  |  |

|               |                                                                                                   | g error (can be ι                         | pdated by rea         | ading RCREG1      | register and r | eceiving next va  | lid byte) |  |  |  |

| bit 1         |                                                                                                   | rrun Error bit                            |                       |                   |                |                   |           |  |  |  |

|               | 1 = Overru                                                                                        | n error (can be c                         | leared by clea        | aring bit, CREN)  | )              |                   |           |  |  |  |

|               |                                                                                                   | rrun error                                |                       |                   |                |                   |           |  |  |  |

| bit 0         |                                                                                                   | rrun error<br>bit of Received D           | )ata bit              |                   |                |                   |           |  |  |  |

# 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

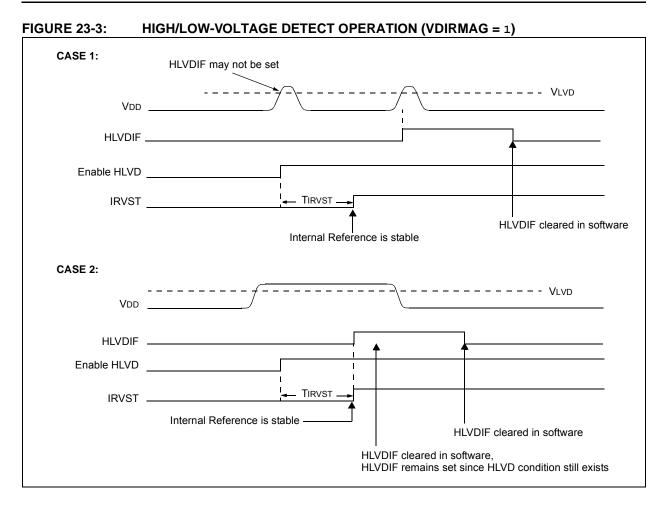

PIC18F6310/6410/8310/8410 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 23-1.

### REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0   | U-0 | R-0   | R/W-0  | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

|---------|-----|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | —   | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |     |       |        |                       |                       |                       | bit 0                 |

| Legend:      |                                                   |                                                                                                 |                                                                     |                                                                              |  |  |  |

|--------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| R = Readal   | ole bit                                           | W = Writable bit                                                                                | U = Unimplemented bit,                                              | read as '0'                                                                  |  |  |  |

| -n = Value a | at POR                                            | '1' = Bit is set                                                                                | '0' = Bit is cleared                                                | x = Bit is unknown                                                           |  |  |  |

| bit 7        | VDIRMA                                            | G: Voltage Direction Magnit                                                                     | ude Select bit                                                      |                                                                              |  |  |  |

|              | 1 = Ever                                          | nt occurs when voltage equal                                                                    | ls or exceeds trip point (HLVD)<br>s or falls below trip point (HLV |                                                                              |  |  |  |

| bit 6        | Unimple                                           | emented: Read as '0'                                                                            |                                                                     |                                                                              |  |  |  |

| bit 5        | IRVST: Internal Reference Voltage Stable Flag bit |                                                                                                 |                                                                     |                                                                              |  |  |  |

|              | 0 = Indi                                          |                                                                                                 | logic will not generate the inte                                    | flag at the specified voltage ranger<br>errupt flag at the specified voltage |  |  |  |

| bit 4        | 1 = HLV                                           | HLVDEN: High/Low-Voltage Detect Power Enable bit<br>1 = HLVD is enabled<br>0 = HLVD is disabled |                                                                     |                                                                              |  |  |  |

| bit 3-0      | HLVDL<                                            | :3:0>: Voltage Detection Limi                                                                   | it bits <sup>(1)</sup>                                              |                                                                              |  |  |  |

|              | 1110 =                                            | Maximum setting                                                                                 |                                                                     |                                                                              |  |  |  |

|              | •                                                 |                                                                                                 |                                                                     |                                                                              |  |  |  |

|              | •                                                 |                                                                                                 |                                                                     |                                                                              |  |  |  |

|              | •<br>0001 =                                       |                                                                                                 |                                                                     |                                                                              |  |  |  |

**Note 1:** HLVDL<3:0> modes that result in a trip point, below the valid operating voltage of the device, are not tested.

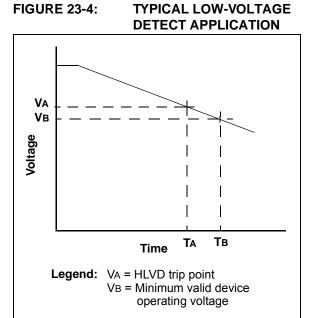

## 23.5 Applications

In many applications, the ability to detect a drop below, or rise above, a particular threshold is desirable. For example, the HLVD module could be periodically enabled to detect USB attach or detach. This assumes the device is powered by a lower voltage source than the Universal Serial Bus (USB) when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

For general battery applications, Figure 23-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### 23.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 23.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|

| HLVDCON | VDIRMAG  |           | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 64                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR2    | OSCFIF   | CMIF      | —      | _      | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 65                         |

| PIE2    | OCSFIE   | CMIE      | _      | —      | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 65                         |

| IPR2    | OSCFIP   | CMIP      | _      | _      | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 65                         |

### TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

# 25.0 INSTRUCTION SET SUMMARY

PIC18F6310/6410/8310/8410 devices incorporate the standard set of 75 PIC18 core instructions, as well as an extended set of 8 new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 25.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> device instruction sets, while maintaining an easy migration from these PIC device instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 25-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 25-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction. The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator, 'b', selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- · A program memory address (specified by 'n')

- The mode of the call or return instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 25-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 25-2, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>™</sup>).

Section 25.1.1 "Standard Instruction Set" provides a description of each instruction.

| MUL                | LW                                       | Multip                                                                                | Multiply literal with W                                                                                                                                                                                                                                                                                                                                                                  |               |      |          |                                   |  |

|--------------------|------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------|-----------------------------------|--|

| Synta              | ax:                                      | MULLW                                                                                 | V I                                                                                                                                                                                                                                                                                                                                                                                      | K             |      |          |                                   |  |

| Oper               | ands:                                    | $0 \le k \le$                                                                         | 255                                                                                                                                                                                                                                                                                                                                                                                      |               |      |          |                                   |  |

| Oper               | ation:                                   | (W) x k                                                                               | $\rightarrow$ F                                                                                                                                                                                                                                                                                                                                                                          | PRODH:        | PROE | DL       |                                   |  |

| Statu              | s Affected:                              | None                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                          |               |      |          |                                   |  |

| Enco               | oding:                                   | 0000                                                                                  | )                                                                                                                                                                                                                                                                                                                                                                                        | 1101          | kk}  | ck       | kkkk                              |  |

| Desc               | ription:                                 | out betw<br>8-bit lite<br>placed<br>PRODE<br>W is un<br>None o<br>Note th<br>possible | An unsigned multiplication is carried<br>out between the contents of W and the<br>8-bit literal 'k'. The 16-bit result is<br>placed in PRODH:PRODL register pair.<br>PRODH contains the high byte.<br>W is unchanged.<br>None of the Status flags are affected.<br>Note that neither Overflow nor Carry is<br>possible in this operation. A Zero result<br>is possible but not detected. |               |      |          |                                   |  |

| Word               | ls:                                      | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                          |               |      |          |                                   |  |

| Cycle              | es:                                      | 1                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                          |               |      |          |                                   |  |

| QC                 | ycle Activity:                           |                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |               |      |          |                                   |  |

|                    | Q1                                       | Q2                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                          | Q3            |      |          | Q4                                |  |

|                    | Decode                                   | Read<br>literal 'k'                                                                   |                                                                                                                                                                                                                                                                                                                                                                                          | Proce<br>Data |      | re<br>Pl | Write<br>gisters<br>RODH:<br>RODL |  |

| Example:           |                                          | MULLW                                                                                 | V                                                                                                                                                                                                                                                                                                                                                                                        | 0C4h          |      |          |                                   |  |

| Before Instruction |                                          | on                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                          |               |      |          |                                   |  |

|                    | W<br>PRODH<br>PRODL<br>After Instructior | =<br>=<br>=                                                                           | E2<br>?<br>?                                                                                                                                                                                                                                                                                                                                                                             | h             |      |          |                                   |  |