Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 54                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6410-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

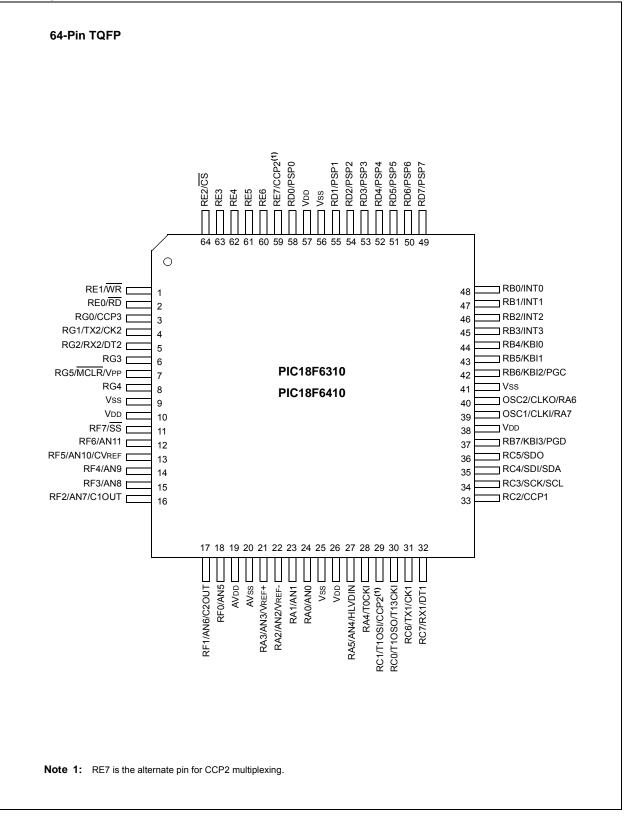

### **Pin Diagrams**

|                                                                                                                                                                                                                                           | Pin Number | Pin               | Buffer                       | Description                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                                                                                                                                                  | TQFP       | Туре              | Туре                         | Description                                                                                                                             |

|                                                                                                                                                                                                                                           |            |                   |                              | PORTC is a bidirectional I/O port.                                                                                                      |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI                                                                                                                                                                                                | 36         | I/O<br>O<br>I     | ST<br>—<br>ST                | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                        |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup>                                                                                                                                                                                     | 35         | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST             | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                               |

| RC2/CCP1<br>RC2<br>CCP1                                                                                                                                                                                                                   | 43         | I/O<br>I/O        | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.                                                                           |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                                                                                                                                                                                                          | 44         | I/O<br>I/O<br>I/O | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C mode. |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                                                                                                                                                                                                          | 45         | I/O<br>I<br>I/O   | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                              |

| RC5/SDO<br>RC5<br>SDO                                                                                                                                                                                                                     | 46         | I/O<br>O          | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                                                           |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                                                                                                                                                                                                          | 37         | I/O<br>O<br>I/O   | ST<br>—<br>ST                | Digital I/O.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related RX1/DT1).                                      |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                                                                                                                                                                                                          | 38         | I/O<br>I<br>I/O   | ST<br>ST<br>ST               | Digital I/O.<br>EUSART1 asynchronous receive.<br>EUSART1 synchronous data (see related TX1/CK1).                                        |

| Legend:TTL = TTL compatible inputCMOS= CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsAnalog = Analog inputAnalog = OutputI = InputO = Output $O$ = OutputP = Power $I^2C$ = ST with $I^2C^{TM}$ or SMB levels |            |                   |                              |                                                                                                                                         |

## TABLE 1-3: PIC18F8310/8410 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

**2:** Default assignment for CCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for CCP2 when CCP2MX is cleared (Microcontroller mode only).

| Pin Name                                                                                                                                                                                                       | Pin Number | Pin           | Buffer                 | Description                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|------------------------|--------------------------------------------------------------------------|--|

| Pin Name                                                                                                                                                                                                       | TQFP       | Туре          | Туре                   | Description                                                              |  |

|                                                                                                                                                                                                                |            |               |                        | PORTF is a bidirectional I/O port.                                       |  |

| RF0/AN5<br>RF0<br>AN5                                                                                                                                                                                          | 24         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 5.                                          |  |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT                                                                                                                                                                           | 23         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                  |  |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT                                                                                                                                                                           | 18         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                  |  |

| RF3/AN8<br>RF3<br>AN8                                                                                                                                                                                          | 17         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 8.                                          |  |

| RF4/AN9<br>RF4<br>AN9                                                                                                                                                                                          | 16         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 9.                                          |  |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF                                                                                                                                                                         | 15         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output. |  |

| RF6/AN11<br>RF6<br>AN11                                                                                                                                                                                        | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 11.                                         |  |

| RF7/SS<br>RF7<br>SS                                                                                                                                                                                            | 13         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                  |  |

| Legend:TTL = TTL compatible inputCMOS = CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsAnalog = Analog inputI = InputO = OutputP = Power $I^2C = ST$ with $I^2C^{TM}$ or SMB levels |            |               |                        |                                                                          |  |

# TABLE 1-3: PIC18F8310/8410 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for CCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for CCP2 when CCP2MX is cleared (Microcontroller mode only).

# 8.4 Operation in Power-Managed Modes

In alternate, power-managed Run modes, the external bus continues to operate normally. If a clock source with a lower speed is selected, bus operations will run at that speed. In these cases, excessive access times for the external memory may result if wait states have been enabled and added to external memory operations. If operations in a lower power Run mode are anticipated, users should provide in their applications for adjusting memory access times at the lower clock speeds.

In Sleep and Idle modes, the microcontroller core does not need to access data; bus operations are suspended. The state of the external bus is frozen with the address/data pins and most of the control pins holding at the same state they were in when the mode was invoked. The only potential changes are the CE, LB and UB pins which are held at logic high.

## TABLE 8-2: REGISTERS ASSOCIATED WITH THE EXTERNAL MEMORY INTERFACE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2   | Bit 1 | Bit 0  | Reset<br>Values<br>on Page |

|----------|-------|-------|-------|-------|-------|---------|-------|--------|----------------------------|

| MEMCON   | EBDIS |       | WAIT1 | WAIT0 |       |         | WM1   | WM0    | 65                         |

| CONFIG3L | WAIT  | BW    | —     | _     | —     | —       | PM1   | PM0    | 285                        |

| CONFIG3H | MCLRE |       | —     | _     | —     | LPT10SC | —     | CCP2MX | 286                        |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for the external memory interface.

# 11.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Output Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 11-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

#### EXAMPLE 11-3: INITIALIZING PORTC

| CLRF  | PORTC |                         |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATC  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | 0CFh  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs |

|       |       | ; RC<5:4> as outputs    |

|       |       | ; RC<7:6> as inputs     |

|       |       |                         |

## 16.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit, CCP2IE (PIE2<1>), clear to avoid false interrupts and should clear the flag bit, CCP2IF, following any such change in operating mode.

## 16.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCP2M<3:0>). Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore, the first capture may be from a non-zero prescaler. Example 16-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 16-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP2CON     | ; | Turn CCP module off |

|-------|-------------|---|---------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the  |

|       |             | ; | new prescaler mode  |

|       |             | ; | value and CCP ON    |

| MOVWF | CCP2CON     | ; | Load CCP2CON with   |

|       |             | ; | this value          |

|       |             |   |                     |

# 16.3 Compare Mode

In Compare mode, the 16-bit CCPR2 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP2 pin can be:

- driven high

- driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP2M<3:0>). At the same time, the interrupt flag bit, CCP2IF, is set.

# 16.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the RC1 or RE7 compare output latch         |

|       | (depending on device configuration) to the  |

|       | default low level. This is not the PORTC or |

|       | PORTE I/O data latch.                       |

## 16.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

## 16.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP2M<3:0> = 1010), the CCP2 pin is not affected. Only a CCP interrupt is generated if enabled and the CCP2IE bit is set.

# 16.3.4 SPECIAL EVENT TRIGGERS

CCP1 and CCP2 are both equipped with a Special Event Trigger. This is an internal hardware signal, generated in Compare mode, to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP2M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

| Note: | The Special Event Trigger of CCP1 only   |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

|       | resets Timer1/Timer3 and cannot start an |  |  |  |  |

|       | A/D conversion even when the A/D         |  |  |  |  |

|       | Converter is enabled.                    |  |  |  |  |

CCP3 is not equipped with a Special Event Trigger. Selecting the Compare Special Event Trigger mode for this device (CCP3M<3:0> = 1011) is functionally the same as selecting the Generate Software Interrupt mode (CCP3M<3:0> = 1010).

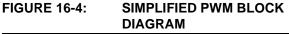

## 16.4 PWM Mode

In Pulse-Width Modulation (PWM) mode, the CCP2 pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTC or PORTE data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force<br>the RC1 or RE7 output latch (depending<br>on device configuration) to the default low<br>level. This is not the PORTC or PORTE |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | level. This is not the PORTC of PORTE                                                                                                                                      |

|       | I/O data latch.                                                                                                                                                            |

Figure 16-4 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 16.4.3** "Setup for Pwm Operation".

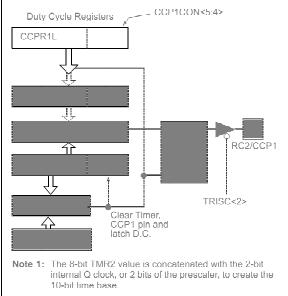

A PWM output (Figure 16-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 16-5: PWM OUTPUT

### 16.4.1 PWM PERIOD

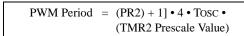

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

#### EQUATION 16-1:

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP2 pin is set (exception: if PWM duty cycle = 0%, the CCP2 pin will not be set)

- The PWM duty cycle is latched from CCPR2L into CCPR2H

# 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

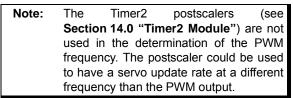

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification Parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification Parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all 7 address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 17.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL flag is clear after each write to SSPBUF to ensure the transfer is correct.

#### 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

## 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

### 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

### 17.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

#### 17.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

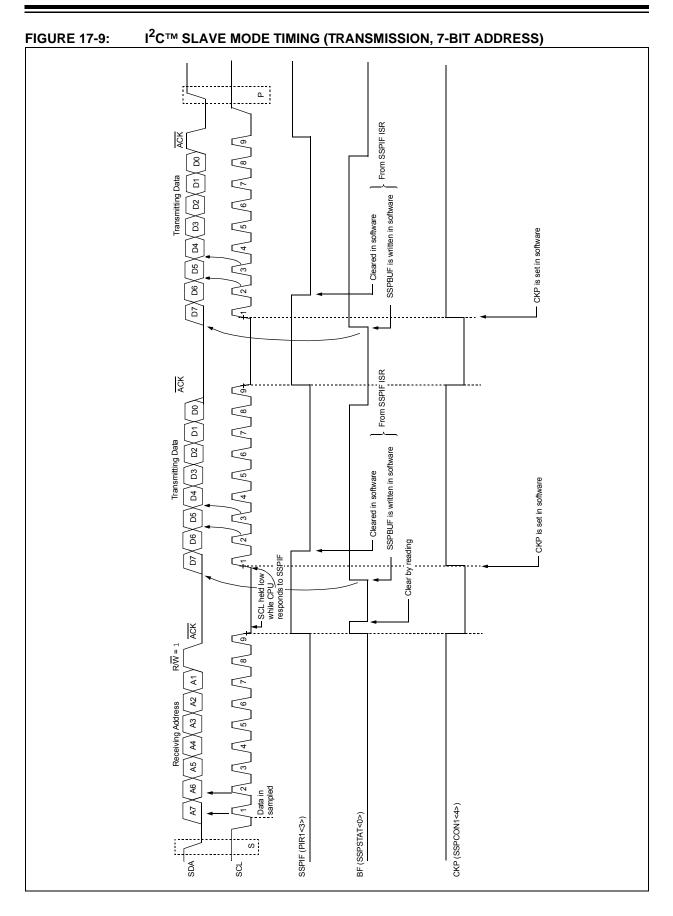

#### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

#### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

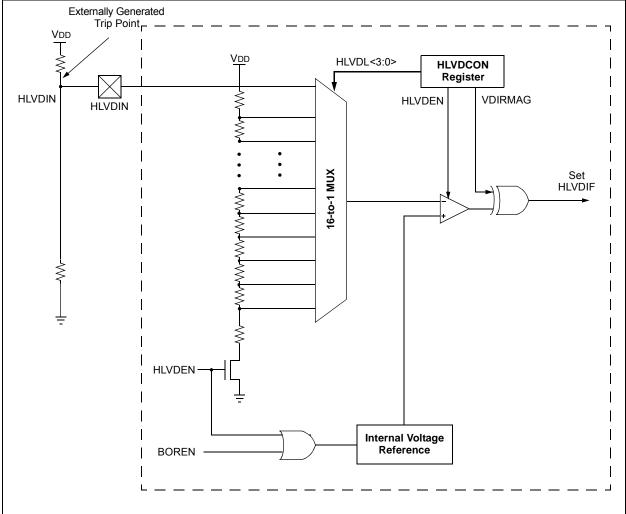

The module is enabled by setting the HLVDEN bit. Each time that the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit and is used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

# 23.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

# REGISTER 24-8: CONFIG7L: CONFIGURATION REGISTER 7 LOW (BYTE ADDRESS 30000Ch)<sup>(1)</sup>

| U-0                                        | U-0 | U-0 | U-0         | U-0                                | U-0        | U-0 | R/C-1                 |

|--------------------------------------------|-----|-----|-------------|------------------------------------|------------|-----|-----------------------|

| —                                          |     | —   | —           | —                                  | —          | _   | EBTR <sup>(2,3)</sup> |

| bit 7                                      |     |     |             |                                    |            |     | bit 0                 |

|                                            |     |     |             |                                    |            |     |                       |

| Legend:                                    |     |     |             |                                    |            |     |                       |

| R = Readable bit C = Clearable bit         |     |     |             | U = Unimplemented bit, read as '0' |            |     |                       |

| -n = Value when device is unprogrammed bit |     |     | u = Unchang | ed from progran                    | nmed state |     |                       |

bit 7-1 Unimplemented: Read as '0

bit 0 **EBTR:** Table Read Protection bit<sup>(2,3)</sup>

- 1= Internal program memory block is not protected from table reads executed from external memory block

- 0= Internal program memory block is protected from table reads executed from external memory block

- Note 1: Unimplemented on PIC18F6310/6410 devices; maintain the bit set.

2: Valid for the entire internal program memory block in Extended Microcontroller mode and for only the boot block (0000h to 07FFh) in Microcontroller with Boot Block mode. This bit has no effect in Microcontroller and Microprocessor modes.

**3:** It is recommended to enable the CP bit to protect the block from external read operations.

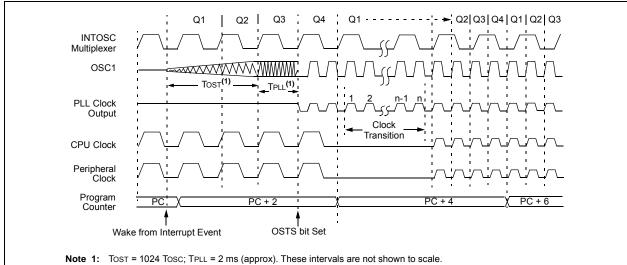

# 24.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-Based modes). Other sources do not require a OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode. In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

## 24.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.2 "Entering Power-Managed Modes"**). In practice, this means that user code can change the SCS<1:0> bits setting or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

## FIGURE 24-2: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

# 24.6 ID Locations

Eight memory locations (20000h-200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are readable during normal execution through the TBLRD instruction. During program/verify, these locations are readable and writable. The ID locations can be read when the device is code-protected.

# 24.7 In-Circuit Serial Programming

PIC18F6310/6410/8310/8410 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 24.8 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use. Table 24-4 shows which resources are required by the background debugger.

| TABLE 24-4: | DEBUGGER RESOURCES |

|-------------|--------------------|

|-------------|--------------------|

| I/O Pins:       | RB6, RB7  |

|-----------------|-----------|

| Stack:          | 2 levels  |

| Program Memory: | <1 Kbyte  |

| Data Memory:    | <16 bytes |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to  $\overline{\text{MCLR}}/\text{VPP}$ , VDD, VSS, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

## TABLE 25-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| a               | RAM access bit                                                                                                                              |  |  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                 |  |  |  |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                |  |  |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                         |  |  |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                  |  |  |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                              |  |  |  |  |  |  |  |

| d               | Destination select bit                                                                                                                      |  |  |  |  |  |  |  |

|                 | d = 0: store result in WREG<br>d = 1: store result in file register f.                                                                      |  |  |  |  |  |  |  |

| dogt            | Destination: either the WREG register or the specified register file location.                                                              |  |  |  |  |  |  |  |

| dest<br>f       | 8-bit register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                               |  |  |  |  |  |  |  |

|                 | 12-bit register file address (000h to FFFh). This is the source address.                                                                    |  |  |  |  |  |  |  |

| fs              | 12-bit register file address (000h to FFFh). This is the destination address.                                                               |  |  |  |  |  |  |  |

| f <sub>d</sub>  | Global interrupt enable bit.                                                                                                                |  |  |  |  |  |  |  |

| GIE             |                                                                                                                                             |  |  |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                   |  |  |  |  |  |  |  |

| label           |                                                                                                                                             |  |  |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions: |  |  |  |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes).                                                                         |  |  |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes).                                                                       |  |  |  |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes).                                                                       |  |  |  |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes).                                                                        |  |  |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for                                    |  |  |  |  |  |  |  |

| 11              | call/branch and return instructions.                                                                                                        |  |  |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                            |  |  |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                   |  |  |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                  |  |  |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                            |  |  |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                           |  |  |  |  |  |  |  |

| PD              | Power-Down bit.                                                                                                                             |  |  |  |  |  |  |  |

| PRODH           | Product of Multiply high byte.                                                                                                              |  |  |  |  |  |  |  |

| PRODL           | Product of Multiply low byte.                                                                                                               |  |  |  |  |  |  |  |

| s               | Fast Call/Return mode select bit                                                                                                            |  |  |  |  |  |  |  |

| -               | s = 0: do not update into/from shadow registers                                                                                             |  |  |  |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                      |  |  |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a program memory location).                                                                                 |  |  |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                          |  |  |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                               |  |  |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                               |  |  |  |  |  |  |  |

| u               | Unused or Unchanged.                                                                                                                        |  |  |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                             |  |  |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                             |  |  |  |  |  |  |  |

| x               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for                              |  |  |  |  |  |  |  |

|                 | compatibility with all Microchip software tools.                                                                                            |  |  |  |  |  |  |  |

| zs              | 7-bit offset value for indirect addressing of register files (source).                                                                      |  |  |  |  |  |  |  |

| zd              | 7-bit offset value for indirect addressing of register files (destination).                                                                 |  |  |  |  |  |  |  |

| { }             | Optional argument.                                                                                                                          |  |  |  |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                               |  |  |  |  |  |  |  |

| (text)          | The contents of text.                                                                                                                       |  |  |  |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                              |  |  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                |  |  |  |  |  |  |  |

| < >             | Register bit field.                                                                                                                         |  |  |  |  |  |  |  |

| E               | In the set of.                                                                                                                              |  |  |  |  |  |  |  |

| italics         | User-defined term (font is Courier New).                                                                                                    |  |  |  |  |  |  |  |

| BTFSC                             |                                                                           | Bit Test File, Skip if Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |                 |                                   | SS                                                                            | Bit Test File, Skip if Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                            |                 |

|-----------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|

| Synta                             | ax:                                                                       | BTFSC f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | Synta           | ax:                               | BTFSS f, b {                                                                  | ,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 |

| Operands:                         |                                                                           | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                 | Oper                              | ands:                                                                         | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 |

|                                   |                                                                           | $0 \le b \le 7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                 |                                   |                                                                               | $0 \le b < 7$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            |                 |

| Operation:                        |                                                                           | a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                 | Onor                              | otion                                                                         | $a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - 1                                        |                 |

| •                                 |                                                                           | skip if (f <b>)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | = 0             |                 | •                                 | ation:                                                                        | skip if (f <b>)</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | = 1                                        |                 |

|                                   | s Affected:                                                               | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bbba ff         |                 |                                   | s Affected:                                                                   | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                            |                 |

| Enco                              | 0                                                                         | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ff ffff         | Enco            | •                                 | 1010 bbba ffff ffff                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |                 |

| Description:<br>Words:<br>Cycles: |                                                                           | If bit 'b' in register 'f' is '0', then the next<br>instruction is skipped. If bit 'b' is '0', then<br>the next instruction fetched during the<br>current instruction execution is discarded<br>and a NOP is executed instead, making<br>this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected. If<br>'a' is '1', the BSR is used to select the<br>GPR bank .<br>If 'a' is '0' and the extended instruction set<br>is enabled, this instruction operates in<br>Indexed Literal Offset Addressing mode<br>whenever $f \le 95$ (5Fh). See<br><b>Section 25.2.3</b> for details.<br>1<br>1(2) |                 |                 | Description:<br>Words:<br>Cycles: |                                                                               | If bit 'b' in register 'f' is '1', then the next<br>instruction is skipped. If bit 'b' is '1', then<br>the next instruction fetched during the<br>current instruction execution is discarded<br>and a NOP is executed instead, making<br>this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected. If<br>'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates in<br>Indexed Literal Offset Addressing mode<br>whenever $f \le 95$ (5Fh). See<br><b>Section 25.2.3</b> for details.<br>1<br>1(2) |                                            |                 |

| ,                                 |                                                                           | Note: 3 cycles if skip and followed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                 | ,                                 |                                                                               | Note: 3 cycles if skip and followed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                            |                 |

|                                   |                                                                           | by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                 | by a 2-word instruction.          |                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |                 |

| QC                                | ycle Activity:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | _               | QC                                | ycle Activity:                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |                 |

|                                   | Q1                                                                        | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3              | Q4              |                                   | Q1                                                                            | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q3                                         | Q4              |

|                                   | Decode                                                                    | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Process<br>Data | No<br>operation |                                   | Decode                                                                        | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Process<br>Data                            | No<br>operation |

| lf sk                             | ip:                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |                 | lf sk                             | ip:                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                            |                 |

|                                   | Q1                                                                        | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Q3              | Q4              |                                   | Q1                                                                            | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q3                                         | Q4              |

|                                   | No                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | No              | No              |                                   | No                                                                            | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | No                                         | No              |