Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

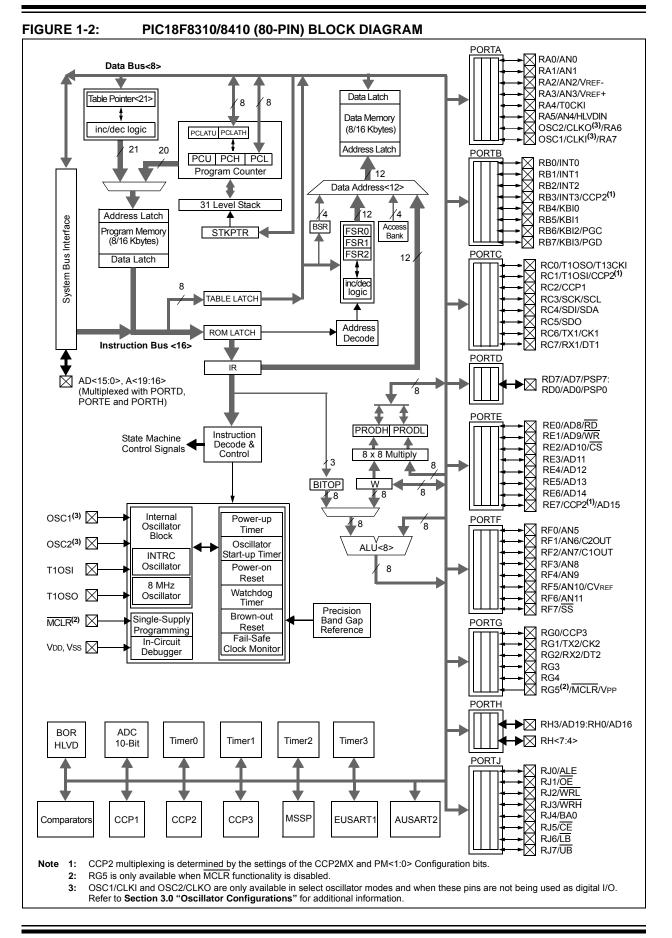

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6410t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Dia Mana                               | Pin Number | Pin           | Buffer                  | Description                                                            |

|----------------------------------------|------------|---------------|-------------------------|------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре                    | Description                                                            |

|                                        |            |               |                         | PORTA is a bidirectional I/O port.                                     |

| RA0/AN0<br>RA0<br>AN0                  | 24         | I/O<br>I      | TTL<br>Analog           | Digital I/O.<br>Analog Input 0.                                        |

| RA1/AN1<br>RA1<br>AN1                  | 23         | I/O<br>I      | TTL<br>Analog           | Digital I/O.<br>Analog Input 1.                                        |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-   | 22         | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.  |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+   | 21         | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input. |

| RA4/T0CKI<br>RA4<br>T0CKI              | 28         | I/O<br>I      | ST<br>ST                | Digital I/O.<br>Timer0 external clock input.                           |

| RA5/AN4/HLVDIN<br>RA5<br>AN4<br>HLVDIN | 27         | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 4.<br>High/Low-Voltage Detect input.      |

| RA6                                    |            |               |                         | See the OSC2/CLKO/RA6 pin.                                             |

| RA7                                    |            |               |                         | See the OSC1/CLKI/RA7 pin.                                             |

| TABLE 1-2: | PIC18F6310/6410 PINOUT I/O DESCRIPTIONS ( | (CONTINUED) | , |

|------------|-------------------------------------------|-------------|---|

|            |                                           |             |   |

P = Power  $l^2C$  = ST with  $l^2C^{TM}$  or SMB levels **Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

### 3.8 Effects of Power-Managed Modes on the Various Clock Sources

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 24.2 "Watchdog Timer (WDT)" through Section 24.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device, or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a real-time clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, PSP, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 27.2 "DC Characteristics: Power-Down and Supply Current".

### 3.9 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 5.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (Parameter 33, Table 27-12). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval, TCSD (Parameter 38, Table 27-12), following POR while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1      | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RCIO, INTIO2    | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| ECIO            | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS   | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

### TABLE 3-3:OSC1 AND OSC2 PIN STATES IN SLEEP MODE<sup>(1)</sup>

Note 1: See Table 5-2 in Section 5.0 "Reset" for time-outs due to Sleep and MCLR Reset.

### 8.0 EXTERNAL MEMORY INTERFACE

| Note: | The ext | ernal  | memo    | ry | interface | is | not |

|-------|---------|--------|---------|----|-----------|----|-----|

|       | impleme | nted   | on      | ΡI | C18F6310  |    | and |

|       | PIC18F6 | 6410 ( | 64-pin) | de | vices.    |    |     |

The external memory interface allows the device to access external memory devices (such as Flash, EPROM, SRAM, etc.) as program or data memory. It is implemented with 28 pins, multiplexed across four I/O ports. Three ports (PORTD, PORTE and PORTH) are multiplexed with the address/data bus for a total of 20 available lines, while PORTJ is multiplexed with the bus control signals. A list of the pins and their functions is provided in Table 8-1.

As implemented here, the interface is similar to that introduced on PIC18F8X20 microcontrollers. The most notable difference is that the interface on PIC18F8310/8410 devices supports both 16-Bit and Multiplexed 8-Bit Data Width modes; it does not support the 8-Bit Demultiplexed mode. The Bus Width mode is set by the BW Configuration bit when the device is programmed and cannot be changed in software.

The operation of the interface is controlled by the MEMCON register (Register 8-1). Clearing the EBDIS bit (MEMCON<7>) enables the interface and disables the I/O functions of the ports, as well as any other multiplexed functions. Setting the bit disables the interface and enables the ports.

For a more complete discussion of the operating modes that use the external memory interface, refer to Section 8.1 "Program Memory Modes and the External Memory Interface".

### REGISTER 8-1: MEMCON: MEMORY CONTROL REGISTER

| R/W-0 | R/W-0 | U-0 | U-0 | R/W-0 | R/W-0 | U-0 | R/W-0 |

|-------|-------|-----|-----|-------|-------|-----|-------|

| WM0   | WM1   | _   | _   | WAIT0 | WAIT1 | _   | EBDIS |

| bit 0 |       |     |     |       |       |     | bit 7 |

|       |       |     |     |       |       |     | bit 7 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | EBDIS: External Bus Disable bit                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = External system bus disabled, all external bus drivers are mapped as I/O ports</li> <li>0 = External system bus enabled, I/O ports are disabled</li> </ul> |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                              |

| bit 5-4 | WAIT<1:0>: Table Reads and Writes Bus Cycle Wait Count bits                                                                                                             |

|         | 11 = Table reads and writes will wait 0 TCY                                                                                                                             |

|         | 10 = Table reads and writes will wait 1 Tcy                                                                                                                             |

|         | 01 = Table reads and writes will wait 2 Tcy                                                                                                                             |

|         | 00 = Table reads and writes will wait 3 TCY                                                                                                                             |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                              |

| bit 1-0 | WM<1:0>: TBLWRT Operation with 16-Bit Bus Width bits                                                                                                                    |

|         | 1x = Word Write mode: TABLAT0 and TABLAT1 word output; WRH active when TABLAT1<br>is written                                                                            |

|         | 01 = Byte Select mode: TABLAT data copied on both MSB and LSB; WRH and (UB or LB)<br>will activate                                                                      |

|         | 00 = Byte Write mode: TABLAT data copied on both MSB and LSB; WRH or WRL will activate                                                                                  |

|         |                                                                                                                                                                         |

#### Note 1: If SBOREN is enabled, its Reset state is '1'; otherwise, it is '0'.

| <b>TABLE 8-1</b> : | PIC18F8310/8410 EXTERNAL BUS – I/O PORT FUNCTIONS |

|--------------------|---------------------------------------------------|

|--------------------|---------------------------------------------------|

| Name                          | Port  | Bit | Function                                                                                                         |  |  |  |

|-------------------------------|-------|-----|------------------------------------------------------------------------------------------------------------------|--|--|--|

| RD0/AD0/PSP0                  | PORTD | 0   | Input/Output or System Bus Address bit 0 or Data bit 0 or Parallel Slave Port bit 0                              |  |  |  |

| RD1/AD1/PSP1                  | PORTD | 1   | Input/Output or System Bus Address bit 1 or Data bit 1 or Parallel Slave Port bit 1                              |  |  |  |

| RD2/AD2/PSP2                  | PORTD | 2   | Input/Output or System Bus Address bit 2 or Data bit 2 or Parallel Slave Port bit 2                              |  |  |  |

| RD3/AD3/PSP3                  | PORTD | 3   | Input/Output or System Bus Address bit 3 or Data bit 3 or Parallel Slave Port bit 3                              |  |  |  |

| RD4/AD4/PSP4                  | PORTD | 4   | Input/Output or System Bus Address bit 4 or Data bit 4 or Parallel Slave Port bit 4                              |  |  |  |

| RD5/AD5/PSP5                  | PORTD | 5   | put/Output or System Bus Address bit 5 or Data bit 5 or Parallel Slave Port bit 5                                |  |  |  |

| RD6/AD6/PSP6                  | PORTD | 6   | Input/Output or System Bus Address bit 6 or Data bit 6 or Parallel Slave Port bit 6                              |  |  |  |

| RD7/AD7/PSP7                  | PORTD | 7   | Input/Output or System Bus Address bit 7 or Data bit 7 or Parallel Slave Port bit 7                              |  |  |  |

| RE0/AD8/RD                    | PORTE | 0   | Input/Output or System Bus Address bit 8 or Data bit 8 or Parallel Slave Port Read Control pin                   |  |  |  |

| RE1/AD9/WR                    | PORTE | 1   | Input/Output or System Bus Address bit 9 or Data bit 9 or Parallel Slave Port Write Control pin                  |  |  |  |

| RE2/AD10/CS                   | PORTE | 2   | Input/Output or System Bus Address bit 10 or Data bit 10 or Parallel Slave Port Chip Select pin                  |  |  |  |

| RE3/AD11                      | PORTE | 3   | Input/Output or System Bus Address bit 11 or Data bit 11                                                         |  |  |  |

| RE4/AD12                      | PORTE | 4   | Input/Output or System Bus Address bit 12 or Data bit 12                                                         |  |  |  |

| RE5/AD13                      | PORTE | 5   | Input/Output or System Bus Address bit 13 or Data bit 13                                                         |  |  |  |

| RE6/AD14                      | PORTE | 6   | Input/Output or System Bus Address bit 14 or Data bit 14                                                         |  |  |  |

| RE7/CCP2 <sup>(1)</sup> /AD15 | PORTE | 7   | Input/Output or Capture 2 Input/Compare 2 Output/PWM 2 Output pin or System Bus<br>Address bit 15 or Data bit 15 |  |  |  |

| RH0/AD16                      | PORTH | 0   | Input/Output or System Bus Address bit 16                                                                        |  |  |  |

| RH1/AD17                      | PORTH | 1   | Input/Output or System Bus Address bit 17                                                                        |  |  |  |

| RH2/AD18                      | PORTH | 2   | Input/Output or System Bus Address bit 18                                                                        |  |  |  |

| RH3/AD19                      | PORTH | 3   | Input/Output or System Bus Address bit 19                                                                        |  |  |  |

| RJ0/ALE                       | PORTJ | 0   | Input/Output or System Bus Address Latch Enable (ALE) Control pin                                                |  |  |  |

| RJ1/OE                        | PORTJ | 1   | Input/Output or System Bus Output Enable (OE) Control pin                                                        |  |  |  |

| RJ2/WRL                       | PORTJ | 2   | Input/Output or System Bus Write Low (WRL) Control pin                                                           |  |  |  |

| RJ3/WRH                       | PORTJ | 3   | Input/Output or System Bus Write High (WRH) Control pin                                                          |  |  |  |

| RJ4/BA0                       | PORTJ | 4   | Input/Output or System Bus Byte Address bit 0                                                                    |  |  |  |

| RJ5/CE                        | PORTJ | 5   | Input/Output or System Bus Chip Enable (CE) Control pin                                                          |  |  |  |

| RJ6/LB                        | PORTJ | 6   | Input/Output or System Bus Lower Byte Enable (IB) Control pin                                                    |  |  |  |

| RJ7/UB                        | PORTJ | 7   | Input/Output or System Bus Upper Byte Enable (UB) Control pin                                                    |  |  |  |

|                               |       |     |                                                                                                                  |  |  |  |

Note 1: Alternate assignment for CCP2 when CCP2MX Configuration bit is cleared (all devices in Microcontroller mode).

### 8.1 Program Memory Modes and the External Memory Interface

As previously noted, PIC18F8310/8410 devices are capable of operating in any one of four program memory modes, using combinations of on-chip and external program memory. The functions of the multiplexed port pins depends on the program memory mode selected, as well as the setting of the EBDIS bit.

In **Microcontroller mode**, the bus is not active and the pins have their port functions only. Writes to the MEMCOM register are not permitted.

In **Microprocessor mode**, the external bus is always active and the port pins have only the external bus function.

In **Microprocessor with Boot Block** or **Extended Microcontroller mode**, the external program memory bus shares I/O port functions on the pins. When the device is fetching or doing table read/table write operations on the external program memory space, the pins will have the external bus function. If the device is fetching and accessing internal program memory locations only, the EBDIS control bit will change the pins from external memory to I/O port functions. When EBDIS = 0, the pins function as the external bus. When EBDIS = 1, the pins function as I/O ports.

If the device fetches or accesses external memory while EBDIS = 1, the pins will switch to external bus. If the EBDIS bit is set by a program executing from external memory, the action of setting the bit will be delayed until the program branches into the internal memory. At that time, the pins will change from external bus to I/O ports. NOTES:

### 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software-selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- · Dedicated 8-bit software-programmable prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:          |                                                                      |                                                                                                                                                                                                                                   |                                                                |                    |

|------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------|

| R = Readable bit |                                                                      | W = Writable bit                                                                                                                                                                                                                  | U = Unimplemented bit,                                         | read as '0'        |

| -n = Value       | at POR                                                               | '1' = Bit is set                                                                                                                                                                                                                  | '0' = Bit is cleared                                           | x = Bit is unknowr |

| bit 7            | TMR00M                                                               | I: Timer0 On/Off Control bit                                                                                                                                                                                                      |                                                                |                    |

|                  | 1 = Enat<br>0 = Stop                                                 | oles Timer0<br>s Timer0                                                                                                                                                                                                           |                                                                |                    |

| bit 6            | T08BIT:                                                              | Timer0 8-Bit/16-Bit Control b                                                                                                                                                                                                     | it                                                             |                    |

|                  |                                                                      | r0 is configured as an 8-bit ti<br>r0 is configured as a 16-bit ti                                                                                                                                                                |                                                                |                    |

| bit 5            | <b>T0CS</b> : Ti                                                     | mer0 Clock Source Select bi                                                                                                                                                                                                       | it                                                             |                    |

|                  |                                                                      | sition on T0CKI pin input edg<br>nal clock (Fosc/4)                                                                                                                                                                               | je                                                             |                    |

| bit 4            | TOSE: Ti                                                             | mer0 Source Edge Select bit                                                                                                                                                                                                       | t                                                              |                    |

|                  |                                                                      | ment on high-to-low transitio<br>ment on low-to-high transitio                                                                                                                                                                    | •                                                              |                    |

| bit 3            | PSA: Tin                                                             | ner0 Prescaler Assignment b                                                                                                                                                                                                       | vit                                                            |                    |

|                  |                                                                      |                                                                                                                                                                                                                                   | ; Timer0 clock input bypasses<br>ner0 clock input comes from p |                    |

| bit 2-0          | T0PS<2:                                                              | 0>: Timer0 Prescaler Select                                                                                                                                                                                                       | bits                                                           |                    |

|                  | 110 = 1:<br>101 = 1:<br>100 = 1:<br>011 = 1:<br>010 = 1:<br>010 = 1: | <ul> <li>256 Prescale value</li> <li>128 Prescale value</li> <li>64 Prescale value</li> <li>32 Prescale value</li> <li>16 Prescale value</li> <li>8 Prescale value</li> <li>4 Prescale value</li> <li>2 Prescale value</li> </ul> |                                                                |                    |

### 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software-selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external), with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- · Module Reset on CCP Special Event Trigger

### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCP modules (see **Section 16.1.1** "**CCP Modules and Timer Resources**" for more information).

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| Legend:      |                                                                                                                                          |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|--|--|--|--|--|

| R = Readat   | ole bit                                                                                                                                  | W = Writable bit                                                                                                                | U = Unimplemented bit,                                   | read as '0'          |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                                   | '1' = Bit is set                                                                                                                | '0' = Bit is cleared                                     | x = Bit is unknown   |  |  |  |  |  |

| bit 7        | PD16. 16                                                                                                                                 | Bit Read/Write Mode Enabl                                                                                                       | le hit                                                   |                      |  |  |  |  |  |

|              |                                                                                                                                          | es register read/write of Tim                                                                                                   |                                                          |                      |  |  |  |  |  |

|              |                                                                                                                                          | es register read/write of Tim                                                                                                   |                                                          |                      |  |  |  |  |  |

| bit 6, 3     | T3CCP<2:                                                                                                                                 | 1>: Timer3 and Timer1 to (                                                                                                      | CCPx Enable bits                                         |                      |  |  |  |  |  |

|              |                                                                                                                                          |                                                                                                                                 | ompare/capture of all CCP me                             | odules               |  |  |  |  |  |

|              |                                                                                                                                          | er3 is the clock source for c                                                                                                   |                                                          | 0000                 |  |  |  |  |  |

|              |                                                                                                                                          |                                                                                                                                 | ompare/capture of CCP1 and<br>ompare/capture of CCP2 and |                      |  |  |  |  |  |

|              |                                                                                                                                          | 01 = Timer3 is the clock source for compare/capture of CCP2 and CCP3,<br>Timer1 is the clock source for compare/capture of CCP1 |                                                          |                      |  |  |  |  |  |

|              | 00 = Timer1 is the clock source for compare/capture of all CCP modules                                                                   |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

| bit 5-4      | T3CKPS<1:0>: Timer3 Input Clock Prescale Select bits                                                                                     |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|              | 11 <b>= 1:8 P</b>                                                                                                                        | 11 = 1:8 Prescale value                                                                                                         |                                                          |                      |  |  |  |  |  |

|              |                                                                                                                                          | 10 = 1:4 Prescale value                                                                                                         |                                                          |                      |  |  |  |  |  |

|              | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                       |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

| bit 2        |                                                                                                                                          |                                                                                                                                 | t Synchronization Control bit                            |                      |  |  |  |  |  |

|              | <b>T3SYNC:</b> Timer3 External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.)        |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|              | When TMR3CS = 1:                                                                                                                         |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|              |                                                                                                                                          | 1 = Do not synchronize external clock input                                                                                     |                                                          |                      |  |  |  |  |  |

|              | 0 = Synchronize external clock input                                                                                                     |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|              | <u>When TMR3CS = 0:</u><br>This bit is ignored. Timer3 uses the internal clock when TMR3CS = 0.                                          |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

| bit 1        |                                                                                                                                          | •                                                                                                                               |                                                          | 0.                   |  |  |  |  |  |

| DILI         | <b>TMR3CS:</b> Timer3 Clock Source Select bit<br>1 = External clock input from Timer1 oscillator or T13CKI (on the rising edge after the |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

|              |                                                                                                                                          | Illing edge)                                                                                                                    |                                                          | שווש בעשב מונבו נווב |  |  |  |  |  |

|              | 0 = Internal clock (Fosc/4)                                                                                                              |                                                                                                                                 |                                                          |                      |  |  |  |  |  |

| bit 0        | TMR3ON:                                                                                                                                  | Timer3 On bit                                                                                                                   |                                                          |                      |  |  |  |  |  |

|              | 1 = Enable                                                                                                                               | es Timer3                                                                                                                       |                                                          |                      |  |  |  |  |  |

|              | 0 = Stops                                                                                                                                | Timer3                                                                                                                          |                                                          |                      |  |  |  |  |  |

| Name    | Bit 7                                | Bit 6          | Bit 5      | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|---------|--------------------------------------|----------------|------------|----------|----------|--------|---------|---------|----------------------------|

| INTCON  | GIE/GIEH                             | PEIE/GIEL      | TMR0IE     | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 63                         |

| RCON    | IPEN                                 | SBOREN         | _          | RI       | TO       | PD     | POR     | BOR     | 64                         |

| PIR1    | PSPIF                                | ADIF           | RC1IF      | TX1IF    | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 65                         |

| PIE1    | PSPIE                                | ADIE           | RC1IE      | TX1IE    | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 65                         |

| IPR1    | PSPIP                                | ADIP           | RC1IP      | TX1IP    | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 65                         |

| TRISB   | PORTB Da                             | ta Direction I | Register   |          |          |        |         |         | 66                         |

| TRISC   | PORTC Da                             | ta Direction   | Register   |          |          |        |         |         | 66                         |

| TRISE   | PORTE Data Direction Register        |                |            |          |          |        |         | 66      |                            |

| TMR2    | Timer2 Reg                           | gister         |            |          |          |        |         |         | 64                         |

| PR2     | Timer2 Per                           | iod Register   |            |          |          |        |         |         | 64                         |

| T2CON   | _                                    | T2OUTPS3       | T2OUTPS2   | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 64                         |

| CCPR1L  | Capture/Co                           | ompare/PWN     | Register 1 | (LSB)    |          |        |         |         | 65                         |

| CCPR1H  | Capture/Co                           | mpare/PWN      | Register 1 | (MSB)    |          |        |         |         | 65                         |

| CCP1CON |                                      | _              | DC1B1      | DC1B0    | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 65                         |

| CCPR2L  | Capture/Compare/PWM Register 2 (LSB) |                |            |          |          |        |         | 65      |                            |

| CCPR2H  | Capture/Compare/PWM Register 2 (MSB) |                |            |          |          |        | 65      |         |                            |

| CCP2CON |                                      | _              | DC2B1      | DC2B0    | CCP2M3   | CCP2M2 | CCP2M1  | CCP2M0  | 65                         |

| CCPR3L  | Capture/Compare/PWM Register 3 (LSB) |                |            |          |          |        |         | 65      |                            |

| CCPR3H  | Capture/Compare/PWM Register 3 (MSB) |                |            |          |          |        |         | 65      |                            |

| CCP3CON |                                      | _              | DC3B1      | DC3B0    | CCP3M3   | CCP3M2 | CCP3M1  | CCP3M0  | 65                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

NOTES:

### 17.3.8 SLEEP OPERATION

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

In most power-managed modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 3.7 "Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

### 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |  |

|-------------------|--------------------|-----|--|--|--|

| Terminology       | СКР                | CKE |  |  |  |

| 0, 0              | 0                  | 1   |  |  |  |

| 0, 1              | 0                  | 0   |  |  |  |

| 1, 0              | 1                  | 1   |  |  |  |

| 1, 1              | 1                  | 0   |  |  |  |

### TABLE 17-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| IADLE I/- | -2: REGISTERS ASSOCIATED WITH SPIOPERATION                      |              |          |        |       |        |        |        |                            |

|-----------|-----------------------------------------------------------------|--------------|----------|--------|-------|--------|--------|--------|----------------------------|

| Name      | Bit 7                                                           | Bit 6        | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

| INTCON    | GIE/GIEH                                                        | PEIE/GIEL    | TMR0IE   | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR1      | PSPIF                                                           | ADIF         | RC1IF    | TX1IF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 65                         |

| PIE1      | PSPIE                                                           | ADIE         | RC1IE    | TX1IE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 65                         |

| IPR1      | PSPIP                                                           | ADIP         | RC1IP    | TX1IP  | SSPIP | CCP1IP | TMR2IP | TMR1IP | 65                         |

| TRISC     | PORTC Da                                                        | ta Direction | Register |        |       |        |        |        | 66                         |

| TRISF     | PORTF Data Direction Register                                   |              |          |        |       |        |        | 66     |                            |

| SSPBUF    | Master Synchronous Serial Port Receive Buffer/Transmit Register |              |          |        |       |        |        | 64     |                            |

| SSPCON1   | WCOL                                                            | SSPOV        | SSPEN    | CKP    | SSPM3 | SSPM2  | SSPM1  | SSPM0  | 64                         |

| SSPSTAT   | SMP                                                             | CKE          | D/A      | Р      | S     | R/W    | UA     | BF     | 64                         |

### TABLE 17-2: REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

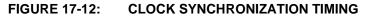

### 17.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has

already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2$ C bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 17-12).

| Name     | Bit 7                                          | Bit 6                                        | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|------------------------------------------------|----------------------------------------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                       | PEIE/GIEL                                    | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR1     | PSPIF                                          | ADIF                                         | RC1IF  | TX1IF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 65                         |

| PIE1     | PSPIE                                          | ADIE                                         | RC1IE  | TX1IE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 65                         |

| IPR1     | PSPIP                                          | ADIP                                         | RC1IP  | TX1IP  | SSPIP | CCP1IP | TMR2IP | TMR1IP | 65                         |

| RCSTA1   | SPEN                                           | RX9                                          | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 65                         |

| TXREG1   | EUSART1                                        | Transmit Re                                  | gister |        |       |        |        |        | 65                         |

| TXSTA1   | CSRC                                           | TX9                                          | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 65                         |

| BAUDCON1 | ABDOVF                                         | RCIDL                                        | RXDTP  | TXCKP  | BRG16 | —      | WUE    | ABDEN  | 66                         |

| SPBRGH1  | EUSART1 Baud Rate Generator Register High Byte |                                              |        |        |       |        |        | 66     |                            |

| SPBRG1   | EUSART1                                        | USART1 Baud Rate Generator Register Low Byte |        |        |       |        |        |        |                            |

| SPBRGH1  |                                                |                                              |        |        |       |        |        |        | 6<br>6                     |

### TABLE 18-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

### 19.2 AUSART Asynchronous Mode

The Asynchronous mode of operation is selected by clearing the SYNC bit (TXSTA2<4>). In this mode, the AUSART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one Stop bit). The most common data format is 8 bits. An on-chip dedicated 8-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator.

The AUSART transmits and receives the LSb first. The AUSART's transmitter and receiver are functionally independent but use the same data format and baud rate. The Baud Rate Generator produces a clock, either x16 or x64 of the bit shift rate, depending on the BRGH bit (TXSTA2<2>). Parity is not supported by the hardware but can be implemented in software and stored as the 9th data bit.

When operating in Asynchronous mode, the AUSART module consists of the following important elements:

- Baud Rate Generator

- · Sampling Circuit

- · Asynchronous Transmitter

- · Asynchronous Receiver

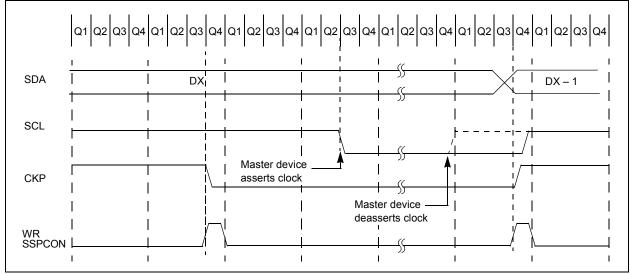

### 19.2.1 AUSART ASYNCHRONOUS TRANSMITTER

The AUSART transmitter block diagram is shown in Figure 19-1. The heart of the transmitter is the Transmit (Serial) Shift register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG2. The TXREG2 register is loaded with data in software. The TSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the TSR is loaded with new data from the TXREG2 register (if available).

Once the TXREG2 register transfers the data to the TSR register (occurs in one Tcr), the TXREG2 register is empty and the TX2IF flag bit (PIR3<4>) is set. This

interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TX2IE (PIE3<4>). TX2IF will be set regardless of the state of TX2IE; it cannot be cleared in software. TX2IF is also not cleared immediately upon loading TXREG2, but becomes valid in the second instruction cycle following the load instruction. Polling TX2IF immediately following a load of TXREG2 will return invalid results.

While TX2IF indicates the status of the TXREG2 register, another bit, TRMT (TXSTA2<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty.

- **Note 1:** The TSR register is not mapped in data memory so it is not available to the user.

- **2:** Flag bit, TX2IF, is set when enable bit, TXEN is set.

To set up an Asynchronous Transmission:

- 1. Initialize the SPBRG2 register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, TX2IE.

- 4. If 9-bit transmission is desired, set transmit bit, TX9. Can be used as address/data bit.

- 5. Enable the transmission by setting bit, TXEN, which will also set bit, TX2IF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Load data to the TXREG2 register (starts transmission).

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 19-1: AUSART TRANSMIT BLOCK DIAGRAM

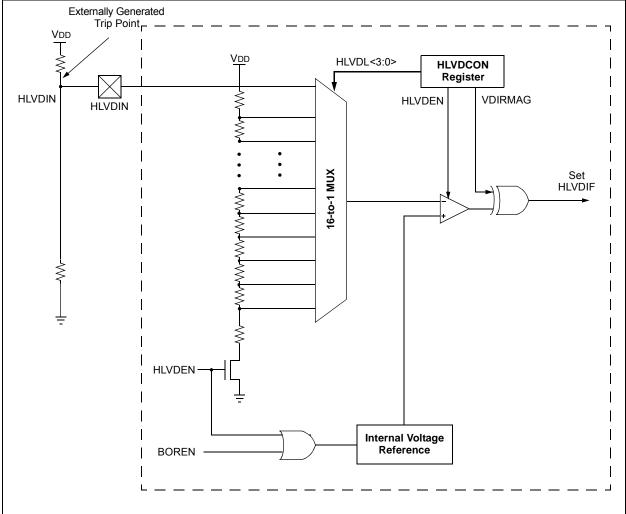

The module is enabled by setting the HLVDEN bit. Each time that the HLVD module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit and is used to indicate when the circuit is stable. The module can only generate an interrupt after the circuit is stable and IRVST is set.

The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

### 23.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module. When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

The HLVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the High/Low-Voltage Detect interrupt to occur at any voltage in the valid operating range.

### REGISTER 24-4: CONFIG3L: CONFIGURATION REGISTER 3 LOW (BYTE ADDRESS 300004h)

| R/P-1   | R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1 | R/P-1 |

|---------|-------|-----|-----|-----|-----|-------|-------|

| WAIT    | BW    | —   | _   | _   | —   | PM1   | PM0   |

| bit 7   | •     | •   |     |     |     |       | bit 0 |

|         |       |     |     |     |     |       |       |

| Legend: |       |     |     |     |     |       |       |

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------------|----------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at erase bit | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 7   | WAIT: External Bus Data Wait Enable bit<br>1 = Wait selections are unavailable, device will not wait<br>0 = Wait is programmed by the WAIT1 and WAIT0 bits of the MEMCOM register (MEMCOM<5:4>)                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | BW: External Bus Data Width Select bit                                                                                                                                                                                   |

|         | <ul> <li>1 = 16-bit external bus data width</li> <li>0 = 8-bit external bus data width</li> </ul>                                                                                                                        |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                                                                               |

| bit 1-0 | PM<1:0>: Processor Data Memory Mode Select bits                                                                                                                                                                          |

|         | <ul> <li>11 = Microcontroller mode</li> <li>10 = Microprocessor mode<sup>(1)</sup></li> <li>01 = Microcontroller with Boot Block mode<sup>(1)</sup></li> <li>00 = Extended Microcontroller mode<sup>(1)</sup></li> </ul> |

Note 1: This mode is only available on PIC18F8310/8410 devices.

| R/P-1                  | U-0                                                                                                                                                                                                                        | U-0                                                                                                                                           | U-0            | U-0              | R/P-0            | U-0            | R/P-1  |  |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|----------------|--------|--|--|--|--|

| MCLRE                  | —                                                                                                                                                                                                                          | —                                                                                                                                             | _              | _                | LPT10SC          | —              | CCP2MX |  |  |  |  |

| bit 7                  |                                                                                                                                                                                                                            |                                                                                                                                               |                |                  |                  |                | bit 0  |  |  |  |  |

|                        |                                                                                                                                                                                                                            |                                                                                                                                               |                |                  |                  |                |        |  |  |  |  |

| Legend:<br>R = Readabl | e hit                                                                                                                                                                                                                      | P = Programn                                                                                                                                  | nahla hit      | =   Inimplei     | mented bit, read | l as 'O'       |        |  |  |  |  |

| -n = Value at          |                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                              |                | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|                        |                                                                                                                                                                                                                            |                                                                                                                                               |                | 0 2.1.0 0.0      |                  |                |        |  |  |  |  |

| bit 7                  | MCLRE: MCL                                                                                                                                                                                                                 | R Pin Enable I                                                                                                                                | oit            |                  |                  |                |        |  |  |  |  |

|                        | $1 = \overline{MCLR} pin$                                                                                                                                                                                                  | = MCLR pin is enabled; RG5 input pin is disabled                                                                                              |                |                  |                  |                |        |  |  |  |  |

|                        | 0 = RG5 input                                                                                                                                                                                                              | t pin is enabled                                                                                                                              | ; MCLR is dis  | sabled           |                  |                |        |  |  |  |  |

| bit 6-3                | Unimplemen                                                                                                                                                                                                                 | ted: Read as '                                                                                                                                | )'             |                  |                  |                |        |  |  |  |  |

| bit 2                  | LPT1OSC: Lo                                                                                                                                                                                                                | ow-Power Time                                                                                                                                 | r 1 Oscillator | Enable bit       |                  |                |        |  |  |  |  |

|                        |                                                                                                                                                                                                                            | configured for<br>configured for                                                                                                              |                |                  |                  |                |        |  |  |  |  |

| bit 1                  | Unimplemen                                                                                                                                                                                                                 | ted: Read as '                                                                                                                                | )              |                  |                  |                |        |  |  |  |  |

| bit 0                  | CCP2MX: CC                                                                                                                                                                                                                 | P2 MUX bit                                                                                                                                    |                |                  |                  |                |        |  |  |  |  |

|                        | 1 = CCP2 inp                                                                                                                                                                                                               | In Microcontroller Mode only (all devices):<br>1 = CCP2 input/output is multiplexed with RC1<br>0 = CCP2 input/output is multiplexed with RE7 |                |                  |                  |                |        |  |  |  |  |

|                        | In Microprocessor, Extended Microcontroller and Microcontroller with Boot Block Modes<br>(PIC18F8310/8410 devices only):<br>1 = CCP2 input/output is multiplexed with RC1<br>0 = CCP2 input/output is multiplexed with RB3 |                                                                                                                                               |                |                  |                  |                |        |  |  |  |  |

### REGISTER 24-5: CONFIG3H: CONFIGURATION REGISTER 3 HIGH (BYTE ADDRESS 300005h)

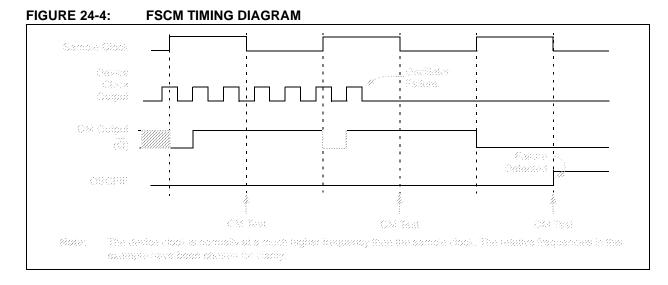

### 24.4.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. Fail-Safe Clock monitoring of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTOSC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, the device will not exit the power-managed mode on oscillator failure. Instead, the device will continue to operate as before, but clocked by the INTOSC multiplexer. While in Idle mode, subsequent interrupts will cause the CPU to begin executing instructions while being clocked by the INTOSC multiplexer.

### 24.4.4 POR OR WAKE FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is in EC, RC or INTRC modes, monitoring can begin immediately following these events.

For oscillator modes involving a crystal or resonator (HS, HSPLL, LP or XT), the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FCSM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscillator failure interrupts on POR, or wake from Sleep, will also prevent the |

|-------|--------------------------------------------------------------------------------------------------------------------|

|       | detection of the oscillator's failure to start                                                                     |

|       | at all following these events. This can be                                                                         |

|       | avoided by monitoring the OSTS bit and                                                                             |

|       | using a timing routine to determine if the                                                                         |

|       | oscillator is taking too long to start. Even                                                                       |

|       | so, no oscillator failure interrupt will be                                                                        |

|       | flagged.                                                                                                           |

As noted in **Section 24.3.1 "Special Considerations for Using Two-Speed Start-up"**, it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new powered-managed mode is selected, the primary clock is disabled.

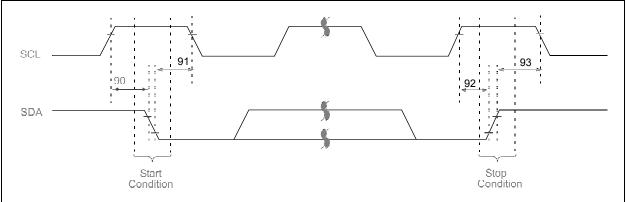

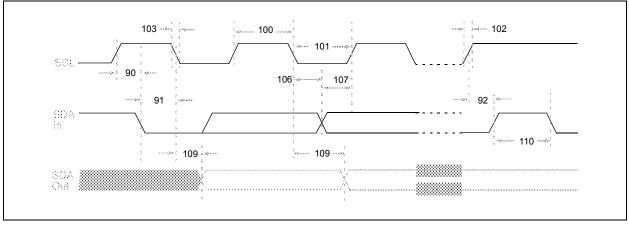

### TABLE 27-19: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characteristic  |              | Min  | Max | Units | Conditions                                 |

|---------------|---------|-----------------|--------------|------|-----|-------|--------------------------------------------|

| 90            | TSU:STA | Start Condition | 100 kHz mode | 4700 | _   | ns    | Only relevant for Repeated Start condition |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                                            |

| 91            | THD:STA | Start Condition | 100 kHz mode | 4000 | _   | ns    | After this period, the first               |

|               |         | Hold Time       | 400 kHz mode | 600  | —   |       | clock pulse is generated                   |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _   | ns    |                                            |

|               |         | Setup Time      | 400 kHz mode | 600  | _   |       |                                            |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | _   | ns    |                                            |

|               |         | Hold Time       | 400 kHz mode | 600  |     |       |                                            |

### FIGURE 27-19: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

| TBLRD                                           | 335 |

|-------------------------------------------------|-----|

| TBLWT                                           | 336 |

| TSTFSZ                                          |     |

| XORLW                                           |     |

| XORWF                                           |     |

| Summary Table                                   |     |

| INTCON Register                                 |     |

| RBIF Bit                                        | 100 |

|                                                 |     |

| INTCON Registers                                |     |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |     |

| Internal Oscillator Block                       |     |

| Adjustment                                      |     |

| INTIO Modes                                     |     |

| INTOSC Frequency Drift                          |     |

| INTOSC Output Frequency                         |     |

| OSCTUNE Register                                |     |

| Internal RC Oscillator                          |     |

| Use with WDT                                    | 290 |

| Internet Address                                |     |

| Interrupt Sources                               |     |

| A/D Conversion Complete                         |     |

| Context Saving During Interrupts                | 124 |

| Interrupt-on-Change (RB7:RB4)                   | 128 |

| INTx Pin                                        |     |

| PORTB, Interrupt-on-Change                      | 124 |

|                                                 |     |

| TMR0                                            |     |

| TMR0 Overflow                                   |     |

| TMR1 Overflow                                   | 155 |

| TMR2 to PR2 Match (PWM)                         |     |

| TMR3 Overflow                                   |     |

| Interrupts                                      | 109 |

| Interrupts, Flag Bits                           |     |

| Interrupt-on-Change (RB7:RB4) Flag              |     |

| (RBIF Bit)                                      | 128 |

| INTOSC, INTRC. See Internal Oscillator Block.   |     |

| IORLW                                           | 320 |

| IORWF                                           | 320 |

| IPR Registers                                   | 120 |

|                                                 |     |

| L                                               |     |

| LFSR                                            | 321 |

| м                                               |     |