Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 × 8                                                                   |

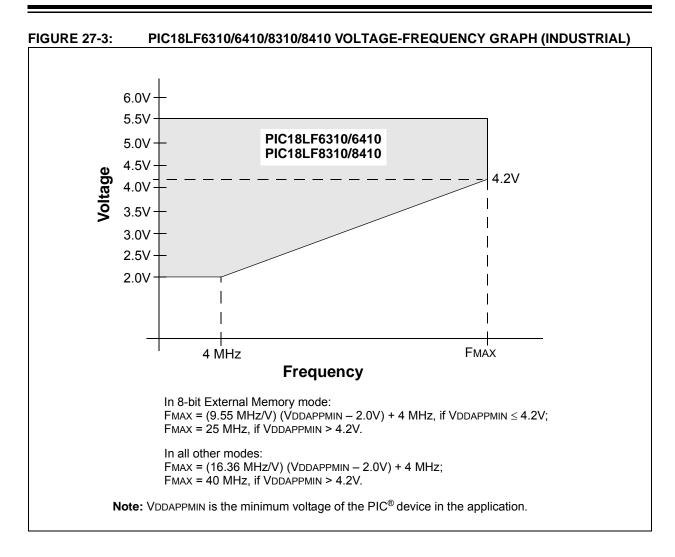

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

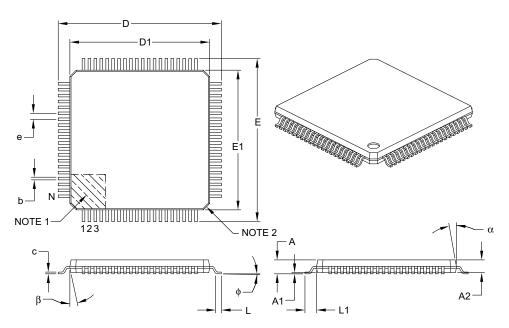

| Mounting Type              | Surface Mount                                                             |

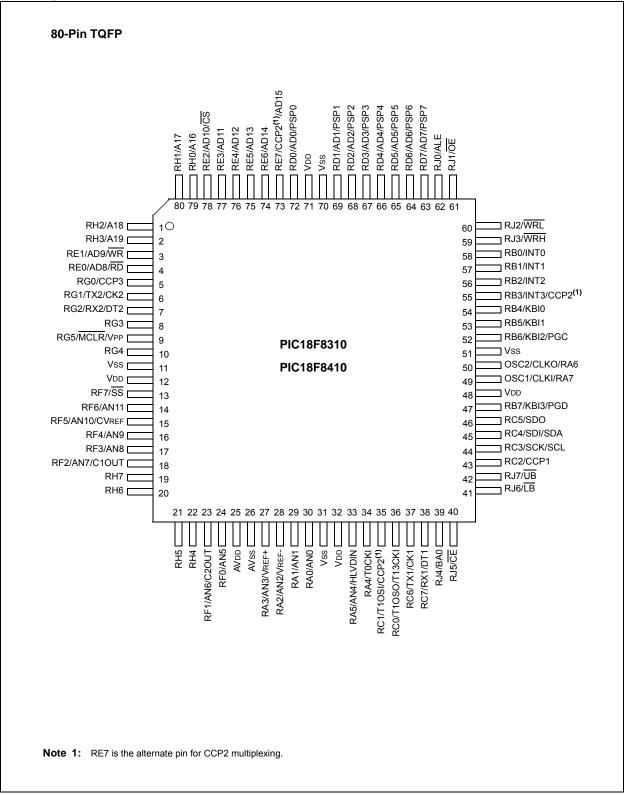

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8310-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Pin Diagrams (Continued)**

#### 6.1.1 PIC18F8310/8410 PROGRAM MEMORY MODES

In addition to available on-chip Flash program memory, 80-pin devices in this family can also address up to 2 Mbytes of external program memory through an external memory interface. There are four distinct operating modes available to the controllers:

- Microprocessor (MP)

- Microprocessor with Boot Block (MPBB)

- Extended Microcontroller (EMC)

- Microcontroller (MC)

The program memory mode is determined by setting the two Least Significant bits of the CONFIG3L Configuration byte, as shown in Register 6-1. (See also **Section 24.1 "Configuration Bits**" for additional details on the device Configuration bits.)

The program memory modes operate as follows:

• The Microcontroller Mode accesses only on-chip Flash memory. Attempts to read above the physical limit of the on-chip Flash (3FFFh) causes a read of all '0's (a NOP instruction). The Microcontroller mode is also the only operating mode available to PIC18F6310 and PIC18F6410 devices.

- The Extended Microcontroller Mode allows access to both internal and external program memories as a single block. The device can access its entire on-chip Flash memory; above this, the device accesses external program memory up to the 2-Mbyte program space limit. As with Boot Block mode, execution automatically switches between the two memories as required.

- The Microprocessor Mode permits access only to external program memory; the contents of the on-chip Flash memory is ignored. The 21-bit program counter permits access to the entire 2-Mbyte linear program memory space.

- The Microprocessor with Boot Block Mode accesses on-chip Flash memory from addresses 000000h to 0007FFh. Above this, external program memory is accessed all the way up to the 2-Mbyte limit. Program execution automatically switches between the two memories as required.

In all modes, the microcontroller has complete access to data RAM.

Figure 6-2 compares the memory maps of the different program memory modes. The differences between on-chip and external memory access limitations are more fully explained in Table 6-1.

#### REGISTER 6-1: CONFIG3L: CONFIGURATION BYTE REGISTER LOW

| R/P-1   | R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1 | R/P-1 |

|---------|-------|-----|-----|-----|-----|-------|-------|

| WAIT    | BW    | —   | —   | _   | —   | PM1   | PM0   |

| bit 7   |       | •   |     |     |     | •     | bit 0 |

|         |       |     |     |     |     |       |       |

| Legend: |       |     |     |     |     |       |       |

| Legena:                                                                                                                                    |                         |                                         |                       |                    |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------|-----------------------|--------------------|--|--|--|--|--|--|

| R = Reada                                                                                                                                  | able bit                | P = Programmable bit                    | U = Unimplemented bit | , read as '0'      |  |  |  |  |  |  |

| -n = Value                                                                                                                                 | after erase bit         | '1' = Bit is set                        | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |  |  |

| bit 7                                                                                                                                      | WAIT: Exter             | rnal Bus Data Wait Enable b             | it                    |                    |  |  |  |  |  |  |

| 1 = Wait selections unavailable, device will not wait         0 = Wait programmed by WAIT1 and WAIT0 bits of MEMCOM register (MEMCOM<5:4>) |                         |                                         |                       |                    |  |  |  |  |  |  |

| bit 6                                                                                                                                      | BW: Extern              | al Bus Data Width Select bit            |                       |                    |  |  |  |  |  |  |

|                                                                                                                                            | 1 = 16-bit e            | = 16-bit external bus data width        |                       |                    |  |  |  |  |  |  |

|                                                                                                                                            | 0 = 8-bit ext           | ternal bus data width                   |                       |                    |  |  |  |  |  |  |

| bit 5-2                                                                                                                                    | Unimpleme               | ented: Read as '0'                      |                       |                    |  |  |  |  |  |  |

| bit 1-0                                                                                                                                    | <b>PM&lt;1:0&gt;:</b> F | Processor Data Memory Moc               | le Select bits        |                    |  |  |  |  |  |  |

|                                                                                                                                            |                         | controller mode                         |                       |                    |  |  |  |  |  |  |

|                                                                                                                                            |                         | processor mode <sup>(1)</sup>           | (4)                   |                    |  |  |  |  |  |  |

|                                                                                                                                            |                         | controller with Boot Block mc           | de <sup>(1)</sup>     |                    |  |  |  |  |  |  |

|                                                                                                                                            | 00 = Extend             | ded Microcontroller mode <sup>(1)</sup> |                       |                    |  |  |  |  |  |  |

| Note 1:                                                                                                                                    | This mode is ava        | ailable only on PIC18F8410              | devices.              |                    |  |  |  |  |  |  |

|                                                                                                                                            |                         |                                         |                       |                    |  |  |  |  |  |  |

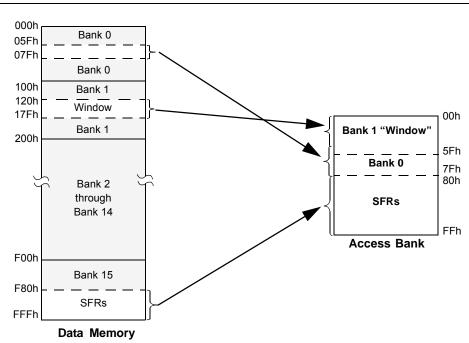

### 6.5.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 6.3.2 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 6-10.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before.

## 6.6 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 25.2 "Extended Instruction Set**".

### FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

### Example Situation:

ADDWF f, d, a FSR2H:FSR2L = 120h

Locations in the region from the FSR2 Pointer (120h) to the pointer plus 05Fh (17Fh) are mapped to the bottom of the Access RAM (000h-05Fh).

Locations in Bank 0 from 060h to 07Fh are mapped, as usual, to the middle of the Access Bank.

Special Function Registers at F80h through FFFh are mapped to 80h through FFh, as usual.

Bank 0 addresses below 5Fh can still be addressed by using the BSR.

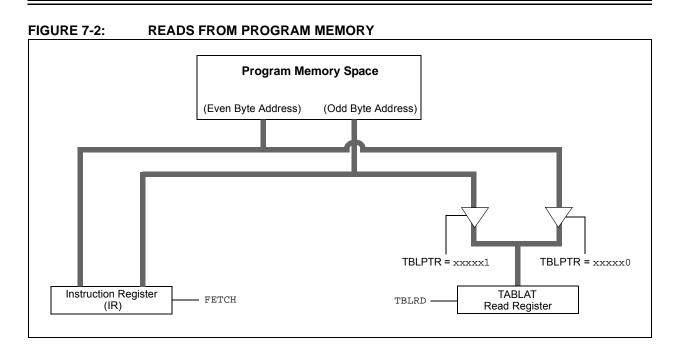

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base      |

|-----------|---------|-----------------|---|--------------------------------|

|           | MOVWF   | TBLPTRU         | ; | address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |   |                                |

|           | MOVWF   | TBLPTRH         |   |                                |

|           | MOVLW   | CODE_ADDR_LOW   |   |                                |

|           | MOVWF   | TBLPTRL         |   |                                |

| READ_WORD |         |                 |   |                                |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVWF   | WORD_EVEN       |   |                                |

|           | TBLRD*+ |                 | ; | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ; | get data                       |

|           | MOVF    | WORD_ODD        |   |                                |

|           |         |                 |   |                                |

NOTES:

#### 10.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

#### REGISTER 10-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| R/W-1         | R/W-1                                                 | R/W-1            | R/W-1                          | R/W-1                              | R/W-1  | R/W-1              | R/W-1  |  |  |  |

|---------------|-------------------------------------------------------|------------------|--------------------------------|------------------------------------|--------|--------------------|--------|--|--|--|

| PSPIP         | ADIP                                                  | RC1IP            | TX1IP                          | SSPIP                              | CCP1IP | TMR2IP             | TMR1IP |  |  |  |

| bit 7         | ·                                                     |                  |                                |                                    |        |                    | bit (  |  |  |  |

|               |                                                       |                  |                                |                                    |        |                    |        |  |  |  |

| Legend:       |                                                       |                  |                                |                                    |        |                    |        |  |  |  |

| R = Readabl   | le bit                                                | W = Writable     | bit                            | U = Unimplemented bit, read as '0' |        |                    |        |  |  |  |

| -n = Value at | t POR                                                 | '1' = Bit is set |                                | '0' = Bit is cle                   | ared   | x = Bit is unknown |        |  |  |  |

| bit 7         | <b>PSPIP:</b> Paral<br>1 = High prio<br>0 = Low prior | rity             | Read/Write In                  | terrupt Priority I                 | bit    |                    |        |  |  |  |

| bit 6         | ADIP: A/D Co                                          | onverter Interru | nverter Interrupt Priority bit |                                    |        |                    |        |  |  |  |

|               | 1 = High prio<br>0 = Low prior                        | •                |                                |                                    |        |                    |        |  |  |  |

| hit E         | DCAID. FUC                                            |                  | town with Duioni               | 4 In 14                            |        |                    |        |  |  |  |

|       | 0 = Low priority                                                    |

|-------|---------------------------------------------------------------------|

| bit 5 | RC1IP: EUSART Receive Interrupt Priority bit                        |

|       | 1 = High priority                                                   |

|       | 0 = Low priority                                                    |

| bit 4 | TX1IP: EUSART Transmit Interrupt Priority bit                       |

|       | 1 = High priority                                                   |

|       | 0 = Low priority                                                    |

| bit 3 | <b>SSPIP:</b> Master Synchronous Serial Port Interrupt Priority bit |

|       | 1 = High priority                                                   |

|       | 0 = Low priority'                                                   |

| bit 2 | CCP1IP: CCP1 Interrupt Priority bit                                 |

|       | 1 = High priority                                                   |

|       | 0 = Low priority                                                    |

| bit 1 | TMR2IP: TMR2 to PR2 Match Interrupt Priority bit                    |

|       | 1 = High priority                                                   |

|       | 0 = Low priority                                                    |

| bit 0 | TMR1IP: TMR1 Overflow Interrupt Priority bit                        |

|       | 1 = High priority                                                   |

|       | 0 = Low priority                                                    |

|       |                                                                     |

| U-0                                                                  | U-0                                       | R-1               | R-1              | U-0               | U-0  | U-0             | R/W-1  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------|-------------------------------------------|-------------------|------------------|-------------------|------|-----------------|--------|--|--|--|--|--|--|--|

| _                                                                    | —                                         | RC2IP             | TX21P            | —                 | —    | —               | CCP3IP |  |  |  |  |  |  |  |

| bit 7                                                                |                                           |                   |                  |                   |      |                 | bit 0  |  |  |  |  |  |  |  |

|                                                                      |                                           |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| Legend:                                                              |                                           |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                           |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| -n = Value at                                                        | POR                                       | '1' = Bit is set  |                  | '0' = Bit is cle  | ared | x = Bit is unkr | nown   |  |  |  |  |  |  |  |

|                                                                      |                                           |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| bit 7-6                                                              | Unimplemen                                | ted: Read as '    | 0'               |                   |      |                 |        |  |  |  |  |  |  |  |

| bit 5                                                                | RC2IP: AUSA                               | ART Receive P     | riority Flag bit | t                 |      |                 |        |  |  |  |  |  |  |  |

|                                                                      | 1 = High prio                             |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

|                                                                      | 0 = Low prior                             | 0 = Low priority  |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| bit 4                                                                | TX2IP: AUSA                               | RT Transmit Ir    | nterrupt Priori  | ty bit            |      |                 |        |  |  |  |  |  |  |  |

|                                                                      | 1 = High prio                             | 1 = High priority |                  |                   |      |                 |        |  |  |  |  |  |  |  |

|                                                                      | 0 = Low prior                             | ity               |                  |                   |      |                 |        |  |  |  |  |  |  |  |

| bit 3-1                                                              | Unimplemen                                | ted: Read as '    | 0'               |                   |      |                 |        |  |  |  |  |  |  |  |

| bit 0                                                                | bit 0 CCP3IP: CCP3 Interrupt Priority bit |                   |                  |                   |      |                 |        |  |  |  |  |  |  |  |

|                                                                      | 1 = High prio                             | ritv              |                  | 1 = High priority |      |                 |        |  |  |  |  |  |  |  |

#### REGISTER 10-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

1 = High priority0 = Low priority

| Name    | Bit 7                         | Bit 6          | Bit 5      | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|---------|-------------------------------|----------------|------------|----------|----------|--------|---------|---------|----------------------------|

| INTCON  | GIE/GIEH                      | PEIE/GIEL      | TMR0IE     | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 63                         |

| RCON    | IPEN                          | SBOREN         | _          | RI       | TO       | PD     | POR     | BOR     | 64                         |

| PIR1    | PSPIF                         | ADIF           | RC1IF      | TX1IF    | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 65                         |

| PIE1    | PSPIE                         | ADIE           | RC1IE      | TX1IE    | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 65                         |

| IPR1    | PSPIP                         | ADIP           | RC1IP      | TX1IP    | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 65                         |

| TRISB   | PORTB Da                      | ta Direction I | Register   |          |          |        |         |         | 66                         |

| TRISC   | PORTC Da                      | ta Direction   | Register   |          |          |        |         |         | 66                         |

| TRISE   | PORTE Data Direction Register |                |            |          |          |        |         |         |                            |

| TMR2    | Timer2 Register               |                |            |          |          |        |         |         |                            |

| PR2     | Timer2 Per                    | iod Register   |            |          |          |        |         |         | 64                         |

| T2CON   | _                             | T2OUTPS3       | T2OUTPS2   | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 64                         |

| CCPR1L  | Capture/Co                    | ompare/PWN     | Register 1 | (LSB)    |          |        |         |         | 65                         |

| CCPR1H  | Capture/Co                    | mpare/PWN      | Register 1 | (MSB)    |          |        |         |         | 65                         |

| CCP1CON |                               | _              | DC1B1      | DC1B0    | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 65                         |

| CCPR2L  | Capture/Co                    | mpare/PWN      | Register 2 | (LSB)    |          |        |         |         | 65                         |

| CCPR2H  | Capture/Co                    | mpare/PWN      | Register 2 | (MSB)    |          |        |         |         | 65                         |

| CCP2CON |                               | _              | DC2B1      | DC2B0    | CCP2M3   | CCP2M2 | CCP2M1  | CCP2M0  | 65                         |

| CCPR3L  | Capture/Co                    | mpare/PWN      | Register 3 | (LSB)    |          |        |         |         | 65                         |

| CCPR3H  | Capture/Co                    | mpare/PWN      | Register 3 | (MSB)    |          |        |         |         | 65                         |

| CCP3CON |                               | _              | DC3B1      | DC3B0    | CCP3M3   | CCP3M2 | CCP3M1  | CCP3M0  | 65                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

#### 17.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDI must have TRISC<4> bit cleared

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISF<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

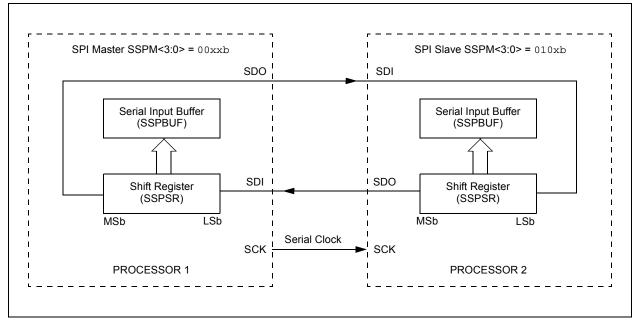

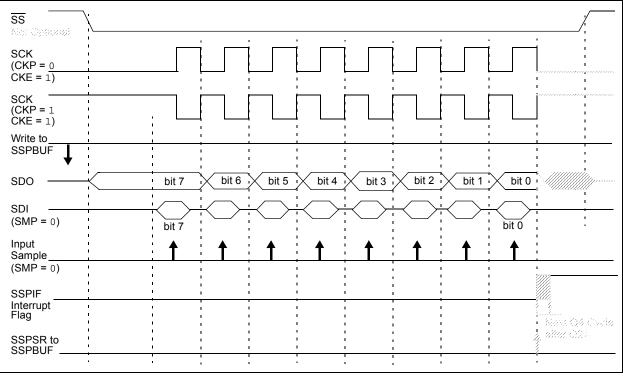

### 17.3.4 TYPICAL CONNECTION

Figure 17-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

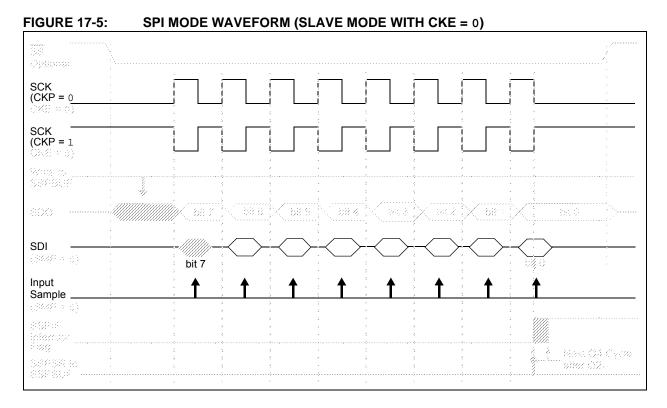

### FIGURE 17-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

|                                                             | R/W-0                                                                                                            | R/W-0                         | R/W-0                    | R/W-0                          | R/W-0               | R/W-0               | R/W-0               | R/W-0              |  |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|--------------------------------|---------------------|---------------------|---------------------|--------------------|--|--|--|

|                                                             | GCEN                                                                                                             | ACKSTAT                       | ACKDT <sup>(1)</sup>     | ACKEN <sup>(2)</sup>           | RCEN <sup>(2)</sup> | PEN <sup>(2)</sup>  | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |  |  |  |

| b                                                           | it 7                                                                                                             |                               |                          |                                |                     |                     |                     | bit 0              |  |  |  |

| G                                                           | CEN: Ge                                                                                                          | neral Call Er                 | able bit (Sla            | ave mode on                    | ly)                 |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | interrupt wh<br>I call addres |                          | I call addres                  | s (0000h) is        | received in         | the SSPSR           |                    |  |  |  |

| ACKSTAT: Acknowledge Status bit (Master Transmit mode only) |                                                                                                                  |                               |                          |                                |                     |                     |                     |                    |  |  |  |

|                                                             | <ul> <li>1 = Acknowledge was not received from slave</li> <li>0 = Acknowledge was received from slave</li> </ul> |                               |                          |                                |                     |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | viedge was r<br>cknowledge l  |                          |                                | mode only)          | (1)                 |                     |                    |  |  |  |

|                                                             |                                                                                                                  | knowledge                     | Jala Dil (ivia           | SIEI RECEIVE                   | mode only)          |                     |                     |                    |  |  |  |

|                                                             | = Acknov                                                                                                         | •                             |                          |                                |                     |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | cknowledge                    | -                        | -                              |                     |                     |                     |                    |  |  |  |

| 1                                                           |                                                                                                                  | Acknowledge<br>atically clear |                          |                                | d SCL pins a        | ind transmit        | ACKDT data          | a bit;             |  |  |  |

| 0                                                           |                                                                                                                  | wledge sequ                   | •                        | ale                            |                     |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | ceive Enable                  |                          | mode only)(2                   | 2)                  |                     |                     |                    |  |  |  |

|                                                             | = Enable<br>= Receive                                                                                            | s Receive m<br>e Idle         | ode for I <sup>2</sup> C |                                |                     |                     |                     |                    |  |  |  |

| Ρ                                                           | EN: Stop                                                                                                         | Condition Er                  | nable bit (Ma            | aster mode o                   | nly) <sup>(2)</sup> |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | Stop condition Idle           | on on SDA a              | and SCL pins                   | ; automatica        | ally cleared I      | oy hardware         |                    |  |  |  |

| R                                                           | SEN: Rep                                                                                                         | peated Start                  | Condition E              | nable bit (Ma                  | ster mode o         | nly) <sup>(2)</sup> |                     |                    |  |  |  |

|                                                             |                                                                                                                  | Repeated S ted Start cor      |                          | n on SDA an                    | d SCL pins;         | automatical         | ly cleared by       | hardware.          |  |  |  |

| S                                                           | EN: Start                                                                                                        | Condition Er                  | nable/Stretcl            | h Enable bit <sup>(</sup>      | 2)                  |                     |                     |                    |  |  |  |

|                                                             | <u>Master n</u>                                                                                                  |                               |                          |                                |                     |                     | <b>.</b>            |                    |  |  |  |

|                                                             |                                                                                                                  | Start condition Idle          | on on SDA a              | and SCL pins                   | ; automatica        | ally cleared        | by hardware         |                    |  |  |  |

|                                                             | Slave mo                                                                                                         |                               |                          |                                |                     |                     |                     |                    |  |  |  |

|                                                             |                                                                                                                  | stretching is e               |                          | ooth slave tra                 | ansmit and s        | lave receive        | e (stretch ena      | abled)             |  |  |  |

| :                                                           | Value that a receive                                                                                             | at will be tran               | smitted whe              | n the user in                  | itiates an Ac       | knowledge           | sequence at         | the end of         |  |  |  |

| 2:                                                          | If the I <sup>2</sup> C                                                                                          | module is n                   |                          | ode, this bit m<br>le SSPBUF a |                     |                     | ing) and the        | SSPBUF             |  |  |  |

### REGISTER 17-5: SSPCON2: MSSP CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> MODE)

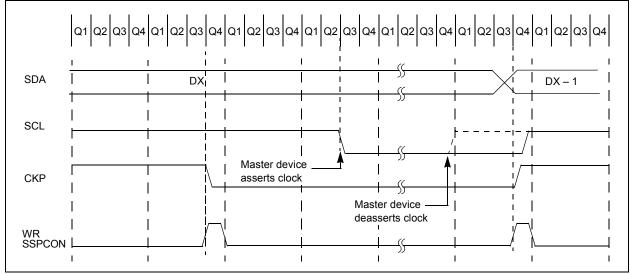

## 17.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has

already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2$ C bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 17-12).

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | _                     |                               |                             |                       |            |                             | _                     |            | _                           |                       |            | _                           |  |  |

| 1.2          | —                     | _                             | _                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16      | 103                         |  |  |

| 2.4          | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16      | 51                          |  |  |

| 9.6          | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16      | 12                          |  |  |

| 19.2         | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _          | _                           |  |  |

| 57.6         | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | _                     | _          | _                           |  |  |

| 115.2        | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | _                     | _          | _                           |  |  |

#### TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODES

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD        | Fos                   | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |  |  |  |

| 1.2         | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |  |  |  |

| 2.4         | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |

| 9.6         | 8.929                 | -6.99                         | 6                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 19.2        | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |

| 57.6        | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |

| 115.2       | 62.500                | -45.75                        | 0                           | _                     | —          | _                           |                       | —          |                             |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | —                     | _                             | _                           | —                     | _          | _                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 1.2          | —                     | —                             | —                           | —                     | —          | —                           | —                     | —          | —                           | —                     | —          | —                           |  |

| 2.4          | —                     | _                             | _                           | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |  |

| 9.6          | 9.766                 | 1.73                          | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |

| 19.2         | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |

| 57.6         | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |

| 115.2        | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | _                     | —          | —                           |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Foso                  | = 4.000                       | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | _                     |                               | _                           | _                     | _          | _                           | 0.300                 | -0.16      | 207                         |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           | _                     | _          | —                           | _                     | —          | —                           |  |  |  |  |

### 18.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CK1 pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 18.4.1 EUSART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG1 and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREG1 register.

- c) Flag bit, TX1IF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREG1 register will transfer the second word to the TSR and flag bit, TX1IF, will now be set.

- e) If enable bit, TX1IE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXIE.

- 4. If the signal from the CKx pin is to be inverted, set the TXCKP bit.

- 5. If 9-bit transmission is desired, set bit, TX9.

- 6. Enable the transmission by setting enable bit, TXEN.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 8. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7    | Bit 6                                         | Bit 5       | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|----------|-----------------------------------------------|-------------|--------------|-------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL                                     | TMR0IE      | INT0IE       | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR1     | PSPIF    | ADIF                                          | RC1IF       | TX1IF        | SSPIF | CCP1IF | TMR2IF | TMR1IF | 65                         |

| PIE1     | PSPIE    | ADIE                                          | RC1IE       | TX1IE        | SSPIE | CCP1IE | TMR2IE | TMR1IE | 65                         |

| IPR1     | PSPIP    | ADIP                                          | RC1IP       | TX1IP        | SSPIP | CCP1IP | TMR2IP | TMR1IP | 65                         |

| RCSTA1   | SPEN     | RX9                                           | SREN        | CREN         | ADDEN | FERR   | OERR   | RX9D   | 65                         |

| TXREG1   | EUSART1  | Transmit Reg                                  | gister      |              |       |        |        |        | 65                         |

| TXSTA1   | CSRC     | TX9                                           | TXEN        | SYNC         | SENDB | BRGH   | TRMT   | TX9D   | 65                         |

| BAUDCON1 | ABDOVF   | RCIDL                                         | RXDTP       | TXCKP        | BRG16 | _      | WUE    | ABDEN  | 66                         |

| SPBRGH1  | EUSART1  | Baud Rate G                                   | enerator Re | egister High | Byte  |        |        |        | 66                         |

| SPBRG1   | EUSART1  | EUSART1 Baud Rate Generator Register Low Byte |             |              |       |        |        |        | 65                         |

#### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

| REGISTER 20-2: ADCONT: A/D CONTROL REGISTER I | REGISTER 20-2: | ADCON1: A/D CONTROL REGISTER 1 |

|-----------------------------------------------|----------------|--------------------------------|

|-----------------------------------------------|----------------|--------------------------------|

| U-0           | U-0                                                                                      | R/      | W-0        | R/       | W-0     | R        | /W-q      |         | R/W-q     |         | R/W-     | -q     | R/  | W-q |

|---------------|------------------------------------------------------------------------------------------|---------|------------|----------|---------|----------|-----------|---------|-----------|---------|----------|--------|-----|-----|

| _             | —                                                                                        | VC      | FG1        | VC       | FG0     | PC       | FG3       | F       | PCFG2     |         | PCFC     | G1     | PC  | FG0 |

| bit 7         |                                                                                          |         |            |          |         |          |           |         |           |         |          |        |     | bit |

| Legend:       |                                                                                          |         |            |          |         |          |           |         |           |         |          |        |     |     |

| R = Readabl   | e bit                                                                                    | W = V   | Vritable   | bit      |         | U = L    | Jnimple   | emente  | ed bit, r | read as | s 'O'    |        |     |     |

| -n = Value at | POR                                                                                      | '1' = E | Bit is set | t        |         | ·0' =    | Bit is cl | eared   |           | х       | = Bit is | s unkn | own |     |

| bit 7-6       | Unimplemen                                                                               | ted: Re | ead as '   | 0'       |         |          |           |         |           |         |          |        |     |     |

| bit 5         | Unimplemented: Read as '0'<br>VCFG1: Voltage Reference Configuration bit (VREF- source): |         |            |          |         |          |           |         |           |         |          |        |     |     |

|               | 1 = VREF- (AN2)                                                                          |         |            |          |         |          |           |         |           |         |          |        |     |     |

|               | 0 = AVss                                                                                 |         |            |          |         |          |           |         |           |         |          |        |     |     |

| bit 4         | VCFG0: Volta                                                                             | ige Ref | erence     | Config   | uration | bit (VF  | REF+ SC   | ource): |           |         |          |        |     |     |

|               | 1 = VREF+ (A                                                                             | -       |            | 5        |         | Ň        |           | ,       |           |         |          |        |     |     |

|               | 0 = AVDD                                                                                 | ,       |            |          |         |          |           |         |           |         |          |        |     |     |

| bit 3-0       | PCFG<3:0>:                                                                               | A/D Po  | rt Confi   | iguratic | on Cont | rol bits | :         |         |           |         |          |        |     |     |

|               | PCFG<3:0>                                                                                | AN11    | AN10       | AN9      | AN8     | AN7      | AN6       | AN5     | AN4       | AN3     | AN2      | AN1    | ANO |     |

|               | 0000                                                                                     | A       | А          | A        | A       | A        | Α         | А       | A         | Α       | Α        | А      | А   |     |

|               | 0001                                                                                     | Α       | Α          | Α        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0010                                                                                     | А       | Α          | Α        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0011                                                                                     | А       | Α          | Α        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0100                                                                                     | D       | Α          | Α        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0101                                                                                     | D       | D          | Α        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0110                                                                                     | D       | D          | D        | Α       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 0111                                                                                     | D       | D          | D        | D       | Α        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 1000                                                                                     | D       | D          | D        | D       | D        | Α         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 1001                                                                                     | D       | D          | D        | D       | D        | D         | Α       | Α         | Α       | Α        | Α      | Α   |     |

|               | 1010                                                                                     | D       | D          | D        | D       | D        | D         | D       | Α         | Α       | Α        | Α      | Α   |     |

|               | 1011                                                                                     | D       | D          | D        | D       | D        | D         | D       | D         | Α       | Α        | Α      | Α   |     |

|               | 1100                                                                                     | D       | D          | D        | D       | D        | D         | D       | D         | D       | Α        | А      | Α   |     |

|               | 1101                                                                                     | D       | D          | D        | D       | D        | D         | D       | D         | D       | D        | Α      | Α   |     |

|               | 1110                                                                                     | D       | D          | D        | D       | D        | D         | D       | D         | D       | D        | D      | Α   |     |

|               | -                                                                                        |         |            |          |         |          |           |         |           |         |          |        |     |     |

|               | 1111                                                                                     | D       | D          | D        | D       | D        | D         | D       | D         | D       | D        | D      | D   |     |

| BR          | 4                                                                                                                                                                                                                    | Uncondit            | ional Branch        | ı               | BSF                        |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|-----------------|----------------------------|--|

| Synt        | ax:                                                                                                                                                                                                                  | BRA n               |                     |                 | Syntax:                    |  |

| Ope         | rands:                                                                                                                                                                                                               | -1024 ≤ n ≤         | 1023                |                 | Operands:                  |  |

| Ope         | ration:                                                                                                                                                                                                              | (PC) + 2 + 2        | $2n \rightarrow PC$ |                 |                            |  |

| Statu       | us Affected:                                                                                                                                                                                                         | None                |                     |                 | Operation                  |  |

| Enco        | oding:                                                                                                                                                                                                               | 1101                | 0nnn nnr            | in nnnn         | Operation:<br>Status Affeo |  |

| Deso        | Description:       Add the 2's complement number '2n' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a two-cycle instruction. |                     |                     |                 |                            |  |

| Wor         | ds:                                                                                                                                                                                                                  | 1                   |                     |                 |                            |  |

| Cycl        | es:                                                                                                                                                                                                                  | 2                   |                     |                 |                            |  |

| QC          | Cycle Activity:                                                                                                                                                                                                      |                     |                     |                 |                            |  |

|             | Q1                                                                                                                                                                                                                   | Q2                  | Q3                  | Q4              |                            |  |

|             | Decode                                                                                                                                                                                                               | Read literal<br>'n' | Process<br>Data     | Write to<br>PC  | Words:<br>Cycles:          |  |

|             | No<br>operation                                                                                                                                                                                                      | No<br>operation     | No<br>operation     | No<br>operation | Q Cycle Ad                 |  |

| <u>Exar</u> | <u>mple:</u>                                                                                                                                                                                                         | HERE                | BRA Jump            |                 | Dec                        |  |

|             | Before Instruct<br>PC<br>After Instruction<br>PC                                                                                                                                                                     | = ad                | dress (HERE)        |                 | <u>Example:</u><br>Before  |  |

|             | PG                                                                                                                                                                                                                   | = ad                | dress (Jump)        | )               | F<br>After li              |  |

| BSF                                                                         | Bit Set f                                                                                                                                                                                                                                                                                                                                           |                 |                       |  |  |  |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--|--|--|

| Syntax:                                                                     | BSF f, b {                                                                                                                                                                                                                                                                                                                                          | ,a}             |                       |  |  |  |

| Operands:                                                                   | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                  |                 |                       |  |  |  |

| Operation:                                                                  | $1 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                           |                 |                       |  |  |  |

| Status Affected:                                                            | None                                                                                                                                                                                                                                                                                                                                                |                 |                       |  |  |  |

| Encoding:                                                                   | 1000                                                                                                                                                                                                                                                                                                                                                | bbba ff:        | ff ffff               |  |  |  |

| Description:                                                                | tion: Bit 'b' in register 'f' is set.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select th<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 25.2.3 for details. |                 |                       |  |  |  |

| Words:                                                                      | 1                                                                                                                                                                                                                                                                                                                                                   |                 |                       |  |  |  |

| Cycles:                                                                     | 1                                                                                                                                                                                                                                                                                                                                                   |                 |                       |  |  |  |

| Q Cycle Activity:                                                           |                                                                                                                                                                                                                                                                                                                                                     |                 |                       |  |  |  |

| Q1                                                                          | Q2                                                                                                                                                                                                                                                                                                                                                  | Q3              | Q4                    |  |  |  |

| Decode                                                                      | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                | Process<br>Data | Write<br>register 'f' |  |  |  |

| Example:                                                                    | BSF F                                                                                                                                                                                                                                                                                                                                               | LAG_REG, 7      | , 1                   |  |  |  |

| Before Instruction<br>FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah |                                                                                                                                                                                                                                                                                                                                                     |                 |                       |  |  |  |

| GOTO                                                | Uncondit                                                                                          | ional Branc                                                                          | h                                         | INC          | F                                                                             | Incremen                                                                                       | tf                                                                                                                     |                                        |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|--------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| Syntax:                                             | GOTO k                                                                                            |                                                                                      |                                           | Synt         | ax:                                                                           | INCF f{,c                                                                                      | 1 {,a}}                                                                                                                |                                        |  |

| Operands:                                           | $0 \le k \le 104$                                                                                 | 8575                                                                                 |                                           | Oper         | rands:                                                                        | $0 \leq f \leq 255$                                                                            |                                                                                                                        |                                        |  |