Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

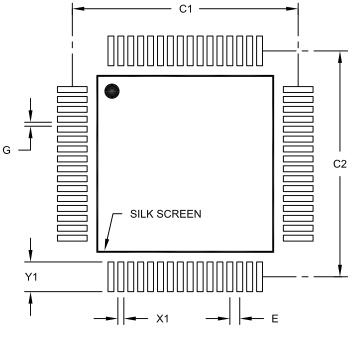

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8310t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: DEVICE FEATURES      |                                                                                                              |                                                                                                              |                                                                                                              |                                                                                                              |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Features                        | PIC18F6310                                                                                                   | PIC18F6410                                                                                                   | PIC18F8310                                                                                                   | PIC18F8410                                                                                                   |  |  |

| Operating Frequency             | DC – 40 MHz                                                                                                  |  |  |

| Program Memory (Bytes)          | 8K                                                                                                           | 16K                                                                                                          | 8K                                                                                                           | 16K                                                                                                          |  |  |

| Program Memory (Instructions)   | 4096                                                                                                         | 8192                                                                                                         | 4096                                                                                                         | 8192                                                                                                         |  |  |

| Data Memory (Bytes)             | 768                                                                                                          | 768                                                                                                          | 768                                                                                                          | 768                                                                                                          |  |  |

| External Memory Interface       | No                                                                                                           | No                                                                                                           | Yes                                                                                                          | Yes                                                                                                          |  |  |

| Interrupt Sources               | 22                                                                                                           | 22                                                                                                           | 22                                                                                                           | 22                                                                                                           |  |  |

| I/O Ports                       | Ports A, B, C, D, E,<br>F, G                                                                                 | Ports A, B, C, D, E,<br>F, G                                                                                 | Ports A, B, C, D, E,<br>F, G, H, J                                                                           | Ports A, B, C, D, E,<br>F, G, H, J                                                                           |  |  |

| Timers                          | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            |  |  |

| Capture/Compare/PWM Modules     | 3                                                                                                            | 3                                                                                                            | 3                                                                                                            | 3                                                                                                            |  |  |

| Serial Communications           | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               |  |  |

| Parallel Communications         | PSP                                                                                                          | PSP                                                                                                          | PSP                                                                                                          | PSP                                                                                                          |  |  |

| 10-Bit Analog-to-Digital Module | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            |  |  |

| Resets (and Delays)             | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR (optional),<br>WDT |  |  |

| Programmable Low-Voltage Detect | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |  |  |

| Programmable Brown-out Reset    | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |  |  |

| Instruction Set                 | 75 Instructions;<br>83 with Extended<br>Instruction Set<br>enabled                                           |  |  |

| Packages                        | 64-Pin TQFP                                                                                                  | 64-Pin TQFP                                                                                                  | 80-Pin TQFP                                                                                                  | 80-Pin TQFP                                                                                                  |  |  |

## TABLE 1-1: DEVICE FEATURES

| Pin Name                               | Pin Number | Pin           | Buffer                 | Description                                                                                                                                                            |

|----------------------------------------|------------|---------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре          | Туре                   | Description                                                                                                                                                            |

|                                        |            |               |                        | PORTF is a bidirectional I/O port.                                                                                                                                     |

| RF0/AN5<br>RF0<br>AN5                  | 18         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 5.                                                                                                                                        |

| RF1/AN6/C2OUT<br>RF1<br>AN6<br>C2OUT   | 17         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.                                                                                                                |

| RF2/AN7/C1OUT<br>RF2<br>AN7<br>C1OUT   | 16         | I/O<br>I<br>O | ST<br>Analog<br>—      | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.                                                                                                                |

| RF3/AN8<br>RF3<br>AN8                  | 15         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 8.                                                                                                                                        |

| RF4/AN9<br>RF4<br>AN9                  | 14         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 9.                                                                                                                                        |

| RF5/AN10/CVREF<br>RF5<br>AN10<br>CVREF | 13         | I/O<br>I<br>O | ST<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.                                                                                               |

| RF6/AN11<br>RF6<br>AN11                | 12         | I/O<br>I      | ST<br>Analog           | Digital I/O.<br>Analog Input 11.                                                                                                                                       |

| RF7/SS<br>RF7<br>SS                    | 11         | I/O<br>I      | ST<br>TTL              | Digital I/O.<br>SPI slave select input.                                                                                                                                |

| ST = Schr<br>I = Inpu<br>P = Pow       | er         | t with CN     |                        | CMOS = CMOS compatible input or output<br>s Analog = Analog input<br>O = Output<br>I <sup>2</sup> C = ST with I <sup>2</sup> C™ or SMB levels<br>ion bit CCP2MX is set |

### TABLE 1-2: PIC18F6310/6410 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

## TABLE 3-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |  |

|----------|-----------------|-------------------------------------|-------|--|--|

|          | Fieq            | C1                                  | C2    |  |  |

| LP       | 32 kHz          | 33 pF                               | 33 pF |  |  |

|          | 200 kHz         | 15 pF                               | 15 pF |  |  |

| XT       | 1 MHz           | 33 pF                               | 33 pF |  |  |

|          | 4 MHz           | 27 pF                               | 27 pF |  |  |

| HS       | 4 MHz           | 27 pF                               | 27 pF |  |  |

|          | 8 MHz           | 22 pF                               | 22 pF |  |  |

|          | 20 MHz          | 15 pF                               | 15 pF |  |  |

#### Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |        |  |  |  |

|----------------|--------|--|--|--|

| 32 kHz         | 4 MHz  |  |  |  |

| 200 kHz        | 8 MHz  |  |  |  |

| 1 MHz          | 20 MHz |  |  |  |

- Note 1: Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use the HS mode or switch to a crystal oscillator.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required to avoid overdriving crystals with low drive level specification.

- **5:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

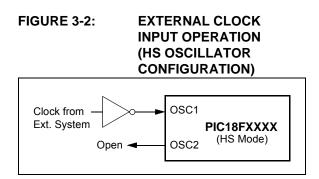

An external clock source may also be connected to the OSC1 pin in the HS mode, as shown in Figure 3-2.

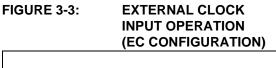

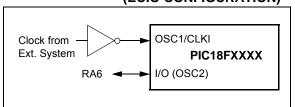

## 3.3 External Clock Input

The EC and ECIO Oscillator modes require an external clock source to be connected to the OSC1 pin. There is no oscillator start-up time required after a Power-on Reset or after an exit from Sleep mode.

In the EC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-3 shows the pin connections for the EC Oscillator mode.

The ECIO Oscillator mode functions like the EC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6). Figure 3-4 shows the pin connections for the ECIO Oscillator mode.

#### EXTERNAL CLOCK INPUT OPERATION (ECIO CONFIGURATION)

| Register |      | Applicable Power-on Reset,<br>Devices Brown-out Reset |           | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|------|-------------------------------------------------------|-----------|---------------------------------------------------------------|---------------------------------|--|

| TOSU     | 6X10 | 8X10                                                  | 0 0000    | 0 0000                                                        | 0 uuuu <b>(3)</b>               |  |

| TOSH     | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu <b>(3)</b>            |  |

| TOSL     | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu <sup>(3)</sup>        |  |

| STKPTR   | 6X10 | 8X10                                                  | uu-0 0000 | 00-0 0000                                                     | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 6X10 | 8X10                                                  | 0 0000    | 0 0000                                                        | u uuuu                          |  |

| PCLATH   | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu                       |  |

| PCL      | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 6X10 | 8X10                                                  | 00 0000   | 00 0000                                                       | uu uuuu                         |  |

| TBLPTRH  | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu                       |  |

| TBLPTRL  | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu                       |  |

| TABLAT   | 6X10 | 8X10                                                  | 0000 0000 | 0000 0000                                                     | uuuu uuuu                       |  |

| PRODH    | 6X10 | 8X10                                                  | XXXX XXXX | uuuu uuuu                                                     | uuuu uuuu                       |  |

| PRODL    | 6X10 | 8X10                                                  | XXXX XXXX | uuuu uuuu                                                     | uuuu uuuu                       |  |

| INTCON   | 6X10 | 8X10                                                  | 0000 000x | 0000 000u                                                     | սսսս սսսս <b>(1)</b>            |  |

| INTCON2  | 6X10 | 8X10                                                  | 1111 1111 | 1111 1111                                                     | սսսս սսսս <b>(1)</b>            |  |

| INTCON3  | 6X10 | 8X10                                                  | 1100 0000 | 1100 0000                                                     | uuuu uuuu <b>(1)</b>            |  |

| INDF0    | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| POSTINC0 | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| POSTDEC0 | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| PREINC0  | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| PLUSW0   | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| FSR0H    | 6X10 | 8X10                                                  | xxxx      | uuuu                                                          | uuuu                            |  |

| FSR0L    | 6X10 | 8X10                                                  | XXXX XXXX | uuuu uuuu                                                     | uuuu uuuu                       |  |

| WREG     | 6X10 | 8X10                                                  | XXXX XXXX | uuuu uuuu                                                     | uuuu uuuu                       |  |

| INDF1    | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| POSTINC1 | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| POSTDEC1 | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| PREINC1  | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| PLUSW1   | 6X10 | 8X10                                                  | N/A       | N/A                                                           | N/A                             |  |

| FSR1H    | 6X10 | 8X10                                                  | xxxx      | uuuu                                                          | uuuu                            |  |

| FSR1L    | 6X10 | 8X10                                                  | XXXX XXXX | uuuu uuuu                                                     | uuuu uuuu                       |  |

| BSR      | 6X10 | 8X10                                                  | 0000      | 0000                                                          | uuuu                            |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 5-3 for Reset value for specific condition.

**5:** Bits, 6 and 7 of PORTA, LATA and TRISA, are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

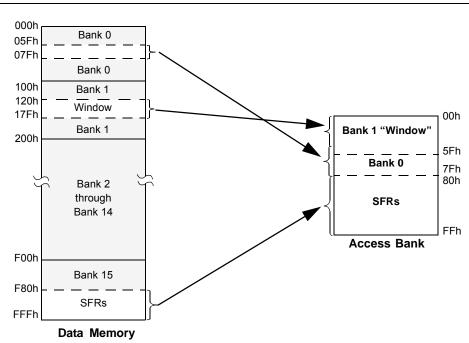

### 6.5.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped into the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see **Section 6.3.2 "Access Bank"**). An example of Access Bank remapping in this addressing mode is shown in Figure 6-10.

Remapping of the Access Bank applies *only* to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before.

## 6.6 PIC18 Instruction Execution and the Extended Instruction Set

Enabling the extended instruction set adds eight additional commands to the existing PIC18 instruction set. These instructions are executed as described in **Section 25.2 "Extended Instruction Set**".

## FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

### Example Situation:

ADDWF f, d, a FSR2H:FSR2L = 120h

Locations in the region from the FSR2 Pointer (120h) to the pointer plus 05Fh (17Fh) are mapped to the bottom of the Access RAM (000h-05Fh).

Locations in Bank 0 from 060h to 07Fh are mapped, as usual, to the middle of the Access Bank.

Special Function Registers at F80h through FFFh are mapped to 80h through FFh, as usual.

Bank 0 addresses below 5Fh can still be addressed by using the BSR.

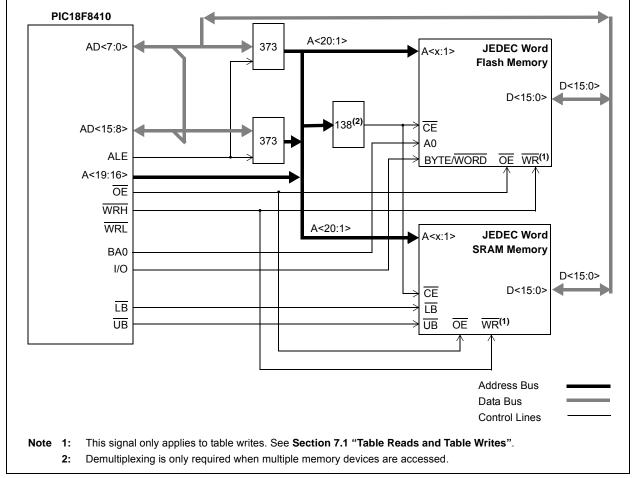

#### 8.2.3 16-BIT BYTE SELECT MODE

Figure 8-3 shows an example of 16-Bit Byte Select mode. This mode allows table write operations to word-wide external memories with byte selection capability. This generally includes both word-wide Flash and SRAM devices.

During a TBLWT cycle, the TABLAT data is presented on the upper and lower byte of the AD<15:0> bus. The WRH signal is strobed for each write cycle; the WRL pin is not used. The BA0 or UB/LB signals are used to select the byte to be written, based on the Least Significant bit of the TBLPTR register. Flash and SRAM devices use different control signal combinations to implement Byte Select mode. JEDEC standard Flash memories require that a controller I/O port pin be connected to the memory's BYTE/WORD pin to provide the select signal. They also use the BA0 signal from the controller as a byte address. JEDEC standard static RAM memories, on the other hand, use the UB or LB signals to select the byte.

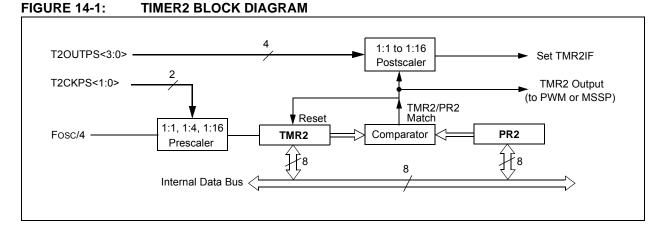

### 14.2 Timer2 Interrupt

Timer2 also can generate an optional device interrupt. The Timer2 output signal (TMR2-to-PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

### 14.3 TMR2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 17.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                  | Bit 6                                       | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|--------|------------------------|---------------------------------------------|----------|----------|----------|--------|---------|---------|----------------------------|

| INTCON | GIE/GIEH               | PEIE/GIEL                                   | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 63                         |

| PIR1   | PSPIF                  | ADIF                                        | RC1IF    | TX1IF    | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 65                         |

| PIE1   | PSPIE                  | ADIE                                        | RC1IE    | TX1IE    | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 65                         |

| IPR1   | PSPIP                  | ADIP RC1IP TX1IP SSPIP CCP1IP TMR2IP TMR1IP |          |          |          |        | 65      |         |                            |

| TMR2   | Timer2 Register        |                                             |          |          |          |        |         | 64      |                            |

| T2CON  | _                      | T2OUTPS3                                    | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 64                         |

| PR2    | Timer2 Period Register |                                             |          |          |          |        |         |         | 64                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

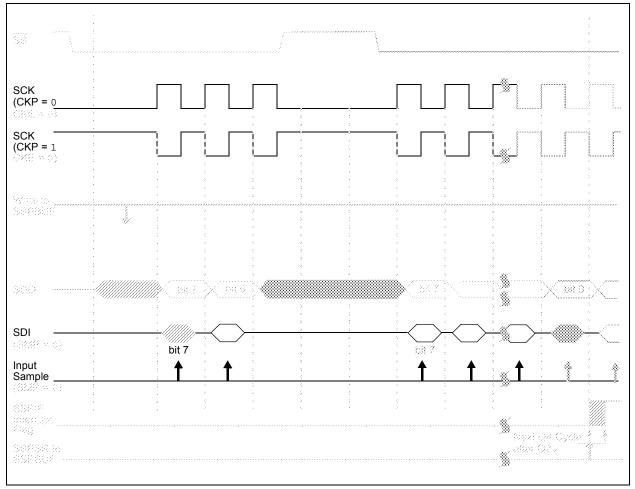

#### 17.3.6 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched, the SSPIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device will wake-up from Sleep.

#### 17.3.7 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON1<3:0> = 04h). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. The data latch must be high. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the SDO pin is no longer driven,

even if in the middle of a transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

- Note 1: When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

- 2: If the SPI is used in Slave mode with CKE set, then the SS pin control must be enabled

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver, the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

FIGURE 17-4: SLAVE SYNCHRONIZATION WAVEFORM

### 18.1.3 AUTO-BAUD RATE DETECT

The Enhanced USART module supports the automatic detection and calibration of baud rate. This feature is active only in Asynchronous mode and while the WUE bit is clear.

The automatic baud rate measurement sequence (Figure 18-1) begins whenever a Start bit is received and the ABDEN bit is set. The calculation is self-averaging.

In the Auto-Baud Rate Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX1 signal, the RX1 signal is timing the BRG. In ABD mode, the internal Baud Rate Generator is used as a counter to time the bit period of the incoming serial byte stream.

Once the ABDEN bit is set, the state machine will clear the BRG and look for a Start bit. The Auto-Baud Rate Detect must receive a byte with the value, 55h (ASCII "U", which is also the LIN/J2602 bus Sync character), in order to calculate the proper bit rate. The measurement is taken over both a low and a high bit time in order to minimize any effects caused by asymmetry of the incoming signal. After a Start bit, the SPBRG1 begins counting up, using the preselected clock source on the first rising edge of RX1. After eight bits on the RX1 pin or the fifth rising edge, an accumulated value totalling the proper BRG period is left in the SPBRGH1:SPBRG1 register pair. Once the 5th edge is seen (this should correspond to the Stop bit), the ABDEN bit is automatically cleared.

If a rollover of the BRG occurs (an overflow from FFFh to 0000h), the event is trapped by the ABDOVF status bit (BAUDCON1<7>). It is set in hardware by BRG rollovers and can be set or cleared by the user in software. ABD mode remains active after rollover events and the ABDEN bit remains set (Figure 18-2).

While calibrating the baud rate period, the BRG registers are clocked at 1/8th the preconfigured clock rate. Note that the BRG clock can be configured by the BRG16 and BRGH bits. The BRG16 bit must be set to use both SPBRG1 and SPBRGH1 as a 16-bit counter. This allows the user to verify that no carry occurred for 8-bit modes by checking for 00h in the SPBRGH1 register. Refer to Table 18-4 for counter clock rates to the BRG.

While the ABD sequence takes place, the EUSART state machine is held in Idle. The RC1IF interrupt is set once the fifth rising edge on RX1 is detected. The value in the RCREG1 needs to be read to clear the RC1IF interrupt. The contents of RCREG1 should be discarded.

- Note 1: If the WUE bit is set with the ABDEN bit, Auto-Baud Rate Detection will occur on the byte *following* the Break character.

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible due to bit error rates. Overall system timing and communication baud rates must be taken into consideration when using the Auto-Baud Rate Detection feature.

- **3:** To maximize baud rate range, it is recommended to set the BRG16 bit if the auto-baud feature is used.

#### TABLE 18-4: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Counter Clock |

|-------|------|-------------------|

| 0     | 0    | Fosc/512          |

| 0     | 1    | Fosc/128          |

| 1     | 0    | Fosc/128          |

| 1     | 1    | Fosc/32           |

### 18.1.3.1 ABD and EUSART Transmission

Since the BRG clock is reversed during ABD acquisition, the EUSART transmitter cannot be used during ABD. This means that whenever the ABDEN bit is set, TXREG1 cannot be written to. Users should also ensure that ABDEN does not become set during a transmit sequence. Failing to do this may result in unpredictable EUSART operation.

| Name     | Bit 7                                                | Bit 6     | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|------------------------------------------------------|-----------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                             | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR1     | PSPIF                                                | ADIF      | RC1IF  | TX1IF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 65                         |

| PIE1     | PSPIE                                                | ADIE      | RC1IE  | TX1IE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 65                         |

| IPR1     | PSPIP                                                | ADIP      | RC1IP  | TX1IP  | SSPIP | CCP1IP | TMR2IP | TMR1IP | 65                         |

| RCSTA1   | SPEN                                                 | RX9       | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 65                         |

| TXREG1   | EUSART1 Transmit Register                            |           |        |        |       |        | 65     |        |                            |

| TXSTA1   | CSRC                                                 | TX9       | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 65                         |

| BAUDCON1 | ABDOVF                                               | RCIDL     | RXDTP  | TXCKP  | BRG16 | —      | WUE    | ABDEN  | 66                         |

| SPBRGH1  | BRGH1 EUSART1 Baud Rate Generator Register High Byte |           |        |        |       |        |        | 66     |                            |

| SPBRG1   | SPBRG1 EUSART1 Baud Rate Generator Register Low Byte |           |        |        |       |        |        | 65     |                            |

#### TABLE 18-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

#### 18.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up, due to activity on the RX1/DT1 line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX1/DT1 is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX1/DT1 line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN/J2602 protocol.)

Following a wake-up event, the module generates an RC1IF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 18-8) and asynchronously, if the device is in Sleep mode (Figure 18-9). The interrupt condition is cleared by reading the RCREG1 register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RX1 line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 18.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX1/DT1, information with any state changes before the Stop bit may signal a false End-of-Character (EOC) and cause data or framing errors. Therefore, to work properly, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices, or 000h (12 bits) for the LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 18.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RC1IF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RC1IF bit. The WUE bit is cleared after this when a rising edge is seen on RX1/DT1. The interrupt condition is then cleared by reading the RCREG1 register. Ordinarily, the data in RCREG1 will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RC1IF flag is set should not be used as an indicator of the integrity of the data in RCREG1. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

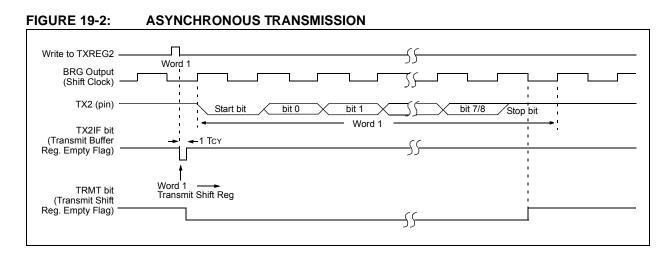

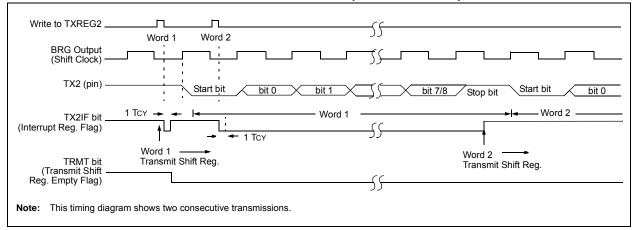

### FIGURE 19-3: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 19-4: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                     | Bit 6       | Bit 5       | Bit 4    | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|--------|---------------------------|-------------|-------------|----------|-------|--------|--------|--------|----------------------------|

| INTCON | GIE/GIEH                  | PEIE/GIEL   | TMR0IE      | INT0IE   | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR3   |                           | —           | RC2IF       | TX2IF    | —     | —      | _      | CCP3IF | 65                         |

| PIE3   | —                         | —           | RC2IE       | TX2IE    | —     | —      | _      | CCP3IE | 65                         |

| IPR3   |                           | —           | RC2IP       | TX2IP    | —     | —      | _      | CCP3IP | 65                         |

| RCSTA2 | SPEN                      | RX9         | SREN        | CREN     | ADDEN | FERR   | OERR   | RX9D   | 66                         |

| TXREG2 | AUSART2 Transmit Register |             |             |          |       |        | 66     |        |                            |

| TXSTA2 | CSRC                      | TX9         | TXEN        | SYNC     | _     | BRGH   | TRMT   | TX9D   | 66                         |

| SPBRG2 | AUSART2                   | Baud Rate ( | Generator R | legister |       |        |        |        | 66                         |

**Legend:** — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous transmission.

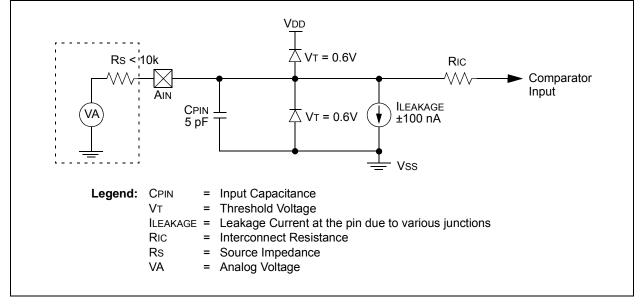

### 21.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

| TABLE 21-1: | <b>REGISTERS ASSOCIATED WITH COMPARATOR MODULE</b> |

|-------------|----------------------------------------------------|

|-------------|----------------------------------------------------|

| Name   | Bit 7      | Bit 6         | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|--------|------------|---------------|----------|--------|-------|--------|--------|--------|----------------------------|

| CMCON  | C2OUT      | C1OUT         | C2INV    | C1INV  | CIS   | CM2    | CM1    | CM0    | 65                         |

| CVRCON | CVREN      | CVROE         | CVRR     | CVRSS  | CVR3  | CVR2   | CVR1   | CVR0   | 65                         |

| INTCON | GIE/GIEH   | PEIE/GIEL     | TMR0IE   | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR2   | OSCFIF     | CMIF          |          | _      | BCLIF | HLVDIF | TMR3IF | CCP2IF | 65                         |

| PIE2   | OCSFIE     | CMIE          | _        | _      | BCLIE | HLVDIE | TMR3IE | CCP2IE | 65                         |

| IPR2   | OSCFIP     | CMIP          | _        | _      | BCLIP | HLVDIP | TMR3IP | CCP2IP | 65                         |

| PORTF  | RF7        | RF6           | RF5      | RF4    | RF3   | RF2    | RF1    | RF0    | 66                         |

| LATF   | LATF Outpu | ut Latch Regi | ster     |        |       |        |        |        | 66                         |

| TRISF  | PORTF Dat  | a Direction F | Register |        |       |        |        |        | 66                         |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

# 24.0 SPECIAL FEATURES OF THE CPU

PIC18F6310/6410/8310/8410 devices include several features intended to maximize reliability and minimize cost through elimination of external components. These are:

- Oscillator Selection

- Resets:

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor

- · Two-Speed Start-up

- Code Protection

- · ID Locations

- In-Circuit Serial Programming (ICSP)

The oscillator can be configured for the application depending on frequency, power, accuracy and cost. All of the options are discussed in detail in **Section 3.0 "Oscillator Configurations"**.

A complete discussion of device Resets and interrupts is available in previous sections of this data sheet.

In addition to their Power-up and Oscillator Start-up Timers provided for Resets, PIC18F6310/6410/8310/8410 devices have a Watchdog Timer, which is either permanently enabled via the Configuration bits, or software controlled (if configured as disabled).

The inclusion of an internal RC oscillator also provides the additional benefits of a Fail-Safe Clock Monitor (FSCM) and Two-Speed Start-up. FSCM provides for background monitoring of the peripheral clock and automatic switchover in the event of its failure. Two-Speed Start-up enables code to be executed almost immediately on start-up, while the primary clock source completes its start-up delays.

All of these features are enabled and configured by setting the appropriate Configuration register bits.

### 24.1 Configuration Bits

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped, starting at program memory location, 300000h.

The user will note that address, 300000h, is beyond the user program memory space. In fact, it belongs to the configuration memory space (300000h-3FFFFFh), which can only be accessed using table reads.

| File    | e Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2   | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|-------------------------|-------|-------|-------|--------|--------|---------|--------|--------|-----------------------------------|

| 300001h | CONFIG1H                | IESO  | FCMEN |       |        | FOSC3  | FOSC2   | FOSC1  | FOSC0  | 00 0111                           |

| 300002h | CONFIG2L                | _     | _     |       | BORV1  | BORV0  | BOREN1  | BOREN0 | PWRTEN | 1 1111                            |

| 300003h | CONFIG2H                |       | _     |       | WDTPS3 | WDTPS2 | WDTPS1  | WDTPS0 | WDTEN  | 1 1111                            |

| 300004h | CONFIG3L                | WAIT  | BW    |       | —      |        | _       | PM1    | PM0    | 1111                              |

| 300005h | CONFIG3H                | MCLRE | _     |       |        |        | LPT10SC |        | CCP2MX | 10-1                              |

| 300006h | CONFIG4L                | DEBUG | XINST | —     | _      | _      | —       | —      | STVREN | 101                               |

| 300008h | CONFIG5L                | —     | —     | _     | —      | _      | —       |        | CP     | 1                                 |

| 30000Ch | CONFIG7L <sup>(1)</sup> | _     | _     | _     | —      | _      | _       | _      | EBTR   | 1                                 |

| 3FFFFEh | DEVID1                  | DEV2  | DEV1  | DEV0  | REV4   | REV3   | REV2    | REV1   | REV0   | 11qx xxxx(2)                      |

| 3FFFFFh | DEVID2                  | DEV10 | DEV9  | DEV8  | DEV7   | DEV6   | DEV5    | DEV4   | DEV3   | 0000 qqlq <b>(2)</b>              |

#### TABLE 24-1: CONFIGURATION BITS AND DEVICE IDs

$\label{eq:lagend: x = unknown, u = unchanged, - = unimplemented, q = value depends on individual device. Shaded cells are unimplemented, read as '0'.$

**Note 1:** Unimplemented in PIC18F6310/6410 devices; maintain this bit set.

2: See Register 24-9 for DEVID1 values. DEVID registers are read-only and cannot be programmed by the user.

| BR          | 4                                                | Uncondit                                                                                | ional Branch                                | ı               | BSF                       |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------|-----------------|---------------------------|

| Synt        | ax:                                              | BRA n                                                                                   |                                             |                 | Syntax:                   |

| Ope         | rands:                                           | -1024 ≤ n ≤                                                                             | 1023                                        |                 | Operands:                 |

| Ope         | ration:                                          | (PC) + 2 + 2                                                                            | $2n \rightarrow PC$                         |                 |                           |

| Statu       | us Affected:                                     | None                                                                                    |                                             |                 | Operation                 |

| Enco        | oding:                                           | 1101                                                                                    | 0nnn nnr                                    | in nnnn         | Operation:                |

| Deso        | cription:                                        | Add the 2's<br>the PC. Sin<br>incremente<br>instruction,<br>PC + 2 + 2r<br>two-cycle ir | I Status Affect<br>Encoding:<br>Description |                 |                           |

| Wor         | ds:                                              | 1                                                                                       |                                             |                 |                           |

| Cycl        | es:                                              | 2                                                                                       |                                             |                 |                           |

| QC          | Cycle Activity:                                  |                                                                                         |                                             |                 |                           |

|             | Q1                                               | Q2                                                                                      | Q3                                          | Q4              |                           |

|             | Decode                                           | Read literal<br>'n'                                                                     | Process<br>Data                             | Write to<br>PC  | Words:<br>Cycles:         |

|             | No<br>operation                                  | No<br>operation                                                                         | No<br>operation                             | No<br>operation | Q Cycle Ad                |

| <u>Exar</u> | <u>mple:</u>                                     | HERE                                                                                    | BRA Jump                                    |                 | Dec                       |

|             | Before Instruct<br>PC<br>After Instruction<br>PC | = ad                                                                                    | dress (HERE)                                |                 | <u>Example:</u><br>Before |

|             | PG                                               | = ad                                                                                    | dress (Jump)                                | 1               | F<br>After I              |

| BSF                                                                         | Bit Set f                                                                                                         |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Syntax:                                                                     | BSF f, b {                                                                                                        | ,a}                                                                                                                                                                                                                                                                                                                                                  |                       |  |  |  |

| Operands:                                                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                              |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Operation:                                                                  | $1 \rightarrow f \le b >$                                                                                         |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Status Affected:                                                            | None                                                                                                              |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Encoding:                                                                   | 1000                                                                                                              | bbba ff:                                                                                                                                                                                                                                                                                                                                             | ff ffff               |  |  |  |

| Description:                                                                | If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed I<br>mode when | Bit 'b' in register 'f' is set.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 25.2.3 for details. |                       |  |  |  |

| Words:                                                                      | 1                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Cycles:                                                                     | 1                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Q Cycle Activity:                                                           |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| Q1                                                                          | Q2                                                                                                                | Q3                                                                                                                                                                                                                                                                                                                                                   | Q4                    |  |  |  |

| Decode                                                                      | Read<br>register 'f'                                                                                              | Process<br>Data                                                                                                                                                                                                                                                                                                                                      | Write<br>register 'f' |  |  |  |

| Example:                                                                    | BSF F                                                                                                             | LAG_REG, 7                                                                                                                                                                                                                                                                                                                                           | , 1                   |  |  |  |

| Before Instruction<br>FLAG_REG = 0Ah<br>After Instruction<br>FLAG_REG = 8Ah |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                      |                       |  |  |  |

| CLRF                                                              | Clear f                         |                                          |                                    | CLRWDT           | Clear Wat                                   | chdog Tim            | er                                                   |

|-------------------------------------------------------------------|---------------------------------|------------------------------------------|------------------------------------|------------------|---------------------------------------------|----------------------|------------------------------------------------------|

| Syntax:                                                           | CLRF f{,a                       | a}                                       |                                    | Syntax:          | CLRWDT                                      |                      |                                                      |

| Operands:                                                         | $0 \le f \le 255$               |                                          |                                    | Operands:        | None                                        |                      |                                                      |

| Operation:                                                        | a ∈ [0,1]<br>000h → f,<br>1 → Z |                                          |                                    | Operation:       | $1 \rightarrow \overline{\text{TO}}$ ,      | OT,<br>OT postscaler | ,                                                    |

| Status Affected:                                                  | Z                               |                                          |                                    |                  | $1 \rightarrow \overline{PD}$               |                      |                                                      |

| Encoding:                                                         | 0110                            | 101a ff:                                 | ff ffff                            | Status Affected: | TO, PD                                      |                      |                                                      |

| Description:                                                      | Clears the                      | contents of the                          | e specified                        | Encoding:        | 0000                                        | 0000 00              | 00 0100                                              |

|                                                                   | lf 'a' is '1', tl<br>GPR bank.  |                                          | nk is selected.<br>d to select the | Description:     | Watchdog 7                                  | e WDT. Status        | ets the<br>resets <u>the</u> post-<br>s bits, TO and |

|                                                                   |                                 |                                          | ction operates                     | Words:           | 1                                           |                      |                                                      |

|                                                                   |                                 | Literal Offset A                         | •                                  | Cycles:          | 1                                           |                      |                                                      |

|                                                                   |                                 | ever f $\leq$ 95 (5)<br>.2.3 for details | ,                                  | Q Cycle Activity | :                                           |                      |                                                      |

| Manda.                                                            |                                 | .z.3 IOI details                         | j.                                 | Q1               | Q2                                          | Q3                   | Q4                                                   |

| Words:<br>Cycles:                                                 | 1                               |                                          |                                    | Decode           | No<br>operation                             | Process<br>Data      | No<br>operation                                      |

|                                                                   | I                               |                                          |                                    |                  | operation                                   | Bata                 | operation                                            |

| Q Cycle Activity:<br>Q1                                           | Q2                              | Q3                                       | Q4                                 | Example:         | CLRWDT                                      |                      |                                                      |

| Decode                                                            | Read<br>register 'f'            | Process<br>Data                          | Write<br>register 'f'              |                  | Counter =                                   | ?                    |                                                      |

| Example:<br>Before Instruc<br>FLAG_R<br>After Instructi<br>FLAG_R | REG = 5A<br>on                  |                                          | 1                                  |                  | tion<br>Counter =<br>Postscaler =<br>=<br>= | 00h<br>0<br>1<br>1   |                                                      |

| LFS         | R                                                   | Load FS                                                            | R                |                            |                                       |

|-------------|-----------------------------------------------------|--------------------------------------------------------------------|------------------|----------------------------|---------------------------------------|

| Synta       | ax:                                                 | LFSR f,                                                            | k                |                            |                                       |

| Oper        | ands:                                               | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95               |                            |                                       |

| Oper        | ation:                                              | $k \rightarrow FSRf$                                               |                  |                            |                                       |

| Statu       | s Affected:                                         | None                                                               |                  |                            |                                       |

| Enco        | ding:                                               | 1110<br>1111                                                       | 1110<br>0000     | 00ff<br>k <sub>7</sub> kkk | k <sub>11</sub> kkk<br>kkkk           |

| Desc        | ription:                                            | The 12-bit file select                                             |                  |                            |                                       |

| Word        | ls:                                                 | 2                                                                  |                  |                            |                                       |

| Cycle       | es:                                                 | 2                                                                  |                  |                            |                                       |

| QC          | ycle Activity:                                      |                                                                    |                  |                            |                                       |

|             | Q1                                                  | Q2                                                                 | Q3               |                            | Q4                                    |

|             | Decode                                              | Read literal<br>'k' MSB                                            | Proce<br>Data    | a li                       | Write<br>teral 'k'<br>MSB to<br>FSRfH |

|             | Decode                                              | Read literal<br>'k' LSB                                            | Proce<br>Data    |                            | rite literal<br>to FSRfL              |

| <u>Exan</u> | n <u>ple:</u><br>After Instructio<br>FSR2H<br>FSR2L | = 0                                                                | 3ABh<br>3h<br>Bh |                            |                                       |

| MOVF                                         | Move f                                                                                                                                                                          |                                                                                                          |                                                                                                                 |                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Syntax:                                      | MOVF f{                                                                                                                                                                         | ,d {,a}}                                                                                                 |                                                                                                                 |                                                                                     |

| Operands:                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                             |                                                                                                          |                                                                                                                 |                                                                                     |

| Operation:                                   | $f \to \text{dest}$                                                                                                                                                             |                                                                                                          |                                                                                                                 |                                                                                     |

| Status Affected:                             | N, Z                                                                                                                                                                            |                                                                                                          |                                                                                                                 |                                                                                     |

| Encoding:                                    | 0101                                                                                                                                                                            | 00da                                                                                                     | ffff                                                                                                            | ffff                                                                                |

|                                              | a destinatic<br>status of 'd'<br>placed in W<br>placed back<br>can be any<br>If 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank.<br>If 'a' is '0' a<br>set is enabl<br>in Indexed | . If 'd' is<br>/. If 'd' is<br>k in regis<br>where in<br>he Acces<br>he BSR i<br>nd the ex<br>ed, this i | 0', the res<br>'1', the re-<br>ter 'f'. Loc<br>the 256-b<br>ss Bank is<br>s used to<br>ktended in<br>nstruction | sult is<br>sult is<br>ation 'f'<br>yte bank.<br>selected<br>select the<br>struction |

|                                              | mode wher<br>Section 25                                                                                                                                                         | ever f ≤                                                                                                 | 95 (5Fh).                                                                                                       | •                                                                                   |

| Words:                                       | mode wher                                                                                                                                                                       | ever f ≤                                                                                                 | 95 (5Fh).                                                                                                       | •                                                                                   |