Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 70                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

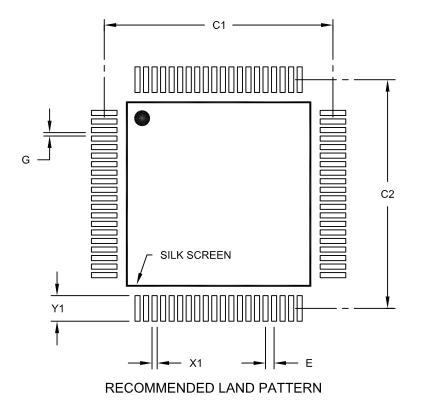

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8410-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F6310 PIC18LF6310

- PIC18F6410 PIC18LF6410

- PIC18F8310 PIC18LF8310

- PIC18F8410 PIC18LF8410

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price. In addition to these features, the PIC18F6310/6410/8310/8410 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power-sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F6310/6410/8310/8410 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled, but the peripherals still active. In these states, power consumption can be reduced even further to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Lower Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer have been reduced by up to 80%, with typical values of 1.1  $\mu$ A and 2.1  $\mu$ A, respectively.

#### 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F6310/6410/8310/8410 family offer nine different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes, with the same pin options as the External Clock modes.

- An internal oscillator block which provides an 8 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of six user-selectable clock frequencies between 125 kHz to 4 MHz for a total of eight clock frequencies. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, which allows clock speeds of up to 40 MHz. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds from 31 kHz to 32 MHz

– all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator block, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset or wake-up from Sleep mode until the primary clock source is available.

| Din Nome                                            | Pin Number | Pin               | Buffer           |                                                                                                   |  |  |  |

|-----------------------------------------------------|------------|-------------------|------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                            | TQFP       | Туре              | Туре             | Description                                                                                       |  |  |  |

|                                                     |            |                   |                  | PORTE is a bidirectional I/O port.                                                                |  |  |  |

| RE0/AD8/RD<br>RE0<br>AD8<br>RD                      | 4          | I/O<br>I/O<br>I   | ST<br>TTL<br>TTL | Digital I/O.<br>External Memory Address/Data 8.<br>Read control for Parallel Slave Port.          |  |  |  |

| RE1/AD9/WR<br>RE1<br>AD9<br>WR                      | 3          | I/O<br>I/O<br>I   | ST<br>TTL<br>TTL | TTL External Memory Address/Data 9.                                                               |  |  |  |

| RE2/AD10/ <del>CS</del><br>RE2<br>AD10<br>CS        | 78         | I/O<br>I/O<br>I   | ST<br>TTL<br>TTL | Digital I/O.<br>External Memory Address/Data 10.<br>Chip Select control for Parallel Slave Port.  |  |  |  |

| RE3/AD11<br>RE3<br>AD11                             | 77         | I/O<br>I/O        | ST<br>TTL        | Digital I/O.<br>External Memory Address/Data 11.                                                  |  |  |  |

| RE4/AD12<br>RE4<br>AD12                             | 76         | I/O<br>I/O        | ST<br>TTL        | Digital I/O.<br>External Memory Address/Data 12.                                                  |  |  |  |

| RE5/AD13<br>RE5<br>AD13                             | 75         | I/O<br>I/O        | ST<br>TTL        | Digital I/O.<br>External Memory Address/Data 13.                                                  |  |  |  |

| RE6/AD14<br>RE6<br>AD14                             | 74         | I/O<br>I/O        | ST<br>TTL        | Digital I/O.<br>External Memory Address/Data 14.                                                  |  |  |  |

| RE7/CCP2/AD15<br>RE7<br>CCP2 <sup>(3)</sup><br>AD15 | 73         | I/O<br>I/O<br>I/O | ST<br>ST<br>TTL  | Digital I/O.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>External Memory Address/Data 15. |  |  |  |

#### TABLE 1-3: PIC18F8310/8410 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared (all operating modes except Microcontroller mode).

2: Default assignment for CCP2 in all operating modes (CCP2MX is set).

3: Alternate assignment for CCP2 when CCP2MX is cleared (Microcontroller mode only).

# 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

# 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.2.3 CONSIDERATIONS WHEN USING BOR

When the Brown-out Reset (BOR) feature is enabled, a sudden change in VDD may result in a spontaneous BOR event. This can happen when the microcontroller is operating under normal operating conditions, regardless of what the BOR set point has been programmed to, and even if VDD does not approach the set point. The precipitating factor in these BOR events is a rise or fall in VDD with a slew rate faster than  $0.15V/\mu s$ .

An application that incorporates adequate decoupling between the power supplies will not experience such rapid voltage changes. Additionally, the use of an electrolytic tank capacitor across VDD and Vss, as described above, will be helpful in preventing high slew rate transitions.

If the application has components that turn on or off, and share the same VDD circuit as the microcontroller, the BOR can be disabled in software by using the SBOREN bit before switching the component. Afterwards, allow a small delay before re-enabling the BOR. By doing this, it is ensured that the BOR is disabled during the interval that might cause high slew rate changes of VDD.

Note: Not all devices incorporate software BOR control. See Section 5.0 "Reset" for device-specific information.

# 5.4 Brown-out Reset (BOR)

PIC18F6310/6410/8310/8410 devices implement a BOR circuit that provides the user with a number of configuration and power-saving options. The BOR is controlled by the BORV<1:0> and BOREN<1:0> Configuration bits. There are a total of four BOR configurations, which are summarized in Table 5-1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0> except '00'), any drop of VDD below VBOR (Parameter D005) for greater than TBOR (Parameter 35) will reset the device. A Reset may or may not occur if VDD falls below VBOR for less than TBOR. The chip will remain in Brown-out Reset until VDD rises above VBOR.

If the Power-up Timer is enabled, it will be invoked after VDD rises above VBOR; it then will keep the chip in Reset for an additional time delay, TPWRT (Parameter 33). If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be initialized. Once VDD rises above VBOR, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer (PWRT) are independently configured. Enabling the Brown-out Reset does not automatically enable the PWRT.

#### 5.4.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<6>). Setting SBOREN enables the BOR to function as previously described. Clearing SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing the BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor device power consumption in software by eliminating the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note | Even when BOR is under software con-       |

|------|--------------------------------------------|

|      | trol, the Brown-out Reset voltage level is |

|      | still set by the BORV<1:0> Configuration   |

|      | bits. It cannot be changed in software.    |

#### 5.4.2 DETECTING BOR

When Brown-out Reset is enabled, the BOR bit always resets to '0' on any BOR or POR event. This makes it difficult to determine if a Brown-out Reset event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR bit is reset to '1' in software immediately after any POR event. If BOR is '0' while POR is '1', it can be reliably assumed that a BOR event has occurred.

#### 5.4.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, the BOR remains under hardware control and operates as previously described. Whenever the device enters Sleep mode, however, the BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

| BOR Con | Configuration Status of |                     |                                                                                                  |

|---------|-------------------------|---------------------|--------------------------------------------------------------------------------------------------|

| BOREN1  | BOREN0                  | SBOREN<br>(RCON<6>) | BOR Operation                                                                                    |

| 0       | 0                       | Unavailable         | BOR is disabled; must be enabled by reprogramming the Configuration bits.                        |

| 0       | 1                       | Available           | BOR is enabled in software; operation controlled by SBOREN.                                      |

| 1       | 0                       | Unavailable         | BOR is enabled in hardware and active during the Run and Idle modes; disabled during Sleep mode. |

| 1       | 1                       | Unavailable         | BOR is enabled in hardware; must be disabled by reprogramming the Configuration bits.            |

TABLE 5-1: BOR CONFIGURATIONS

NOTES:

When the device is executing out of internal memory (EBDIS = 0) in Microprocessor with Boot Block mode or Extended Microcontroller mode, the control signals will NOT be active. They will go to a state where the AD<15:0> and A<19:16> are tri-state; the CE, OE, WRH, WRL, UB and LB signals are '1'; ALE and BA0 are '0'. Note that only those pins associated with the current address width are forced to tri-state; the other pins continue to function as I/O. In the case of a 16-bit address width, for example, only AD<15:0> (PORTD and PORTE) are affected; A<19:16> (PORTH<3:0>) continue to function as I/O. In all external memory modes, the bus takes priority over any other peripherals that may share pins with it. This includes the Parallel Slave Port and serial communications modules which would otherwise take priorityover the I/O port.

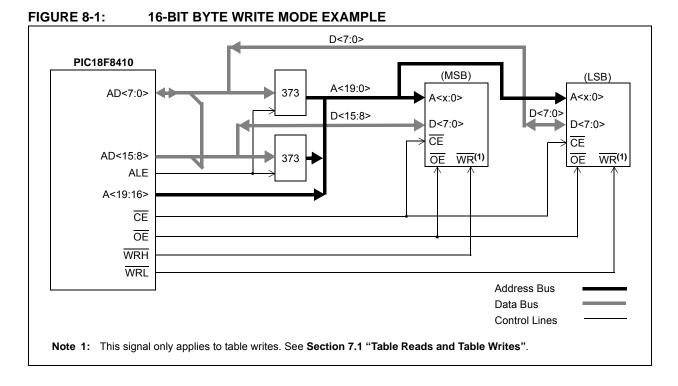

# 8.2 16-Bit Mode

In 16-bit mode, the external memory interface can be connected to external memories in three different configurations:

- 16-Bit Byte Write

- 16-Bit Word Write

- · 16-Bit Byte Select

The configuration to be used is determined by the WM<1:0> bits in the MEMCON register (MEMCON<1:0>). These three different configurations allow the designer maximum flexibility in using both 8-bit and 16-bit devices with 16-bit data.

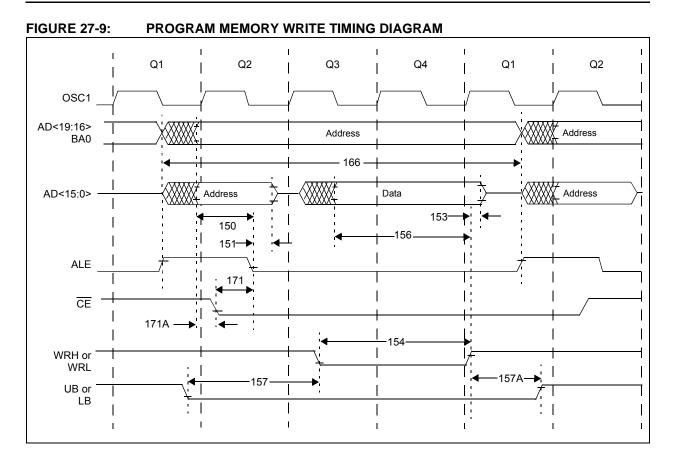

For all 16-bit modes, the Address Latch Enable (ALE) pin indicates that the address bits, A<15:0>, are available on the external memory interface bus. Following the address latch, the Output Enable signal ( $\overline{OE}$ ) will enable both bytes of program memory at once to form a 16-bit instruction word. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing; it is inactive (asserted high) whenever the device is in Sleep mode.

In Byte Select mode, JEDEC standard Flash memories will require BA0 for the byte address line and one I/O line to select between Byte and Word mode. The other 16-bit modes do not need BA0. JEDEC standard static RAM memories will use the  $\overline{\text{UB}}$  or  $\overline{\text{LB}}$  signals for byte selection.

### 8.2.1 16-BIT BYTE WRITE MODE

Figure 8-1 shows an example of 16-Bit Byte Write mode for PIC18F8310/8410 devices. This mode is used for two separate 8-bit memories connected for 16-bit operation. This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate WRH or WRL control line is strobed on the LSb of the TBLPTR.

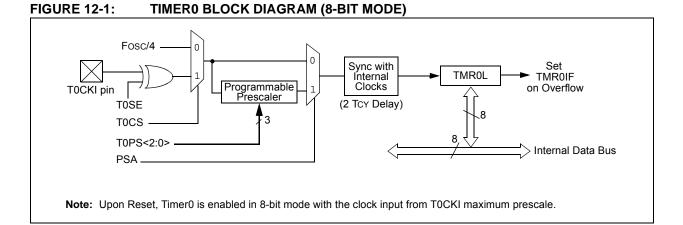

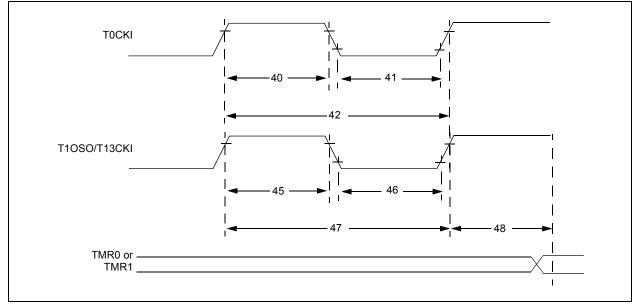

# 12.1 Timer0 Operation

Timer0 can operate as either a timer or a counter; the mode is selected by clearing the TOCS bit (TOCON<5>). In Timer mode (TOCS = 0), the module increments on every clock by default, unless a different prescaler value is selected (see **Section 12.3 "Prescaler"**). If the TMR0 register is written to, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

The Counter mode is selected by setting the TOCS bit (= 1). In Counter mode, Timer0 increments either on every rising or falling edge of pin, RA4/TOCKI. The incrementing edge is determined by the Timer0 Source Edge Select bit, TOSE (TOCON<4>); clearing this bit selects the rising edge. Restrictions on the external clock input are discussed below.

An external clock source can be used to drive Timer0; however, it must meet certain requirements to ensure that the external clock can be synchronized with the internal phase clock (Tosc). There is a delay between synchronization and the onset of incrementing the timer/counter.

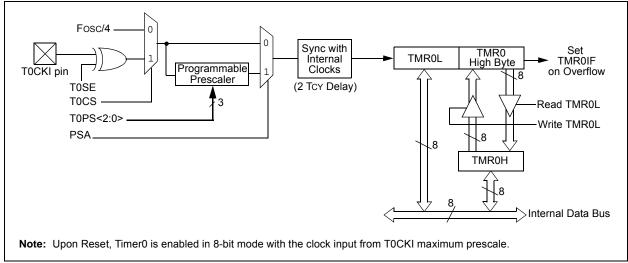

#### 12.2 Timer0 Reads and Writes in 16-Bit Mode

TMR0H is not the actual high byte of Timer0 in 16-bit mode; it is actually a buffered version of the real high byte of Timer0, which is not directly readable nor writable (refer to Figure 12-2). TMR0H is updated with the contents of the high byte of Timer0 during a read of TMR0L. This provides the ability to read all 16 bits of Timer0, without having to verify that the read of the high and low byte were valid, due to a rollover between successive reads of the high and low byte.

Similarly, a write to the high byte of Timer0 must also take place through the TMR0H Buffer register. The high byte is updated with the contents of TMR0H when a write occurs to TMR0L. This allows all 16 bits of Timer0 to be updated at once.

# FIGURE 12-2: TIMER0 BLOCK DIAGRAM (16-BIT MODE)

#### 13.3.3 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity.

The oscillator circuit, shown in Figure 13-3, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator (such as the CCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit may be helpful when used on a single sided PCB, or in addition to a ground plane.

# 13.4 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow, which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# 13.5 Resetting Timer1 Using the CCP Special Event Trigger

If CCP1 or CCP2 is configured in Compare mode to generate a Special Event Trigger (CCP1M<3:0> or CCP2M<3:0> = 1011), this signal will reset Timer1. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 16.3.4** "**Special Event Triggers**" for more information.).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRH:CCPRL register pair effectively becomes a period register for Timer1.

If Timer1 is running in Asynchronous Counter 'mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

**Note:** The special event triggers from the CCP2 module will not set the TMR1IF interrupt flag bit (PIR1<0>).

### 13.6 Using Timer1 as a Real-Time Clock

Adding an external LP oscillator to Timer1 (such as the one described in **Section 13.3 "Timer1 Oscillator**", above), gives users the option to include RTC functionality to their applications. This is accomplished with an inexpensive watch crystal to provide an accurate time base and several lines of application code to calculate the time. When operating in Sleep mode and using a battery or supercapacitor as a power source, it can completely eliminate the need for a separate RTC device and battery backup.

The application code routine, RTCisr, shown in Example 13-1, demonstrates a simple method to increment a counter at one-second intervals using an Interrupt Service Routine. Incrementing the TMR1 register pair to overflow triggers the interrupt and calls the routine, which increments the seconds counter by one; additional counters for minutes and hours are incremented as the previous counter overflow.

Since the register pair is 16 bits wide, counting up to overflow the register directly from a 32.768 kHz clock would take 2 seconds. To force the overflow at the required one-second intervals, it is necessary to preload it; the simplest method is to set the Most Significant bit of TMR1H with a BSF instruction. Note that the TMR1L register is never preloaded or altered; doing so may introduce cumulative error over many cycles.

For this method to be accurate, Timer1 must operate in Asynchronous mode and the Timer1 overflow interrupt must be enabled (PIE1<0> = 1), as shown in the routine RTCinit. The Timer1 oscillator must also be enabled and running at all times.

| REGISTER 17-4 | SSPCON                                                                                              | 11: MSSP C                                                                                                                                                                                                              | ONTROL                                         | REGISTER                                     | R 1 (I <sup>2</sup> C™ I       | MODE)                            |          |       |  |  |

|---------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------|--------------------------------|----------------------------------|----------|-------|--|--|

|               | R/W-0                                                                                               | R/W-0                                                                                                                                                                                                                   | R/W-0                                          | R/W-0                                        | R/W-0                          | R/W-0                            | R/W-0    | R/W-0 |  |  |

|               | SMP                                                                                                 | CKE                                                                                                                                                                                                                     | D/A                                            | P <sup>(1)</sup>                             | S <sup>(1)</sup>               | R/W <sup>(2,3)</sup>             | UA       | BF    |  |  |

|               | bit 7                                                                                               |                                                                                                                                                                                                                         |                                                |                                              |                                |                                  |          | bit 0 |  |  |

| bit 7         | In Master of<br>1 = Slew r                                                                          | <b>MP:</b> Slew Rate Control bit<br><u>n Master or Slave mode:</u><br>= Slew rate control disabled for Standard Speed mode (100 kHz and 1 MHz)                                                                          |                                                |                                              |                                |                                  |          |       |  |  |

| bit 6         | <b>CKE:</b> SME<br>In Master of<br>1 = Enable                                                       | <ul> <li>Slew rate control enabled for High-Speed mode (400 kHz)</li> <li>KE: SMBus Select bit<br/><u>Master or Slave mode:</u></li> <li>Enable SMBus specific inputs</li> <li>Disable SMBus specific inputs</li> </ul> |                                                |                                              |                                |                                  |          |       |  |  |

| bit 5         | <u>In Master r</u><br>Reserved.<br><u>In Slave m</u><br>1 = Indicat<br>0 = Indicat                  | A: Data/Address bit                                                                                                                                                                                                     |                                                |                                              |                                |                                  |          |       |  |  |

| bit 4         |                                                                                                     | (1)<br>es that a Sto<br>it was not de                                                                                                                                                                                   |                                                | en detected                                  | last                           |                                  |          |       |  |  |

| bit 3         |                                                                                                     | es that a Sta                                                                                                                                                                                                           |                                                | en detected                                  | last                           |                                  |          |       |  |  |

| bit 2         | <b>R/W</b> : Read<br>In <u>Slave m</u><br>1 = Read<br>0 = Write<br>In <u>Master r</u><br>1 = Transn |                                                                                                                                                                                                                         |                                                |                                              |                                |                                  |          |       |  |  |

| bit 1         | <b>UA:</b> Updat<br>1 = Indicat                                                                     | e Address bi                                                                                                                                                                                                            | t (10-Bit Sla<br>ser needs to                  | update the                                   |                                | the SSPADD                       | register |       |  |  |

| bit 0         | <b>BF:</b> Buffer<br>In Transmi<br>1 = Receiv<br>0 = Receive<br>In Receive<br>1 = Data tr           | Full Status b<br>t mode:<br>re complete,<br>re not complet<br>mode:<br>ansmit in pro                                                                                                                                    | it<br>SSPBUF is<br>ete, SSPBUF<br>ogress (does | full<br><sup>-</sup> is empty<br>not include |                                | nd Stop bits),<br>Stop bits), St |          |       |  |  |

| Note          | 2: This bit h<br>from the                                                                           | address ma                                                                                                                                                                                                              | V bit informatch to the ne                     | tion followin<br>xt Start bit, S             | g the last ac<br>Stop bit or n | dd <u>ress match</u>             |          | -     |  |  |

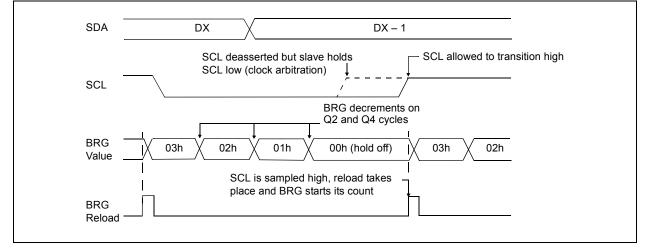

### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

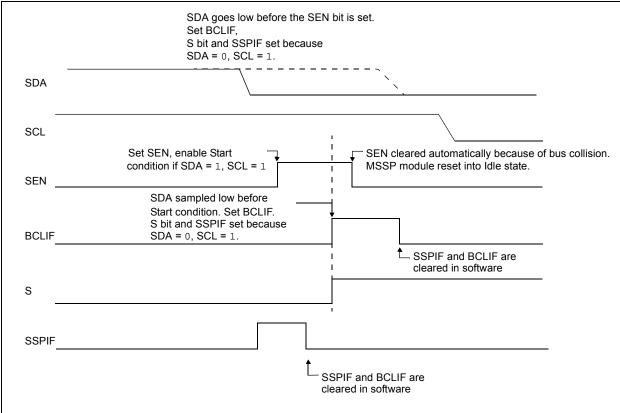

#### 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to '0' and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

### FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

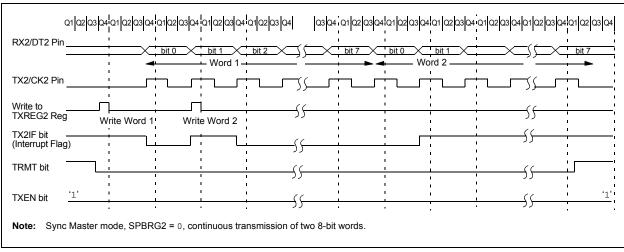

#### 19.3 AUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA2<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA2<4>). In addition, enable bit, SPEN (RCSTA2<7>), is set in order to configure the TX2 and RX2 pins to CK2 (clock) and DT2 (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK2 line.

#### 19.3.1 AUSART SYNCHRONOUS MASTER TRANSMISSION

The AUSART transmitter block diagram is shown in Figure 19-1. The heart of the transmitter is the Transmit (Serial) Shift register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG2. The TXREG2 register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG2 (if available). Once the TXREG2 register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG2 is empty and the TX2IF flag bit (PIR3<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TX2IE (PIE3<4>). TX2IF is set regardless of the state of enable bit, TX2IE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG2 register.

While flag bit, TX2IF, indicates the status of the TXREG2 register, another bit, TRMT (TXSTA2<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG2 register for the appropriate baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TX2IE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG2 register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 19-6: SYNCHRONOUS TRANSMISSION

The value in the ADRESH:ADRESL registers is not modified for a Power-on Reset. The ADRESH:ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 20.1 "A/D Acquisition Requirements". After this acquisition time has elapsed, the A/D conversion can be started. An acquisition time can be programmed to occur between setting the GO/DONE bit and the actual start of the conversion.

The following steps should be followed to perform an A/D conversion:

- 1. Configure the A/D module:

- · Configure analog pins, voltage reference and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D acquisition time (ADCON2)

- Select A/D conversion clock (ADCON2)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if desired):

- · Clear ADIF bit

- Set ADIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (if required).

- 4. Start conversion:

- Set GO/DONE bit (ADCON0 register)

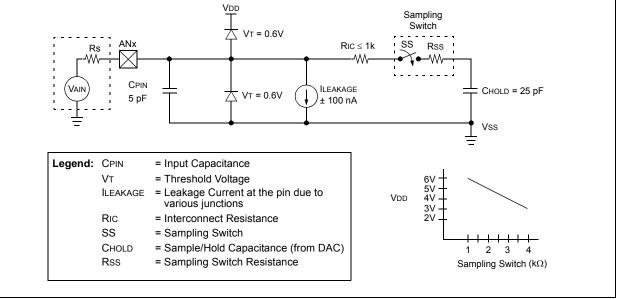

**FIGURE 20-3:** ANALOG INPUT MODEL 5. Wait for A/D conversion to complete, by either:

#### Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH:ADRESL); clear bit, ADIF, if required.

- 7. For next conversion, go to Step 1 or Step 2, as required. The A/D conversion time per bit is defined as TAD. A minimum wait of 3 TAD is required before the next acquisition starts.

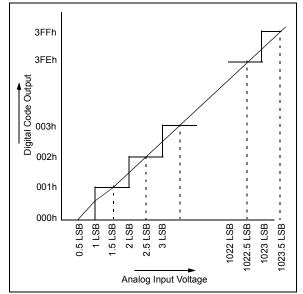

#### **FIGURE 20-2: A/D TRANSFER FUNCTION**

| SUBLW                 | 5           | Subtract W from literal |                         |        |    |           |  |  |

|-----------------------|-------------|-------------------------|-------------------------|--------|----|-----------|--|--|

| Syntax:               | ę           | SUBLW k                 |                         |        |    |           |  |  |

| Operands:             | (           | $0 \le k \le 255$       |                         |        |    |           |  |  |

| Operation:            | k           | x – (W) –               | → W                     |        |    |           |  |  |

| Status Affected:      | 1           | N, OV, C,               | DC, Z                   |        |    |           |  |  |

| Encoding:             | Γ           | 0000                    | 1000                    | kk}    | ck | kkkk      |  |  |

| Description:          |             |                         | racted fro<br>The resul |        |    |           |  |  |

| Words:                | 1           |                         |                         |        |    |           |  |  |

| Cycles:               | 1           |                         |                         |        |    |           |  |  |

| Q Cycle Activity:     |             |                         |                         |        |    |           |  |  |

| Q1                    |             | Q2                      | Q3                      | 6      |    | Q4        |  |  |

| Decode                |             | Read<br>eral 'k'        | Proce<br>Data           |        | W  | rite to W |  |  |

| Example 1:            | S           | SUBLW                   | 02h                     |        |    |           |  |  |

| Before Instruc        | tion        |                         |                         |        |    |           |  |  |

| W                     | =           | 01h                     |                         |        |    |           |  |  |

| C<br>After Instructio | =<br>on     | ?                       |                         |        |    |           |  |  |

| W                     | =           | 01h                     |                         |        |    |           |  |  |

| C<br>Z<br>N           | =<br>=<br>= | 1 ;<br>0<br>0           | result is p             | ositiv | е  |           |  |  |

| Example 2:            | S           | SUBLW                   | 02h                     |        |    |           |  |  |

| Before Instruc        | tion        |                         |                         |        |    |           |  |  |

| W                     | =           | 02h                     |                         |        |    |           |  |  |

| C<br>After Instructio | =           | ?                       |                         |        |    |           |  |  |

| W                     | =           | 00h                     |                         |        |    |           |  |  |

| C                     | =           | 1 ;                     | result is z             | ero    |    |           |  |  |

| Z<br>N                | =           | 1<br>0                  |                         |        |    |           |  |  |

| Example 3:            | S           | SUBLW                   | 02h                     |        |    |           |  |  |

| Before Instruc        | tion        |                         |                         |        |    |           |  |  |

| W<br>C                | =           | 03h<br>?                |                         |        |    |           |  |  |

| After Instruction     | _           | ſ                       |                         |        |    |           |  |  |

| W                     | =           |                         | (2's comp               |        |    |           |  |  |

| C<br>Z                | =           |                         | result is n             | egativ | ve |           |  |  |

| Z<br>N                | =           | 0<br>1                  |                         |        |    |           |  |  |

|                       |             |                         |                         |        |    |           |  |  |

| SUE          | WF               |           | Subtract W from f                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|--------------|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|----------------------|--|--|

| Synta        | ax:              |           | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | f {,d {,a}}       |                      |  |  |

| Oper         | ands:            |           | $0 \le f \le 255$                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              |                  |           | $d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                   |                      |  |  |

| Operation:   |                  |           | (f) – (W                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) —  | → dest            |                      |  |  |

| Statu        | s Affected:      |           | N, OV, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                | C, I | DC, Z             |                      |  |  |

| Enco         | ding:            |           | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | 11da fff          | f ffff               |  |  |

| Desc         | ription:         |           | Subtrac                                                                                                                                                                                                                                                                                                                                                                                                                                                 | t V  | V from register   | ʻf' (2's             |  |  |

| Description: |                  |           | complement method). If 'd' is 'o', the<br>result is stored in W. If 'd' is 'o', the<br>result is stored back in register 'f'.<br>If 'a' is 'o', the Access Bank is<br>selected. If 'a' is V, the BSR is used to<br>select the GPR bank.<br>If 'a' is 'o' and the extended instruction<br>set is enabled, this instruction<br>operates in Indexed Literal Offset<br>Addressing mode whenever $f \le 95$<br>(5Fh). See <b>Section 25.2.3</b> for details. |      |                   |                      |  |  |

| Word         | ls:              |           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

| Cycle        | es:              |           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

| •            | ycle Activity:   |           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | Q1               |           | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      | Q3                | Q4                   |  |  |

|              | Decode           | re        | Read<br>egister 'f                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,    | Process<br>Data   | Write to destination |  |  |

| Exan         | nple 1:          |           | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | REG, 1, 0         |                      |  |  |

|              | Before Instruc   | tior      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | -, , -            |                      |  |  |

|              | REG              | =         | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | W<br>C           | =         | 2<br>?                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                   |                      |  |  |

|              | After Instructio |           | ſ                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | REG              | =         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | W                | =         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | C<br>7           | =         | 1<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ;    | result is positiv | /e                   |  |  |

|              | Z<br>N           | =         | ŏ                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

| Exan         | nple 2:          |           | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | REG, 0, 0         |                      |  |  |

|              | Before Instruc   | tior      |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                   |                      |  |  |

|              | REG              | =         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | W<br>C           | =         | 2<br>?                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                   |                      |  |  |

|              | After Instructio | n         |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                   |                      |  |  |

|              | REG              | =         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | W                | =         | 0<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | rooult is zero    |                      |  |  |

|              | C<br>Z           | =         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ,    | result is zero    |                      |  |  |

| N =          |                  |           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | <u>nple 3:</u>   |           | SUBWF                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | REG, 1, 0         |                      |  |  |

|              | Before Instruc   | tior<br>= | า<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                   |                      |  |  |

|              | REG<br>W         | =         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | C                | =         | ?                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

|              | After Instructio |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |                   |                      |  |  |

|              | REG              | =         | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ;(2  | 2's complemer     | nt)                  |  |  |

|              | W<br>C           | =         | 2<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ; r  | esult is negativ  | /e                   |  |  |

|              | Ž<br>N           | =         | 0<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                  | , ·  |                   |                      |  |  |

|              | IN               | -         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |                   |                      |  |  |

# 27.2 DC Characteristics: Power-Down and Supply Current PIC18F6310/6410/8310/8410 (Industrial, Extended) PIC18LF6310/6410/8310/8410 (Industrial) (Continued)

|                                                     | PIC18LF6310/6410/8310/8410<br>(Industrial) |                                                                                                                                                                                         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |       |            |            |                                                         |  |  |

|-----------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------------|---------------------------------------------------------|--|--|

| PIC18F6310/6410/8310/8410<br>(Industrial, Extended) |                                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                                                                    |       |            |            |                                                         |  |  |

| Param<br>No.                                        | Device                                     | Тур                                                                                                                                                                                     | Max                                                                                                                                | Units | Conditions |            |                                                         |  |  |

|                                                     | Supply Current (IDD) <sup>(2)</sup>        | •                                                                                                                                                                                       | •                                                                                                                                  |       |            |            |                                                         |  |  |

|                                                     | PIC18LFX310/X410                           | 13                                                                                                                                                                                      | 40                                                                                                                                 | μA    | -10°C      |            |                                                         |  |  |

|                                                     |                                            | 14                                                                                                                                                                                      | 40                                                                                                                                 | μA    | +25°C      | VDD = 2.0V |                                                         |  |  |

|                                                     |                                            | 16                                                                                                                                                                                      | 40                                                                                                                                 | μA    | +70°C      |            |                                                         |  |  |

|                                                     | PIC18LFX310/X410                           | 34                                                                                                                                                                                      | 74                                                                                                                                 | μA    | -10°C      |            |                                                         |  |  |

|                                                     |                                            | 31                                                                                                                                                                                      | 70                                                                                                                                 | μA    | +25°C      | VDD = 3.0V | Fosc = 32 kHz <sup>(4)</sup>                            |  |  |

|                                                     |                                            | 28                                                                                                                                                                                      | 67                                                                                                                                 | μA    | +70°C      | Vpp = 5.0V | ( <b>SEC_RUN</b> mode,<br>Timer1 as clock)              |  |  |

|                                                     | All devices                                | 72                                                                                                                                                                                      | 150                                                                                                                                | μA    | -10°C      |            | ,                                                       |  |  |

|                                                     |                                            | 65                                                                                                                                                                                      | 150                                                                                                                                | μA    | +25°C      |            |                                                         |  |  |

|                                                     |                                            | 59                                                                                                                                                                                      | 150                                                                                                                                | μA    | +70°C      | VDD - 5.0V |                                                         |  |  |

|                                                     |                                            | 90                                                                                                                                                                                      | 170                                                                                                                                | μA    | +125°C     |            |                                                         |  |  |

|                                                     | PIC18LFX310/X410                           | 5.5                                                                                                                                                                                     | 15                                                                                                                                 | μA    | -10°C      |            |                                                         |  |  |

|                                                     |                                            | 5.8                                                                                                                                                                                     | 15                                                                                                                                 | μA    | +25°C      | VDD = 2.0V |                                                         |  |  |

|                                                     |                                            | 6.1                                                                                                                                                                                     | 18                                                                                                                                 | μA    | +70°C      |            |                                                         |  |  |

|                                                     | PIC18LFX310/X410                           | 8.2                                                                                                                                                                                     | 30                                                                                                                                 | μA    | -10°C      |            | <b>– – – – – – – – – –</b>                              |  |  |

|                                                     |                                            |                                                                                                                                                                                         | 30                                                                                                                                 | μA    | +25°C      | VDD = 3.0V | Fosc = 32 kHz <sup>(4)</sup><br>( <b>SEC_IDLE</b> mode, |  |  |

|                                                     |                                            | 8.8                                                                                                                                                                                     | 35                                                                                                                                 | μA    | +70°C      |            | Timer1 as clock)                                        |  |  |