Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 54                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

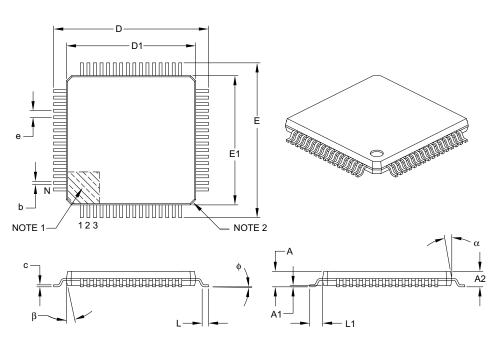

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6410-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

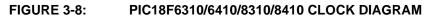

# 3.7 Clock Sources and Oscillator Switching

Like previous PIC18 devices, the PIC18F6310/6410/8310/8410 family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate low-frequency clock source. PIC18F6310/6410/8310/8410 devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary oscillators

- · Secondary oscillators

- · Internal oscillator block

The **primary oscillators** include the External Crystal and Resonator modes, the External RC modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<3:0> Configuration bits. The details of these modes are covered earlier in this chapter. The **secondary oscillators** are those external sources not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F6310/6410/8310/8410 devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC).

Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T13CKI and RC1/T1OSI/CCP2 pins. Like the LP mode oscillator circuit, loading capacitors are also connected from each pin to ground.

The Timer1 oscillator is discussed in greater detail in **Section 13.3 "Timer1 Oscillator"**.

In addition to being a primary clock source, the **internal oscillator block** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor.

The clock sources for the PIC18F6310/6410/8310/8410 devices are shown in Figure 3-8. See **Section 24.0 "Special Features of the CPU"** for Configuration register details.

# 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive, or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended.

This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

On transitions from RC\_RUN mode to PRI\_RUN, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

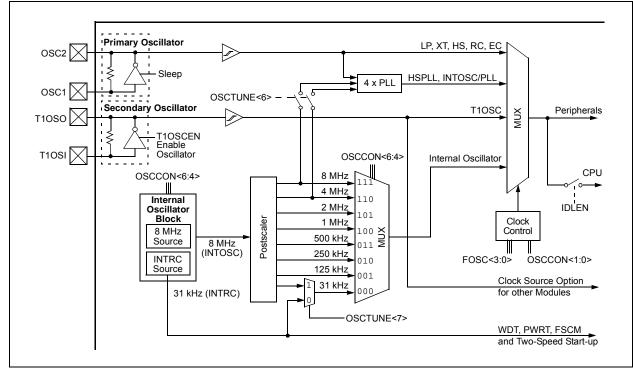

| TABLE 6-1: | MEMORY ACCESS FOR PIC18F8310/8410 PROGRAM MEMORY MODES |

|------------|--------------------------------------------------------|

|------------|--------------------------------------------------------|

| Oneneting                      | Inter             | nal Program Me     | mory           | External Program Memory |                    |                   |  |

|--------------------------------|-------------------|--------------------|----------------|-------------------------|--------------------|-------------------|--|

| Operating<br>Mode              | Execution<br>From | Table Read<br>From | Table Write To | Execution<br>From       | Table Read<br>From | Table Write<br>To |  |

| Microcontroller                | Yes               | Yes                | Yes            | No Access               | No Access          | No Access         |  |

| Extended<br>Microcontroller    | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes               |  |

| Microprocessor                 | No Access         | No Access          | No Access      | Yes                     | Yes                | Yes               |  |

| Microprocessor<br>w/Boot Block | Yes               | Yes                | Yes            | Yes                     | Yes                | Yes               |  |

© 2010 Microchip Technology Inc.

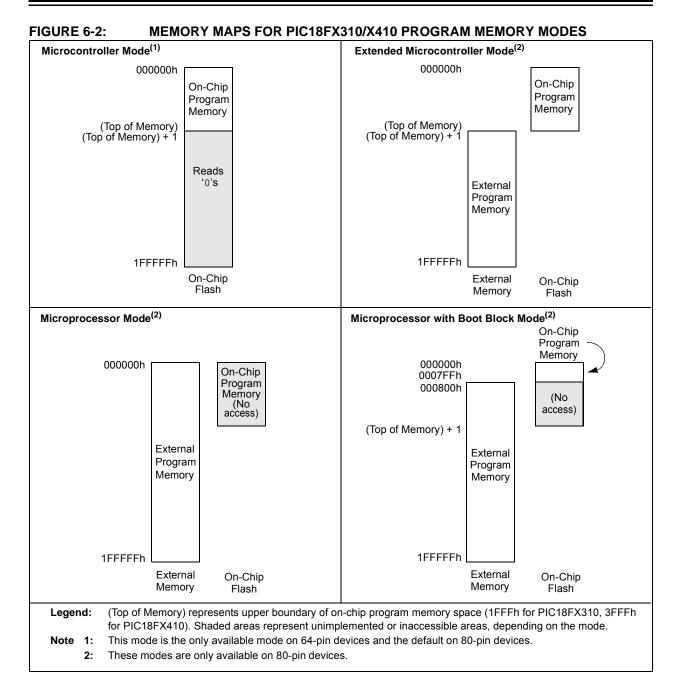

### FIGURE 6-9: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

# When a = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and FFFh. This is the same as locations F60h to FFFh (Bank 15) of data memory.

Locations below 060h are not available in this addressing mode.

#### When a = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When a = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 16 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

| TABLE 7-2: | REGISTERS ASSOCIATED WITH FLASH PROGRAM MEMORY |

|------------|------------------------------------------------|

|            |                                                |

| Name    | Bit 7                                                 | Bit 6     | Bit 5     | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page |

|---------|-------------------------------------------------------|-----------|-----------|------------|-------|-------|-------|-------|----------------------------|

| TBLPTRU |                                                       |           | bit 21    | Program Me | 63    |       |       |       |                            |

| TBLPTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |           |           |            |       |       | 63    |       |                            |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)   |           |           |            |       |       | 63    |       |                            |

| TABLAT  | Program I                                             | Memory Ta | ble Latch |            |       |       |       |       | 63                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash/EEPROM access.

# 8.3 8-Bit Mode

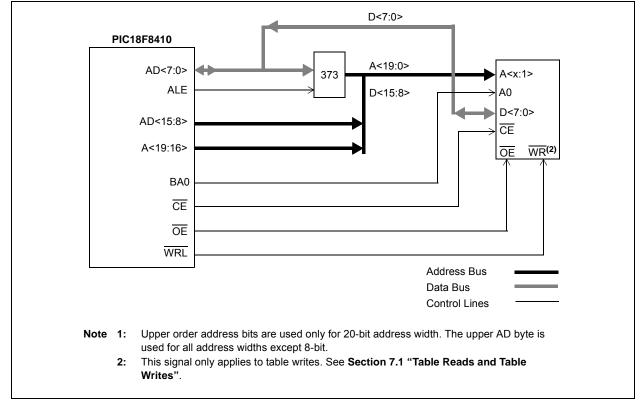

The external memory interface implemented in PIC18F8410 devices operates only in 8-Bit Multiplexed mode; data shares the 8 Least Significant bits of the address bus.

Figure 8-1 shows an example of 8-Bit Multiplexed mode for PIC18F8410 devices. This mode is used for a single 8-bit memory connected for 16-bit operation. The instructions will be fetched as two 8-bit bytes on a shared data/address bus. The two bytes are sequentially fetched within one instruction cycle (TcY). Therefore, the designer must choose external memory devices according to timing calculations based on 1/2 TcY (2 times the instruction rate). For proper memory speed selection, glue logic propagation delay times must be considered along with setup and hold times.

The Address Latch Enable (ALE) pin indicates that the address bits, A<15:0>, are available on the external memory interface bus. The Output Enable signal ( $\overline{OE}$ ) will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The Least Significant bit of the address, BA0, must be connected to the memory devices in this mode. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing; it is inactive (asserted high) whenever the device is in Sleep mode.

This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate level of the BA0 control line is strobed on the LSb of the TBLPTR.

### FIGURE 8-7: 8-BIT MULTIPLEXED MODE EXAMPLE

# 10.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure that the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

# REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0    | R/W-0     | R/W-0  | R/W-0         | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|---------------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | <b>INTOIE</b> | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |               |       |        |        | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | GIE/GIEH: Global Interrupt Enable bit                                                                                                                                     |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | When IPEN = 0:                                                                                                                                                            |  |

|       | 1 = Enables all unmasked interrupts                                                                                                                                       |  |

|       | 0 = Disables all interrupts                                                                                                                                               |  |

|       | When IPEN = 1:                                                                                                                                                            |  |

|       | <ul> <li>1 = Enables all high-priority interrupts</li> <li>0 = Disables all interrupts</li> </ul>                                                                         |  |

| bit 6 | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                                                |  |

|       | When IPEN = 0:                                                                                                                                                            |  |

|       | 1 = Enables all unmasked peripheral interrupts                                                                                                                            |  |

|       | 0 = Disables all peripheral interrupts                                                                                                                                    |  |

|       | When IPEN = 1:                                                                                                                                                            |  |

|       | 1 = Enables all low-priority peripheral interrupts                                                                                                                        |  |

| L:1 F | 0 = Disables all low-priority peripheral interrupts                                                                                                                       |  |

| bit 5 | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                |  |

|       | <ul> <li>1 = Enables the TMR0 overflow interrupt</li> <li>0 = Disables the TMR0 overflow interrupt</li> </ul>                                                             |  |

| bit 4 | INTOIE: INTO External Interrupt Enable bit                                                                                                                                |  |

|       | 1 = Enables the INTO external interrupt                                                                                                                                   |  |

|       | 0 = Disables the INT0 external interrupt                                                                                                                                  |  |

| bit 3 | RBIE: RB Port Change Interrupt Enable bit                                                                                                                                 |  |

|       | 1 = Enables the RB port change interrupt                                                                                                                                  |  |

|       | 0 = Disables the RB port change interrupt                                                                                                                                 |  |

| bit 2 | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                                  |  |

|       | 1 = TMR0 register has overflowed (must be cleared in software)                                                                                                            |  |

|       | 0 = TMR0 register did not overflow                                                                                                                                        |  |

| bit 1 | INTOIF: INTO External Interrupt Flag bit                                                                                                                                  |  |

|       | 1 = The INT0 external interrupt occurred (must be cleared in software)                                                                                                    |  |

|       | 0 = The INTO external interrupt did not occur                                                                                                                             |  |

| bit 0 | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                                             |  |

|       | <ul> <li>1 = At least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |  |

|       | 0 - None of the ND>7.47 pins have changed state                                                                                                                           |  |

|       |                                                                                                                                                                           |  |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and allow the bit to be cleared.

# 10.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

# REGISTER 10-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

| R/W-0 | R/W-0 | R-0   | R-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|-------|--------|--------|--------|

| PSPIF | ADIF  | RC1IF | TX1IF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

| bit 7 |       |       |       |       |        |        | bit 0  |

| Legend:      |                              |                                                             |                                                  |                       |

|--------------|------------------------------|-------------------------------------------------------------|--------------------------------------------------|-----------------------|

| R = Readal   | ble bit                      | W = Writable bit                                            | U = Unimplemented bit                            | , read as '0'         |

| -n = Value a | at POR                       | '1' = Bit is set                                            | '0' = Bit is cleared                             | x = Bit is unknown    |

|              |                              |                                                             |                                                  |                       |

| bit 7        |                              | arallel Slave Port Read/Writ                                |                                                  |                       |

|              |                              | d or a write operation has ta<br>ad or write has occurred   | aken place (must be cleared i                    | n software)           |

| bit 6        |                              | ) Converter Interrupt Flag bi                               | it                                               |                       |

|              |                              |                                                             | ust be cleared in software)                      |                       |

|              |                              | VD conversion is not compl                                  |                                                  |                       |

| bit 5        | RC1IF: E                     | JSART Receive Interrupt F                                   | lag bit                                          |                       |

|              |                              | EUSART receive buffer, RC<br>EUSART receive buffer is er    | REG1, is full (cleared when R<br>mpty            | CREG1 is read)        |

| bit 4        | TX1IF: EU                    | JSART Transmit Interrupt F                                  | lag bit                                          |                       |

|              |                              | EUSART transmit buffer, TX<br>EUSART transmit buffer is fi  | REG1, is empty (cleared whe<br>ull               | en TXREG1 is written) |

| bit 3        | SSPIF: M                     | aster Synchronous Serial P                                  | ort Interrupt Flag bit                           |                       |

|              |                              | ransmission/reception is congression is congression receive | mplete (must be cleared in so                    | oftware)              |

| bit 2        | CCP1IF:                      | CCP1 Interrupt Flag bit                                     |                                                  |                       |

|              |                              |                                                             | occurred (must be cleared in s                   | software)             |

|              | 0 = No TI<br><u>PWM mo</u> o | R1/TMR3 register compare<br>MR1/TMR3 register compar<br>de: | match occurred (must be cle<br>re match occurred | ared in software)     |

|              |                              | this mode.                                                  |                                                  |                       |

| bit 1        |                              | TMR2 to PR2 Match Interru                                   |                                                  |                       |

|              |                              | VR2 to PR2 match occurred (m                                | nust be cleared in software)<br>d                |                       |

| bit 0        | TMR1IF:                      | TMR1 Overflow Interrupt Fla                                 | ag bit                                           |                       |

|              |                              | 1 register overflowed (must<br>1 register did not overflow  | be cleared in software)                          |                       |

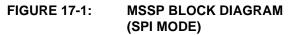

# 17.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

# 17.1 Master SSP (MSSP) Module Overview

The Master Synchronous Serial Port (MSSP) module is a serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C)

- Full Master mode

- Slave mode (with general address call)

The  $I^2C$  interface supports the following modes in hardware:

- Master mode

- · Multi-Master mode

- Slave mode

# 17.2 Control Registers

The MSSP module has three associated registers. These include a status register (SSPSTAT) and two control registers (SSPCON1 and SSPCON2). The use of these registers and their individual configuration bits differ significantly depending on whether the MSSP module is operated in SPI or  $I^2C$  mode.

Additional details are provided under the individual sections.

# 17.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported. To accomplish communication, typically three pins are used:

- Serial Data Out (SDO)

- Serial Data In (SDI)

- Serial Clock (SCK)

Additionally, a fourth pin may be used when in a Slave mode of operation:

• Slave Select (SS)

Figure 17-1 shows the block diagram of the MSSP module when operating in SPI mode.

# 17.4.14 SLEEP OPERATION

While in Sleep mode, the  $I^2C$  module can receive addresses or data and when an address match or complete byte transfer occurs, wake the processor from Sleep (if the MSSP interrupt is enabled).

### 17.4.15 EFFECT OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

#### 17.4.16 MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the detection of the Start and Stop conditions allows the determination of when the bus is free. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the I<sup>2</sup>C bus may be taken when the P bit (SSPSTAT<4>) is set, or the bus is Idle, with both the S and P bits clear. When the bus is busy, enabling the MSSP interrupt will generate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be monitored for arbitration to see if the signal level is the expected output level. This check is performed in hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

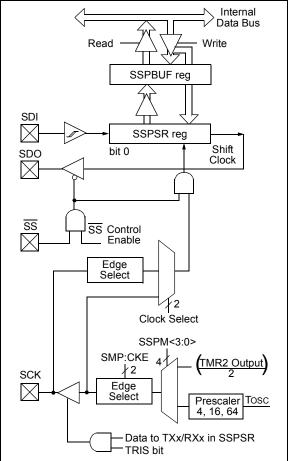

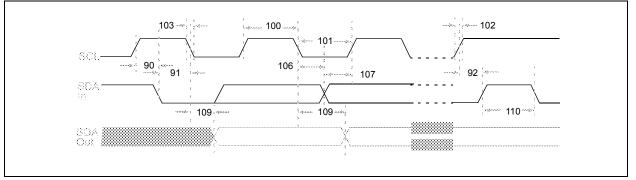

#### 17.4.17 MULTI -MASTER COMMUNICATION, BUS COLLISION AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA, by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the  $I^2C$  port to its Idle state (Figure 17-25).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are deasserted and the SSPBUF can be written to. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are deasserted and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision Interrupt Service Routine and if the  $I^2C$  bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit regardless of where the transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is Idle and the S and P bits are cleared.

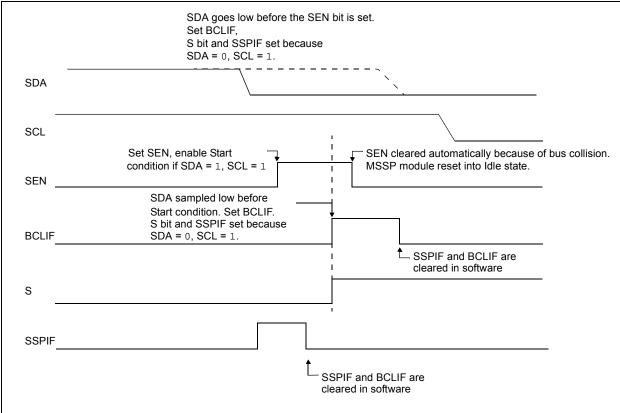

#### FIGURE 17-25: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### 17.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 17-26).

- b) SCL is sampled low before SDA is asserted low (Figure 17-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 17-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 17-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to '0' and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

# FIGURE 17-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

| R/W-0             | R/W-0                                           | R/W-0                                                                                                      | R/W-0                             | R/W-0            | R-0             | R-0               | R-x      |  |  |  |

|-------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-----------------|-------------------|----------|--|--|--|

| SPEN              | RX9                                             | SREN                                                                                                       | CREN                              | ADDEN            | FERR            | OERR              | RX9D     |  |  |  |

| bit 7             |                                                 |                                                                                                            |                                   |                  |                 |                   | bit (    |  |  |  |

|                   |                                                 |                                                                                                            |                                   |                  |                 |                   |          |  |  |  |

| Legend:           |                                                 |                                                                                                            |                                   |                  |                 |                   |          |  |  |  |

| R = Readable      |                                                 | W = Writable                                                                                               |                                   | -                | nented bit, rea | id as '0'         |          |  |  |  |

| -n = Value at POR |                                                 | '1' = Bit is set                                                                                           |                                   | '0' = Bit is cle | ared            | x = Bit is unkr   | nown     |  |  |  |

| bit 7             | SPEN: Seria                                     | al Port Enable bi                                                                                          | t                                 |                  |                 |                   |          |  |  |  |

|                   |                                                 | ort is enabled<br>ort is disabled                                                                          |                                   |                  |                 |                   |          |  |  |  |

| bit 6             | RX9: 9-Bit F                                    | Receive Enable I                                                                                           | oit                               |                  |                 |                   |          |  |  |  |

|                   |                                                 | 9-bit reception<br>8-bit reception                                                                         |                                   |                  |                 |                   |          |  |  |  |

| bit 5             | SREN: Sing                                      | le Receive Enat                                                                                            | ole bit                           |                  |                 |                   |          |  |  |  |

|                   | <u>Asynchrono</u><br>Don't care.                | <u>us mode</u> :                                                                                           |                                   |                  |                 |                   |          |  |  |  |

|                   | 1 = Enables<br>0 = Disable<br>This bit is cl    | <u>s mode – Maste</u><br>s single receive<br>s single receive<br>eared after rece<br><u>s mode – Slave</u> | ption is comp                     | lete.            |                 |                   |          |  |  |  |

| bit 4             | Don't care. CREN: Continuous Receive Enable bit |                                                                                                            |                                   |                  |                 |                   |          |  |  |  |

|                   | Asynchrono<br>1 = Enables<br>0 = Disable        | <u>us mode:</u><br>s receiver                                                                              |                                   |                  |                 |                   |          |  |  |  |

|                   |                                                 | <u>s mode:</u><br>s continuous rec<br>s continuous rec                                                     |                                   | ble bit, CREN,   | is cleared (CR  | EN overrides SI   | REN)     |  |  |  |

| bit 3             | ADDEN: Ad                                       | dress Detect En                                                                                            | able bit                          |                  |                 |                   |          |  |  |  |

|                   | 1 = Enables<br>0 = Disable                      | <u>us mode 9-Bit (F</u><br>s address detect<br>s address detec<br>us mode 8-Bit (F                         | ion, enables i<br>tion, all bytes |                  |                 |                   |          |  |  |  |

| bit 2             |                                                 | ning Error bit<br>g error (can be c<br>ning error                                                          | leared by rea                     | ding RCREG1      | register and re | eceiving next val | id byte) |  |  |  |

| bit 1             |                                                 | rrun Error bit                                                                                             |                                   |                  |                 |                   |          |  |  |  |

|                   |                                                 | n error (can be c                                                                                          | leared by clea                    | aring bit, CREN  | )               |                   |          |  |  |  |

| bit 0             |                                                 | it of Received D                                                                                           | ata bit                           |                  |                 |                   |          |  |  |  |

|                   |                                                 |                                                                                                            |                                   |                  |                 |                   |          |  |  |  |

# 18.1 EUSART Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode; setting the BRG16 bit (BAUDCON1<3>) selects 16-bit mode.

The SPBRGH1:SPBRG1 register pair controls the period of a free running timer. In Asynchronous mode, bits, BRGH (TXSTA1<2>) and BRG16 (BAUDCON1<3>), also control the baud rate. In Synchronous mode, BRGH is ignored. Table 18-1 shows the formula for computation of the baud rate for different EUSART modes that only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGH1:SPBRG1 registers can be calculated using the formulas in Table 18-1. From this, the error in baud rate can be determined. An example calculation is shown in Example 18-1. Typical baud rates and error values for the various Asynchronous modes are shown in Table 18-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

TABLE 18-1:BAUD RATE FORMULAS

Writing a new value to the SPBRGH1:SPBRG1 registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

| Note: | The BRG value of '0' is not supported. |

|-------|----------------------------------------|

|       |                                        |

# 18.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRG1 register pair.

### 18.1.2 SAMPLING

The data on the RXx pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RXx pin when SYNC is clear or when both BRG16 and BRGH are not set. The data on the RXx pin is sampled once when SYNC is set or when BRGH16 and BRGH are both set.

| Co   | onfiguration B | its  | BRG/EUSART Mode                      | Baud Rate Formula        |  |  |

|------|----------------|------|--------------------------------------|--------------------------|--|--|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode                      | Bauu Kate Follilula      |  |  |

| 0    | 0              | 0    | 8-bit/Asynchronous Fosc/[64 (n + 1)] |                          |  |  |

| 0    | 0              | 1    | 8-bit/Asynchronous                   | $E_{0} = c/[16 (n + 1)]$ |  |  |

| 0    | 1              | 0    | 16-bit/Asynchronous                  | Fosc/[16 (n + 1)]        |  |  |

| 0    | 1              | 1    | 16-bit/Asynchronous                  |                          |  |  |

| 1    | 0              | x    | 8-bit/Synchronous                    | Fosc/[4 (n + 1)]         |  |  |

| 1    | 1              | x    | 16-bit/Synchronous                   |                          |  |  |

Legend: x = Don't care, n = Value of SPBRGH1:SPBRG1 register pair

#### EXAMPLE 18-1: CALCULATING BAUD RATE ERROR

| For a device with FOSC | of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit BRG:              |

|------------------------|----------------------------------------------------------------------------------|

| Desired Baud Rate      | = Fosc/(64 ([SPBRGH1:SPBRG1] + 1))                                               |

| Solving for SPBRGH1:   | SPBRG1:                                                                          |

| Х                      | = ((Fosc/Desired Baud Rate)/64) – 1                                              |

| :                      | = ((1600000/9600)/64) - 1                                                        |

| :                      | = [25.042] = 25                                                                  |

| Calculated Baud Rate   | = 1600000/(64(25+1))                                                             |

| :                      | = 9615                                                                           |

| Error                  | <ul> <li>(Calculated Baud Rate – Desired Baud Rate)/Desired Baud Rate</li> </ul> |

| :                      | = (9615 - 9600)/9600 = 0.16%                                                     |

|                        |                                                                                  |

# TABLE 18-2: REGISTERS ASSOCIATED WITH THE BAUD RATE GENERATOR

| Bit 7                                          | Bit 6                             | Bit 5                                        | Bit 4                                                                                                              | Bit 3                                                                       | Bit 2                                                                                              | Bit 1                                                                                                                  | Bit 0                                                                                                                          | Reset Values<br>on Page                                                                                                                         |

|------------------------------------------------|-----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| CSRC                                           | TX9                               | TXEN                                         | SYNC                                                                                                               | SENDB                                                                       | BRGH                                                                                               | TRMT                                                                                                                   | TX9D                                                                                                                           | 65                                                                                                                                              |

| SPEN                                           | RX9                               | SREN                                         | CREN                                                                                                               | ADDEN                                                                       | FERR                                                                                               | OERR                                                                                                                   | RX9D                                                                                                                           | 65                                                                                                                                              |

| ABDOVF                                         | RCIDL                             | RXDTP                                        | TXCKP                                                                                                              | BRG16                                                                       | _                                                                                                  | WUE                                                                                                                    | ABDEN                                                                                                                          | 66                                                                                                                                              |

| EUSART1 Baud Rate Generator Register High Byte |                                   |                                              |                                                                                                                    | 66                                                                          |                                                                                                    |                                                                                                                        |                                                                                                                                |                                                                                                                                                 |

| EUSART1 Baud Rate Generator Register Low Byte  |                                   |                                              | 65                                                                                                                 |                                                                             |                                                                                                    |                                                                                                                        |                                                                                                                                |                                                                                                                                                 |

|                                                | CSRC<br>SPEN<br>ABDOVF<br>EUSART1 | CSRCTX9SPENRX9ABDOVFRCIDLEUSART1BaudBaudRate | CSRC     TX9     TXEN       SPEN     RX9     SREN       ABDOVF     RCIDL     RXDTP       EUSART1     Baud     Rate | CSRCTX9TXENSYNCSPENRX9SRENCRENABDOVFRCIDLRXDTPTXCKPEUSART1BaudRateGenerator | CSRCTX9TXENSYNCSENDBSPENRX9SRENCRENADDENABDOVFRCIDLRXDTPTXCKPBRG16EUSART1BaudRateGeneratorRegister | CSRCTX9TXENSYNCSENDBBRGHSPENRX9SRENCRENADDENFERRABDOVFRCIDLRXDTPTXCKPBRG16—EUSART1 Baud RateGeneratorRegisterHigh Byte | CSRCTX9TXENSYNCSENDBBRGHTRMTSPENRX9SRENCRENADDENFERROERRABDOVFRCIDLRXDTPTXCKPBRG16—WUEEUSART1BaudRateGeneratorRegisterHighByte | CSRCTX9TXENSYNCSENDBBRGHTRMTTX9DSPENRX9SRENCRENADDENFERROERRRX9DABDOVFRCIDLRXDTPTXCKPBRG16—WUEABDENEUSART1Baud Rate Generator RegisterHigh Byte |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

| Byte-oriented file register operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Example Instruction       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADDWF MYREG, W, B         |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |                           |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| 15 12 11 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MOVFF MYREG1, MYREG2      |

| 15 12 11 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |

| f = 12-bit file register address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |

| Bit-oriented file register operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| <u>15 12 11 9 8 7 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BSF MYREG, bit, B         |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| Literal operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| OPCODE k (literal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MOVLW 7Fh                 |

| k = 8-bit immediate value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Control operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

| Control operations<br>CALL, GOTO and Branch operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GOTO Label                |

| CALL, GOTO and Branch operations15870                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | GOTO Label                |

| CALL, GOTO and Branch operations15870OPCODEn<7:0> (literal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1                                                                                                                                                                                                                                                                                                                                                                                                                                       | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       1       1                                                                                                                                                                                                                                                                                                                                                                                    | GOTO Label<br>CALL MYFUNC |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE       n<7:0> (literal)         15       12 11       0         1111       n<19:8> (literal)         n = 20-bit immediate value         15       8 7       0                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       15       8       7       0         OPCODE       S       n<7:0> (literal)       1                                                                                                                                                                                                                                                                                                             |                           |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       15       8 7       0         15       8 7       0       0       0         15       8 7       0       0       0         15       8 7       0       0       0         15       12       11       0       0                                                                                                                                                                                           |                           |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE $n<7:0>$ (literal)         15       12 11       0         1111 $n<19:8>$ (literal)         n = 20-bit immediate value         15       8 7       0         OPCODE       S $n<7:0>$ (literal)         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         S = Fast bit       S = Fast bit                                                                                        |                           |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE $n<7:0>$ (literal)       15       12       11       0         15       12       11       0       1111 $n<19:8>$ (literal)         n = 20-bit immediate value       15       8       7       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         1111 $n<19:8>$ (literal)       0         15       11       10       0 |                           |

| CALL, GOTO and Branch operations15870 $OPCODE$ $n<7:0>$ (literal)15121101111 $n<19:8>$ (literal)n = 20-bit immediate value15870 $OPCODE$ S $n<7:0>$ (literal)15121101111 $n<19:8>$ (literal)S = Fast bit1511100 $OPCODE$ $n<10:0>$ (literal)                                                                                                                                                                                                                                                                                                                                                                                      | CALL MYFUNC               |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE $n<7:0>$ (literal)       15       12       11       0         15       12       11       0       1111 $n<19:8>$ (literal)         n = 20-bit immediate value       15       8       7       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         1111 $n<19:8>$ (literal)       0         15       11       10       0 | CALL MYFUNC               |

| RRNCF                                                          | Rotate Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ight f (no ca                           | ry)                  |  |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|--|

| Syntax:                                                        | RRNCF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f {,d {,a}}                             |                      |  |

| Operands:                                                      | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |                      |  |

| Operation:                                                     | $(f \le n >) \rightarrow d$<br>$(f \le 0 >) \rightarrow d$                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | est <n 1="" –="">,<br/>est&lt;7&gt;</n> |                      |  |