Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 768 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6410t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0  | Device Overview                                                              | 9   |

|------|------------------------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC18F Microcontrollers                  |     |

| 3.0  | Oscillator Configurations                                                    |     |

| 4.0  | Power-Managed Modes                                                          |     |

| 5.0  | Reset                                                                        |     |

| 6.0  | Memory Organization                                                          |     |

| 7.0  | Program Memory                                                               |     |

| 8.0  | External Memory Interface                                                    |     |

| 9.0  | 8 x 8 Hardware Multiplier                                                    |     |

| 10.0 | Interrupts                                                                   |     |

| 11.0 | I/O Ports                                                                    |     |

| 12.0 | Timer0 Module                                                                |     |

| 13.0 | Timer1 Module                                                                |     |

| 14.0 | Timer2 Module                                                                |     |

| 15.0 | Timer3 Module                                                                |     |

|      | Capture/Compare/PWM (CCP) Modules                                            |     |

| 17.0 | Master Synchronous Serial Port (MSSP) Module                                 |     |

| 18.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)    |     |

|      | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |     |

| 20.0 | 10-Bit Analog-to-Digital Converter (A/D) Module                              |     |

| 21.0 | Comparator Module                                                            |     |

| 22.0 | Comparator Voltage Reference Module                                          |     |

| 23.0 | High/Low-Voltage Detect (HLVD)                                               |     |

| 24.0 | Special Features of the CPU                                                  |     |

| 25.0 | Instruction Set Summary                                                      |     |

| 26.0 | Development Support                                                          |     |

|      | Electrical Characteristics                                                   |     |

| 28.0 | Packaging Information                                                        |     |

| Appe | ndix A: Revision History                                                     |     |

|      | ndix B: Device Differences                                                   |     |

| Appe | ndix C: Conversion Considerations                                            |     |

|      | ndix D: Migration from Baseline to Enhanced Devices                          |     |

|      | ndix E: Migration from Mid-Range to Enhanced Devices                         |     |

|      | ndix F: Migration from High-End to Enhanced Devices                          |     |

|      | (                                                                            |     |

|      | Nicrochip Web Site                                                           |     |

|      | omer Change Notification Service                                             |     |

|      | omer Support                                                                 |     |

|      | ler Response                                                                 |     |

| PIC1 | 8F6310/6410/8310/8410 Product Identification System                          | 411 |

| Name  | Bit 7     | Bit 6        | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page |

|-------|-----------|--------------|------------|-------|-------|-------|-------|-------|----------------------------|

| PORTC | RC7       | RC6          | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | 66                         |

| LATC  | LATC Outp | out Latch Re | egister    |       |       |       |       |       | 66                         |

| TRISC | PORTC Da  | ata Directio | n Register |       |       |       |       |       | 66                         |

# TABLE 11-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

## 17.3.8 SLEEP OPERATION

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

In most power-managed modes, a clock is provided to the peripherals. That clock should be from the primary clock source, the secondary clock (Timer1 oscillator at 32.768 kHz) or the INTOSC source. See **Section 3.7 "Clock Sources and Oscillator Switching**" for additional information.

In most cases, the speed that the master clocks SPI data is not important; however, this should be evaluated for each system.

If MSSP interrupts are enabled, they can wake the controller from Sleep mode, or one of the Idle modes, when the master completes sending data. If an exit from Sleep or Idle mode is not desired, MSSP interrupts should be disabled.

If the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the devices wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in any power-managed mode and data to be shifted into the SPI Transmit/ Receive Shift register. When all 8 bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

## 17.3.9 EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the current transfer.

### 17.3.10 BUS MODE COMPATIBILITY

Table 17-1 shows the compatibility between the standard SPI modes and the states of the CKP and CKE control bits.

| Standard SPI Mode | Control Bits State |     |  |  |

|-------------------|--------------------|-----|--|--|

| Terminology       | СКР                | CKE |  |  |

| 0, 0              | 0                  | 1   |  |  |

| 0, 1              | 0                  | 0   |  |  |

| 1, 0              | 1                  | 1   |  |  |

| 1, 1              | 1                  | 0   |  |  |

## TABLE 17-1: SPI BUS MODES

There is also an SMP bit which controls when the data is sampled.

| TABLE 17-2: REGISTERS ASSOCIATED WITH SPIOPERATION |            |              |               |              |              |          |        |        |                            |  |

|----------------------------------------------------|------------|--------------|---------------|--------------|--------------|----------|--------|--------|----------------------------|--|

| Name                                               | Bit 7      | Bit 6        | Bit 5         | Bit 4        | Bit 3        | Bit 2    | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |  |

| INTCON                                             | GIE/GIEH   | PEIE/GIEL    | TMR0IE        | INT0IE       | RBIE         | TMR0IF   | INT0IF | RBIF   | 63                         |  |

| PIR1                                               | PSPIF      | ADIF         | RC1IF         | TX1IF        | SSPIF        | CCP1IF   | TMR2IF | TMR1IF | 65                         |  |

| PIE1                                               | PSPIE      | ADIE         | RC1IE         | TX1IE        | SSPIE        | CCP1IE   | TMR2IE | TMR1IE | 65                         |  |

| IPR1                                               | PSPIP      | ADIP         | RC1IP         | TX1IP        | SSPIP        | CCP1IP   | TMR2IP | TMR1IP | 65                         |  |

| TRISC                                              | PORTC Da   | ta Direction | Register      |              |              |          |        |        | 66                         |  |

| TRISF                                              | PORTF Da   | ta Direction | Register      |              |              |          |        |        | 66                         |  |

| SSPBUF                                             | Master Syr | nchronous Se | erial Port Re | eceive Buffe | r/Transmit F | Register |        |        | 64                         |  |

| SSPCON1                                            | WCOL       | SSPOV        | SSPEN         | CKP          | SSPM3        | SSPM2    | SSPM1  | SSPM0  | 64                         |  |

| SSPSTAT                                            | SMP        | CKE          | D/A           | Р            | S            | R/W      | UA     | BF     | 64                         |  |

## TABLE 17-2: REGISTERS ASSOCIATED WITH SPI OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

| Name    | Bit 7      | Bit 6        | Bit 5         | Bit 4        | Bit 3        | Bit 2    | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|------------|--------------|---------------|--------------|--------------|----------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL    | TMR0IE        | INT0IE       | RBIE         | TMR0IF   | INT0IF | RBIF   | 63                         |

| PIR1    | PSPIF      | ADIF         | RC1IF         | TX1IF        | SSPIF        | CCP1IF   | TMR2IF | TMR1IF | 65                         |

| PIE1    | PSPIE      | ADIE         | RC1IE         | TX1IE        | SSPIE        | CCP1IE   | TMR2IE | TMR1IE | 65                         |

| IPR1    | PSPIP      | ADIP         | RC1IP         | TX1IP        | SSPIP        | CCP1IP   | TMR2IP | TMR1IP | 65                         |

| TRISC   | PORTC Da   | ta Direction | Register      |              |              |          |        |        | 66                         |

| SSPBUF  | Master Syr | nchronous Se | erial Port Re | eceive Buffe | r/Transmit F | Register |        |        | 64                         |

| SSPADD  | Master Syr | hchronous Se | erial Port Re | eceive Buffe | r/Transmit F | Register |        |        | 64                         |

| SSPCON1 | WCOL       | SSPOV        | SSPEN         | CKP          | SSPM3        | SSPM2    | SSPM1  | SSPM0  | 64                         |

| SSPCON2 | GCEN       | ACKSTAT      | ACKDT         | ACKEN        | RCEN         | PEN      | RSEN   | SEN    | 64                         |

| SSPSTAT | SMP        | CKE          | D/Ā           | Р            | S            | R/W      | UA     | BF     | 64                         |

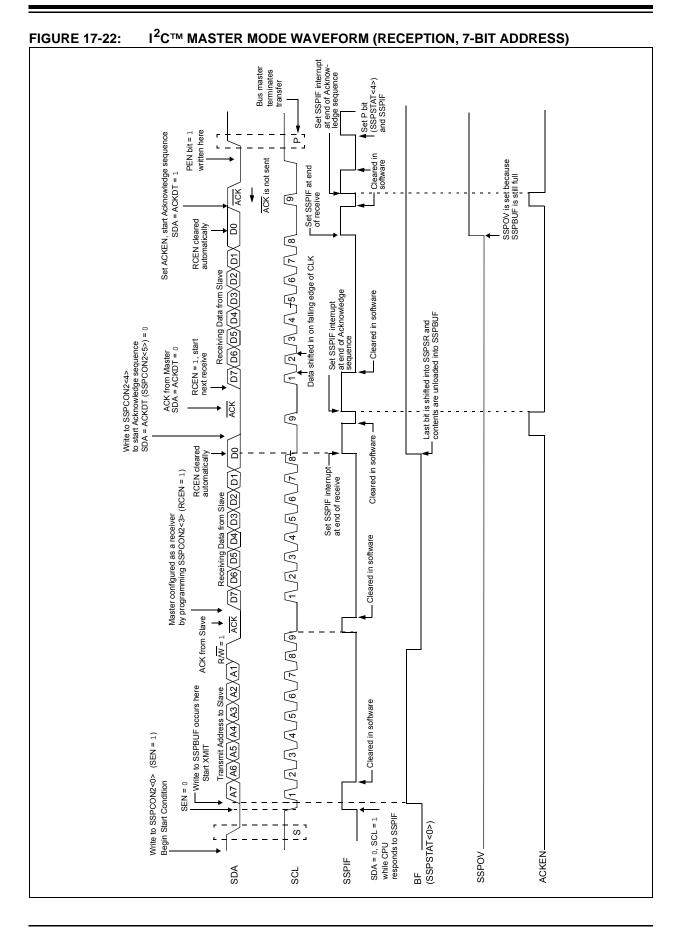

# TABLE 17-4: REGISTERS ASSOCIATED WITH I<sup>2</sup>C<sup>TM</sup> OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the MSSP in  $I^2C$  mode.

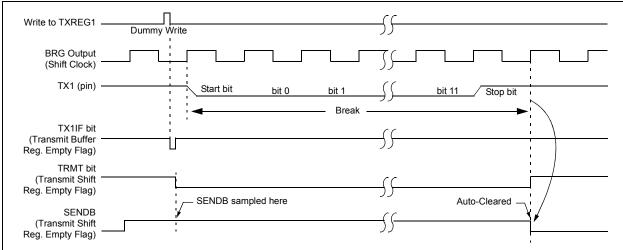

# 18.2.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG1 will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG1 for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-10 for the timing of the Break character sequence.

## 18.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG1 with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG1 to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG1 becomes empty, as indicated by the TX1IF bit, the next data byte can be written to TXREG1.

### 18.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 18.2.4** "**Auto-Wake-up on Sync Break Character**". By enabling this feature, the EUSART will sample the next two transitions on RX1/DT1, cause an RC1IF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TX1IF interrupt is observed.

## FIGURE 18-10: SEND BREAK CHARACTER SEQUENCE

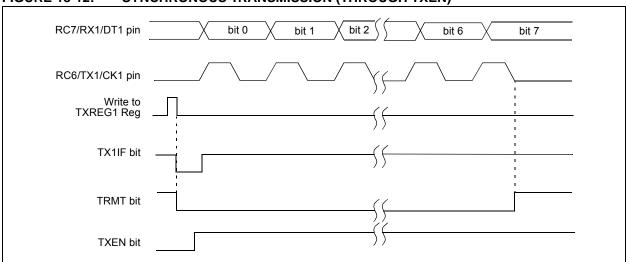

# FIGURE 18-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

# TABLE 18-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|----------|-------------|-------------|--------------|--------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 63                         |

| PIR1     | PSPIF    | ADIF        | RC1IF       | TX1IF        | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 65                         |

| PIE1     | PSPIE    | ADIE        | RC1IE       | TX1IE        | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 65                         |

| IPR1     | PSPIP    | ADIP        | RC1IP       | TX1IP        | SSPIP  | CCP1IP | TMR2IP | TMR1IP | 65                         |

| RCSTA1   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 65                         |

| TXREG1   | EUSART1  | Transmit Re | gister      |              |        |        |        |        | 65                         |

| TXSTA1   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 65                         |

| BAUDCON1 | ABDOVF   | RCIDL       | RXDTP       | TXCKP        | BRG16  | _      | WUE    | ABDEN  | 66                         |

| SPBRGH1  | EUSART1  | Baud Rate ( | Generator R | egister Higl | n Byte |        |        |        | 66                         |

| SPBRG1   | EUSART1  | Baud Rate ( | Generator R | egister Low  | / Byte |        |        |        | 65                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

# 19.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is very similar in function to the Enhanced USART module, discussed in the previous chapter. It is provided as an additional channel for serial communication with external devices, for those situations that do not require Auto-Baud Detection (ABD) or LIN/J2602 bus support.

The AUSART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

The pins of the AUSART module are multiplexed with the functions of PORTG (RG1/TX2/CK2 and RG2/RX2/DT2, respectively). In order to configure these pins as an AUSART:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISG<1> bit must be set (= 1) for Synchronous Slave mode

**Note:** The USART control will automatically reconfigure the pin from input to output as needed.

The operation of the Addressable USART module is controlled through two registers: TXSTA2 and RXSTA2. These are detailed in Register 19-1 and Register 19-2 respectively.

## REGISTER 19-2: RCSTA2: AUSART2 RECEIVE STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                            | R/W-0                                     | R/W-0                 | R/W-0             | R-0             | R-0               | R-x       |

|---------------|----------------------------------|-------------------------------------------|-----------------------|-------------------|-----------------|-------------------|-----------|

| SPEN          | RX9                              | SREN                                      | CREN                  | ADDEN             | FERR            | OERR              | RX9D      |

| bit 7         |                                  |                                           |                       |                   |                 |                   | bit       |

|               |                                  |                                           |                       |                   |                 |                   |           |

| Legend:       |                                  |                                           |                       |                   |                 |                   |           |

| R = Readabl   |                                  | W = Writable                              |                       | U = Unimpler      |                 |                   |           |

| -n = Value at | POR                              | '1' = Bit is set                          | t                     | '0' = Bit is clea | ared            | x = Bit is unkr   | iown      |

| bit 7         | SPEN: Seria                      | al Port Enable bi                         | it                    |                   |                 |                   |           |

|               |                                  | oort is enabled (o<br>oort is disabled (l |                       |                   | CKx pins as s   | serial port pins) |           |

| bit 6         | RX9: 9-Bit F                     | Receive Enable I                          | bit                   |                   |                 |                   |           |

|               |                                  | 9-bit reception<br>8-bit reception        |                       |                   |                 |                   |           |

| bit 5         | SREN: Sing                       | le Receive Enal                           | ole bit               |                   |                 |                   |           |

|               | <u>Asynchrono</u><br>Don't care. | <u>us mode</u> :                          |                       |                   |                 |                   |           |

|               | <u>Synchronou</u>                | s mode – Maste                            | er:                   |                   |                 |                   |           |

|               |                                  | s single receive                          |                       |                   |                 |                   |           |

|               |                                  | s single receive<br>eared after rece      |                       | ete               |                 |                   |           |

|               |                                  | s mode – Slave                            |                       |                   |                 |                   |           |

|               | Don't care.                      |                                           | <u>-</u>              |                   |                 |                   |           |

| bit 4         | CREN: Con                        | tinuous Receive                           | Enable bit            |                   |                 |                   |           |

|               | <u>Asynchrono</u>                |                                           |                       |                   |                 |                   |           |

|               | 1 = Enable                       |                                           |                       |                   |                 |                   |           |

|               | 0 = Disable                      |                                           |                       |                   |                 |                   |           |

|               | <u>Synchronou</u>                |                                           | oivo until ona        | hla hit CREN i    | e cleared (CE   | EN overrides SF   |           |

|               |                                  | s continuous red                          |                       | DIE DIL, CINEN, I | s cleared (Cr   | LIN OVERINGES OF  | (LIN)     |

| bit 3         | ADDEN: Ac                        | ldress Detect Er                          | able bit              |                   |                 |                   |           |

|               |                                  | <u>us mode 9-Bit (</u> F                  |                       |                   |                 |                   |           |

|               |                                  |                                           |                       |                   |                 | e buffer when R   |           |

|               |                                  |                                           | -                     | are received ar   | id ninth bit ca | n be used as a p  | arity bit |

|               | Asynchrono<br>Don't care.        | us mode 9-Bit (F                          | <del>RX9 = 0)</del> : |                   |                 |                   |           |

| bit 2         |                                  | ning Error bit                            |                       |                   |                 |                   |           |

|               |                                  | g error (can be ι                         | pdated by rea         | ading RCREG1      | register and r  | eceiving next va  | lid byte) |

| bit 1         |                                  | rrun Error bit                            |                       |                   |                 |                   |           |

|               | 1 = Overru                       | n error (can be c                         | leared by clea        | aring bit, CREN)  | )               |                   |           |

|               |                                  | rrun error                                |                       |                   |                 |                   |           |

| bit 0         |                                  | rrun error<br>bit of Received D           | )ata bit              |                   |                 |                   |           |

R/W-0

ADCS0

bit 0

#### **REGISTER 20-3:** ADCON2: A/D CONTROL REGISTER 2 R/W-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 ADFM ACQT2 ACQT1 ACQT0 ADCS2 ADCS1 \_\_\_\_\_ bit 7 Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 ADFM: A/D Result Format Select bit 1 = Right justified 0 = Left justified bit 6 Unimplemented: Read as '0' ACQT<2:0>: A/D Acquisition Time Select bits bit 5-3 111 = 20 TAD 110 = 16 TAD 101 = 12 TAD 100 **= 8** TAD 011 = 6 TAD 010 = 4 TAD 001 = 2 TAD

ADCS<2:0>: A/D Conversion Clock Select bits 111 = FRC (clock derived from A/D RC oscillator)<sup>(1)</sup>

011 = FRC (clock derived from A/D RC oscillator)<sup>(1)</sup>

**Note 1:** If the A/D FRC clock source is selected, a delay of one TCY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

000 = 0 TAD<sup>(1)</sup>

110 = Fosc/64 101 = Fosc/16 100 = Fosc/4

010 = Fosc/32 001 = Fosc/8 000 = Fosc/2

bit 2-0

NOTES:

# 23.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

# 23.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |  |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|----------------------------|--|

| HLVDCON | VDIRMAG  |           | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 | 64                         |  |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   | 63                         |  |

| PIR2    | OSCFIF   | CMIF      | —      | _      | BCLIF  | HLVDIF | TMR3IF | CCP2IF | 65                         |  |

| PIE2    | OCSFIE   | CMIE      | _      | —      | BCLIE  | HLVDIE | TMR3IE | CCP2IE | 65                         |  |

| IPR2    | OSCFIP   | CMIP      | _      | _      | BCLIP  | HLVDIP | TMR3IP | CCP2IP | 65                         |  |

## TABLE 23-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

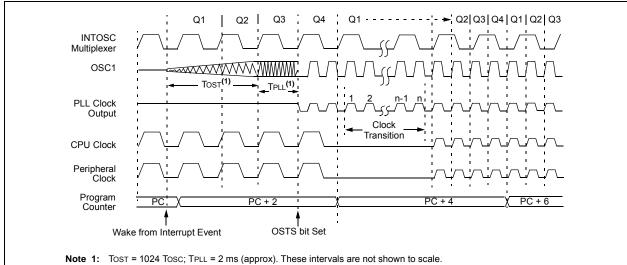

# 24.3 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period from oscillator start-up to code execution by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is LP, XT, HS or HSPLL (Crystal-Based modes). Other sources do not require a OST start-up delay; for these, Two-Speed Start-up should be disabled.

When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF<2:0>, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF<2:0> bits prior to entering Sleep mode. In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

## 24.3.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to **Section 4.1.2 "Entering Power-Managed Modes"**). In practice, this means that user code can change the SCS<1:0> bits setting or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

# FIGURE 24-2: TIMING TRANSITION FOR TWO-SPEED START-UP (INTOSC TO HSPLL)

| Byte-oriented file register operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Example Instruction       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 15 10 9 8 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ADDWF MYREG, W, B         |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                                                                                                                                                                                                                                                                                                             |                           |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| 15 12 11 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MOVFF MYREG1, MYREG2      |

| 15 12 11 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                           |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                           |

| f = 12-bit file register address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |

| Bit-oriented file register operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| <u>15 12 11 9 8 7 0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BSF MYREG, bit, B         |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |

| Literal operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| OPCODE k (literal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MOVLW 7Fh                 |

| k = 8-bit immediate value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| Control operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                           |

| Control operations<br>CALL, GOTO and Branch operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GOTO Label                |

| CALL, GOTO and Branch operations15870OPCODEn<7:0> (literal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1                                                                                                                                                                                                                                                                                                                                                                                                                                       | GOTO Label                |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       1       1                                                                                                                                                                                                                                                                                                                                                                                    | GOTO Label<br>CALL MYFUNC |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE       n<7:0> (literal)         15       12 11       0         1111       n<19:8> (literal)         n = 20-bit immediate value         15       8 7       0                                                                                                                                                                                                                                                                                                                                                                                           |                           |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       15       8       7       0         OPCODE       S       n<7:0> (literal)       1                                                                                                                                                                                                                                                                                                             |                           |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE       n<7:0> (literal)         15       12       11       0         1111       n<19:8> (literal)       1         n = 20-bit immediate value       15       8 7       0         15       8 7       0       0       0         15       8 7       0       0       0         15       8 7       0       0       0         15       12       11       0       0                                                                                                                                                                                           |                           |

| CALL, GOTO and Branch operations         15       8 7       0         OPCODE $n<7:0>$ (literal)         15       12 11       0         1111 $n<19:8>$ (literal)         n = 20-bit immediate value         15       8 7       0         OPCODE       S $n<7:0>$ (literal)         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         15       12 11       0         S = Fast bit       S = Fast bit                                                                                        |                           |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE $n<7:0>$ (literal)       15       12       11       0         15       12       11       0       1111 $n<19:8>$ (literal)         n = 20-bit immediate value       15       8       7       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         1111 $n<19:8>$ (literal)       0         15       11       10       0 |                           |

| CALL, GOTO and Branch operations15870 $OPCODE$ $n<7:0>$ (literal)15121101111 $n<19:8>$ (literal)n = 20-bit immediate value15870 $OPCODE$ S $n<7:0>$ (literal)15121101111 $n<19:8>$ (literal)S = Fast bit1511100 $OPCODE$ $n<10:0>$ (literal)                                                                                                                                                                                                                                                                                                                                                                                      | CALL MYFUNC               |

| CALL, GOTO and Branch operations         15       8       7       0         OPCODE $n<7:0>$ (literal)       15       12       11       0         15       12       11       0       1111 $n<19:8>$ (literal)         n = 20-bit immediate value       15       8       7       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         15       12       11       0         1111 $n<19:8>$ (literal)       0         15       11       10       0 | CALL MYFUNC               |

| BCF                       | Bit Clear f                                                                                                          | F                              |                                                                                                           | BN           |                                | Branch if                                                                                              | Negative                                                                            |                                                        |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|--------------|--------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------|

| Syntax:                   | BCF f, b                                                                                                             | {,a}                           |                                                                                                           | Synta        | ax:                            | BN n                                                                                                   |                                                                                     |                                                        |

| Operands:                 | $0 \le f \le 255$                                                                                                    |                                |                                                                                                           | Oper         | ands:                          | -128 ≤ n ≤ ′                                                                                           | 127                                                                                 |                                                        |

| ·                         | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                        |                                |                                                                                                           | •            | ation:                         | if Negative<br>(PC) + 2 + 2                                                                            | ,                                                                                   |                                                        |

| Operation:                | $0 \rightarrow f < b >$                                                                                              |                                |                                                                                                           | Statu        | s Affected:                    | None                                                                                                   |                                                                                     |                                                        |

| Status Affected:          | None                                                                                                                 |                                |                                                                                                           | Enco         | ding:                          | 1110                                                                                                   | 0110 nn                                                                             | nn nnnn                                                |

| Encoding:<br>Description: | If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enabl<br>in Indexed L<br>mode when | ne BSR is use<br>nd the extend | ared.<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See | Desc         | ription:<br>Is:                | program wi<br>The 2's con<br>added to the<br>incremente<br>instruction,<br>PC + 2 + 2r<br>two-cycle in | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | nber '2n' is<br>ne PC will have<br>next<br>ess will be |

| Words:                    | 1                                                                                                                    |                                |                                                                                                           | Cycle        |                                | 1(2)                                                                                                   |                                                                                     |                                                        |

| Cycles:                   | 1                                                                                                                    |                                |                                                                                                           | Q C<br>If Ju | ycle Activity:<br>mp:          |                                                                                                        |                                                                                     |                                                        |

| Q Cycle Activity:         |                                                                                                                      |                                |                                                                                                           |              | Q1                             | Q2                                                                                                     | Q3                                                                                  | Q4                                                     |

| Q1<br>Decode              | Q2<br>Read                                                                                                           | Q3<br>Process                  | Q4<br>Write                                                                                               |              | Decode                         | Read literal<br>'n'                                                                                    | Process<br>Data                                                                     | Write to PC                                            |

|                           | register 'f'                                                                                                         | Data                           | register 'f'                                                                                              |              | No<br>operation                | No<br>operation                                                                                        | No<br>operation                                                                     | No<br>operation                                        |

| Example:                  | BCF F                                                                                                                | LAG_REG,                       | 7, 0                                                                                                      | lf No        | o Jump:                        |                                                                                                        |                                                                                     |                                                        |

| Before Instruc            | tion                                                                                                                 |                                |                                                                                                           |              | Q1                             | Q2                                                                                                     | Q3                                                                                  | Q4                                                     |

| After Instruction         | EG = C7h<br>on<br>EG = 47h                                                                                           |                                |                                                                                                           |              | Decode                         | Read literal<br>'n'                                                                                    | Process<br>Data                                                                     | No<br>operation                                        |

| _                         |                                                                                                                      |                                |                                                                                                           | Exan         | <u>nple:</u><br>Before Instrue | HERE                                                                                                   | BN Jump                                                                             | >                                                      |

|                           |                                                                                                                      |                                |                                                                                                           |              | PC<br>After Instructi          | = ad<br>on                                                                                             | dress (HERE                                                                         | )                                                      |

If Negative PC If Negative PC

= = =

1; address (Jump) 0; address (HERE + 2)

| LFS         | R                                                   | Load FS                                                            | Load FSR                                                             |                            |                                       |  |  |  |  |

|-------------|-----------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------|---------------------------------------|--|--|--|--|

| Synta       | ax:                                                 | LFSR f,                                                            | LFSR f, k                                                            |                            |                                       |  |  |  |  |

| Oper        | ands:                                               | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 4095 \end{array}$ |                            |                                       |  |  |  |  |

| Oper        | ation:                                              | $k \rightarrow FSRf$                                               | $k \rightarrow FSRf$                                                 |                            |                                       |  |  |  |  |

| Statu       | s Affected:                                         | None                                                               |                                                                      |                            |                                       |  |  |  |  |

| Encoding:   |                                                     | 1110<br>1111                                                       | 1110<br>0000                                                         | 00ff<br>k <sub>7</sub> kkk | k <sub>11</sub> kkk<br>kkkk           |  |  |  |  |

| Desc        | ription:                                            | The 12-bit file select                                             |                                                                      |                            |                                       |  |  |  |  |

| Words:      |                                                     | 2                                                                  |                                                                      |                            |                                       |  |  |  |  |

| Cycles:     |                                                     | 2                                                                  | 2                                                                    |                            |                                       |  |  |  |  |

| QC          | ycle Activity:                                      |                                                                    |                                                                      |                            |                                       |  |  |  |  |

|             | Q1                                                  | Q2                                                                 | Q3                                                                   |                            | Q4                                    |  |  |  |  |

|             | Decode                                              | Read literal<br>'k' MSB                                            | Proce<br>Data                                                        | a li                       | Write<br>teral 'k'<br>VSB to<br>FSRfH |  |  |  |  |

|             | Decode                                              | Read literal<br>'k' LSB                                            | Proce<br>Data                                                        |                            | rite literal<br>to FSRfL              |  |  |  |  |

| <u>Exan</u> | n <u>ple:</u><br>After Instructio<br>FSR2H<br>FSR2L | = 0                                                                | 3ABh<br>3h<br>Bh                                                     |                            |                                       |  |  |  |  |

| MOVF                                         | Move f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                           |                                    |           |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------|-----------|

| Syntax:                                      | MOVF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           |                                    |           |

| Operands:                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           |                                    |           |

| Operation:                                   | $f \to \text{dest}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           |                                    |           |

| Status Affected:                             | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                           |                                    |           |

| Encoding:                                    | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00da                                                      | ffff                               | ffff      |

|                                              | a destination dependent upon the<br>status of 'd'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. Location 'f'<br>can be anywhere in the 256-byte bank.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br><b>Section 25.2.3</b> for details |                                                           |                                    |           |

|                                              | mode wher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ever f≤                                                   | 95 (5Fh).                          | •         |

| Words:                                       | mode wher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ever f≤                                                   | 95 (5Fh).                          | •         |

| Words:<br>Cycles:                            | mode wher<br>Section 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ever f≤                                                   | 95 (5Fh).                          | •         |