Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 70                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8410-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

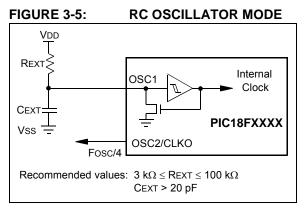

# 3.4 RC Oscillator

For timing-insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The actual oscillator frequency is a function of several factors:

- · Supply voltage

- Values of the external resistor (REXT) and capacitor (CEXT)

- · Operating temperature

Given the same device, operating voltage and temperature and component values, there will also be unit-to-unit frequency variations. These are due to factors such as:

- Normal manufacturing variation

- Difference in lead frame capacitance between package types (especially for low CEXT values)

- Variations within the tolerance of limits of  $\ensuremath{\mathsf{REXT}}$  and  $\ensuremath{\mathsf{CEXT}}$

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic. Figure 3-5 shows how the R/C combination is connected.

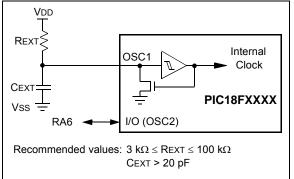

The RCIO Oscillator mode (Figure 3-6) functions like the RC mode, except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

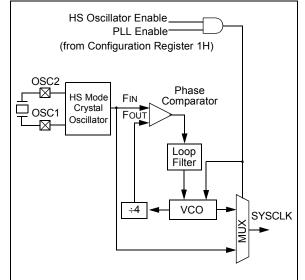

# 3.5 PLL Frequency Multiplier

A Phase Locked Loop (PLL) circuit is provided as an option for users who want to use a lower frequency oscillator circuit, or to clock the device up to its highest rated frequency from a crystal oscillator. This may be useful for customers who are concerned with EMI due to high-frequency crystals, or users who require higher clock speeds from an internal oscillator.

### 3.5.1 HSPLL OSCILLATOR MODE

The HSPLL mode makes use of the HS Oscillator mode for frequencies up to 10 MHz. A PLL then multiplies the oscillator output frequency by 4 to produce an internal clock frequency up to 40 MHz.

The PLL is only available to the crystal oscillator when the FOSC<3:0> Configuration bits are programmed for HSPLL mode (= 0110).

### FIGURE 3-7: PLL BLOCK DIAGRAM (HS MODE)

### 3.5.2 PLL AND INTOSC

The PLL is also available to the internal oscillator block in selected oscillator modes. In this configuration, the PLL is enabled in software and generates a clock output of up to 32 MHz. The operation of INTOSC with the PLL is described in **Section 3.6.4 "PLL in INTOSC Modes"**.

### 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator block using the INTOSC multiplexer and the primary clock is shut down. When using the INTRC source, this mode provides the best power conservation of all the Run modes, while still executing code. It works well for user applications which are not highly timing-sensitive, or do not require high-speed clocks at all times.

If the primary clock source is the internal oscillator block (either INTRC or INTOSC), there are no distinguishable differences between PRI\_RUN and RC\_RUN modes during execution. However, a clock switch delay will occur during entry to and exit from RC\_RUN mode. Therefore, if the primary clock source is the internal oscillator block, the use of RC\_RUN mode is not recommended.

This mode is entered by setting the SCS1 bit to '1'. Although it is ignored, it is recommended that the SCS0 bit also be cleared; this is to maintain software compatibility with future devices. When the clock source is switched to the INTOSC multiplexer (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared. The IRCF bits may be modified at any time to immediately change the clock speed.

Note: Caution should be used when modifying a single IRCF bit. If VDD is less than 3V, it is possible to select a higher clock speed than is supported by the low VDD. Improper device operation may result if the VDD/Fosc specifications are violated.

If the IRCF bits and the INTSRC bit are all clear, the INTOSC output is not enabled and the IOFS bit will remain clear; there will be no indication of the current clock source. The INTRC source is providing the device clocks.

If the IRCF bits are changed from all clear (thus, enabling the INTOSC output), or if INTSRC is set, the IOFS bit becomes set after the INTOSC output becomes stable. Clocks to the device continue while the INTOSC source stabilizes after an interval of TIOBST.

If the IRCF bits were previously at a non-zero value, or if INTSRC was set before setting SCS1 and the INTOSC source was already stable, the IOFS bit will remain set.

On transitions from RC\_RUN mode to PRI\_RUN, the device continues to be clocked from the INTOSC multiplexer while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the IOFS bit is cleared, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

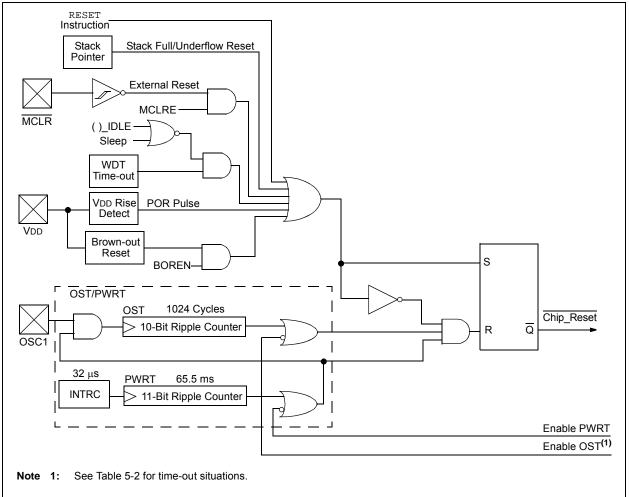

# 5.0 RESET

The PIC18F6310/6410/8310/8410 devices differentiate between various kinds of Reset:

- a) Power-on Reset (POR)

- b) MCLR Reset during normal operation

- c) MCLR Reset during power-managed modes

- d) Watchdog Timer (WDT) Reset (during execution)

- e) Programmable Brown-out Reset (BOR)

- f) RESET Instruction

- g) Stack Full Reset

- h) Stack Underflow Reset

This section discusses Resets generated by MCLR, POR and BOR and covers the operation of the various start-up timers. Stack Reset events are covered in Section 6.1.3.4 "Stack Full and Underflow Resets". WDT Resets are covered in Section 24.2 "Watchdog Timer (WDT)".

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 5-1.

# 5.1 RCON Register

Device Reset events are tracked through the RCON register (Register 5-1). The lower five bits of the register indicate that a specific Reset event has occurred. In most cases, these bits can only be set by the event and must be cleared by the application after the event. The state of these flag bits, taken together, can be read to indicate the type of Reset that just occurred. This is described in more detail in **Section 5.6 "Reset State of Registers"**.

The RCON register also has control bits for setting interrupt priority (IPEN) and software control of the BOR (SBOREN). Interrupt priority is discussed in Section 10.0 "Interrupts". BOR is covered in Section 5.4 "Brown-out Reset (BOR)".

### FIGURE 5-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 6.1.2 PROGRAM COUNTER

The Program Counter (PC) specifies the address of the instruction to fetch for execution. The PC is 21 bits wide and is contained in three separate 8-bit registers. The low byte, known as the PCL register, is both readable and writable. The high byte, or PCH register, contains the PC<15:8> bits; it is not directly readable or writable. Updates to the PCH register are performed through the PCLATH register. The upper byte is called PCU. This register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCH register. Updates to the PCU register are performed through the PCLATH register contains the PC<20:16> bits; it is also not directly readable or writable. Updates to the PCU register are performed through the PCLATU register.

The contents of PCLATH and PCLATU are transferred to the program counter by any operation that writes PCL. Similarly, the upper two bytes of the program counter are transferred to PCLATH and PCLATU by an operation that reads PCL. This is useful for computed offsets to the PC (see **Section 6.1.5.1 "Computed GOTO"**).

The PC addresses bytes in the program memory. To prevent the PC from becoming misaligned with word instructions, the Least Significant bit of PCL is fixed to a value of '0'. The PC increments by 2 to address sequential instructions in the program memory.

The CALL, RCALL, GOTO and program branch instructions write to the program counter directly. For these instructions, the contents of PCLATH and PCLATU are not transferred to the program counter.

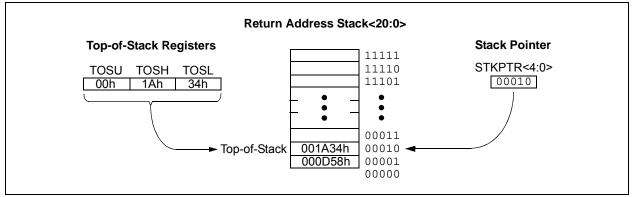

### 6.1.3 RETURN ADDRESS STACK

The Return Address Stack allows any combination of up to 31 program calls and interrupts to occur. The PC is pushed onto the stack when a CALL or RCALL instruction is executed, or an interrupt is Acknowledged. The PC value is pulled off the stack on a RETURN, RETLW or a RETFIE instruction. PCLATU and PCLATH are not affected by any of the RETURN or CALL instructions. The stack operates as a 31-word by 21-bit RAM and a 5-bit Stack Pointer register, STKPTR. The stack space is not part of either program or data space. The Stack Pointer is readable and writable and the address on the top of the stack is readable and writable through the Top-of-Stack (TOS) Special File Registers. Data can also be pushed to or popped from the stack using these registers.

A CALL type instruction causes a push onto the stack; the Stack Pointer is first incremented and the location pointed to by the Stack Pointer is written with the contents of the PC (already pointing to the instruction following the CALL). A RETURN type instruction causes a pop from the stack; the contents of the location pointed to by the STKPTR are transferred to the PC and then the Stack Pointer is decremented.

The Stack Pointer is initialized to '00000' after all Resets. There is no RAM associated with the location corresponding to a Stack Pointer value of '00000'; this is only a Reset value. Status bits indicate if the stack is full, has overflowed or has underflowed.

### 6.1.3.1 Top-of-Stack Access

Only the top of the Return Address Stack (TOS) is readable and writable. A set of three registers, TOSU:TOSH:TOSL, hold the contents of the stack location pointed to by the STKPTR register (Figure 6-3). This allows users to implement a software stack if necessary. After a CALL, RCALL or interrupt, the software can read the pushed value by reading the TOSU:TOSH:TOSL registers. These values can be placed on a user-defined software stack. At return time, the software can return these values to TOSU:TOSH:TOSL and do a return.

The user must disable the global interrupt enable bits while accessing the stack to prevent inadvertent stack corruption.

### FIGURE 6-3: RETURN ADDRESS STACK AND ASSOCIATED REGISTERS

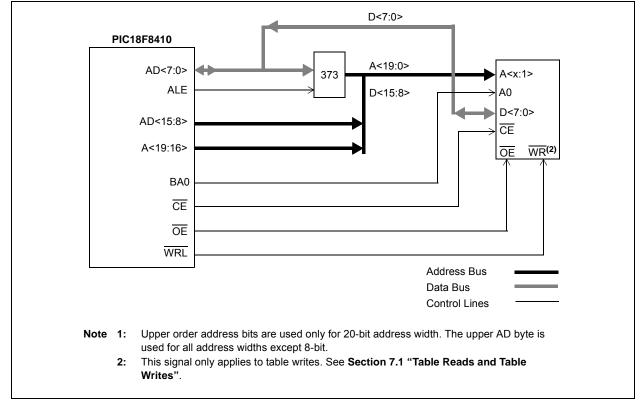

### 8.3 8-Bit Mode

The external memory interface implemented in PIC18F8410 devices operates only in 8-Bit Multiplexed mode; data shares the 8 Least Significant bits of the address bus.

Figure 8-1 shows an example of 8-Bit Multiplexed mode for PIC18F8410 devices. This mode is used for a single 8-bit memory connected for 16-bit operation. The instructions will be fetched as two 8-bit bytes on a shared data/address bus. The two bytes are sequentially fetched within one instruction cycle (TcY). Therefore, the designer must choose external memory devices according to timing calculations based on 1/2 TcY (2 times the instruction rate). For proper memory speed selection, glue logic propagation delay times must be considered along with setup and hold times.

The Address Latch Enable (ALE) pin indicates that the address bits, A<15:0>, are available on the external memory interface bus. The Output Enable signal ( $\overline{OE}$ ) will enable one byte of program memory for a portion of the instruction cycle, then BA0 will change and the second byte will be enabled to form the 16-bit instruction word. The Least Significant bit of the address, BA0, must be connected to the memory devices in this mode. The Chip Enable signal ( $\overline{CE}$ ) is active at any time that the microcontroller accesses external memory, whether reading or writing; it is inactive (asserted high) whenever the device is in Sleep mode.

This generally includes basic EPROM and Flash devices. It allows table writes to byte-wide external memories.

During a TBLWT instruction cycle, the TABLAT data is presented on the upper and lower bytes of the AD<15:0> bus. The appropriate level of the BA0 control line is strobed on the LSb of the TBLPTR.

### FIGURE 8-7: 8-BIT MULTIPLEXED MODE EXAMPLE

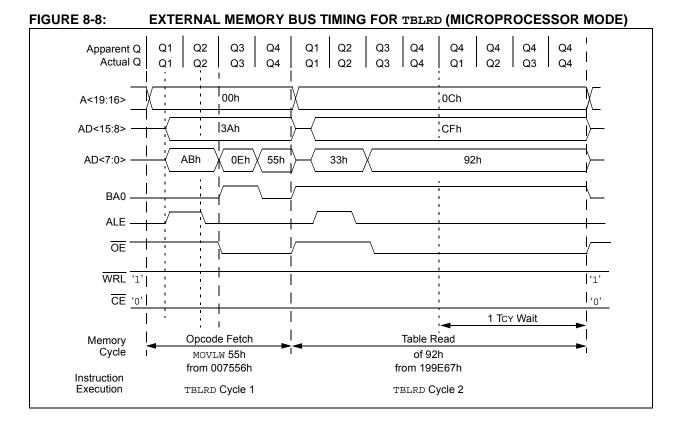

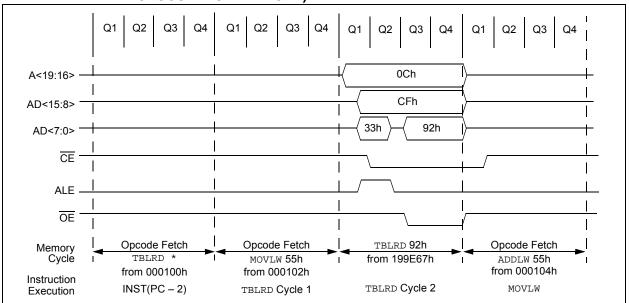

### 8.3.1 8-BIT MODE TIMING

The presentation of control signals on the external memory bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 8-4 through Figure 8-6.

# FIGURE 8-9: EXTERNAL MEMORY BUS TIMING FOR TBLRD (EXTENDED MICROCONTROLLER MODE)

| TABLE 11-7:  | PORTD              |                 |     |             |                                                                      |

|--------------|--------------------|-----------------|-----|-------------|----------------------------------------------------------------------|

| Pin Name     | Function           | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                          |

| RD0/AD0/PSP0 | RD0                | 0               | 0   | DIG         | LATD<0> data output.                                                 |

|              |                    | 1               | I   | ST          | PORTD<0> data input.                                                 |

|              | AD0 <sup>(2)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 0 output. <sup>(1)</sup> |

|              |                    | х               | Ι   | TTL         | External memory interface, Data Bit 0 input. <sup>(1)</sup>          |

|              | PSP0               | х               | 0   | DIG         | PSP read data output (LATD<0>); takes priority over port data.       |

|              |                    | х               | Ι   | TTL         | PSP write data input.                                                |

| RD1/AD1/PSP1 | RD1                | 0               | 0   | DIG         | LATD<1> data output.                                                 |

|              |                    | 1               | I   | ST          | PORTD<1> data input.                                                 |

|              | AD1 <sup>(2)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 1 output. <sup>(1)</sup> |

|              |                    | х               | I   | TTL         | External memory interface, Data Bit 1 input. <sup>(1)</sup>          |

|              | PSP1               | х               | 0   | DIG         | PSP read data output (LATD<1>); takes priority over port data.       |

|              |                    | x               | I   | TTL         | PSP write data input.                                                |

| RD2/AD2/PSP2 | RD2                | 0               | 0   | DIG         | LATD<2> data output.                                                 |

|              |                    | 1               | I   | ST          | PORTD<2> data input.                                                 |

|              | AD2 <sup>(2)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 2 output. <sup>(1)</sup> |

|              |                    | х               | I   | TTL         | External memory interface, Data Bit 2 input. <sup>(1)</sup>          |

|              | PSP2               | х               | 0   | DIG         | PSP read data output (LATD<2>); takes priority over port data.       |

|              |                    | х               | I   | TTL         | PSP write data input.                                                |

| RD3/AD3/PSP3 | RD3                | 0               | 0   | DIG         | LATD<3> data output.                                                 |

|              |                    | 1               | I   | ST          | PORTD<3> data input.                                                 |

|              | AD3 <sup>(2)</sup> | х               | 0   | DIG         | External memory interface, Address/Data Bit 3 output. <sup>(1)</sup> |

|              |                    | х               | I   | TTL         | External memory interface, Data Bit 3 input. <sup>(1)</sup>          |

|              | PSP3               | х               | 0   | DIG         | PSP read data output (LATD<3>); takes priority over port data.       |

|              |                    | х               | I   | TTL         | PSP write data input.                                                |

| RD4/AD4/PSP4 | RD4                | 0               | 0   | DIG         | LATD<4> data output.                                                 |

|              |                    | 1               | I   | ST          | PORTD<4> data input.                                                 |

|              | AD4 <sup>(2)</sup> | x               | 0   | DIG         | External memory interface, Address/Data Bit 4 output. <sup>(1)</sup> |

|              |                    | x               | I   | TTL         | External memory interface, Data Bit 4 input. <sup>(1)</sup>          |

|              | PSP4               | x               | 0   | DIG         | PSP read data output (LATD<4>); takes priority over port data.       |

|              |                    | x               | I   | TTL         | PSP write data input.                                                |

| RD5/AD5/PSP5 | RD5                | 0               | 0   | DIG         | LATD<5> data output.                                                 |

|              | -                  | 1               | -   | ST          | PORTD<5> data input.                                                 |

|              | AD5 <sup>(2)</sup> | x               | 0   | DIG         | External memory interface, Address/Data Bit 5 output. <sup>(1)</sup> |

|              |                    | x               |     | TTL         | External memory interface, Data Bit 5 input. <sup>(1)</sup>          |

|              | PSP5               | x               | 0   | DIG         | PSP read data output (LATD<5>); takes priority over port data.       |

|              |                    | x               | I   | TTL         | PSP write data input.                                                |

| RD6/AD6/PSP6 | RD6                | 0               | 0   | DIG         | LATD<6> data output.                                                 |

| -            |                    | 1               | I   | ST          | PORTD<6> data input.                                                 |

|              | AD6 <sup>(2)</sup> | x               | 0   | DIG-3       | External memory interface, Address/Data Bit 6 output. <sup>(1)</sup> |

|              |                    | x               |     | TTL         | External memory interface, Data Bit 6 input. <sup>(1)</sup>          |

|              |                    | -               |     |             |                                                                      |

|              | PSP6               | х               | 0   | DIG         | PSP read data output (LATD<6>); takes priority over port data.       |

TABLE 11-7: PORTD FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option). Note 1: External memory interface I/O takes priority over all other digital and PSP I/O.

**2:** Implemented on 80-pin devices only.

# 11.7 PORTG, TRISG and LATG Registers

PORTG is a 6-bit wide, bidirectional port. The corresponding Data Direction register is TRISG. Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., put the contents of the output latch on the selected pin).

The Output Latch register (LATG) is also memory mapped. Read-modify-write operations on the LATG register, read and write the latched output value for PORTG.

PORTG is multiplexed with USART functions (Table 11-13). PORTG pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTG pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register without concern due to peripheral overrides. The sixth pin of PORTG (RG5/MCLR/VPP) is an input only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin (MCLRE = 0), it functions as a digital input only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RG5 also functions as the programming voltage input during programming.

| Note: | On a Power-on Reset, RG5 is enabled as      |

|-------|---------------------------------------------|

|       | a digital input only if Master Clear        |

|       | functionality is disabled. All other 5 pins |

|       | are configured as digital inputs.           |

| EXAMP | LE 11-7 | INITIALIZING PORTG       |

|-------|---------|--------------------------|

| CLRF  | PORTG   | ; Initialize PORTG by    |

|       |         | ; clearing output        |

|       |         | ; data latches           |

| CLRF  | LATG    | ; Alternate method       |

|       |         | ; to clear output        |

|       |         | ; data latches           |

| MOVLW | 0x04    | ; Value used to          |

|       |         | ; initialize data        |

|       |         | ; direction              |

| MOVWF | TRISG   | ; Set RG1:RG0 as outputs |

|       |         | ; RG2 as input           |

|       |         | ; RG4:RG3 as inputs      |

### 16.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

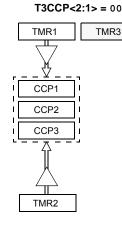

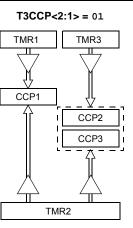

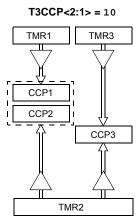

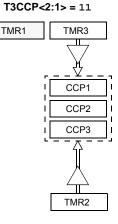

#### 16.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

### TABLE 16-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource   |

|----------|------------------|

| Capture  | Timer1 or Timer3 |

| Compare  | Timer1 or Timer3 |

| PWM      | Timer2           |

The assignment of a particular timer to a module is determined by the Timer-to-CCP enable bits in the T3CON register (Register 15-1). All three modules may be active at any given time and may share the same

timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time.

Depending on the configuration selected, up to three timers may be active at once, with modules in the same configuration (Capture/Compare or PWM) sharing timer resources. The possible configurations are shown in Figure 16-1.

### 16.1.2 CCP2 PIN ASSIGNMENT

The CCP2MX Configuration bit determines if CCP2 is multiplexed to its default or alternate assignment. By default, CCP2 is assigned to RC1 (CCP2MX = 1). If CCP2MX is cleared, CCP2 is multiplexed with either RE7 or RB3 (RE7 is the only alternative assignment for 64-pin devices).

For any device in Microcontroller mode, the alternate CCP2 assignment is RE7. For 80-pin devices in Microcoprocessor, Extended Microcontroller or Microcontroller with Boot Block mode, the alternate assignment is RB3. Note that RE7 is the only alternative assignment for 64-pin devices.

Changing the pin assignment of CCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for CCP2 operation, regardless of where it is located.

### FIGURE 16-1: CCP AND TIMER INTERCONNECT CONFIGURATIONS

Timer1 is used for all Capture and Compare operations for all three CCP modules. Timer2 is used for PWM operations for all three CCP modules. Timer3 is not used.

All modules may share Timer1 and Timer2 resources as common time bases.

Timer1 is used for Capture and Compare operations for CCP1 and Timer 3 is used for CCP2 and CCP3.

All three modules share Timer2 as a common time base for PWM operation.

Timer1 is used for Capture and Compare operations for CCP1 and CCP2. Timer 3 is used for CCP3.

All three modules share Timer2 as a common time base for PWM operation.

Timer3 is used for all Capture and Compare operations for all three CCP modules. Timer2 is used for PWM operations for all three CCP modules. Timer1 is not used.

All modules may share Timer2 and Timer3 resources as common time bases.

| Name    | Bit 7      | Bit 6          | Bit 5        | Bit 4         | Bit 3        | Bit 2      | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|---------|------------|----------------|--------------|---------------|--------------|------------|--------|--------|----------------------------|

| INTCON  | GIE/GIEH   | PEIE/GIEL      | TMR0IE       | INT0IE        | RBIE         | TMR0IF     | INT0IF | RBIF   | 63                         |

| RCON    | IPEN       | SBOREN         | _            | RI            | TO           | PD         | POR    | BOR    | 64                         |

| PIR1    | PSPIF      | ADIF           | RC1IF        | TX1IF         | SSPIF        | CCP1IF     | TMR2IF | TMR1IF | 65                         |

| PIE1    | PSPIE      | ADIE           | RC1IE        | TX1IE         | SSPIE        | CCP1IE     | TMR2IE | TMR1IE | 65                         |

| IPR1    | PSPIP      | ADIP           | RC1IP        | TX1IP         | SSPIP        | CCP1IP     | TMR2IP | TMR1IP | 65                         |

| PIR2    | OSCFIF     | CMIF           | _            | _             | BCLIF        | HLVDIF     | TMR3IF | CCP2IF | 65                         |

| PIE2    | OSCFIE     | CMIE           |              | _             | BCLIE        | HLVDIE     | TMR3IE | CCP2IE | 65                         |

| IPR2    | OSCFIP     | CMIP           | _            | _             | BCLIP        | HLVDIP     | TMR3IP | CCP2IP | 65                         |

| PIR3    | —          | _              | RC2IF        | TX2IF         | _            | _          | _      | CCP3IF | 65                         |

| PIE3    | _          | _              | RC2IE        | TX2IE         |              | _          | _      | CCP3IE | 65                         |

| IPR3    | —          | _              | RC2IP        | TX2IP         |              | _          | _      | CCP3IP | 65                         |

| TRISB   | PORTB Da   | ata Direction  | Register     |               |              |            |        |        | 66                         |

| TRISC   | PORTC Da   | ata Direction  | Register     |               |              |            |        |        | 66                         |

| TRISE   | PORTE Da   | ata Direction  | Register     |               |              |            |        |        | 66                         |

| TMR1L   | Holding Re | gister for the | e Least Sigr | nificant Byte | of the 16-B  | it TMR1 Re | gister |        | 64                         |

| TMR1H   | Holding Re | gister for the | e Most Sign  | ificant Byte  | of the 16-Bi | t TMR1 Reg | gister |        | 64                         |

| T1CON   | RD16       | T1RUN          | T1CKPS1      | T1CKPS0       | T1OSCEN      | T1SYNC     | TMR1CS | TMR10N | 64                         |

| TMR3H   | Timer3 Reg | gister High E  | Byte         |               |              |            |        |        | 65                         |

| TMR3L   | Timer3 Reg | gister Low B   | yte          |               |              |            |        |        | 65                         |

| T3CON   | RD16       | T3CCP2         | T3CKPS1      | T3CKPS0       | T3CCP1       | T3SYNC     | TMR3CS | TMR3ON | 65                         |

| CCPR1L  | Capture/Co | ompare/PWI     | A Register 2 | 1 (LSB)       |              |            |        |        | 65                         |

| CCPR1H  | Capture/Co | ompare/PWI     | A Register 2 | 1 (MSB)       |              |            |        |        | 65                         |

| CCP1CON | —          | _              | DC1B1        | DC1B0         | CCP1M3       | CCP1M2     | CCP1M1 | CCP1M0 | 65                         |

| CCPR2L  | Capture/Co | ompare/PWI     | M Register 2 | 2 (LSB)       |              |            |        |        | 65                         |

| CCPR2H  | Capture/Co | ompare/PWI     | M Register 2 | 2 (MSB)       |              |            |        |        | 65                         |

| CCP2CON | _          |                | DC2B1        | DC2B0         | CCP2M3       | CCP2M2     | CCP2M1 | CCP2M0 | 65                         |

| CCPR3L  | Capture/Co | ompare/PWI     | M Register 3 | 3 (LSB)       |              | -          | -      |        | 65                         |

| CCPR3H  | Capture/Co | ompare/PWI     | M Register 3 | 3 (MSB)       |              |            |        |        | 65                         |

| CCP3CON | —          |                | DC3B1        | DC3B0         | CCP3M3       | CCP3M2     | CCP3M1 | CCP3M0 | 65                         |

### TABLE 16-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

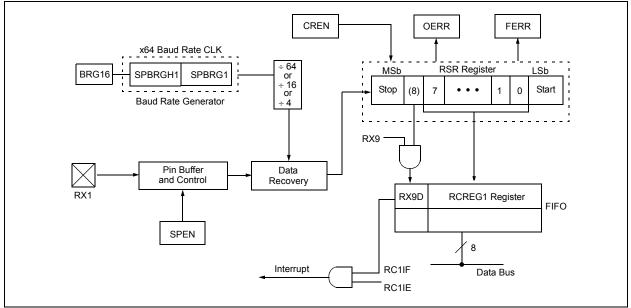

# FIGURE 18-6: EUSART RECEIVE BLOCK DIAGRAM

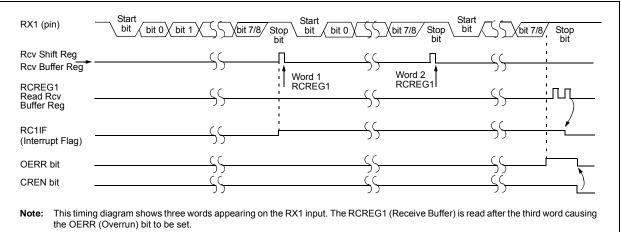

### FIGURE 18-7: ASYNCHRONOUS RECEPTION

### FIGURE 18-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

# 23.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F6310/6410/8310/8410 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The High/Low-Voltage Detect Control register (Register 23-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 23-1.

### REGISTER 23-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0   | U-0 | R-0   | R/W-0  | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

|---------|-----|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | —   | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |     |       |        |                       |                       |                       | bit 0                 |

| Legend:      |             |                                                                                            |                                                                     |                                                                              |

|--------------|-------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|

| R = Readal   | ole bit     | W = Writable bit                                                                           | U = Unimplemented bit,                                              | read as '0'                                                                  |

| -n = Value a | at POR      | '1' = Bit is set                                                                           | '0' = Bit is cleared                                                | x = Bit is unknown                                                           |

| bit 7        | VDIRMA      | G: Voltage Direction Magnit                                                                | ude Select bit                                                      |                                                                              |

|              | 1 = Ever    | nt occurs when voltage equal                                                               | ls or exceeds trip point (HLVD)<br>s or falls below trip point (HLV |                                                                              |

| bit 6        | Unimple     | emented: Read as '0'                                                                       |                                                                     |                                                                              |

| bit 5        | IRVST:      | nternal Reference Voltage St                                                               | able Flag bit                                                       |                                                                              |

|              | 0 = Indi    |                                                                                            | logic will not generate the inte                                    | flag at the specified voltage ranger<br>errupt flag at the specified voltage |

| bit 4        | 1 = HLV     | <ul> <li>High/Low-Voltage Detect F</li> <li>D is enabled</li> <li>D is disabled</li> </ul> | Power Enable bit                                                    |                                                                              |

| bit 3-0      | HLVDL<      | :3:0>: Voltage Detection Limi                                                              | it bits <sup>(1)</sup>                                              |                                                                              |

|              | 1110 =      | Maximum setting                                                                            |                                                                     |                                                                              |

|              | •           |                                                                                            |                                                                     |                                                                              |

|              | •           |                                                                                            |                                                                     |                                                                              |

|              | •<br>0001 = |                                                                                            |                                                                     |                                                                              |

**Note 1:** HLVDL<3:0> modes that result in a trip point, below the valid operating voltage of the device, are not tested.

### TABLE 25-2: PIC18FXXXX INSTRUCTION SET

| Mnem     | onic,                           | Description                              | Cueles     | 16-  | Bit Instr | uction V | Vord | Status          | Notes      |

|----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera    | nds                             | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORI | ENTED (                         | OPERATIONS                               |            |      |           |          |      |                 |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N |            |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|          | 3 <sup>,</sup> u                | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N | -          |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            | -          |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N |            |

|          | . ,                             | Borrow                                   |            |      |           |          |      |                 |            |

| SWAPF    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     |      | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

Table write instructions are unavailable in 64-pin devices in normal operating modes. See Section 7.4 "Writing to Program Memory Space (PIC18F8310/8410 only)" and Section 7.6 "Writing and Erasing On-Chip Program Memory (ICSP Mode)" for more information.

| ANDWF                               | AND W w                                                                                                                                                             | rith f                                |                                                                                                                                                    | BC                     |                                                                                      | Branch if                                                                 | Carry                                                                                                   |                                                                      |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Syntax:                             | ANDWF                                                                                                                                                               | f {,d {,a}}                           |                                                                                                                                                    | Synta                  | x:                                                                                   | BC n                                                                      |                                                                                                         |                                                                      |

| Operands:                           | $0 \leq f \leq 255$                                                                                                                                                 |                                       |                                                                                                                                                    | Opera                  | ands:                                                                                | -128 ≤ n ≤ ′                                                              | 127                                                                                                     |                                                                      |

|                                     | $\begin{array}{l} d \in [0,1] \\ a \in [0,1] \end{array}$                                                                                                           |                                       |                                                                                                                                                    | Opera                  | ation:                                                                               | if Carry bit i<br>(PC) + 2 + :                                            | ,                                                                                                       |                                                                      |

| Operation:                          | (W) .AND.                                                                                                                                                           | (f) $\rightarrow$ dest                |                                                                                                                                                    | Status                 | s Affected:                                                                          | None                                                                      |                                                                                                         |                                                                      |

| Status Affected                     | : N, Z                                                                                                                                                              |                                       |                                                                                                                                                    | Enco                   | dina:                                                                                | 1110                                                                      | 0010 nn                                                                                                 | nn nnnn                                                              |

| Encoding:<br>Description:           | register 'f'.<br>in W. If 'd' is<br>in register '<br>If 'a' is '0', f<br>If 'a' is '1', f<br>GPR bank.<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode wher | f'.<br>he Access Bai<br>he BSR is use | D'ed with<br>result is stored<br>s stored back<br>hk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See | Desci<br>Word<br>Cycle | s:<br>s:<br>vcle Activity:                                                           | will branch.<br>The 2's con<br>added to the<br>incremente<br>instruction, | bit is '1', then<br>nplement num<br>e PC. Since th<br>d to fetch the<br>the new addr<br>n. This instruc | the program<br>ber '2n' is<br>be PC will have<br>next<br>ess will be |

| Words:                              | 1                                                                                                                                                                   |                                       |                                                                                                                                                    |                        | Q1                                                                                   | Q2                                                                        | Q3                                                                                                      | Q4                                                                   |

| Cycles:                             | 1                                                                                                                                                                   |                                       |                                                                                                                                                    |                        | Decode                                                                               | Read literal                                                              | Process<br>Data                                                                                         | Write to PC                                                          |

| Q Cycle Activ                       | •                                                                                                                                                                   |                                       |                                                                                                                                                    |                        | No                                                                                   | No                                                                        | No                                                                                                      | No                                                                   |

| Q1                                  | Q2                                                                                                                                                                  | Q3                                    | Q4                                                                                                                                                 |                        | operation                                                                            | operation                                                                 | operation                                                                                               | operation                                                            |

| Decod                               |                                                                                                                                                                     | Process                               | Write to                                                                                                                                           | lf No                  | Jump:                                                                                |                                                                           |                                                                                                         |                                                                      |

|                                     | register 'f'                                                                                                                                                        | Data                                  | destination                                                                                                                                        | г                      | Q1                                                                                   | Q2                                                                        | Q3                                                                                                      | Q4                                                                   |

| Example:                            | ANDWF                                                                                                                                                               | REG, 0, 0                             |                                                                                                                                                    |                        | Decode                                                                               | Read literal<br>'n'                                                       | Process<br>Data                                                                                         | No<br>operation                                                      |

| Before In:                          | struction                                                                                                                                                           |                                       |                                                                                                                                                    |                        |                                                                                      |                                                                           |                                                                                                         |                                                                      |

| W<br>REG<br>After Instr<br>W<br>REG | uction<br>= 02h                                                                                                                                                     |                                       |                                                                                                                                                    |                        | <u>ple:</u><br>Before Instruc<br>PC<br>After Instructi<br>If Carry<br>PC<br>If Carry | = ad<br>ion<br>= 1;                                                       | BC 5<br>dress (HERE<br>dress (HERE                                                                      |                                                                      |

| BTG                       | Bit Toggle                                                                                                                                             | f                             |                                                                                                                  | BO          | /                                                                    | Branch if                                                                               | Overflow                                                                         |                                   |                                          |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------|------------------------------------------|

| Syntax:                   | BTG f, b {,a}                                                                                                                                          |                               |                                                                                                                  | Synt        | ax:                                                                  | BOV n                                                                                   |                                                                                  |                                   |                                          |

| Operands:                 | $0 \leq f \leq 255$                                                                                                                                    |                               |                                                                                                                  | Oper        | rands:                                                               | -128 ≤ n ≤ ′                                                                            | 127                                                                              |                                   |                                          |

|                           | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                 |                               |                                                                                                                  | Oper        | ration:                                                              | if Overflow<br>(PC) + 2 + 2                                                             | ,                                                                                |                                   |                                          |

| Operation:                | $(f \le b >) \rightarrow f \le b$                                                                                                                      | )>                            |                                                                                                                  | Statu       | s Affected:                                                          | None                                                                                    |                                                                                  |                                   |                                          |

| Status Affected:          | None                                                                                                                                                   |                               |                                                                                                                  | Enco        | oding:                                                               | 1110                                                                                    | 0100 ni                                                                          | nnn                               | nnnn                                     |

| Encoding:<br>Description: | Bit 'b' in data<br>inverted.<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enable<br>in Indexed L<br>mode where | e BSR is use<br>d the extende | ation 'f' is<br>nk is selected.<br>d to select the<br>ed instruction<br>ction operates<br>Addressing<br>Fh). See |             | ds:                                                                  | If the Overf<br>program wi<br>The 2's con<br>added to the<br>incremente<br>instruction, | nplement num<br>e PC. Since t<br>d to fetch the<br>the new add<br>n. This instru | mber '<br>he PC<br>next<br>ress v | 2n' is<br>; will have<br><i>v</i> ill be |

| Words:                    | 1                                                                                                                                                      |                               |                                                                                                                  |             | ycle Activity:                                                       |                                                                                         |                                                                                  |                                   |                                          |

| Cycles:                   | 1                                                                                                                                                      |                               |                                                                                                                  | lf Ju       | imp:                                                                 | 00                                                                                      | 00                                                                               |                                   | 04                                       |

| Q Cycle Activity:         |                                                                                                                                                        |                               |                                                                                                                  |             | Q1<br>Decode                                                         | Q2<br>Read literal                                                                      | Q3<br>Process                                                                    |                                   | Q4<br>Vrite to                           |

| Q1                        | Q2                                                                                                                                                     | Q3                            | Q4                                                                                                               |             | Decode                                                               | 'n'                                                                                     | Data                                                                             | v                                 | PC                                       |

| Decode                    | Read                                                                                                                                                   | Process                       | Write                                                                                                            |             | No                                                                   | No                                                                                      | No                                                                               |                                   | No                                       |

|                           | register 'f'                                                                                                                                           | Data                          | register 'f'                                                                                                     |             | operation                                                            | operation                                                                               | operation                                                                        | ор                                | eration                                  |

|                           |                                                                                                                                                        |                               |                                                                                                                  | If N        | o Jump:                                                              |                                                                                         |                                                                                  |                                   |                                          |

| Example:                  | BTG PO                                                                                                                                                 | RTC, 4, 0                     | )                                                                                                                |             | Q1                                                                   | Q2                                                                                      | Q3                                                                               |                                   | Q4                                       |

| Before Instruc<br>PORTC   |                                                                                                                                                        | 101 <b>[75h]</b>              |                                                                                                                  |             | Decode                                                               | Read literal<br>'n'                                                                     | Process<br>Data                                                                  | op                                | No<br>eration                            |

| After Instructio<br>PORTC | on:                                                                                                                                                    | 101 <b>[65h]</b>              |                                                                                                                  | <u>Exar</u> | nple:<br>Before Instruc<br>PC<br>After Instructi<br>If Overfil<br>PC | = ad<br>on<br>ow = 1;                                                                   | BOV Jum<br>dress (HER<br>dress (Jum                                              | Е)                                |                                          |

PC = address (Jump) If Overflow = 0; PC = address (HERE + 2)

| LFS                                             | R              | Load FS                                                            | Load FSR         |                            |                                       |  |  |  |  |

|-------------------------------------------------|----------------|--------------------------------------------------------------------|------------------|----------------------------|---------------------------------------|--|--|--|--|

| Synta                                           | ax:            | LFSR f,                                                            | LFSR f, k        |                            |                                       |  |  |  |  |

| Oper                                            | ands:          | $\begin{array}{l} 0 \leq f \leq 2 \\ 0 \leq k \leq 40 \end{array}$ | 95               |                            |                                       |  |  |  |  |

| Oper                                            | ation:         | $k \rightarrow FSRf$                                               |                  |                            |                                       |  |  |  |  |

| Statu                                           | s Affected:    | None                                                               |                  |                            |                                       |  |  |  |  |

| Enco                                            | ding:          | 1110<br>1111                                                       | 1110<br>0000     | 00ff<br>k <sub>7</sub> kkk | k <sub>11</sub> kkk<br>kkkk           |  |  |  |  |

| Desc                                            | ription:       | The 12-bit file select                                             |                  |                            |                                       |  |  |  |  |

| Word                                            | ls:            | 2                                                                  |                  |                            |                                       |  |  |  |  |

| Cycles:                                         |                | 2                                                                  |                  |                            |                                       |  |  |  |  |

| QC                                              | ycle Activity: |                                                                    |                  |                            |                                       |  |  |  |  |

|                                                 | Q1             | Q2                                                                 | Q3               |                            | Q4                                    |  |  |  |  |

|                                                 | Decode         | Read literal<br>'k' MSB                                            | Proce<br>Data    | a li                       | Write<br>teral 'k'<br>MSB to<br>FSRfH |  |  |  |  |

|                                                 | Decode         | Read literal<br>'k' LSB                                            | Proce<br>Data    |                            | rite literal<br>to FSRfL              |  |  |  |  |

| Example:<br>After Instruction<br>FSR2H<br>FSR2L |                | = 0                                                                | 3ABh<br>3h<br>Bh |                            |                                       |  |  |  |  |

| MOVF                                         | Move f                                                                                                                                                                          |                                                                                                            |                                                                                                                 |                                                                                     |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--|

| Syntax:                                      | MOVF f{                                                                                                                                                                         | MOVF f {,d {,a}}                                                                                           |                                                                                                                 |                                                                                     |  |

| Operands:                                    | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                             |                                                                                                            |                                                                                                                 |                                                                                     |  |

| Operation:                                   | $f \to \text{dest}$                                                                                                                                                             |                                                                                                            |                                                                                                                 |                                                                                     |  |

| Status Affected:                             | N, Z                                                                                                                                                                            |                                                                                                            |                                                                                                                 |                                                                                     |  |