### What is "Embedded - Microcontrollers"?

Welcome to E-XFL.COM

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                          |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8052                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 12.58MHz                                                        |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART                                   |

| Peripherals                | POR, PSM, PWM, Temp Sensor, WDT                                 |

| Number of I/O              | 34                                                              |

| Program Memory Size        | 62KB (62K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | 4K x 8                                                          |

| RAM Size                   | 2.25K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.25V                                                    |

| Data Converters            | A/D 3x16b, 4x24b; D/A 1x12b                                     |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 56-VFQFN Exposed Pad, CSP                                       |

| Supplier Device Package    | 56-LFCSP-VQ (8x8)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc834bcpz |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ADUC834\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

ADuC834 QuickStart Development System

### **DOCUMENTATION**

### **Application Notes**

- AN-1074: Understanding the Serial Download Protocol (Formerly uC004)

- AN-1139: Understanding the Parallel Programming Protocol

- AN-282: Fundamentals of Sampled Data Systems

- AN-644: Frequency Measurement Using Timer 2 on a MicroConverter <sup>®</sup> (uC013)

- AN-645: Interfacing an HD44780 Character LCD to a MicroConverter <sup>®</sup> (uC014)

- AN-660: XY-Matrix Keypad Interface to MicroConverter<sup>®</sup>

- AN-709: RTD Interfacing and Linearization Using an ADuC8xx MicroConverter<sup>®</sup>

- AN-759: Expanding the Number of DAC Outputs on the ADuC8xx and ADuC702x Families (uC012)

- UC-001: MicroConverter® I2C® Compatible Interface

- UC-002: Developing in C with the Keil uVision2 IDE

- UC-006: A 4-wire UART-to-PC Interface

- UC-007: User Download (ULOAD) Mode

- UC-008: Using the ADuC834 C-library

- UC-009: Addressing 16MB of External Data Memory

- UC-018: Uses of the Time Interval Counter

### Data Sheet

- ADuC834: MicroConverter<sup>®</sup> Dual 16-/24- Bit SIgma-Delta ADCs with Embedded 62KB Flash MCU Data Sheet

- ADuC834: Silicon Errata Sheet

### **User Guides**

- ADuC834 Quick Reference Guide

- UG-041: ADuC8xx Evaluation Kit Getting Started User Guide

### TOOLS AND SIMULATIONS $\Box$

• Sigma-Delta ADC Tutorial

### REFERENCE MATERIALS

### **Technical Articles**

· Integrated Route Taken to Pulse Oximetry

### DESIGN RESOURCES

- ADUC834 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADUC834 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                    |                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| FEATURES                                                                                                                                                                                                                                                                             | . 1                                                                        |

| APPLICATIONS                                                                                                                                                                                                                                                                         | . 1                                                                        |

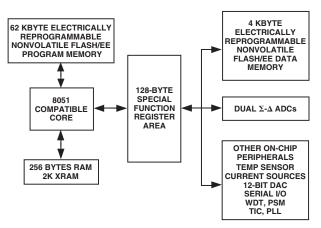

| FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                             | . 1                                                                        |

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                  | . 1                                                                        |

| SPECIFICATIONS                                                                                                                                                                                                                                                                       | . 3                                                                        |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                             | . 9                                                                        |

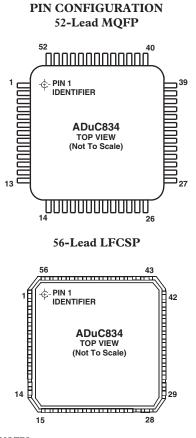

| PIN CONFIGURATIONS                                                                                                                                                                                                                                                                   | . 9                                                                        |

| DETAILED BLOCK DIAGRAM                                                                                                                                                                                                                                                               | 10                                                                         |

| PIN FUNCTION DESCRIPTIONS                                                                                                                                                                                                                                                            | 10                                                                         |

| MEMORY ORGANIZATION                                                                                                                                                                                                                                                                  | 13                                                                         |

| SPECIAL FUNCTION REGISTERS (SFRS)Accumulator (ACC)B SFR (B)Data Pointer (DPTR)Data Pointer (SP and SPH)Program Status Word (PSW)Power Control SFR (PCON)ADuC834 Configuration SFR (CFG834)Complete SFR Map                                                                           | 14<br>14<br>15<br>15<br>15<br>15                                           |

| ADC SFR INTERFACE<br>ADCSTAT<br>ADCMODE<br>ADC0CON<br>ADC1CON<br>ADC0H/ADC0M/ADC0L/ADC1H/ADC1L<br>OF0H/OF0M/OF0L/OF1H/OF1L<br>GN0H/GN0M/GN0L/GN1H/GN1L<br>SF<br>ICON                                                                                                                 | 18<br>19<br>19<br>20<br>20<br>20<br>21                                     |

| PRIMARY AND AUXILIARY ADC NOISE<br>PERFORMANCE                                                                                                                                                                                                                                       | 22                                                                         |

| PRIMARY AND AUXILIARY ADC CIRCUIT<br>DESCRIPTION                                                                                                                                                                                                                                     |                                                                            |

| OverviewPrimary ADCAuxiliary ADCAnalog Input ChannelsPrimary and Auxiliary ADC InputsAnalog Input RangesProgrammable Gain AmplifierBipolar/Unipolar InputsReference InputBurnout CurrentsExcitation CurrentsReference Detect $\Sigma$ - $\Delta$ ModulatorDigital FilterADC Chopping | 23<br>24<br>25<br>25<br>25<br>25<br>26<br>26<br>26<br>26<br>26<br>26<br>27 |

| Calibration                                                                                                                                                                                                                                                                          |                                                                            |

| NONVOLATILE FLASH/EE MEMORY                                    |          |

|----------------------------------------------------------------|----------|

| Flash/EE Memory Overview                                       | 28       |

| Flash/EE Memory and the ADuC834                                | 28       |

| ADuC834 Flash/EE Memory Reliability                            | 29       |

| Flash/EE Program Memory                                        |          |

| Serial Downloading                                             |          |

| Parallel Programming                                           |          |

| User Download Mode (ULOAD)<br>Flash/EE Program Memory Security | 30<br>31 |

| Lock, Secure, and Serial Safe Modes                            | 31       |

| Using the Flash/EE Data Memory                                 |          |

| ECON                                                           |          |

| Programming the Flash/EE Data Memory<br>Flash/EE Memory Timing | 33       |

|                                                                | "        |

| OTHER ON-CHIP PERIPHERALS                                      | 2.4      |

| DAC                                                            | 34       |

| Pulsewidth Modulator (PWM)<br>On-Chip PLL                      |          |

| Time Interval Counter (Wake-Up/RTC Timer)                      | 39<br>40 |

| Watchdog Timer                                                 |          |

| Power Supply Monitor                                           |          |

| Serial Peripheral Interface (SPI)                              |          |

| I <sup>2</sup> C Serial Interface                              | 46       |

| Dual Data Pointer                                              |          |

| 8052 COMPATIBLE ON-CHIP PERIPHERALS                            |          |

| Parallel I/O Ports 0–3                                         | 49       |

|                                                                | 52       |

| UART Serial Interface                                          | 57       |

| UART Operating Modes                                           | 57       |

| Baud Rate Generation Using Timer 1 and Timer 2                 |          |

| Baud Rate Generation Using Timer 3                             | 60       |

| Interrupt System                                               | 61       |

| HARDWARE DESIGN CONSIDERATIONS                                 |          |

| External Memory Interface                                      | 63       |

| Power Supplies                                                 |          |

| Power-On Reset (POR) Operation                                 |          |

| Power Consumption                                              |          |

| Power Saving Modes                                             |          |

| Wake-Up from Power-Down Latency                                |          |

| Grounding and Board Layout Recommendations                     |          |

| ADuC834 System Self-Identification                             |          |

|                                                                | 00       |

| OTHER HARDWARE CONSIDERATIONS                                  |          |

| In-Circuit Serial Download Access                              | 67       |

| Embedded Serial Port Debugger                                  | 67       |

| Single-Pin Emulation Mode                                      |          |

| Typical System Configuration                                   |          |

| TIMING SPECIFICATIONS                                          |          |

|                                                                |          |

| OUTLINE DIMENSIONS                                             |          |

|                                                                | 80       |

| REVISION HISTORY                                               | 81       |

| Parameter                                                              | ADuC834          | Test Conditions/Comments                                    | Unit          |

|------------------------------------------------------------------------|------------------|-------------------------------------------------------------|---------------|

| TRANSDUCER BURNOUT CURRENT                                             | SOURCES          |                                                             |               |

| AIN+ Current                                                           | -100             | AIN+ Is the Selected Positive Input to the Primary ADC      | nA typ        |

| AIN- Current                                                           | +100             | AIN– Is the Selected Negative Input to<br>the Auxiliary ADC | nA typ        |

| Initial Tolerance @ 25°C                                               | ±10              |                                                             | % typ         |

| Drift                                                                  | 0.03             |                                                             | %/°C typ      |

| EXCITATION CURRENT SOURCES                                             |                  |                                                             |               |

| Output Current                                                         | -200             | Available from Each Current Source                          | μA typ        |

| Initial Tolerance @ 25°C                                               | ±10              |                                                             | % typ         |

| Drift                                                                  | 200              |                                                             | ppm/°C typ    |

| Initial Current Matching @ 25°C                                        | ±1               | Matching between Both Current Sources                       | % typ         |

| Drift Matching                                                         | 20               |                                                             | ppm/°C typ    |

| Line Regulation (AV <sub>DD</sub> )                                    | 1                | $AV_{DD} = 5 V + 5\%$                                       | μA/V typ      |

| Load Regulation                                                        | 0.1              |                                                             | μA/V typ      |

| Output Compliance <sup>2</sup>                                         | $AV_{DD} - 0.6$  |                                                             | V max         |

|                                                                        | AGND             |                                                             | min           |

| LOGIC INPUTS                                                           |                  |                                                             |               |

| All Inputs Except SCLOCK, RESET,<br>and XTAL1 <sup>2</sup>             |                  |                                                             |               |

| V <sub>INL</sub> , Input Low Voltage                                   | 0.8              | $DV_{DD} = 5 V$                                             | V max         |

|                                                                        | 0.4              | $DV_{DD} = 3 V$                                             | V max         |

| V <sub>INH</sub> , Input High Voltage                                  | 2.0              |                                                             | V min         |

| SCLOCK and RESET Only                                                  |                  |                                                             |               |

| (Schmitt-Triggered Inputs) <sup>2</sup>                                |                  |                                                             |               |

| V <sub>T+</sub>                                                        | 1.3/3            | $DV_{DD} = 5 V$                                             | V min/V max   |

|                                                                        | 0.95/2.5         | $DV_{DD} = 3 V$                                             | V min/V max   |

| $V_{T-}$                                                               | 0.8/1.4          | $DV_{DD} = 5 V$                                             | V min/V max   |

|                                                                        | 0.4/1.1          | $DV_{DD} = 3 V$                                             | V min/V max   |

| $V_{T^+} - V_{T^-}$                                                    | 0.3/0.85         | $DV_{DD} = 5 V$                                             | V min/V max   |

|                                                                        | 0.3/0.85         | $DV_{DD} = 3 V$                                             | V min/V max   |

| Input Currents                                                         |                  |                                                             |               |

| Port 0, P1.2–P1.7, EA                                                  | ±10              | $V_{IN} = 0 V \text{ or } V_{DD}$                           | μA max        |

| SCLOCK, MOSI, MISO, $\overline{SS}^{13}$                               | -10 min, -40 max | $V_{IN} = 0 V, DV_{DD} = 5 V,$ Internal Pull-Up             | μA min/μA max |

|                                                                        | ±10              | $V_{IN} = V_{DD}, DV_{DD} = 5 V$                            | μA max        |

| RESET                                                                  | ±10              | $V_{IN} = 0 V, DV_{DD} = 5 V$                               | μA max        |

|                                                                        | 35 min, 105 max  | $V_{IN} = V_{DD}$ , $DV_{DD} = 5$ V, Internal Pull-Down     | μA min/μA max |

| P1.0, P1.1, Ports 2 and 3                                              | ±10              | $V_{IN} = V_{DD}, DV_{DD} = 5 V$                            | μA max        |

|                                                                        | -180             | $V_{IN} = 2 V, DV_{DD} = 5 V$                               | μA min        |

|                                                                        | -660             |                                                             | μA max        |

|                                                                        | -20              | $V_{IN}$ = 450 mV, $DV_{DD}$ = 5 V                          | μA min        |

|                                                                        | -75              |                                                             | μA max        |

| Input Capacitance                                                      | 5                | All Digital Inputs                                          | pF typ        |

| CRYSTAL OSCILLATOR (XTAL1 AND<br>Logic Inputs, XTAL1 Only <sup>2</sup> | XTAL2)           |                                                             |               |

| V <sub>INI</sub> , Input Low Voltage                                   | 0.8              | $DV_{DD} = 5 V$                                             | V max         |

|                                                                        | 0.4              | $DV_{DD} = 3 V$                                             | V max         |

| V <sub>INH</sub> , Input High Voltage                                  | 3.5              | $DV_{DD} = 5 V$                                             | V min         |

| · IIII                                                                 | 2.5              | $DV_{DD} = 3 V$                                             | V min         |

| XTAL1 Input Capacitance                                                | 18               |                                                             | pF typ        |

| XTAL2 Output Capacitance                                               | 18               |                                                             | pF typ        |

|                                                                        |                  | <u> </u>                                                    | r* 'JP        |

### ADuC834 SPECIFICATIONS (continued)

| Parameter                                          | ADuC834   | Test Conditions/Comments                                             | Unit                                    |

|----------------------------------------------------|-----------|----------------------------------------------------------------------|-----------------------------------------|

| LOGIC OUTPUTS (Not Including XTAL2) <sup>2</sup>   |           |                                                                      |                                         |

| $V_{OH}$ , Output High Voltage                     | 2.4       | $V_{DD} = 5 \text{ V}, \text{ I}_{\text{SOURCE}} = 80 \ \mu\text{A}$ | V min                                   |

| , Un Culput Ingh , Olugo                           | 2.4       | $V_{DD} = 3 V$ , $I_{SOURCE} = 20 \mu A$                             | V min                                   |

| V <sub>OL</sub> , Output Low Voltage <sup>14</sup> | 0.4       | $I_{SINK} = 8 \text{ mA}, \text{ SCLOCK},$                           | V max                                   |

| V <sub>OL</sub> , Output Low Voltage               |           | MOSI/SDATA                                                           | v IIIax                                 |

|                                                    | 0.4       | $I_{SINK}$ = 10 mA, P1.0 and P1.1                                    | V max                                   |

|                                                    | 0.4       | $I_{SINK}$ = 1.6 mA, All Other Outputs                               | V max                                   |

| Floating State Leakage Current <sup>2</sup>        | ±10       |                                                                      | μA max                                  |

| Floating State Output Capacitance                  | 5         |                                                                      | pF typ                                  |

| POWER SUPPLY MONITOR (PSM)                         |           |                                                                      |                                         |

| AV <sub>DD</sub> Trip Point Selection Range        | 2.63      | Four Trip Points Selectable in This Range                            | V min                                   |

|                                                    | 4.63      | Programmed via TPA1–0 in PSMCON                                      | V max                                   |

| AV <sub>DD</sub> Power Supply Trip Point Accuracy  | ±3.0      | $T_{MAX} = 85^{\circ}C$                                              | % max                                   |

|                                                    | $\pm 4.0$ | $T_{MAX} = 125^{\circ}C$                                             | % max                                   |

| DV <sub>DD</sub> Trip Point Selection Range        | 2.63      | Four Trip Points Selectable in This Range                            | V min                                   |

|                                                    | 4.63      | Programmed via TPD1–0 in PSMCON                                      | V max                                   |

| DV <sub>DD</sub> Power Supply Trip Point Accuracy  | ±3.0      | $T_{MAX} = 85^{\circ}C$                                              | % max                                   |

|                                                    | ± 4.0     | $T_{MAX} = 0.0$ C<br>$T_{MAX} = 125$ °C                              | % max                                   |

|                                                    |           |                                                                      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| WATCHDOG TIMER (WDT)                               |           |                                                                      |                                         |

| Timeout Period                                     | 0         | Nine Timeout Periods in This Range                                   | ms min                                  |

|                                                    | 2000      | Programmed via PRE3–0 in WDCON                                       | ms max                                  |

| MCU CORE CLOCK RATE                                |           | Clock Rate Generated via On-Chip PLL                                 |                                         |

| MCU Clock Rate <sup>2</sup>                        | 98.3      | Programmable via CD2–0 Bits in                                       | kHz min                                 |

|                                                    |           | PLLCON SFR                                                           |                                         |

|                                                    | 12.58     |                                                                      | MHz max                                 |

| START-UP TIME                                      |           |                                                                      |                                         |

| At Power-On                                        | 300       |                                                                      | ms typ                                  |

| After External RESET in Normal Mode                | 3         |                                                                      | ms typ                                  |

| After WDT Reset in Normal Mode                     | 3         | Controlled via WDCON SFR                                             | ms typ                                  |

| From Idle Mode                                     | 10        |                                                                      |                                         |

| From Power-Down Mode                               | 10        |                                                                      | μs typ                                  |

| Oscillator Running                                 |           | OSC_PD Bit = 0 in PLLCON SFR                                         |                                         |

| Wake-Up with INT0 Interrupt                        | 20        | $550_1 D DR = 0 III 1 ELCON SI R$                                    | us two                                  |

| Wake-Up with SPI Interrupt                         | 20 20     |                                                                      | μs typ                                  |

| Wake-Up with TIC Interrupt                         |           |                                                                      | μs typ                                  |

|                                                    | 20        |                                                                      | μs typ                                  |

| Wake-Up with External RESET                        | 3         | O(C, DD, D; t = 1; DLL O(D), ODD                                     | ms typ                                  |

| Oscillator Powered Down                            | 20        | OSC_PD Bit = 1 in PLLCON SFR                                         |                                         |

| Wake-Up with INTO Interrupt                        | 20        |                                                                      | μs typ                                  |

| Wake-Up with SPI Interrupt                         | 20        |                                                                      | μs typ                                  |

| Wake-Up with External RESET                        | 5         |                                                                      | ms typ                                  |

| FLASH/EE MEMORY RELIABILITY CHA                    |           |                                                                      |                                         |

| Endurance <sup>16</sup>                            | 100,000   |                                                                      | Cycles min                              |

| Data Retention <sup>17</sup>                       | 100       |                                                                      | Years min                               |

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

$(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$

| $AV_{DD}$ to AGND $\hfill \ldots \hfill -0.3$ V to +7 V                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------|

| AV <sub>DD</sub> to DGND $\dots \dots \dots$  |

| $DV_{DD}$ to AGND                                                                                                                             |

| $DV_{DD}$ to DGND $\hdotspace{-0.3}$ V to +7 V                                                                                                |

| AGND to DGND <sup>2</sup> $\dots \dots \dots$ |

| $AV_{DD}$ to $DV_{DD}$                                                                                                                        |

| Analog Input Voltage to AGND <sup>3</sup> $-0.3$ V to AV <sub>DD</sub> + 0.3 V                                                                |

| Reference Input Voltage to AGND $\dots$ -0.3 V to AV <sub>DD</sub> + 0.3 V                                                                    |

| AIN/REFIN Current (Indefinite)                                                                                                                |

| Digital Input Voltage to DGND $\dots$ -0.3 V to DV <sub>DD</sub> + 0.3 V                                                                      |

| Digital Output Voltage to DGND $\dots$ -0.3 V to DV <sub>DD</sub> + 0.3 V                                                                     |

| Operating Temperature Range40°C to +125°C                                                                                                     |

| Storage Temperature Range65°C to +150°C                                                                                                       |

| Junction Temperature 150°C                                                                                                                    |

| $\theta_{IA}$ Thermal Impedance (MQFP)                                                                                                        |

| $\theta_{IA}$ Thermal Impedance (LFCSP Base Floating) 52°C/W                                                                                  |

| Lead Temperature, Soldering                                                                                                                   |

| Vapor Phase (60 sec) 215°C                                                                                                                    |

| Infrared (15 sec) 220°C                                                                                                                       |

| NOTES                                                                                                                                         |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>AGND and DGND are shorted internally on the ADuC834.

<sup>3</sup>Applies to P1.2 to P1.7 pins operating in analog or digital input modes.

NOTES 1. EXPOSED PAD. THE LFCSP HAS AN EXPOSED PAD THAT MUST BE SOLDERED TO THE METAL PLATE ON THE PCB AND TO DGND.

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADuC834 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

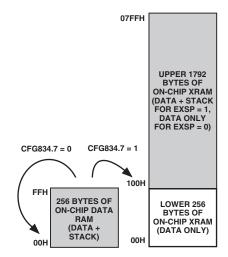

When accessing the internal XRAM, the P0 and P2 port pins, as well as the  $\overline{RD}$  and  $\overline{WR}$  strobes, will not be output as per a standard 8051 MOVX instruction. This allows the user to use these port pins as standard I/O.

The upper 1792 bytes of the internal XRAM can be configured to be used as an extended 11-bit stack pointer. By default, the stack will operate exactly like an 8052 in that it will roll over from FFH to 00H in the general-purpose RAM. On the ADuC834 however, it is possible (by setting CFG834.7) to enable the 11-bit extended stack pointer. In this case, the stack will roll over from FFH in RAM to 0100H in XRAM. The 11-bit stack pointer is visible in the SP and SPH SFRs. The SP SFR is located at 81H as with a standard 8052. The SPH SFR is located at B7H. The 3 LSBs of this SFR contain the three extra bits necessary to extend the 8-bit stack pointer into an 11-bit stack pointer.

Figure 4. Extended Stack Pointer Operation

### External Data Memory (External XRAM)

Just like a standard 8051 compatible core, the ADuC834 can access external data memory using a MOVX instruction. The MOVX instruction automatically outputs the various control strobes required to access the data memory.

The ADuC834 however, can access up to 16 Mbytes of external data memory. This is an enhancement of the 64 Kbytes external data memory space available on a standard 8051 compatible core.

The external data memory is discussed in more detail in the ADuC834 Hardware Design Considerations section.

### SPECIAL FUNCTION REGISTERS (SFRS)

The SFR space is mapped into the upper 128 bytes of internal data memory space and accessed by direct addressing only. It provides an interface between the CPU and all on-chip peripherals. A block diagram showing the programming model of the ADuC834 via the SFR area is shown in Figure 5.

### Figure 5. Programming Model

All registers, except the Program Counter (PC) and the four general-purpose register banks, reside in the SFR area. The SFR registers include control, configuration, and data registers that provide an interface between the CPU and all on-chip peripherals.

### Accumulator SFR (ACC)

ACC is the Accumulator Register and is used for math operations including addition, subtraction, integer multiplication and division, and Boolean bit manipulations. The mnemonics for accumulator-specific instructions refer to the Accumulator as A.

### B SFR (B)

The B Register is used with the ACC for multiplication and division operations. For other instructions, it can be treated as a general-purpose scratchpad register.

### Data Pointer (DPTR)

The Data Pointer is made up of three 8-bit registers, named DPP (page byte), DPH (high byte) and DPL (low byte). These are used to provide memory addresses for internal and external code access and external data access. It may be manipulated as a 16-bit register (DPTR = DPH, DPL), although INC DPTR instructions will automatically carry over to DPP, or as three independent 8-bit registers (DPP, DPH, DPL).

The ADuC834 supports dual data pointers. Refer to the Dual Data Pointer section in this data sheet.

### Stack Pointer (SP and SPH)

The SP SFR is the stack pointer and is used to hold an internal RAM address that is called the 'top of the stack.' The SP Register is incremented before data is stored during PUSH and CALL executions. While the Stack may reside anywhere in on-chip RAM, the SP Register is initialized to 07H after a reset. This causes the stack to begin at location 08H.

As mentioned earlier, the ADuC834 offers an extended 11-bit stack pointer. The three extra bits to make up the 11-bit stack pointer are the 3 LSBs of the SPH byte located at B7H.

### Program Status Word (PSW)

The PSW SFR contains several bits reflecting the current status of the CPU as detailed in Table I.

| SFR Address            | D0H |

|------------------------|-----|

| Power-On Default Value | 00H |

| Bit Addressable        | Yes |

| Table I. | PSW | SFR | Bit | Designations |

|----------|-----|-----|-----|--------------|

|----------|-----|-----|-----|--------------|

| Bit | Name | Description               |  |  |

|-----|------|---------------------------|--|--|

| 7   | СҮ   | Carry Flag                |  |  |

| 6   | AC   | Auxiliary Carry Flag      |  |  |

| 5   | F0   | General-Purpose Flag      |  |  |

| 4   | RS1  | Register Bank Select Bits |  |  |

| 3   | RS0  | RS1 RS0 Selected Bank     |  |  |

|     |      | 0 0 0                     |  |  |

|     |      | 0 1 1                     |  |  |

|     |      | 1 0 2                     |  |  |

|     |      | 1 1 3                     |  |  |

| 2   | OV   | Overflow Flag             |  |  |

| 1   | F1   | General-Purpose Flag      |  |  |

| 0   | Р    | Parity Bit                |  |  |

### Power Control SFR (PCON)

The PCON SFR contains bits for power-saving options and general-purpose status flags as shown in Table II.

The TIC (wake-up/RTC timer) can be used to accurately wake up the ADuC834 from power-down at regular intervals. To use the TIC to wake up the ADuC834 from power-down, the OSC\_PD bit in the PLLCON SFR must be clear and the TIC must be enabled.

| SFR Address            | 87H |

|------------------------|-----|

| Power-On Default Value | 00H |

| Bit Addressable        | No  |

Table II. PCON SFR Bit Designations

| Bit | Name   | Description                      |

|-----|--------|----------------------------------|

| 7   | SMOD   | Double UART Baud Rate            |

| 6   | SERIPD | SPI Power-Down Interrupt Enable  |

| 5   | INT0PD | INT0 Power-Down Interrupt Enable |

| 4   | ALEOFF | Disable ALE Output               |

| 3   | GF1    | General-Purpose Flag Bit         |

| 2   | GF0    | General-Purpose Flag Bit         |

| 1   | PD     | Power-Down Mode Enable           |

| 0   | IDL    | Idle Mode Enable                 |

### ADuC834 CONFIGURATION SFR (CFG834)

The CFG834 SFR contains the necessary bits to configure the internal XRAM and the extended SP. By default it configures the user into 8051 mode, i.e., extended SP is disabled, internal XRAM is disabled.

| SFR Address            | AFH |

|------------------------|-----|

| Power-On Default Value | 00H |

| Bit Addressable        | No  |

### Table III. CFG834 SFR Bit Designations

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                   |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EXSP   | Extended SP Enable. If this bit is set, the<br>stack will roll over from SPH/SP = 00FFH<br>to 0100H. If this bit is clear, the SPH SFR<br>will be disabled and the stack will roll<br>over from SP = FFH to SP = 00H                                                                                                          |

| 6   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 5   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 4   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 3   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 2   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 1   |        | Reserved for Future Use                                                                                                                                                                                                                                                                                                       |

| 0   | XRAMEN | XRAM Enable Bit. If this bit is set, the<br>internal XRAM will be mapped into the<br>lower 2 Kbytes of the external address<br>space. If this bit is clear, the internal<br>XRAM will not be accessible and the<br>external data memory will be mapped<br>into the lower 2 Kbytes of external data<br>memory. (See Figure 3.) |

### **COMPLETE SFR MAP**

Figure 6 shows a full SFR memory map and the SFR contents after RESET. NOT USED indicates unoccupied SFR locations. Unoccupied locations in the SFR address space are not

implemented; i.e., no register exists at this location. If an unoccupied location is read, an unspecified value is returned. SFR locations that are reserved for future use are shaded (RESERVED) and should not be accessed by user software.

| 10.51         |             | 0.00         |               |    |               |      |        | 00004         |            |     |      | ٦.              | SPICON     |     |                   |       |                     | DACL              | DACH              | DACCON            |          |          |

|---------------|-------------|--------------|---------------|----|---------------|------|--------|---------------|------------|-----|------|-----------------|------------|-----|-------------------|-------|---------------------|-------------------|-------------------|-------------------|----------|----------|

| ISPI<br>FFH 0 | WCOL<br>FEH | SPE<br>0 FDH | SPIN<br>0 FCH |    | CPOL<br>FBH ( | CPH  |        | SPR1<br>F9H 0 | SPF<br>F8H | 10  | BITS | $\geq$          | F8H 04     |     | RESERVE           | DR    | RESERVED            | FBH 00H           | FCH 00H           | FDH 00H           | RESERVED | RESERVED |

|               |             |              |               |    |               |      |        |               |            |     |      | _               | B          | *** |                   | +     |                     | гвп ооп           | PCH UUH           |                   |          | SPIDAT   |

|               |             | _            |               | -  |               |      |        |               |            |     | BITS | >               |            |     | RESERVE           | DR    | ESERVED             | NOT USED          | RESERVED          | RESERVED          | RESERVED | SPIDAT   |

| F7H 0         | F6H         | 0 F5H        | 0 F4H         | 0  | F3H (         | F2H  | 0      | F1H 0         | F0H        | 0   |      | 1               | F0H 00     | н   |                   |       |                     |                   |                   |                   |          | F7H 00H  |

| MDO           | MDE         | MCO          | MD            | I  | I2CM          | I2CF | IS     | I2CTX         | I2C        | 1   | BITS |                 | I2CCON     | 1   | GN0L <sup>1</sup> |       | GN0M <sup>1</sup>   | GN0H <sup>1</sup> | GN1L <sup>1</sup> | GN1H <sup>1</sup> | RESERVED | RESERVED |

| EFH 0         | EEH         | 0 EDH        | 0 ECH         | 0  | EBH (         | EAH  | 0      | E9H 0         | E8H        | 0   | ытэ  |                 | E8H 00     | н   | E9H 55            | н     | EAH 55H             | EBH 53H           | ECH 9AH           | EDH 59H           | ILOLINED | HEOLINED |

|               |             |              |               |    |               | T    |        |               |            |     |      | ٦               | ACC        |     | OF0L              |       | OF0M                | OF0H              | OF1L              | OF1H              |          |          |

| E7H 0         | E6H         | 0 E5H        | 0 E4H         | 0  | E3H (         | E2H  | 0      | E1H 0         | E0H        | 0   | BITS | $\geq$          | E0H 00     |     | E1H 00            |       | E2H 00H             | E3H 80H           | E4H 00H           | E5H 80H           | RESERVED | RESERVED |

|               |             |              |               |    |               |      |        | 1             |            |     |      | _               | ADCSTA     | -   | ADCOL             |       | ADCOM               | ADC0H             | ADC1L             | ADC1H             |          | PSMCON   |

| RDY0          | RDY1        |              | NOXE          |    | ERR0          | ERF  |        |               |            |     | BITS | $\leq$          | ADCSTA     | "   | ADCUL             |       | ADCOM               | ADCON             | ADCIL             | ADCIN             | RESERVED | PSMCON   |

| DFH 0         | DEH         | 0 DDH        | 0 DCH         | 0  | DBH (         | DAH  | 0      | D9H 0         | D8H        | 0   |      | 1               | D8H 00     | н   | D9H 00            | н     | DAH 00H             | DBH 00H           | DCH 00H           | DDH 00H           |          | DFH DEH  |

| CY            | AC          | F0           | RS            | I  | RS0           | ov   |        | FI            | Р          |     | DITO | Z               | PSW        |     | ADCMOD            | E     | ADC0CON             | ADC1CON           | SF                | ICON              | RESERVED | PLLCON   |

| D7H 0         | D6H         | 0 D5H        | 0 D4H         | 0  | D3H (         | D2H  | 0      | D1H 0         | D0H        | 0   | BITS |                 | рон оо     | н   | D1H 00            | н     | D2H 07H             | D3H 00H           | D4H 45H           | D5H 00H           | NEGENVED | D7H 03H  |

| TF2           | EXF2        | RCLK         | TCL           | ĸ  | EXEN2         | TR   | ,      | CNT2          | CAP        | 2   |      | 7               | T2CON      |     |                   |       | RCAP2L              | RCAP2H            | TL2               | TH2               |          |          |

| CFH 0         |             |              | 0 CCH         |    | CBH (         |      |        | C9H 0         |            | 0   | BITS | $\geq$          | <br>С8Н 00 |     | RESERVE           |       | САН 00Н             | СВН ООН           | ссн оон           | CDH 00H           | RESERVED | RESERVED |

|               |             |              |               |    |               |      |        |               |            |     |      | -               | WDCON      |     |                   | -     | CHIPID              | CBI1 0011         | 0011              | 0011              | EADRL    |          |

| PRE3          | PRE2        | PRE1         | PRE           | -  | WDIR          | WD   | s      | WDE           | WDW        | /R  | BITS | >               |            |     | RESERVE           | D     | CHIPID              | RESERVED          | RESERVED          | RESERVED          | EADRL    | EADRH    |

| C7H 0         | C6H         | 0   C5H      | 0 C4H         | 1  | C3H (         | C2H  | 0      | C1H 0         | COH        | 0   |      | 1               | C0H 10     | н   |                   | (     | C2H 2×H             |                   | -                 |                   | C6H 00H  | C7H 00H  |

|               | PADC        | PT2          | PS            | ;  | PT1           | PX1  |        | PT0           | PX0        | )   | BITS |                 | IP         |     | ECON              |       | RESERVED            | RESERVED          | EDATA1            | EDATA2            | EDATA3   | EDATA4   |

| BFH 0         | BEH         | 0 BDH        | 0 BCH         | 0  | BBH (         | BAH  |        | B9H 0         | B8H        | 0   | 5113 |                 | B8H 00     | н   | B9H 00            |       | RESERVED            | RESERVED          | BCH 00H           | BDH 00H           | BEH 00H  | BFH 00H  |

| RD            | WB          | T1           | то            |    | INT1          | INTO | ī      | тхр           | RX         |     |      | ٦               | P3         |     | PWM0L             |       | PWM0H               | PWM1L             | PWM1H             |                   |          | SPH      |

| B7H 1         |             |              | 1 B4H         |    | B3H 1         |      | ,<br>1 | B1H 1         | вон        | 1   | BITS | $\geq$          | BOH FF     | н   | B1H 00            | нГ    | 32H 00H             | B3H 00H           | B4H 00H           | RESERVED          | RESERVED | B7H 00H  |

|               |             | -            |               |    |               |      |        |               |            |     |      | -               | IE         | -   | IEIP2             |       |                     |                   |                   |                   |          |          |

| EA            | EADC        | ET2          | ES            |    | ET1           | EX1  |        | ET0           | EXO        |     | BITS | >               | - "        |     | IEIP2             | F     | RESERVED            | RESERVED          | RESERVED          | RESERVED          | PWMCON   | CFG834   |

| AFH 0         | AEH         | 0 ADH        | 0 ACH         | 0  | ABH (         | AAH  | 0      | A9H 0         | A8H        | 0   |      | 1               | A8H 00     | н   | A9H A0            | н     |                     |                   |                   |                   | AEH 00H  | AFH 00H  |

|               |             |              |               |    |               |      |        |               |            |     | BITS | $\overline{\ }$ | P2         |     | TIMECON           | 4     | HTHSEC <sup>2</sup> | SEC <sup>2</sup>  | MIN <sup>2</sup>  | HOUR <sup>2</sup> | INTVAL   | DPCON    |

| A7H 1         | A6H         | 1 A5H        | 1 A4H         | 1  | A3H 1         | A2H  | 1      | A1H 1         | A0H        | 1   | ытэ  |                 | A0H FF     | н   | A1H 00            | н     | A2H 00H             | A3H 00H           | A4H 00H           | A5H 00H           | A6H 00H  | A7H 00H  |

| SM0           | SM1         | SM2          | REN           | u. | TB8           | RB8  |        | T1            | R1         |     |      | ٦               | SCON       |     | SBUF              |       |                     |                   |                   | T3FD              | T3CON    |          |

|               |             |              | 0 9CH         |    |               | 9AH  |        |               | 98H        | 0   | BITS | $\geq$          | 98H 00     |     | 99H 00            |       | RESERVED            | RESERVED          | NOT USED          | 9DH 00H           | 9EH 00H  | RESERVED |

|               |             |              |               |    |               | -    |        |               |            |     |      | -               | P1         |     | 00                |       |                     |                   |                   |                   |          |          |

| 97H 1         | 061         | 1 95H        | 1 94H         | 1  | 93H 1         | 92H  | 1      | T2EX<br>91H 1 | T2<br>90H  |     | BITS | >               | +          |     | RESERVE           | DR    | ESERVED             | RESERVED          | RESERVED          | RESERVED          | RESERVED | RESERVED |

| 3/N 1         | 96H         | 1 990        | 1 9411        |    | 501           | 9211 | 1      | 91H 1         | 900        | - 1 |      | 1               | 90H FF     | FH  |                   |       |                     |                   |                   |                   |          |          |

| TF1           | TR1         | TF0          | TR            | D  | IE1           | IT1  |        | IE0           | IT0        |     | BITS | $\overline{\ }$ | TCON       |     | TMOD              |       | TL0                 | TL1               | TH0               | TH1               | RESERVED | RESERVED |

| 8FH 0         | 8EH         | 0 8DH        | 0 8CH         | 0  | 8BH (         | 8AH  | 0      | 89H 0         | 88H        | 0   | 5    |                 | 88H 00     | н   | 89H 00            | н     | ВАН ООН             | 8BH 00H           | 8CH 00H           | 8DH 00H           | HEGENVED | ILOLIVED |

|               |             |              |               |    |               | T    |        |               |            |     |      | 7               | P0         |     | SP                |       | DPL                 | DPH               | DPP               |                   |          | PCON     |

| 87H 1         | 86H         | 1 85H        | 1 84H         | 1  | 83H 1         | 82H  | 1      | 81H 1         | 80H        | 1   | BITS | $\geq$          | 80H FF     |     | 81H 07            |       | 82H 00H             | 83H 00H           | 84H 00H           | RESERVED          | RESERVED | 87H 00H  |

| -             |             |              |               |    |               |      |        |               |            |     |      | -               | OUH FF     | -11 | 81H 07            | n   1 | 82H 00H             | 03H 00H           | 84H 00H           |                   |          | 87H 00H  |

#### NOTES

1CALIBRATION COEFFICIENTS ARE PRECONFIGURED AT POWER-UP TO FACTORY CALIBRATED VALUES. <sup>2</sup>THESE SFRS MAINTAIN THEIR PRERESET VALUES AFTER A RESET IF TIMECON.0 = 1.

SFR NOTE: SFRs WHOSE ADDRESSES END IN 0H OR 8H ARE BIT-ADDRESSABLE.

Figure 6. Special Function Register Locations and Their Reset Default Values

## PRIMARY AND AUXILIARY ADC NOISE PERFORMANCE

Tables X, XI, and XII show the output rms noise in  $\mu$ V and output peak-to-peak resolution in bits (rounded to the nearest 0.5 LSB) for some typical output update rates on both the primary and auxiliary ADCs. The numbers are typical and are generated at a differential input voltage of 0 V. The output update rate is

selected via the Sinc Filter (SF) SFR. It is important to note that the peak-to-peak resolution figures represent the resolution for which there will be no code flicker within a six-sigma limit.

The QuickStart Development system PC software comes complete with an ADC noise evaluation tool. This tool can be easily used with the evaluation board to see these figures from silicon.

## Table X. Primary ADC, Typical Output RMS Noise ( $\mu V$ )Typical Output RMS Noise vs. Input Range and Update Rate; Output RMS Noise in $\mu V$

| SF   | Data Update |        |        |        | Input Range |         |         |         |         |

|------|-------------|--------|--------|--------|-------------|---------|---------|---------|---------|

| Word | Rate (Hz)   | ±20 mV | ±40 mV | ±80 mV | ±160 mV     | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |

| 13   | 105.3       | 1.50   | 1.50   | 1.60   | 1.75        | 3.50    | 4.50    | 6.70    | 11.75   |

| 69   | 19.79       | 0.60   | 0.65   | 0.65   | 0.65        | 0.65    | 0.95    | 1.40    | 2.30    |

| 255  | 5.35        | 0.35   | 0.35   | 0.37   | 0.37        | 0.37    | 0.51    | 0.82    | 1.25    |

Table XI. Primary ADC, Peak-to-Peak Resolution (Bits)

Peak-to-Peak Resolution vs. Input Range and Update Rate; Peak-to-Peak Resolution in Bits

| SF   | Data Update |                     |                     |        | Input Range |         |         |         |         |

|------|-------------|---------------------|---------------------|--------|-------------|---------|---------|---------|---------|

| Word | Rate (Hz)   | $\pm 20 \text{ mV}$ | $\pm 40 \text{ mV}$ | ±80 mV | ±160 mV     | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |

| 13   | 105.3       | 12                  | 13                  | 14     | 15          | 15      | 15.5    | 16      | 16      |

| 69   | 19.79       | 13.5                | 14                  | 15     | 16          | 17      | 17.5    | 18      | 18.5    |

| 255  | 5.35        | 14                  | 15                  | 16     | 17          | 18      | 18.5    | 19      | 19.5    |

### Typical RMS Resolution vs. Input Range and Update Rate: RMS Resolution in Bits\*

| SF   | Data Update |        |        |        | Input Range |         |         |         |         |

|------|-------------|--------|--------|--------|-------------|---------|---------|---------|---------|

| Word | Rate (Hz)   | ±20 mV | ±40 mV | ±80 mV | ±160 mV     | ±320 mV | ±640 mV | ±1.28 V | ±2.56 V |

| 13   | 105.3       | 14.7   | 15.7   | 16.7   | 17.7        | 17.7    | 18.2    | 18.7    | 18.7    |

| 69   | 19.79       | 16.2   | 16.7   | 17.7   | 18.7        | 19.7    | 20.2    | 20.7    | 21.2    |

| 255  | 5.35        | 16.7   | 17.7   | 18.7   | 19.7        | 20.7    | 21.2    | 21.7    | 22.2    |

\*Based on a six-sigma limit, the rms resolution is 2.7 bits greater than the peak-to-peak resolution.

### Table XII. Auxiliary ADC

#### Typical Output RMS Noise vs. Update Rate\* Output RMS Noise in µV

| SF<br>Word | Data Update<br>Rate (Hz) | Input Range<br>2.5 V |  |  |

|------------|--------------------------|----------------------|--|--|

| 13         | 105.3                    | 10.75                |  |  |

| 69         | 19.79                    | 2.00                 |  |  |

| 255        | 5.35                     | 1.15                 |  |  |

\*ADC converting in Bipolar mode

### Peak-to-Peak Resolution vs. Update Rate<sup>1</sup> Peak-to-Peak Resolution in Bits

| SF<br>Word | Data Update<br>Rate (Hz) | Input Range<br>2.5 V |

|------------|--------------------------|----------------------|

| 13         | 105.3                    | 16 <sup>2</sup>      |

| 69         | 19.79                    | 16                   |

| 255        | 5.35                     | 16                   |

NOTES

<sup>1</sup>ADC converting in Bipolar mode

<sup>2</sup>In Unipolar mode, peak-to-peak resolution at 105 Hz is 15 bits.

### **Reference Input**

The ADuC834's reference inputs, REFIN(+) and REFIN(-), provide a differential reference input capability. The commonmode range for these differential inputs is from AGND to  $AV_{DD}$ . The nominal reference voltage,  $V_{REF}$  (REFIN(+) – REFIN(-)), for specified operation is 2.5 V with the primary and auxiliary reference enable bits set in the respective ADC0CON and/or ADC1CON SFRs.

The part is also functional (although not specified for performance) when the XREF0 or XREF1 bits are 0, which enables the on-chip internal band gap reference. In this mode, the ADCs will see the internal reference of 1.25 V, therefore halving all input ranges. As a result of using the internal reference voltage, a noticeable degradation in peak-to-peak resolution will result. Therefore, for best performance, operation with an external reference is strongly recommended.

In applications where the excitation (voltage or current) for the transducer on the analog input also drives the reference voltage for the part, the effect of the low frequency noise in the excitation source will be removed as the application is ratiometric. If the ADuC834 is not used in a ratiometric application, a low noise reference should be used. Recommended reference voltage sources for the ADuC834 include the AD780, REF43, and REF192.

It should also be noted that the reference inputs provide a high impedance, dynamic load. Because the input impedance of each reference input is dynamic, resistor/capacitor combinations on these inputs can cause dc gain errors depending on the output impedance of the source that is driving the reference inputs. Reference voltage sources, like those recommended above (e.g., AD780), will typically have low output impedances and therefore decoupling capacitors on the REFIN(+) input would be recommended. Deriving the reference input voltage across an external resistor, as shown in Figure 66, will mean that the reference input sees a significant external source impedance. External decoupling on the REFIN(+) and REFIN(-) pins would not be recommended in this type of circuit configuration.

### **Burnout Currents**

The primary ADC on the ADuC834 contains two 100 nA constant current generators, one sourcing current from  $AV_{DD}$  to AIN(+), and one sinking from AIN(-) to AGND. The currents are switched to the selected analog input pair. Both currents are either on or off, depending on the Burnout Current Enable (BO) bit in the ICON SFR (see Table IX). These currents can be used to verify that an external transducer is still operational before attempting to take measurements on that channel. Once the burnout currents are turned on, they will flow in the external transducer circuit, and a measurement of the input voltage on the analog input channel can be taken. If the resultant voltage measured is full-scale, it indicates that the transducer has gone open-circuit.

If the voltage measured is 0 V, it indicates that the transducer has short circuited. For normal operation, these burnout currents are turned off by writing a 0 to the BO bit in the ICON SFR. The current sources work over the normal absolute input voltage range specifications.

### **Excitation Currents**

The ADuC834 also contains two identical, 200  $\mu$ A constant current sources. Both source current from AV<sub>DD</sub> to Pin 3 (IEXC1) or Pin 4 (IEXC2). These current sources are controlled via bits in the ICON SFR shown in Table IX. They can be configured to source 200  $\mu$ A individually to both pins or a combination of both currents, i.e., 400  $\mu$ A, to either of the selected pins. These current sources can be used to excite external resistive bridge or RTD sensors.

### **Reference Detect**

The ADuC834 includes on-chip circuitry to detect if the part has a valid reference for conversions or calibrations. If the voltage between the external REFIN(+) and REFIN(-) pins goes below 0.3 V or either the REFIN(+) or REFIN(-) inputs is open circuit, the ADuC834 detects that it no longer has a valid reference. In this case, the NOXREF bit of the ADCSTAT SFR is set to a 1. If the ADuC834 is performing normal conversions and the NOXREF bit becomes active, the conversion results revert to all 1s. It is not necessary to continuously monitor the status of the NOXREF bit when performing conversions. It is only necessary to verify its status if the conversion result read from the ADC Data Register is all 1s.

If the ADuC834 is performing either an offset or gain calibration and the NOXREF bit becomes active, the updating of the respective calibration registers is inhibited to avoid loading incorrect coefficients to these registers, and the appropriate ERR0 or ERR1 bits in the ADCSTAT SFR are set. If the user is concerned about verifying that a valid reference is in place every time a calibration is performed, the status of the ERR0 or ERR1 bit should be checked at the end of the calibration cycle.

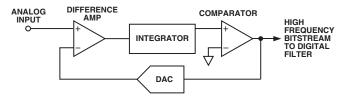

### $\Sigma$ - $\Delta$ Modulator

A  $\Sigma$ - $\Delta$  ADC generally consists of two main blocks, an analog modulator and a digital filter. In the case of the ADuC834 ADCs, the analog modulators consist of a difference amplifier, an integrator block, a comparator, and a feedback DAC as illustrated in Figure 10.

Figure 10.  $\Sigma$ - $\Delta$  Modulator Simplified Block Diagram

### **PWM MODES OF OPERATION**

Mode 0: PWM Disabled

The PWM is disabled, allowing P1.0 and P1.1 be used as normal.

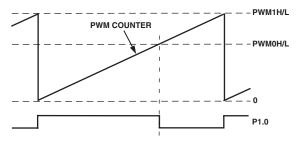

#### Mode 1: Single-Variable Resolution PWM

In Mode 1, both the pulse length and the cycle time (period) are programmable in user code, allowing the resolution of the PWM to be variable.

PWM1H/L sets the period of the output waveform. Reducing PWM1H/L reduces the resolution of the PWM output but increases the maximum output rate of the PWM (e.g., setting PWM1H/L to 65536 gives a 16-bit PWM with a maximum output rate of 192 Hz (12.583 MHz/65536). Setting PWM1H/L to 4096 gives a 12-bit PWM with a maximum output rate of 3072 Hz (12.583 MHz/4096)).

PWM0H/L sets the duty cycle of the PWM output waveform, as shown in Figure 27.

Figure 27. PWM in Mode 1

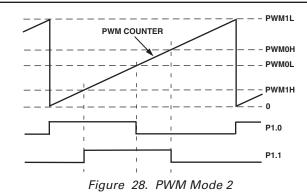

#### Mode 2: Twin 8-Bit PWM

In Mode 2, the duty cycle of the PWM outputs and the resolution of the PWM outputs are both programmable. The maximum resolution of the PWM output is eight bits.

PWM1L sets the period for both PWM outputs. Typically this will be set to 255 (FFh) to give an 8-bit PWM, although it is possible to reduce this as necessary. A value of 100 could be loaded here to give a percentage PWM (i.e., the PWM is accurate to 1%).

The outputs of the PWM at P1.0 and P1.1 are shown in the diagram below. As can be seen, the output of PWM0 (P1.0) goes low when the PWM counter equals PWM0L. The output of PWM1 (P1.1) goes high when the PWM counter equals PWM1H and goes low again when the PWM counter equals PWM0H. Setting PWM1H to 0 ensures that both PWM outputs start simultaneously.

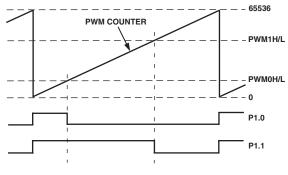

### Mode 3: Twin 16-Bit PWM

In Mode 3, the PWM counter is fixed to count from 0 to 65536 giving a fixed 16-bit PWM. Operating from the 12.58 MHz core clock results in a PWM output rate of 192 Hz. The duty cycle of the PWM outputs at P1.0 and P1.1 are independently programmable.

As shown below, while the PWM counter is less than PWM0H/L, the output of PWM0 (P1.0) is high. Once the PWM counter equals PWM0H/L, then PWM0 (P1.0) goes low and remains low until the PWM counter rolls over.

Similarly, while the PWM counter is less than PWM1H/L, the output of PWM1 (P1.1) is high. Once the PWM counter equals PWM1H/L, then PWM1 (P1.1) goes low and remains low until the PWM counter rolls over.

In this mode, both PWM outputs are synchronized (i.e., once the PWM counter rolls over to 0, both PWM0 (P1.0) and PWM1 (P1.1) will go high).

Figure 29. PWM Mode 3

### TIME INTERVAL COUNTER (WAKE-UP/RTC TIMER)

A time interval counter (TIC) is provided on-chip for:

- · periodically waking the part up from power-down

- implementing a Real-Time Clock

- counting longer intervals than the standard 8051 compatible timers are capable of

The TIC is capable of timeout intervals ranging from 1/128th second to 255 hours. Furthermore, this counter is clocked by the crystal oscillator rather than the PLL and thus has the ability to remain active in power-down mode and time long power-down intervals. This has obvious applications for remote battery-powered sensors where regular widely spaced readings are required.

The TIC counter can easily be used to generate a real-time clock. The hardware will count in seconds, minutes, and hours; however, user software will have to count in days, months, and years. The current time can be written to the timebase SFRs (HTHSEC, SEC, MIN, and HOUR) while TCEN is low. When the RTC timer is enabled (TCEN is set), the TCEN bit itself and the HTHSEC, SEC, MIN, and HOUR Registers are not reset to 00H after a hardware or watchdog timer reset. This is to prevent the need to recalibrate the real-time clock after a reset. However, these registers will be reset to 00H after a power cycle (independent of TCEN) or after any reset if TCEN is clear.

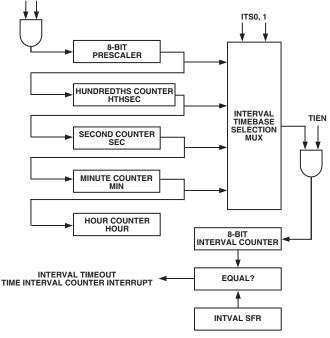

Six SFRs are associated with the time interval counter, TIMECON being its control register. Depending on the configuration of the IT0 and IT1 bits in TIMECON, the selected time counter register overflow will clock the interval counter. When this counter is equal to the time interval value loaded in the INTVAL SFR, the TII bit (TIMECON.2) is set and generates an interrupt if enabled. (See IEIP2 SFR description under Interrupt System in this data sheet.) If the ADuC834 is in power-down mode, again with TIC interrupt enabled, the TII bit will wake up the device and resume code execution by vectoring directly to the TIC interrupt service vector address at 0053H. The TIC-related SFRs are described below with a block diagram of the TIC shown in Figure 33.

Figure 33. TIC, Simplified Block Diagram

### Table XVIII. TIMECON SFR Bit Designations

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7   |      | Reserved for Future Use                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 6   |      | Reserved for Future Use. For future product code compatibility, this bit should be written as a '1.'                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 5   | ITS1 | Interval Timebase Selection Bits                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 4   | ITS0 | Written by user to determine the interval counter update rate.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|     |      | ITS1 ITS0 Interval Timebase                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|     |      | 0 0 1/128 Second                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |