### \_\_\_Lattice Semiconductor Corporation - <u>LFECP33E-4FN672I Datasheet</u>

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

XE

| Detans                         |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 32800                                                                       |

| Total RAM Bits                 | 434176                                                                      |

| Number of I/O                  | 496                                                                         |

| Number of Gates                | -                                                                           |

| Voltage - Supply               | 1.14V ~ 1.26V                                                               |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 672-BBGA                                                                    |

| Supplier Device Package        | 672-FPBGA (27x27)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/lattice-semiconductor/lfecp33e-4fn672i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LatticeECP/EC Family Data Sheet Architecture

#### September 2012

**Data Sheet**

### **Architecture Overview**

The LatticeECP-DSP and LatticeEC architectures contain an array of logic blocks surrounded by Programmable I/ O Cells (PIC). Interspersed between the rows of logic blocks are rows of sysMEM Embedded Block RAM (EBR), as shown in Figures 2-1 and 2-2. In addition, LatticeECP-DSP supports an additional row of DSP blocks, as shown in Figure 2-2.

There are two kinds of logic blocks, the Programmable Functional Unit (PFU) and Programmable Functional unit without RAM/ROM (PFF). The PFU contains the building blocks for logic, arithmetic, RAM, ROM and register functions. The PFF block contains building blocks for logic, arithmetic and ROM functions. Both PFU and PFF blocks are optimized for flexibility, allowing complex designs to be implemented quickly and efficiently. Logic Blocks are arranged in a two-dimensional array. Only one type of block is used per row. The PFU blocks are used on the outside rows. The rest of the core consists of rows of PFF blocks interspersed with rows of PFU blocks. For every three rows of PFF blocks there is a row of PFU blocks.

Each PIC block encompasses two PIOs (PIO pairs) with their respective sysI/O interfaces. PIO pairs on the left and right edges of the device can be configured as LVDS transmit/receive pairs. sysMEM EBRs are large dedicated fast memory blocks. They can be configured as RAM or ROM.

The PFU, PFF, PIC and EBR Blocks are arranged in a two-dimensional grid with rows and columns as shown in Figure 2-1. The blocks are connected with many vertical and horizontal routing channel resources. The place and route software tool automatically allocates these routing resources.

At the end of the rows containing the sysMEM Blocks are the sysCLOCK Phase Locked Loop (PLL) Blocks. These PLLs have multiply, divide and phase shifting capability; they are used to manage the phase relationship of the clocks. The LatticeECP/EC architecture provides up to four PLLs per device.

Every device in the family has a JTAG Port with internal Logic Analyzer (ispTRACY) capability. The sysCONFIG<sup>™</sup> port which allows for serial or parallel device configuration. The LatticeECP/EC devices use 1.2V as their core voltage.

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### **Modes of Operation**

Each Slice is capable of four modes of operation: Logic, Ripple, RAM and ROM. The Slice in the PFF is capable of all modes except RAM. Table 2-2 lists the modes and the capability of the Slice blocks.

#### Table 2-2. Slice Modes

|           | Logic              | Ripple                | RAM     | ROM         |

|-----------|--------------------|-----------------------|---------|-------------|

| PFU Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | SPR16x2 | ROM16x1 x 2 |

| PFF Slice | LUT 4x2 or LUT 5x1 | 2-bit Arithmetic Unit | N/A     | ROM16x1 x 2 |

**Logic Mode:** In this mode, the LUTs in each Slice are configured as 4-input combinatorial lookup tables. A LUT4 can have 16 possible input combinations. Any logic function with four inputs can be generated by programming this lookup table. Since there are two LUT4s per Slice, a LUT5 can be constructed within one Slice. Larger lookup tables such as LUT6, LUT7 and LUT8 can be constructed by concatenating other Slices.

**Ripple Mode:** Ripple mode allows the efficient implementation of small arithmetic functions. In ripple mode, the following functions can be implemented by each Slice:

- Addition 2-bit

- Subtraction 2-bit

- Add/Subtract 2-bit using dynamic control

- Up counter 2-bit

- Down counter 2-bit

- Ripple mode multiplier building block

- Comparator functions of A and B inputs

- A greater-than-or-equal-to B

- A not-equal-to B

- A less-than-or-equal-to B

Ripple Mode includes an optional configuration that performs arithmetic using fast carry chain methods. In this configuration (also referred to as CCU2 mode) two additional signals, Carry Generate and Carry Propagate, are generated on a per slice basis to allow fast arithmetic functions to be constructed by concatenating Slices.

**RAM Mode:** In this mode, distributed RAM can be constructed using each LUT block as a 16x1-bit memory. Through the combination of LUTs and Slices, a variety of different memories can be constructed.

The Lattice design tools support the creation of a variety of different size memories. Where appropriate, the software will construct these using distributed memory primitives that represent the capabilities of the PFU. Table 2-3 shows the number of Slices required to implement different distributed RAM primitives. Figure 2-5 shows the distributed memory primitive block diagrams. Dual port memories involve the pairing of two Slices, one Slice functions as the read-write port. The other companion Slice supports the read-only port. For more information about using RAM in LatticeECP/EC devices, please see the list of technical documentation at the end of this data sheet.

#### Table 2-3. Number of Slices Required For Implementing Distributed RAM

|                  | SPR16x2 | DPR16x2 |

|------------------|---------|---------|

| Number of slices | 1       | 2       |

|                  |         |         |

Note: SPR = Single Port RAM, DPR = Dual Port RAM

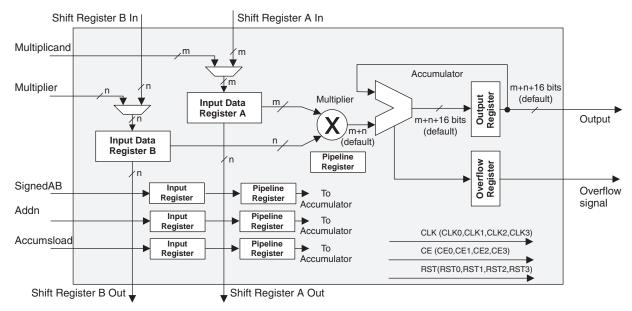

#### Figure 2-20. MAC sysDSP Element

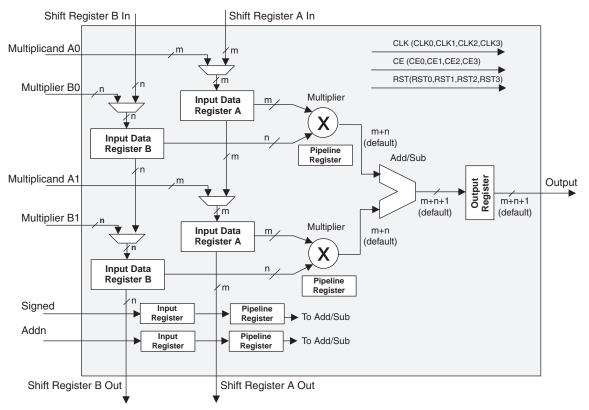

### **MULTADD sysDSP Element**

In this case, the operands A0 and B0 are multiplied and the result is added/subtracted with the result of the multiplier operation of operands A1 and A2. The user can enable the input, output and pipeline registers. Figure 2-21 shows the MULTADD sysDSP element.

#### Figure 2-21. MULTADD

### Signed and Unsigned with Different Widths

The DSP block supports different widths of signed and unsigned multipliers besides x9, x18 and x36 widths. For unsigned operands, unused upper data bits should be filled to create a valid x9, x18 or x36 operand. For signed two's complement operands, sign extension of the most significant bit should be performed until x9, x18 or x36 width is reached. Table 2-8 provides an example of this.

| Number | Unsigned | Unsigned<br>9-bit | Unsigned<br>18-bit | Signed | Two's Complement<br>Signed 9-Bits | Two's Complement<br>Signed 18-bits |

|--------|----------|-------------------|--------------------|--------|-----------------------------------|------------------------------------|

| +5     | 0101     | 000000101         | 00000000000000101  | 0101   | 00000101                          | 00000000000000101                  |

| -6     | 0110     | 000000110         | 0000000000000110   | 1010   | 111111010                         | 111111111111111010                 |

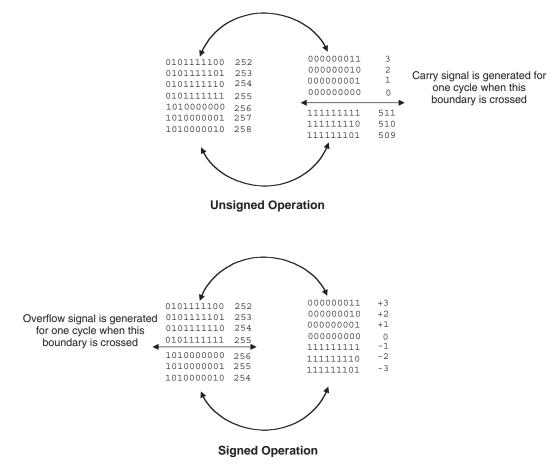

### **OVERFLOW Flag from MAC**

The sysDSP block provides an overflow output to indicate that the accumulator has overflowed. When two unsigned numbers are added and the result is a smaller number then accumulator roll over is said to occur and overflow signal is indicated. When two positive numbers are added with a negative sum and when two negative numbers are added with a positive sum, then the accumulator "roll-over" is said to have occurred and an overflow signal is indicated. Note when overflow occurs the overflow flag is present for only one cycle. By counting these overflow pulses in FPGA logic, larger accumulators can be constructed. The conditions overflow signals for signed and unsigned operands are listed in Figure 2-23.

#### Figure 2-23. Accumulator Overflow/Underflow Conditions

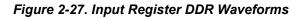

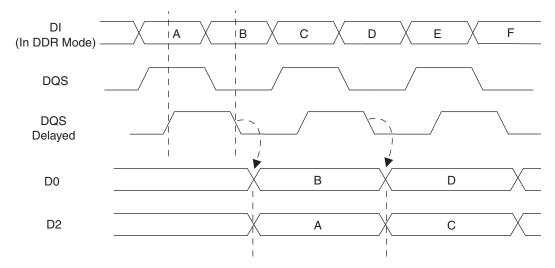

#### Figure 2-28. INDDRXB Primitive

#### **Output Register Block**

The output register block provides the ability to register signals from the core of the device before they are passed to the sysl/O buffers. The block contains a register for SDR operation that is combined with an additional latch for DDR operation. Figure 2-29 shows the diagram of the Output Register Block.

In SDR mode, ONEG0 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a Dtype or latch. In DDR mode, ONEG0 is fed into one register on the positive edge of the clock and OPOS0 is latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

Figure 2-30 shows the design tool DDR primitives. The SDR output register has reset and clock enable available. The additional register for DDR operation does not have reset or clock enable available.

### Typical I/O Behavior During Power-up

The internal power-on-reset (POR) signal is deactivated when  $V_{CC}$  and  $V_{CCAUX}$  have reached satisfactory levels. After the POR signal is deactivated, the FPGA core logic becomes active. It is the user's responsibility to ensure that all other  $V_{CCIO}$  banks are active with valid input logic levels to properly control the output logic states of all the I/O banks that are critical to the application. For more information about controlling the output logic state with valid input logic levels during power-up in LatticeECP/EC devices, see the list of technical documentation at the end of this data sheet.

The V<sub>CC</sub> and V<sub>CCAUX</sub> supply the power to the FPGA core fabric, whereas the V<sub>CCIO</sub> supplies power to the I/O buffers. In order to simplify system design while providing consistent and predictable I/O behavior, it is recommended that the I/O buffers be powered-up prior to the FPGA core fabric. V<sub>CCIO</sub> supplies should be powered-up before or together with the V<sub>CC</sub> and V<sub>CCAUX</sub> supplies.

### **Supported Standards**

The LatticeECP/EC sysl/O buffer supports both single-ended and differential standards. Single-ended standards can be further subdivided into LVCMOS, LVTTL and other standards. The buffers support the LVTTL, LVCMOS 1.2, 1.5, 1.8, 2.5 and 3.3V standards. In the LVCMOS and LVTTL modes, the buffer has individually configurable options for drive strength, bus maintenance (weak pull-up, weak pull-down, or a bus-keeper latch) and open drain. Other single-ended standards supported include SSTL and HSTL. Differential standards supported include LVDS, BLVDS, LVPECL, RSDS, differential SSTL and differential HSTL. Tables 2-13 and 2-14 show the I/O standards (together with their supply and reference voltages) supported by the LatticeECP/EC devices. For further information about utilizing the sysl/O buffer to support a variety of standards please see the the list of technical information at the end of this data sheet.

| Input Standard                       | V <sub>REF</sub> (Nom.) | V <sub>CCIO</sub> <sup>1</sup> (Nom.) |  |  |  |

|--------------------------------------|-------------------------|---------------------------------------|--|--|--|

| Single Ended Interfaces              |                         |                                       |  |  |  |

| LVTTL                                | —                       | —                                     |  |  |  |

| LVCMOS33 <sup>2</sup>                | —                       | —                                     |  |  |  |

| LVCMOS25 <sup>2</sup>                | —                       | —                                     |  |  |  |

| LVCMOS18                             | —                       | 1.8                                   |  |  |  |

| LVCMOS15                             | _                       | 1.5                                   |  |  |  |

| LVCMOS12 <sup>2</sup>                | —                       | —                                     |  |  |  |

| PCI                                  | —                       | 3.3                                   |  |  |  |

| HSTL18 Class I, II                   | 0.9                     | —                                     |  |  |  |

| HSTL18 Class III                     | 1.08                    | —                                     |  |  |  |

| HSTL15 Class I                       | 0.75                    | —                                     |  |  |  |

| HSTL15 Class III                     | 0.9                     | —                                     |  |  |  |

| SSTL3 Class I, II                    | 1.5                     | —                                     |  |  |  |

| SSTL2 Class I, II                    | 1.25                    | —                                     |  |  |  |

| SSTL18 Class I                       | 0.9                     | —                                     |  |  |  |

| Differential Interfaces              |                         |                                       |  |  |  |

| Differential SSTL18 Class I          | —                       | —                                     |  |  |  |

| Differential SSTL2 Class I, II       | —                       | —                                     |  |  |  |

| Differential SSTL3 Class I, II       | —                       | —                                     |  |  |  |

| Differential HSTL15 Class I, III     | —                       | —                                     |  |  |  |

| Differential HSTL18 Class I, II, III | —                       | —                                     |  |  |  |

| LVDS, LVPECL, BLVDS, RSDS            | —                       | —                                     |  |  |  |

#### Table 2-13. Supported Input Standards

1. When not specified  $V_{\mbox{\scriptsize CCIO}}$  can be set anywhere in the valid operating range.

2. JTAG inputs do not have a fixed threshold option and always follow  $V_{\mbox{CCJ.}}$

### LatticeECP/EC External Switching Characteristics

|                                 |                                                                   |             | -                 | 5    | -4    |      | -3    |      | <u> </u> |

|---------------------------------|-------------------------------------------------------------------|-------------|-------------------|------|-------|------|-------|------|----------|

| Parameter                       | Description                                                       | Device      | Min.              | Max. | Min.  | Max. | Min.  | Max. | Units    |

| General I/O                     | Pin Parameters (Using Primary Cl                                  | ock without | PLL) <sup>1</sup> |      |       |      |       |      |          |

|                                 |                                                                   | LFEC1       | _                 | 5.09 | _     | 6.11 | —     | 7.13 | ns       |

|                                 |                                                                   | LFEC3       | —                 | 5.71 | _     | 6.85 | —     | 7.99 | ns       |

|                                 |                                                                   | LFEC6       | _                 | 5.60 | —     | 6.72 | —     | 7.84 | ns       |

| t <sub>CO</sub> <sup>7</sup>    | Clock to Output - PIO Output<br>Register                          | LFEC10      | —                 | 5.47 | —     | 6.57 | —     | 7.66 | ns       |

|                                 | l logistoi                                                        | LFEC15      | _                 | 5.67 | —     | 6.81 | —     | 7.94 | ns       |

|                                 |                                                                   | LFEC20      | _                 | 5.89 | —     | 7.07 | —     | 8.25 | ns       |

|                                 |                                                                   | LFEC33      | _                 | 6.19 | —     | 7.42 | —     | 8.66 | ns       |

|                                 |                                                                   | LFEC1       | -0.08             | —    | -0.10 | —    | -0.12 |      | ns       |

|                                 |                                                                   | LFEC3       | -0.70             | —    | -0.84 | —    | -0.98 |      | ns       |

|                                 |                                                                   | LFEC6       | -0.63             | —    | -0.76 | —    | -0.89 |      | ns       |

| t <sub>SU</sub> 7               | Clock to Data Setup - PIO Input<br>Register                       | LFEC10      | -0.43             | —    | -0.52 | —    | -0.61 |      | ns       |

|                                 | l logistoi                                                        | LFEC15      | -0.70             | —    | -0.84 | —    | -0.98 |      | ns       |

|                                 |                                                                   | LFEC20      | -0.88             | —    | -1.06 | —    | -1.24 |      | ns       |

|                                 |                                                                   | LFEC33      | -1.12             | —    | -1.34 | —    | -1.56 |      | ns       |

|                                 |                                                                   | LFEC1       | 2.19              | —    | 2.62  | —    | 3.06  |      | ns       |

|                                 |                                                                   | LFEC3       | 2.80              | —    | 3.36  | —    | 3.92  |      | ns       |

|                                 |                                                                   | LFEC6       | 2.69              | —    | 3.23  | —    | 3.77  |      | ns       |

| t <sub>H</sub> 7                | Clock to Data Hold - PIO Input<br>Register                        | LFEC10      | 2.56              | —    | 3.08  | —    | 3.59  |      | ns       |

|                                 |                                                                   | LFEC15      | 2.76              | —    | 3.32  | —    | 3.87  |      | ns       |

|                                 |                                                                   | LFEC20      | 2.99              | —    | 3.58  | —    | 4.18  |      | ns       |

|                                 |                                                                   | LFEC33      | 3.28              | —    | 3.93  | —    | 4.59  |      | ns       |

|                                 |                                                                   | LFEC1       | 3.36              | —    | 4.03  | —    | 4.70  |      | ns       |

|                                 |                                                                   | LFEC3       | 2.74              | —    | 3.29  | —    | 3.84  |      | ns       |

|                                 |                                                                   | LFEC6       | 2.81              | —    | 3.37  | —    | 3.93  |      | ns       |

| t <sub>SU_DEL</sub> 7           | Clock to Data Setup - PIO Input<br>Register with Data Input Delay | LFEC10      | 3.01              | —    | 3.61  | —    | 4.21  |      | ns       |

|                                 |                                                                   | LFEC15      | 2.74              | —    | 3.29  | —    | 3.83  |      | ns       |

|                                 |                                                                   | LFEC20      | 2.56              | —    | 3.07  | —    | 3.58  |      | ns       |

|                                 |                                                                   | LFEC33      | 2.32              | —    | 2.79  | —    | 3.25  |      | ns       |

|                                 |                                                                   | LFEC1       | -1.31             | —    | -1.57 | —    | -1.83 |      | ns       |

|                                 |                                                                   | LFEC3       | -0.70             | —    | -0.83 | —    | -0.97 |      | ns       |

|                                 |                                                                   | LFEC6       | -0.80             | —    | -0.96 | —    | -1.12 |      | ns       |

| tH_DEL <sup>7</sup>             | Clock to Data Hold - PIO Input<br>Register with Input Data Delay  | LFEC10      | -0.93             | —    | -1.12 | —    | -1.30 |      | ns       |

|                                 | lingiotor mar input Data Dolay                                    | LFEC15      | -0.73             | —    | -0.88 | —    | -1.02 |      | ns       |

|                                 |                                                                   | LFEC20      | -0.51             | —    | -0.61 | —    | -0.71 | —    | ns       |

|                                 |                                                                   | LFEC33      | -0.22             | —    | -0.26 | —    | -0.30 | —    | ns       |

| f <sub>MAX_IO<sup>2</sup></sub> | Clock Frequency of I/O and PFU<br>Register                        | All         | _                 | 420  | —     | 378  | —     | 340  | Mhz      |

| DDR I/O Pin                     | Parameters <sup>3, 4, 5</sup>                                     |             |                   | -    | -     | -    | -     | •    |          |

| t <sub>DVADQ</sub>              | Data Valid After DQS (DDR Read)                                   | All         | —                 | 0.19 | —     | 0.19 | —     | 0.19 | UI       |

| t <sub>DVEDQ</sub>              | Data Hold After DQS (DDR Read)                                    | All         | 0.67              | —    | 0.67  | —    | 0.67  | —    | UI       |

### **Over Recommended Operating Conditions**

# sysCLOCK PLL Timing

| Parameter                       | Description                           | Conditions                                 | Min.  | Тур. | Max.    | Units |

|---------------------------------|---------------------------------------|--------------------------------------------|-------|------|---------|-------|

| f <sub>IN</sub>                 | Input Clock Frequency (CLKI, CLKFB)   |                                            | 25    | —    | 420     | MHz   |

| f <sub>ouт</sub>                | Output Clock Frequency (CLKOP, CLKOS) |                                            | 25    |      | 420     | MHz   |

| f <sub>OUT2</sub>               | K-Divider Output Frequency (CLKOK)    |                                            | 0.195 | _    | 210     | MHz   |

| f <sub>VCO</sub>                | PLL VCO Frequency                     |                                            | 420   | —    | 840     | MHz   |

| f <sub>PFD</sub>                | Phase Detector Input Frequency        |                                            | 25    |      | —       | MHz   |

| AC Characte                     | eristics                              |                                            |       |      |         |       |

| t <sub>DT</sub>                 | Output Clock Duty Cycle               | Default Duty Cycle<br>Elected <sup>3</sup> | 45    | 50   | 55      | %     |

| t <sub>PH</sub> ⁴               | Output Phase Accuracy                 |                                            | _     |      | 0.05    | UI    |

| t 1 Output Clock Devied I       | Output Clock Period Jitter            | f <sub>OUT</sub> >= 100MHz                 | —     |      | +/- 125 | ps    |

| <sup>t</sup> OPJIT <sup>1</sup> |                                       | f <sub>OUT</sub> < 100MHz                  | _     |      | 0.02    | UIPP  |

| t <sub>SK</sub>                 | Input Clock to Output Clock Skew      | Divider ratio = integer                    | _     |      | +/- 200 | ps    |

| t <sub>W</sub>                  | Output Clock Pulse Width              | At 90% or 10% <sup>3</sup>                 | 1     |      | —       | ns    |

| t <sub>LOCK</sub> <sup>2</sup>  | PLL Lock-in Time                      |                                            | _     |      | 150     | μs    |

| t <sub>PA</sub>                 | Programmable Delay Unit               |                                            | 100   | 250  | 450     | ps    |

| t <sub>IPJIT</sub>              | Input Clock Period Jitter             |                                            | —     |      | +/- 200 | ps    |

| t <sub>FBKDLY</sub>             | External Feedback Delay               |                                            | —     | _    | 10      | ns    |

| t <sub>HI</sub>                 | Input Clock High Time                 | 90% to 90%                                 | 0.5   |      | —       | ns    |

| t <sub>LO</sub>                 | Input Clock Low Time                  | 10% to 10%                                 | 0.5   | —    | —       | ns    |

| t <sub>RST</sub>                | RST Pulse Width                       |                                            | 10    |      | —       | ns    |

1. Jitter sample is taken over 10,000 samples of the primary PLL output with clean reference clock.

2. Output clock is valid after  $t_{\rm LOCK}$  for PLL reset and dynamic delay adjustment. 3. Using LVDS output buffers.

4. Relative to CLKOP.

Timing v.G 0.30

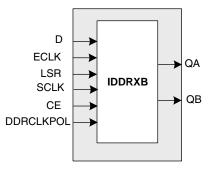

# **JTAG Port Timing Specifications**

#### **Over Recommended Operating Conditions**

| Symbol               | Parameter                                                          | Min | Max | Units |

|----------------------|--------------------------------------------------------------------|-----|-----|-------|

| f <sub>MAX</sub>     | TCK clock frequency                                                | _   | 25  | MHz   |

| t <sub>BTCP</sub>    | TCK [BSCAN] clock pulse width                                      | 40  | —   | ns    |

| t <sub>BTCPH</sub>   | TCK [BSCAN] clock pulse width high                                 | 20  | —   | ns    |

| t <sub>BTCPL</sub>   | TCK [BSCAN] clock pulse width low                                  | 20  | —   | ns    |

| t <sub>BTS</sub>     | TCK [BSCAN] setup time                                             | 8   | —   | ns    |

| t <sub>BTH</sub>     | TCK [BSCAN] hold time                                              | 10  | —   | ns    |

| t <sub>BTRF</sub>    | TCK [BSCAN] rise/fall time                                         |     | —   | mV/ns |

| t <sub>BTCO</sub>    | TAP controller falling edge of clock to valid output               |     | 10  | ns    |

| t <sub>BTCODIS</sub> | TAP controller falling edge of clock to valid disable              |     | 10  | ns    |

| t <sub>BTCOEN</sub>  | TAP controller falling edge of clock to valid enable               |     | 10  | ns    |

| t <sub>BTCRS</sub>   | BSCAN test capture register setup time                             |     | —   | ns    |

| t <sub>BTCRH</sub>   | BSCAN test capture register hold time                              |     | —   | ns    |

| t <sub>BUTCO</sub>   | BSCAN test update register, falling edge of clock to valid output  |     | 25  | ns    |

| t <sub>BTUODIS</sub> | BSCAN test update register, falling edge of clock to valid disable |     | 25  | ns    |

| t <sub>BTUPOEN</sub> | BSCAN test update register, falling edge of clock to valid enable  |     | 25  | ns    |

Timing v.G 0.30

# LatticeECP/EC Family Data Sheet Pinout Information

#### September 2012

**Data Sheet**

### **Signal Descriptions**

| Signal Name                               | I/O    | Description                                                                                                                                                                                                                                                          |  |  |

|-------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| General Purpose                           |        |                                                                                                                                                                                                                                                                      |  |  |

|                                           |        | [Edge] indicates the edge of the device on which the pad is located. Valid edge designations are L (Left), B (Bottom), R (Right), T (Top).                                                                                                                           |  |  |

|                                           |        | [Row/Column Number] indicates the PFU row or the column of the device on which the PIC exists. When Edge is T (Top) or (Bottom), only need to specify Row Number. When Edge is L (Left) or R (Right), only need to specify Column Number.                            |  |  |

| P[Edge] [Row/Column Number*]_[A/B]        | I/O    | [A/B] indicates the PIO within the PIC to which the pad is connected.                                                                                                                                                                                                |  |  |

|                                           |        | Some of these user-programmable pins are shared with special function pins. These pin when not used as special purpose pins can be programmed as I/Os for user logic.                                                                                                |  |  |

|                                           |        | During configuration the user-programmable I/Os are tri-stated with an inter-<br>nal pull-up resistor enabled. If any pin is not used (or not bonded to a pack-<br>age pin), it is also tri-stated with an internal pull-up resistor enabled after<br>configuration. |  |  |

| GSRN                                      | I      | Global RESET signal (active low). Any I/O pin can be GSRN.                                                                                                                                                                                                           |  |  |

| NC                                        | _      | No connect.                                                                                                                                                                                                                                                          |  |  |

| GND                                       | _      | Ground. Dedicated pins.                                                                                                                                                                                                                                              |  |  |

| V <sub>CC</sub>                           | _      | Power supply pins for core logic. Dedicated pins.                                                                                                                                                                                                                    |  |  |

| V <sub>CCAUX</sub>                        | _      | Auxiliary power supply pin. It powers all the differential and referenced input buffers. Dedicated pins.                                                                                                                                                             |  |  |

| V <sub>CCIOx</sub>                        |        | Power supply pins for I/O bank x. Dedicated pins.                                                                                                                                                                                                                    |  |  |

| V <sub>REF1_x</sub> , V <sub>REF2_x</sub> | _      | Reference supply pins for I/O bank x. Pre-determined pins in each bank are assigned as $V_{\text{REF}}$ inputs. When not used, they may be used as I/O pins.                                                                                                         |  |  |

| XRES                                      | _      | 10K ohm +/-1% resistor must be connected between this pad and ground.                                                                                                                                                                                                |  |  |

| V <sub>CCPLL</sub>                        |        | Power supply pin for PLL.pApplicable to ECP/EC33 device.                                                                                                                                                                                                             |  |  |

|                                           | progra | ammable I/O pins when not in use for PLL or clock pins)                                                                                                                                                                                                              |  |  |

| [LOC][num]_PLL[T, C]_IN_A                 | I      | Reference clock (PLL) input pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A,B,Cat each side.                                                                                                                               |  |  |

| [LOC][num]_PLL[T, C]_FB_A                 | I      | Optional feedback (PLL) input pads: ULM, LLM, URM, LRM, num = row from center, $T =$ true and $C =$ complement, index A,B,Cat each side.                                                                                                                             |  |  |

| PCLK[T, C]_[n:0]_[3:0]                    | I      | Primary Clock pads, $T =$ true and $C =$ complement, n per side, indexed by bank and 0,1,2,3 within bank.                                                                                                                                                            |  |  |

| [LOC]DQS[num]                             | I      | DQS input pads: T (Top), R (Right), B (Bottom), L (Left), DQS, num = ball function number. Any pad can be configured to be output.                                                                                                                                   |  |  |

| Test and Programming (Dedicated pins)     |        |                                                                                                                                                                                                                                                                      |  |  |

| TMS                                       | I      | Test Mode Select input, used to control the 1149.1 state machine. Pull-up is enabled during configuration.                                                                                                                                                           |  |  |

| тск                                       | I      | Test Clock input pin, used to clock the 1149.1 state machine. No pull-up enabled.                                                                                                                                                                                    |  |  |

<sup>© 2012</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

# Signal Descriptions (Cont.)

| Signal Name                            | I/O   | Description                                                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| тді                                    | I     | Test Data in pin. Used to load data into device using 1149.1 state machine.<br>After power-up, this TAP port can be activated for configuration by sending<br>appropriate command. (Note: once a configuration port is selected it is<br>locked. Another configuration port cannot be selected until the power-up<br>sequence). Pull-up is enabled during configuration. |  |  |

| TDO                                    | 0     | Output pin. Test Data out pin used to shift data out of device using 1149.1.                                                                                                                                                                                                                                                                                             |  |  |

| V <sub>CCJ</sub>                       | _     | V <sub>CCJ</sub> - The power supply pin for JTAG Test Access Port.                                                                                                                                                                                                                                                                                                       |  |  |

| Configuration Pads (used during sysCOI | NFIG) |                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| CFG[2:0]                               | I     | Mode pins used to specify configuration modes values latched on rising edge of INITN. During configuration, a pull-up is enabled. These are dedicated pins.                                                                                                                                                                                                              |  |  |

| INITN                                  | I/O   | Open Drain pin. Indicates the FPGA is ready to be configured. During configuration, a pull-up is enabled. It is a dedicated pin.                                                                                                                                                                                                                                         |  |  |

| PROGRAMN                               | I     | Initiates configuration sequence when asserted low. This pin always has an active pull-up. This is a dedicated pin.                                                                                                                                                                                                                                                      |  |  |

| DONE                                   | I/O   | Open Drain pin. Indicates that the configuration sequence is complete, and the startup sequence is in progress. This is a dedicated pin.                                                                                                                                                                                                                                 |  |  |

| CCLK                                   | I/O   | Configuration Clock for configuring an FPGA in sysCONFIG mode.                                                                                                                                                                                                                                                                                                           |  |  |

| BUSY/SISPI                             | I/O   | Read control command in SPI3 or SPIX mode.                                                                                                                                                                                                                                                                                                                               |  |  |

| CSN                                    | I     | sysCONFIG chip select (Active low). During configuration, a pull-up is enabled.                                                                                                                                                                                                                                                                                          |  |  |

| CS1N                                   | I     | sysCONFIG chip select (Active low). During configuration, a pull-up is enabled.                                                                                                                                                                                                                                                                                          |  |  |

| WRITEN                                 | I     | Write Data on Parallel port (Active low).                                                                                                                                                                                                                                                                                                                                |  |  |

| D[7:0]/SPID[0:7]                       | I/O   | sysCONFIG Port Data I/O.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DOUT/CSON                              | 0     | Output for serial configuration data (rising edge of CCLK) when using sys-<br>CONFIG port.                                                                                                                                                                                                                                                                               |  |  |

| DI/CSSPIN                              | I/O   | Input for serial configuration data (clocked with CCLK) when using sysCOI<br>FIG port. During configuration, a pull-up is enabled. Output when used in<br>SPI/SPIX modes.                                                                                                                                                                                                |  |  |

# LFEC3 and LFECP/EC6 Logic Signal Connections: 256 fpBGA (Cont.)

| Ball   |               | L    | FEC3 |                | LFECP6/LFEC6  |      |      |                |  |  |

|--------|---------------|------|------|----------------|---------------|------|------|----------------|--|--|

| Number | Ball Function | Bank | LVDS | Dual Function  | Ball Function | Bank | LVDS | Dual Function  |  |  |

| K2     | PL11A         | 6    | Т    | LLM0_PLLT_IN_A | PL20A         | 6    | Т    | LLM0_PLLT_IN_A |  |  |

| K1     | PL11B         | 6    | С    | LLM0_PLLC_IN_A | PL20B         | 6    | С    | LLM0_PLLC_IN_A |  |  |

| L2     | PL12A         | 6    | Т    | LLM0_PLLT_FB_A | PL21A         | 6    | Т    | LLM0_PLLT_FB_A |  |  |

| L1     | PL12B         | 6    | С    | LLM0_PLLC_FB_A | PL21B         | 6    | С    | LLM0_PLLC_FB_A |  |  |

| M2     | PL13A         | 6    | Т    |                | PL22A         | 6    | Т    |                |  |  |

| M1     | PL13B         | 6    | С    |                | PL22B         | 6    | С    |                |  |  |

| N1     | PL14A         | 6    | Т    |                | PL23A         | 6    | Т    |                |  |  |

| GND    | GND6          | 6    |      |                | GND6          | 6    |      |                |  |  |

| N2     | PL14B         | 6    | С    |                | PL23B         | 6    | С    |                |  |  |

| M4     | PL15A         | 6    | Т    | LDQS15         | PL24A         | 6    | Т    | LDQS24         |  |  |

| M3     | PL15B         | 6    | С    |                | PL24B         | 6    | С    |                |  |  |

| P1     | PL16A         | 6    | Т    |                | PL25A         | 6    | Т    |                |  |  |

| R1     | PL16B         | 6    | С    |                | PL25B         | 6    | С    |                |  |  |

| P2     | PL17A         | 6    | Т    |                | PL26A         | 6    | Т    |                |  |  |

| P3     | PL17B         | 6    | С    |                | PL26B         | 6    | С    |                |  |  |

| N3     | PL18A         | 6    | Т    | VREF1_6        | PL27A         | 6    | Т    | VREF1_6        |  |  |

| N4     | PL18B         | 6    | С    | VREF2_6        | PL27B         | 6    | С    | VREF2_6        |  |  |

| GND    | GND6          | 6    |      |                | GND6          | 6    |      |                |  |  |

| GND    | GND5          | 5    |      |                | GND5          | 5    |      |                |  |  |

| P4     | PB2A          | 5    | Т    |                | PB2A          | 5    | Т    |                |  |  |

| N5     | PB2B          | 5    | С    |                | PB2B          | 5    | С    |                |  |  |

| P5     | PB3A          | 5    | Т    |                | PB3A          | 5    | Т    |                |  |  |

| P6     | PB3B          | 5    | С    |                | PB3B          | 5    | С    |                |  |  |

| R4     | PB4A          | 5    | Т    |                | PB4A          | 5    | Т    |                |  |  |

| R3     | PB4B          | 5    | С    |                | PB4B          | 5    | С    |                |  |  |

| T2     | PB5A          | 5    | Т    |                | PB5A          | 5    | Т    |                |  |  |

| Т3     | PB5B          | 5    | С    |                | PB5B          | 5    | С    |                |  |  |

| R5     | PB6A          | 5    | Т    | BDQS6          | PB6A          | 5    | Т    | BDQS6          |  |  |

| R6     | PB6B          | 5    | С    |                | PB6B          | 5    | С    |                |  |  |

| T4     | PB7A          | 5    | Т    |                | PB7A          | 5    | Т    |                |  |  |

| T5     | PB7B          | 5    | С    |                | PB7B          | 5    | С    |                |  |  |

| N6     | PB8A          | 5    | Т    |                | PB8A          | 5    | Т    |                |  |  |

| M6     | PB8B          | 5    | С    |                | PB8B          | 5    | С    |                |  |  |

| T6     | PB9A          | 5    | Т    |                | PB9A          | 5    | Т    |                |  |  |

| GND    | GND5          | 5    |      |                | GND5          | 5    |      |                |  |  |

| T7     | PB9B          | 5    | С    |                | PB9B          | 5    | С    |                |  |  |

| P7     | PB10A         | 5    | Т    |                | PB10A         | 5    | Т    |                |  |  |

| N7     | PB10B         | 5    | С    |                | PB10B         | 5    | С    |                |  |  |

| R7     | PB11A         | 5    | Т    |                | PB11A         | 5    | Т    |                |  |  |

| R8     | PB11B         | 5    | С    |                | PB11B         | 5    | С    |                |  |  |

| M7     | PB12A         | 5    | T    |                | PB12A         | 5    | Т    |                |  |  |

| M8     | PB12B         | 5    | С    |                | PB12B         | 5    | С    |                |  |  |

| T8     | PB13A         | 5    | Т    |                | PB13A         | 5    | Т    |                |  |  |

# LFEC3 and LFECP/EC6 Logic Signal Connections: 256 fpBGA (Cont.)

| Ball   |                      | L    | FEC3 |                      | LFECP6/LFEC6  |      |      |                      |  |  |

|--------|----------------------|------|------|----------------------|---------------|------|------|----------------------|--|--|

| Number | <b>Ball Function</b> | Bank | LVDS | <b>Dual Function</b> | Ball Function | Bank | LVDS | <b>Dual Function</b> |  |  |

| E5     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| E8     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| M12    | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| M5     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| M9     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| B15    | VCCAUX               | -    |      |                      | VCCAUX        | -    |      |                      |  |  |

| R2     | VCCAUX               | -    |      |                      | VCCAUX        | -    |      |                      |  |  |

| F7     | VCCIO0               | 0    |      |                      | VCCIO0        | 0    |      |                      |  |  |

| F8     | VCCIO0               | 0    |      |                      | VCCIO0        | 0    |      |                      |  |  |

| F10    | VCCIO1               | 1    |      |                      | VCCIO1        | 1    |      |                      |  |  |

| F9     | VCCIO1               | 1    |      |                      | VCCIO1        | 1    |      |                      |  |  |

| G11    | VCCIO2               | 2    |      |                      | VCCIO2        | 2    |      |                      |  |  |

| H11    | VCCIO2               | 2    |      |                      | VCCIO2        | 2    |      |                      |  |  |

| J11    | VCCIO3               | 3    |      |                      | VCCIO3        | 3    |      |                      |  |  |

| K11    | VCCIO3               | 3    |      |                      | VCCIO3        | 3    |      |                      |  |  |

| L10    | VCCIO4               | 4    |      |                      | VCCIO4        | 4    |      |                      |  |  |

| L9     | VCCIO4               | 4    |      |                      | VCCIO4        | 4    |      |                      |  |  |

| L7     | VCCIO5               | 5    |      |                      | VCCIO5        | 5    |      |                      |  |  |

| L8     | VCCIO5               | 5    |      |                      | VCCIO5        | 5    |      |                      |  |  |

| J6     | VCCIO6               | 6    |      |                      | VCCIO6        | 6    |      |                      |  |  |

| K6     | VCCIO6               | 6    |      |                      | VCCIO6        | 6    |      |                      |  |  |

| G6     | VCCI07               | 7    |      |                      | VCCIO7        | 7    |      |                      |  |  |

| H6     | VCCI07               | 7    |      |                      | VCCIO7        | 7    |      |                      |  |  |

| F6     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| F11    | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| L11    | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

| L6     | VCC                  | -    |      |                      | VCC           | -    |      |                      |  |  |

# LFECP/EC10 and LFECP/EC15 Logic Signal Connections: 256 fpBGA (Cont.)

| Ball   |               | LFECF | 10/LFEC | :10            | LFECP15/LFEC15 |      |      |                |  |  |

|--------|---------------|-------|---------|----------------|----------------|------|------|----------------|--|--|

| Number | Ball Function | Bank  | LVDS    | Dual Function  | Ball Function  | Bank | LVDS | Dual Function  |  |  |

| P14    | PR35B         | 3     | С       |                | PR43B          | 3    | С    |                |  |  |

| P15    | PR35A         | 3     | Т       |                | PR43A          | 3    | Т    |                |  |  |

| R15    | PR34B         | 3     | С       |                | PR42B          | 3    | С    |                |  |  |

| R16    | PR34A         | 3     | Т       |                | PR42A          | 3    | Т    |                |  |  |

| M13    | PR33B         | 3     | С       |                | PR41B          | 3    | С    |                |  |  |

| M14    | PR33A         | 3     | Т       | RDQS33         | PR41A          | 3    | Т    | RDQS41         |  |  |

| P16    | PR32B         | 3     | С       | RLM0_PLLC_FB_A | PR40B          | 3    | С    | RLM0_PLLC_FB_A |  |  |

| GND    | GND3          | 3     |         |                | GND3           | 3    |      |                |  |  |

| N16    | PR32A         | 3     | Т       | RLM0_PLLT_FB_A | PR40A          | 3    | Т    | RLM0_PLLT_FB_A |  |  |

| N15    | PR31B         | 3     | С       | RLM0_PLLC_IN_A | PR39B          | 3    | С    | RLM0_PLLC_IN_A |  |  |

| M15    | PR31A         | 3     | Т       | RLM0_PLLT_IN_A | PR39A          | 3    | Т    | RLM0_PLLT_IN_A |  |  |

| M16    | PR30B         | 3     | С       | DI/CSSPIN      | PR38B          | 3    | С    | DI/CSSPIN      |  |  |

| L16    | PR30A         | 3     | Т       | DOUT/CSON      | PR38A          | 3    | Т    | DOUT/CSON      |  |  |

| K16    | PR29B         | 3     | С       | BUSY/SISPI     | PR37B          | 3    | С    | BUSY/SISPI     |  |  |

| J16    | PR29A         | 3     | Т       | D7/SPID0       | PR37A          | 3    | Т    | D7/SPID0       |  |  |

| L12    | CFG2          | 3     |         |                | CFG2           | 3    |      |                |  |  |

| L14    | CFG1          | 3     |         |                | CFG1           | 3    |      |                |  |  |

| L13    | CFG0          | 3     |         |                | CFG0           | 3    |      |                |  |  |

| K13    | PROGRAMN      | 3     |         |                | PROGRAMN       | 3    |      |                |  |  |

| L15    | CCLK          | 3     |         |                | CCLK           | 3    |      |                |  |  |

| K15    | INITN         | 3     |         |                | INITN          | 3    |      |                |  |  |

| K14    | DONE          | 3     |         |                | DONE           | 3    |      |                |  |  |

| GND    | GND3          | 3     |         |                | GND3           | 3    |      |                |  |  |

| H16    | PR27B         | 3     | С       |                | PR31B          | 3    | С    |                |  |  |

| -      | -             | -     |         |                | GND3           | 3    |      |                |  |  |

| H15    | PR27A         | 3     | Т       |                | PR31A          | 3    | Т    |                |  |  |

| G16    | PR26B         | 3     | С       |                | PR30B          | 3    | С    |                |  |  |

| G15    | PR26A         | 3     | Т       |                | PR30A          | 3    | Т    |                |  |  |

| K12    | PR25B         | 3     | С       |                | PR29B          | 3    | С    |                |  |  |

| J12    | PR25A         | 3     | Т       |                | PR29A          | 3    | Т    |                |  |  |

| J14    | PR24B         | 3     | С       |                | PR28B          | 3    | С    |                |  |  |

| J15    | PR24A         | 3     | Т       | RDQS24         | PR28A          | 3    | Т    | RDQS28         |  |  |

| F16    | PR23B         | 3     | С       |                | PR27B          | 3    | С    |                |  |  |

| GND    | GND3          | 3     |         |                | GND3           | 3    |      |                |  |  |

| F15    | PR23A         | 3     | Т       |                | PR27A          | 3    | Т    |                |  |  |

| J13    | PR22B         | 3     | С       |                | PR26B          | 3    | С    |                |  |  |

| H13    | PR22A         | 3     | Т       |                | PR26A          | 3    | Т    |                |  |  |

| H14    | PR21B         | 3     | С       |                | PR25B          | 3    | С    |                |  |  |

| G14    | PR21A         | 3     | Т       |                | PR25A          | 3    | Т    |                |  |  |

| E16    | PR20B         | 3     | С       |                | PR24B          | 3    | С    |                |  |  |

| E15    | PR20A         | 3     | Т       |                | PR24A          | 3    | Т    |                |  |  |

| H12    | PR18B         | 2     | С       | PCLKC2_0       | PR22B          | 2    | С    | PCLKC2_0       |  |  |

| GND    | GND2          | 2     |         |                | GND2           | 2    |      |                |  |  |

# LFECP/EC20 and LFECP/EC33 Logic Signal Connections: 484 fpBGA (Cont.)

|             | LFECP         | 20/LFE | C20      |                | LFECP/LFEC33 |               |      |          |               |  |  |

|-------------|---------------|--------|----------|----------------|--------------|---------------|------|----------|---------------|--|--|

| Ball Number | Ball Function | Bank   | LVD<br>S | Dual Function  | Ball Number  | Ball Function | Bank | LVD<br>S | Dual Function |  |  |

| K3          | PL21A         | 7      | Т        |                | К3           | PL33A         | 7    | Т        |               |  |  |

| K2          | PL21B         | 7      | С        |                | K2           | PL33B         | 7    | С        |               |  |  |

| J1          | PL22A         | 7      | Т        | PCLKT7_0       | J1           | PL34A         | 7    | Т        | PCLKT7_0      |  |  |

| GND         | GND7          | 7      |          |                | GND          | GND7          | 7    |          |               |  |  |

| K1          | PL22B         | 7      | С        | PCLKC7_0       | K1           | PL34B         | 7    | С        | PCLKC7_0      |  |  |

| L3          | XRES          | 6      |          |                | L3           | XRES          | 6    |          |               |  |  |

| L4          | PL24A         | 6      | Т        |                | L4           | PL36A         | 6    | Т        |               |  |  |

| L5          | PL24B         | 6      | С        |                | L5           | PL36B         | 6    | С        |               |  |  |

| L2          | PL25A         | 6      | Т        |                | L2           | PL37A         | 6    | Т        |               |  |  |

| L1          | PL25B         | 6      | С        |                | L1           | PL37B         | 6    | С        |               |  |  |

| M4          | PL26A         | 6      | Т        |                | M4           | PL38A         | 6    | Т        |               |  |  |

| M5          | PL26B         | 6      | С        |                | M5           | PL38B         | 6    | С        |               |  |  |

| M1          | PL27A         | 6      | Т        |                | M1           | PL39A         | 6    | Т        |               |  |  |

| GND         | GND6          | 6      |          |                | GND          | GND6          | 6    |          |               |  |  |

| M2          | PL27B         | 6      | С        |                | M2           | PL39B         | 6    | С        |               |  |  |

| N3          | PL28A         | 6      | Т        | LDQS28         | N3           | PL40A         | 6    | Т        | LDQS40        |  |  |

| M3          | PL28B         | 6      | С        |                | M3           | PL40B         | 6    | С        |               |  |  |

| N5          | PL29A         | 6      | Т        |                | N5           | PL41A         | 6    | Т        |               |  |  |

| N4          | PL29B         | 6      | С        |                | N4           | PL41B         | 6    | С        |               |  |  |

| N1          | PL30A         | 6      | Т        |                | N1           | PL42A         | 6    | Т        |               |  |  |

| N2          | PL30B         | 6      | С        |                | N2           | PL42B         | 6    | С        |               |  |  |

| P1          | PL31A         | 6      | Т        |                | P1           | PL43A         | 6    | Т        |               |  |  |

| GND         | GND6          | 6      |          |                | GND          | GND6          | 6    |          |               |  |  |

| P2          | PL31B         | 6      | С        |                | P2           | PL43B         | 6    | С        |               |  |  |

| R6          | PL32A         | 6      | Т        |                | R6           | PL44A         | 6    | Т        |               |  |  |

| P5          | PL32B         | 6      | С        |                | P5           | PL44B         | 6    | С        |               |  |  |

| P3          | PL33A         | 6      | Т        |                | P3           | PL45A         | 6    | Т        |               |  |  |

| P4          | PL33B         | 6      | С        |                | P4           | PL45B         | 6    | С        |               |  |  |

| R1          | PL34A         | 6      | Т        |                | R1           | PL46A         | 6    | Т        |               |  |  |

| R2          | PL34B         | 6      | С        |                | R2           | PL46B         | 6    | С        |               |  |  |

| R5          | PL35A         | 6      | Т        |                | R5           | PL47A         | 6    | Т        |               |  |  |

| GND         | GND6          | 6      |          |                | GND          | GND6          | 6    |          |               |  |  |

| R4          | PL35B         | 6      | С        |                | R4           | PL47B         | 6    | С        |               |  |  |

| T1          | PL36A         | 6      | Т        | LDQS36         | T1           | PL48A         | 6    | Т        | LDQS48        |  |  |

| T2          | PL36B         | 6      | С        |                | T2           | PL48B         | 6    | С        |               |  |  |

| R3          | PL37A         | 6      | Т        |                | R3           | PL49A         | 6    | Т        |               |  |  |

| T3          | PL37B         | 6      | С        |                | Т3           | PL49B         | 6    | С        |               |  |  |

| GND         | GND6          | 6      |          |                | GND          | GND6          | 6    |          |               |  |  |

| T5          | ТСК           | 6      |          |                | T5           | ТСК           | 6    | -        |               |  |  |

| U5          | TDI           | 6      |          |                | U5           | TDI           | 6    |          |               |  |  |

| T4          | TMS           | 6      |          |                | T4           | TMS           | 6    |          |               |  |  |

| U1          | TDO           | 6      |          |                | U1           | TDO           | 6    | -        |               |  |  |

| U2          | VCCJ          | 6      |          |                | U2           | VCCJ          | 6    |          |               |  |  |

| V1          | PL41A         | 6      | Т        | LLM0_PLLT_IN_A | V1           | PL53A         | 6    | Т        | LLM0_PLLT_IN_ |  |  |

# LFECP/EC20 and LFECP/EC33 Logic Signal Connections: 484 fpBGA (Cont.)

|             | LFECP         | 20/LFE | C20      |               | LFECP/LFEC33 |               |      |          |               |  |  |

|-------------|---------------|--------|----------|---------------|--------------|---------------|------|----------|---------------|--|--|

| Ball Number | Ball Function | Bank   | LVD<br>S | Dual Function | Ball Number  | Ball Function | Bank | LVD<br>S | Dual Function |  |  |

| A7          | PT27B         | 0      | С        |               | A7           | PT27B         | 0    | С        |               |  |  |

| A6          | PT27A         | 0      | Т        |               | A6           | PT27A         | 0    | Т        |               |  |  |

| B7          | PT26B         | 0      | С        |               | B7           | PT26B         | 0    | С        |               |  |  |

| B8          | PT26A         | 0      | Т        |               | B8           | PT26A         | 0    | Т        |               |  |  |

| A5          | PT25B         | 0      | С        |               | A5           | PT25B         | 0    | С        |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| B6          | PT25A         | 0      | Т        |               | B6           | PT25A         | 0    | Т        |               |  |  |

| G10         | PT24B         | 0      | С        |               | G10          | PT24B         | 0    | С        |               |  |  |

| E10         | PT24A         | 0      | Т        |               | E10          | PT24A         | 0    | Т        |               |  |  |

| F10         | PT23B         | 0      | С        |               | F10          | PT23B         | 0    | С        |               |  |  |

| D10         | PT23A         | 0      | Т        |               | D10          | PT23A         | 0    | Т        |               |  |  |

| G9          | PT22B         | 0      | С        |               | G9           | PT22B         | 0    | С        |               |  |  |

| E9          | PT22A         | 0      | Т        | TDQS22        | E9           | PT22A         | 0    | Т        | TDQS22        |  |  |

| C9          | PT21B         | 0      | С        |               | C9           | PT21B         | 0    | С        |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| C8          | PT21A         | 0      | Т        |               | C8           | PT21A         | 0    | Т        |               |  |  |

| F9          | PT20B         | 0      | С        |               | F9           | PT20B         | 0    | С        |               |  |  |

| D9          | PT20A         | 0      | Т        |               | D9           | PT20A         | 0    | Т        |               |  |  |

| F8          | PT19B         | 0      | С        |               | F8           | PT19B         | 0    | С        |               |  |  |

| D7          | PT19A         | 0      | Т        |               | D7           | PT19A         | 0    | Т        |               |  |  |

| D8          | PT18B         | 0      | С        |               | D8           | PT18B         | 0    | С        |               |  |  |

| C7          | PT18A         | 0      | Т        |               | C7           | PT18A         | 0    | Т        |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| A4          | PT17B         | 0      | С        |               | A4           | PT17B         | 0    | С        |               |  |  |

| B4          | PT17A         | 0      | Т        |               | B4           | PT17A         | 0    | Т        |               |  |  |

| C4          | PT16B         | 0      | С        |               | C4           | PT16B         | 0    | С        |               |  |  |

| C5          | PT16A         | 0      | Т        |               | C5           | PT16A         | 0    | Т        |               |  |  |

| D6          | PT15B         | 0      | С        |               | D6           | PT15B         | 0    | С        |               |  |  |

| B5          | PT15A         | 0      | Т        |               | B5           | PT15A         | 0    | Т        |               |  |  |

| E6          | PT14B         | 0      | С        |               | E6           | PT14B         | 0    | С        |               |  |  |

| C6          | PT14A         | 0      | Т        | TDQS14        | C6           | PT14A         | 0    | Т        | TDQS14        |  |  |

| A3          | PT13B         | 0      | С        |               | A3           | PT13B         | 0    | С        |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| B3          | PT13A         | 0      | Т        |               | B3           | PT13A         | 0    | Т        |               |  |  |

| F6          | PT12B         | 0      | С        |               | F6           | PT12B         | 0    | С        |               |  |  |

| D5          | PT12A         | 0      | Т        |               | D5           | PT12A         | 0    | Т        |               |  |  |

| F7          | PT11B         | 0      | С        |               | F7           | PT11B         | 0    | С        |               |  |  |

| E8          | PT11A         | 0      | Т        |               | E8           | PT11A         | 0    | Т        |               |  |  |

| G6          | PT10B         | 0      | С        |               | G6           | PT10B         | 0    | С        |               |  |  |

| E7          | PT10A         | 0      | Т        |               | E7           | PT10A         | 0    | Т        |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| GND         | GND0          | 0      |          |               | GND          | GND0          | 0    |          |               |  |  |

| A1          | GND           | -      |          |               | A1           | GND           | -    |          |               |  |  |

| A22         | GND           | -      |          |               | A22          | GND           | -    |          |               |  |  |

# LFECP/EC20, LFECP/EC33 Logic Signal Connections: 672 fpBGA

|                | LF               | EC20/L | FECP2 | D              | LFECP/EC33     |                  |      |      |                  |  |  |

|----------------|------------------|--------|-------|----------------|----------------|------------------|------|------|------------------|--|--|

| Ball<br>Number | Ball<br>Function | Bank   | LVDS  | Dual Function  | Ball<br>Number | Ball<br>Function | Bank | LVDS | Dual<br>Function |  |  |

| GND            | GND7             | 7      |       |                | GND            | GND7             | 7    |      |                  |  |  |

| E3             | PL2A             | 7      | Т     | VREF2_7        | E3             | PL2A             | 7    | Т    | VREF2_7          |  |  |

| E4             | PL2B             | 7      | С     | VREF1_7        | E4             | PL2B             | 7    | С    | VREF1_7          |  |  |

| E5             | NC               | -      |       |                | E5             | PL6A             | 7    | Т    | LDQS6            |  |  |

| D5             | NC               | -      |       |                | D5             | PL6B             | 7    | С    |                  |  |  |

| F4             | NC               | -      |       |                | F4             | PL7A             | 7    | Т    |                  |  |  |

| F5             | NC               | -      |       |                | F5             | PL7B             | 7    | С    |                  |  |  |

| C3             | NC               | -      |       |                | C3             | PL8A             | 7    | Т    |                  |  |  |

| D3             | NC               | -      |       |                | D3             | PL8B             | 7    | С    |                  |  |  |

| C2             | NC               | -      |       |                | C2             | PL9A             | 7    | Т    |                  |  |  |

| -              | -                | -      |       |                | GND            | GND7             | 7    |      |                  |  |  |

| B2             | NC               | -      |       |                | B2             | PL9B             | 7    | С    |                  |  |  |

| B1             | PL3A             | 7      | Т     |                | B1             | PL10A            | 7    | Т    |                  |  |  |

| C1             | PL3B             | 7      | С     |                | C1             | PL10B            | 7    | С    |                  |  |  |

| F3             | PL4A             | 7      | Т     |                | F3             | PL11A            | 7    | Т    |                  |  |  |

| G3             | PL4B             | 7      | С     |                | G3             | PL11B            | 7    | С    |                  |  |  |

| D2             | PL5A             | 7      | Т     |                | D2             | PL12A            | 7    | Т    |                  |  |  |