### Microchip Technology - AT90S1200-12SC Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 12MHz                                                                    |

| Connectivity               | SPI                                                                      |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 15                                                                       |

| Program Memory Size        | 1KB (512 x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64 x 8                                                                   |

| RAM Size                   | -                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C                                                               |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 20-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s1200-12sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Description

The AT90S1200 is a low-power CMOS 8-bit microcontroller based on the AVR RISC architecture. By executing powerful instructions in a single clock cycle, the AT90S1200 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with the 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

### **Block Diagram**

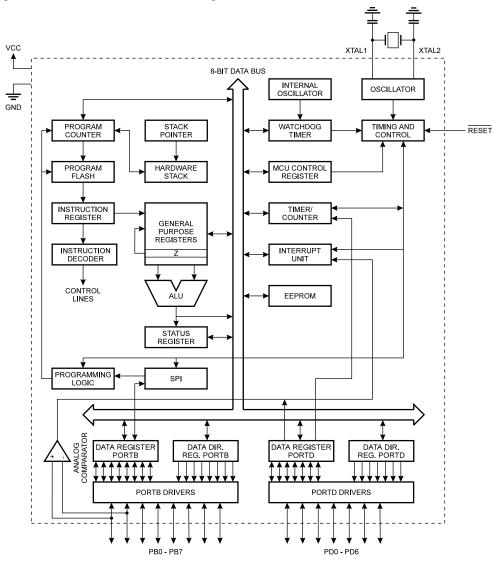

Figure 1. The AT90S1200 Block Diagram

The architecture supports high-level languages efficiently as well as extremely dense assembler code programs. The AT90S1200 provides the following features: 1K byte of In-System Programmable Flash, 64 bytes EEPROM, 15 general purpose I/O lines, 32 general purpose working registers, internal and external interrupts, programmable watchdog timer with internal oscillator, an SPI serial port for program downloading and two software selectable power-saving modes. The Idle Mode stops the CPU while allow-

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the stack. The stack is a 3-level-deep hardware stack dedicated for subroutines and interrupts.

The I/O memory space contains 64 addresses for CPU peripheral functions such as Control Registers, Timer/Counters, A/D Converters and other I/O functions. The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All the different interrupts have a separate interrupt vector in the interrupt vector table at the beginning of the program memory. The different interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

### General Purpose Register File

Figure 5 shows the structure of the 32 general purpose registers in the CPU.

Figure 5. AVR CPU General Purpose Working Registers

General Purpose Working Registers

| 7                | 0 |

|------------------|---|

| R0               |   |

| R1               |   |

| R2               |   |

|                  |   |

|                  |   |

| R28              |   |

| R29              |   |

| R30 (Z-Register) |   |

| R31              |   |

All the register operating instructions in the instruction set have direct and single cycle access to all registers. The only exception is the five constant arithmetic and logic instructions SBCI, SUBI, CPI, ANDI, ORI between a constant and a register and the LDI instruction for load immediate constant data. These instructions apply to the second half of the registers in the register file (R16..R31). The general SBC, SUB, CP, AND, OR and all other operations between two registers or on a single register apply to the entire register file.

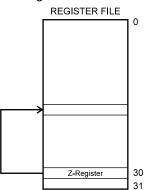

Register 30 also serves as an 8-bit pointer for indirect address of the register file.

ALU – Arithmetic Logic Unit The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, ALU operations between registers in the register file are executed. The ALU operations are divided into three main categories – arithmetic, logic and bit-functions.

In-SystemThe AT90S1200 contains 1K bytes On-chip In-System Programmable Flash memory for<br/>program storage. Since all instructions are single 16-bit words, the Flash is organized as<br/>512 x 16. The Flash memory has an endurance of at least 1000 write/erase cycles.

The AT90S1200 Program Counter is 9 bits wide, thus addressing the 512 words Flash program memory.

See page 37 for a detailed description on Flash data downloading.

### Program and Data Addressing Modes

The AT90S1200 AVR RISC Microcontroller supports powerful and efficient addressing modes. This section describes the different addressing modes supported in the AT90S1200. In the figures, OP means the operation code part of the instruction word. To simplify, not all figures show the exact location of the addressing bits.

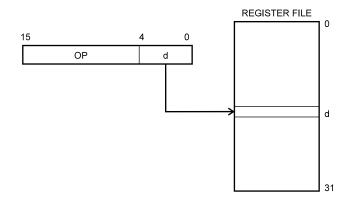

Register Direct, Single Register Rd Figure 6. Direct Single Register Addressing

The operand is contained in register d (Rd).

**Register Indirect**

Figure 7. Indirect Register Addressing

The register accessed is the one pointed to by the Z-register (R30).

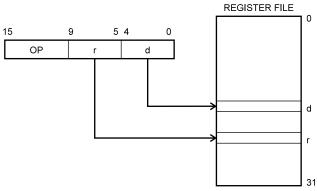

| <b>Register Direct, Two Registers</b> | Figure 8. | Direct Register | Addressing, | Two Registers |

|---------------------------------------|-----------|-----------------|-------------|---------------|

| Rd and Rr                             |           |                 |             |               |

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

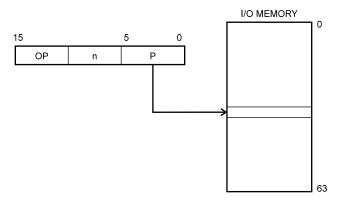

I/O Direct

Figure 9. I/O Direct Addressing

Operand address is contained in 6 bits of the instruction word. n is the destination or source register address.

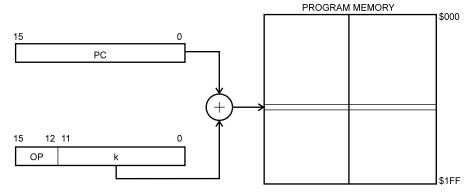

Relative Program Addressing, RJMP and RCALL Figure 10. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

**Subroutine and Interrupt Hardware Stack** The AT90S1200 uses a 3 level deep hardware stack for subroutines and interrupts. The hardware stack is 9 bits wide and stores the Program Counter (PC) return address while subroutines and interrupts are executed.

RCALL instructions and interrupts push the PC return address onto stack level 0, and the data in the other stack levels 1 - 2 are pushed one level deeper in the stack. When a RET or RETI instruction is executed the returning PC is fetched from stack level 0, and the data in the other stack levels 1 - 2 are popped one level in the stack.

If more than three subsequent subroutine calls or interrupts are executed, the first values written to the stack are overwritten.

8

# **EEPROM Data Memory** The AT90S1200 contains 64 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 100,000 write/erase cycles. The access between the EEPROM and the CPU is described on page 25 specifying the EEPROM address register, the EEPROM data register, and the EEPROM control register. For the SPI data download-ing, see page 44 for a detailed description.

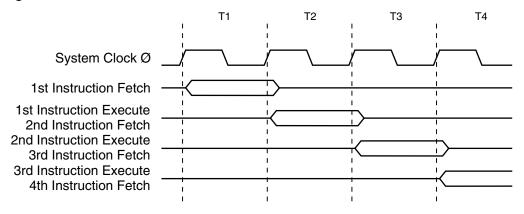

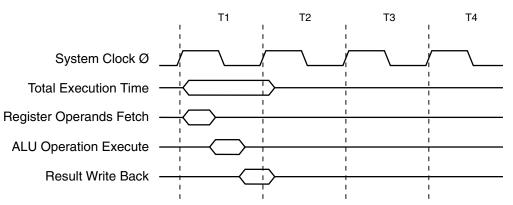

# Instruction ExecutionThis section describes the general access timing concepts for instruction execution and<br/>internal memory access.

The AVR CPU is driven by the System Clock  $\emptyset$ , directly generated from the external clock crystal for the chip. No internal clock division is used.

Figure 11 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture and the fast-access register file concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 11. The Parallel Instruction Fetches and Instruction Executions

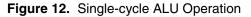

Figure 12 shows the internal timing concept for the register file. In a single clock cycle an ALU operation using two register operands is executed, and the result is stored back to the destination register.

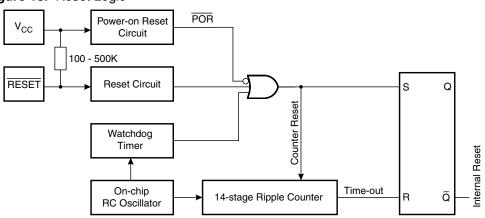

Figure 13. Reset Logic

**Table 3.** Reset Characteristics ( $V_{CC} = 5.0V$ )

| Symbol                          | Parameter                                                                                                                                                                    | Min  | Тур  | Max                  | Units |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------|-------|

| V (1)                           | Power-on Reset Threshold Voltage (rising)                                                                                                                                    | 0.8  | 1.2  | 1.6                  | V     |

| V <sub>POT</sub> <sup>(1)</sup> | Power-on Reset Threshold Voltage (falling)                                                                                                                                   | 0.2  | 0.4  | 0.6                  | V     |

| V <sub>RST</sub>                | Pin Threshold Voltage                                                                                                                                                        | _    | _    | 0.85 V <sub>CC</sub> | V     |

| t <sub>POR</sub>                | Power-on Reset Period                                                                                                                                                        | 2.0  | 3.0  | 4.0                  | ms    |

| t <sub>TOUT</sub>               | Reset Delay Time-out Period (The Time-out<br>period equals 16K WDT cycles. See "Typical<br>Characteristics" on page 51. for typical WDT<br>frequency at different voltages). | 11.0 | 16.0 | 21.0                 | ms    |

Note: 1. The Power-on Reset will not work unless the supply voltage has been below V<sub>POT</sub> (falling).

#### **Power-on Reset**

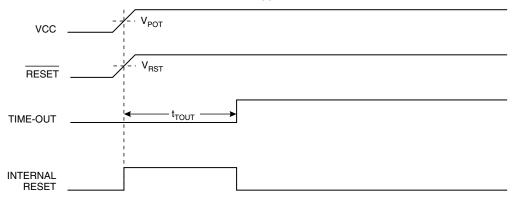

A Power-on Reset (POR) circuit ensures that the device is reset from power-on. As shown in Figure 13, an internal timer clocked from the Watchdog timer oscillator prevents the MCU from starting until after a certain period after  $V_{CC}$  has reached the Power-on Threshold voltage ( $V_{POT}$ ), regardless of the  $V_{CC}$  rise time (see Figure 14).

#### Figure 14. MCU Start-up, RESET Tied to V<sub>CC</sub>.

If the built-in start-up delay is sufficient,  $\overline{\text{RESET}}$  can be connected to  $V_{CC}$  directly or via an external pull-up resistor. By holding the  $\overline{\text{RESET}}$  pin low for a period after  $V_{CC}$  has

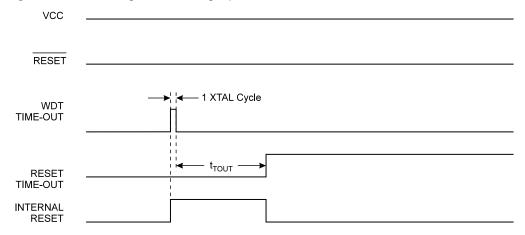

#### Figure 17. Watchdog Reset during Operation

#### Interrupt Handling

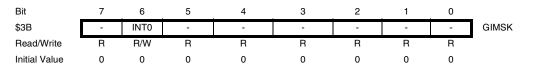

The AT90S1200 has two Interrupt Mask Control Registers: the GIMSK (General Interrupt Mask Register) at I/O space address \$3B and the TIMSK (Timer/Counter Interrupt Mask Register) at I/O address \$39.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software can set (one) the I-bit to enable interrupts. The I-bit is set (one) when a Return from Interrupt instruction (RETI) is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is active.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

#### General Interrupt Mask Register – GIMSK

#### Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S1200 and always reads as zero.

### **External Interrupts** The External Interrupt is triggered by the INT0 pin. The interrupt can trigger on rising edge, falling edge or low level. This is set up as described in the specification for the MCU Control Register (MCUCR). When INTO is level triggered, the interrupt is pending as long as INT0 is held low. The interrupt is triggered even if INT0 is configured as an output. This provides a way to generate a software interrupt. The interrupt flag can not be directly accessed by the user. If an external edge-triggered interrupt is suspected to be pending, the flag can be cleared as follows. 1. Disable the External Interrupt by clearing the INT0 flag in GIMSK. 2. Select level triggered interrupt. 3. Select desired interrupt edge. 4. Re-enable the external interrupt by setting INT0 in GIMSK. Interrupt Response Time The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. Four clock cycles after the interrupt flag has been set, the program vector address for the actual interrupt handling routine is executed. During this 4-clock-cycle period, the Program Counter (9 bits) is pushed onto the Stack. The vector is normally a relative jump to the interrupt routine, and this jump takes two clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (9 bits) is popped back from the Stack and the I-flag in SREG is set. When the AVR exits from an interrupt, it will always return to the main program and execute one more instruction before any pending interrupt is served.

Note that the Subroutine and Interrupt Stack is a 3-level true hardware stack, and if more than three nested subroutines and interrupts are executed, only the most recent three return addresses are stored.

# I/O Ports

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies for changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input).

Port B

Port B is an 8-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port B, one each for the Data Register – PORTB (\$18), Data Direction Register – DDRB (\$17), and the Port B Input Pins – PINB (\$16). The Port B Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

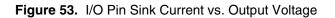

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in Table 8.

Table 8. Port B Pin Alternate Functions

| Port Pin | Alternate Functions                           |

|----------|-----------------------------------------------|

| PB0      | AIN0 (Analog Comparator positive input)       |

| PB1      | AIN1 (Analog Comparator negative input)       |

| PB5      | MOSI (Data Input line for memory downloading) |

| PB6      | MISO (Data Output line for memory uploading)  |

| PB7      | SCK (Serial Clock input)                      |

When the pins are used for the alternate function, the DDRB and PORTB register has to be set according to the alternate function description.

#### Port B Data Register – PORTB

|                                | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$18          | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Data Direction Register |               |        |        |        |        |        |        |        |        |       |

| – DDRB                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$17          | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | DDRB  |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Input Pin Address –     |               |        |        |        |        |        |        |        |        |       |

| PINB                           | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$16          | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

|                                | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      |       |

|                                | Initial Value | N/A    |       |

The Port B Input Pins address (PINB) is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read, and when reading PINB, the logical values present on the pins are read.

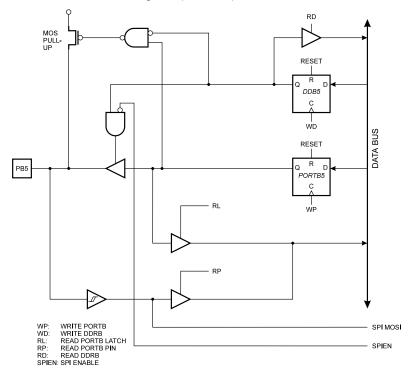

Figure 23. Port B Schematic Diagram (Pins PB2, PB3, and PB4)

Figure 24. Port B Schematic Diagram (Pin PB5)

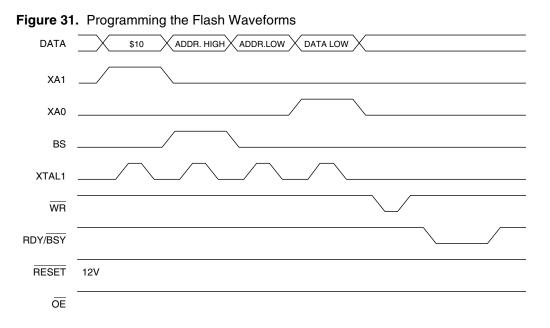

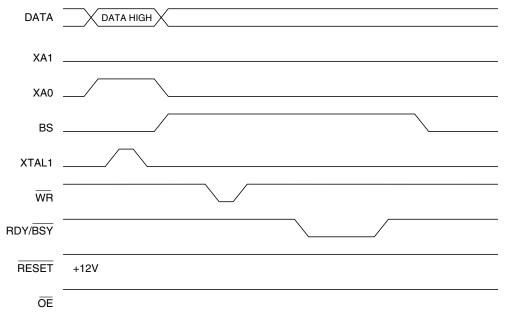

#### Figure 32. Programming the Flash Waveforms (Continued)

#### **Reading the Flash**

The algorithm for reading the Flash memory is as follows (refer to "Programming the Flash" for details on command and address loading):

- 1. A: Load Command "0000 0010".

- 2. B: Load Address High Byte (\$00 \$01).

- 3. C: Load Address Low Byte (\$00 \$FF).

- 4. Set  $\overline{OE}$  to "0", and BS to "0". The Flash word low byte can now be read at DATA.

- 5. Set BS to "1". The Flash word high byte can now be read from DATA.

- 6. Set OE to "1".

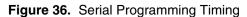

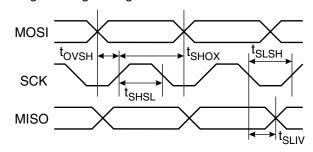

### Serial Programming Characteristics

| Symbol              | Parameter                                      | Min                    | Тур  | Max  | Units |

|---------------------|------------------------------------------------|------------------------|------|------|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 2.7 - 4.0V$ ) | 0                      |      | 4.0  | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period ( $V_{CC} = 2.7 - 4.0V$ )    | 250.0                  |      |      | ns    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 4.0 - 6.0V$ ) | 0                      |      | 12.0 | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period ( $V_{CC} = 4.0 - 6.0V$ )    | 83.3                   |      |      | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High                           | 4.0 t <sub>CLCL</sub>  |      |      | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low                            | t <sub>CLCL</sub>      |      |      | ns    |

| t <sub>OVSH</sub>   | MOSI Setup to SCK High                         | 1.25 t <sub>CLCL</sub> |      |      | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High                       | 2.5 t <sub>CLCL</sub>  |      |      | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid                          | 10.0                   | 16.0 | 32.0 | ns    |

Table 21. Minimum Wait Delay after the Chip Erase Instruction

| Symbol                | 3.2V  | 3.6V  | 4.0V  | 5.0V |

|-----------------------|-------|-------|-------|------|

| t <sub>WD_ERASE</sub> | 18 ms | 14 ms | 12 ms | 8 ms |

Table 22. Minimum Wait Delay after Writing a Flash or EEPROM Location

| Symbol               | 3.2V | 3.6V | 4.0V | 5.0V |

|----------------------|------|------|------|------|

| t <sub>WD_PROG</sub> | 9 ms | 7 ms | 6 ms | 4 ms |

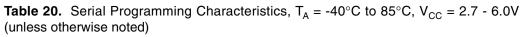

Figure 45. Power-down Supply Current vs.  $V_{\text{CC}},$  Watchdog Timer Enabled

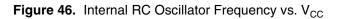

INTERNAL RC OSCILLATOR FREQUENCY vs.  $\rm V_{cc}$

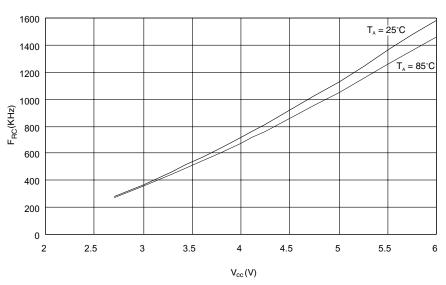

Figure 47. Analog Comparator Current vs. V<sub>CC</sub>

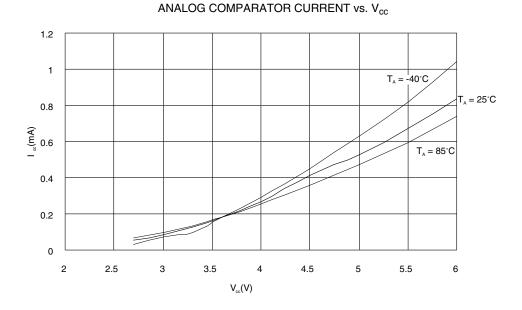

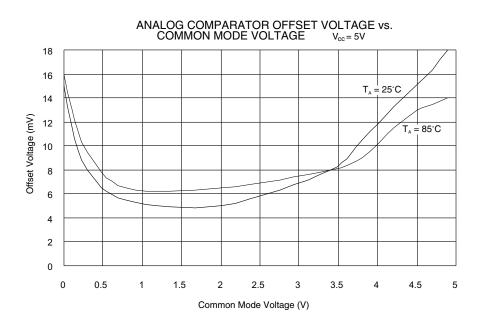

Note: Analog comparator offset voltage is measured as absolute offset.

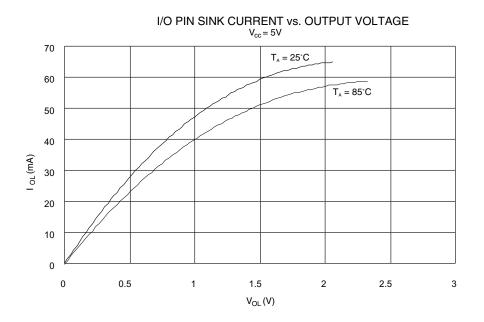

Figure 54. I/O Pin Source Current vs. Output Voltage

# AT90S1200 Register Summary

| Address                                                                          | Name                                                                                           | Bit 7                   | Bit 6                           | Bit 5                           | Bit 4                           | Bit 3                           | Bit 2                           | Bit 1                   | Bit 0                   | Page                                                |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|-------------------------|-------------------------|-----------------------------------------------------|

| \$3F                                                                             | SREG                                                                                           | 1                       | Т                               | Н                               | S                               | V                               | N                               | Z                       | С                       | page 1                                              |

| \$3E                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$3D                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$3C                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$3B                                                                             | GIMSK                                                                                          | -                       | INT0                            | -                               | -                               | -                               | -                               | -                       | -                       | page 1                                              |

| \$3A                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$39                                                                             | TIMSK                                                                                          | -                       | -                               | -                               | -                               | -                               | -                               | TOIE0                   | -                       | page 16                                             |

| \$38                                                                             | TIFR                                                                                           | -                       | -                               | -                               | -                               | -                               | -                               | TOV0                    | -                       | page 16                                             |

| \$37                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$36                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$35                                                                             | MCUCR                                                                                          | -                       | -                               | SE                              | SM                              | -                               | -                               | ISC01                   | ISC00                   | page 18                                             |

| \$34                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$33                                                                             | TCCR0                                                                                          | -                       | -                               | -                               | -                               | -                               | CS02                            | CS01                    | CS00                    | page 2                                              |

| \$32                                                                             | TCNT0                                                                                          |                         |                                 |                                 | Timer/Cou                       | nter0 (8 Bits)                  |                                 |                         |                         | page 22                                             |

| \$31                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$30                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2F                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2E                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2D                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2C                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2B                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$2A                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$29                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$28                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$27                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$26                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$25                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$24                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$23                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$22                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$21                                                                             | WDTCR                                                                                          | -                       | -                               | -                               | -                               | WDE                             | WDP2                            | WDP1                    | WDP0                    | page 23                                             |

| \$20                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$1F                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$1E                                                                             | EEAR                                                                                           | -                       |                                 |                                 | EEP                             | ROM Address R                   | egister                         |                         |                         | page 25                                             |

| \$1D                                                                             | EEDR                                                                                           |                         |                                 |                                 | EEPROM                          | Data Register                   |                                 |                         |                         | page 25                                             |

| \$1C                                                                             | EECR                                                                                           | -                       | -                               | -                               | -                               | -                               | -                               | EEWE                    | EERE                    | page 25                                             |

| \$1B                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$1A                                                                             | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

|                                                                                  | Reserved                                                                                       |                         |                                 |                                 |                                 |                                 |                                 |                         |                         |                                                     |

| \$19                                                                             |                                                                                                |                         |                                 | DODTDE                          | DODTD4                          | DODTDO                          | PORTB2                          | PORTB1                  | PORTB0                  | page 29                                             |

| \$19<br>\$18                                                                     | PORTB                                                                                          | PORTB7                  | PORTB6                          | PORTB5                          | PORTB4                          | PORTB3                          | TOTTEL                          |                         |                         | page 29                                             |

|                                                                                  |                                                                                                | PORTB7<br>DDB7          | PORTB6<br>DDB6                  | DDB5                            | DDB4                            | DDB3                            | DDB2                            | DDB1                    | DDB0                    |                                                     |

| \$18                                                                             | PORTB                                                                                          |                         |                                 |                                 |                                 |                                 |                                 | DDB1<br>PINB1           | DDB0<br>PINB0           |                                                     |

| \$18<br>\$17                                                                     | PORTB<br>DDRB                                                                                  | DDB7                    | DDB6                            | DDB5                            | DDB4                            | DDB3                            | DDB2                            |                         |                         |                                                     |

| \$18<br>\$17<br>\$16                                                             | PORTB<br>DDRB<br>PINB                                                                          | DDB7                    | DDB6                            | DDB5                            | DDB4                            | DDB3                            | DDB2                            |                         |                         |                                                     |

| \$18<br>\$17<br>\$16<br>\$15                                                     | PORTB<br>DDRB<br>PINB<br>Reserved                                                              | DDB7                    | DDB6                            | DDB5                            | DDB4                            | DDB3                            | DDB2                            |                         |                         |                                                     |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13                                     | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved                                                  | DDB7                    | DDB6                            | DDB5                            | DDB4                            | DDB3                            | DDB2                            |                         |                         | page 29                                             |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14                                             | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>Reserved                                      | DDB7<br>PINB7           | DDB6<br>PINB6                   | DDB5<br>PINB5                   | DDB4<br>PINB4                   | DDB3<br>PINB3                   | DDB2<br>PINB2                   | PINB1                   | PINBO                   | page 29<br>page 34                                  |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13<br>\$12                             | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>Reserved<br>PORTD                             | DDB7<br>PINB7           | DDB6<br>PINB6<br>PORTD6         | DDB5<br>PINB5<br>PORTD5         | DDB4<br>PINB4<br>PORTD4         | DDB3<br>PINB3<br>PORTD3         | DDB2<br>PINB2<br>PORTD2         | PINB1<br>PORTD1         | PINB0<br>PORTD0         | page 29<br>page 34<br>page 34                       |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13<br>\$12<br>\$11                     | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>Reserved<br>PORTD<br>DDRD                     | DDB7<br>PINB7<br>-<br>- | DDB6<br>PINB6<br>PORTD6<br>DDD6 | DDB5<br>PINB5<br>PORTD5<br>DDD5 | DDB4<br>PINB4<br>PORTD4<br>DDD4 | DDB3<br>PINB3<br>PORTD3<br>DDD3 | DDB2<br>PINB2<br>PORTD2<br>DDD2 | PINB1<br>PORTD1<br>DDD1 | PINB0<br>PORTD0<br>DDD0 | page 29<br>page 34<br>page 34                       |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10             | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND                         | DDB7<br>PINB7<br>-<br>- | DDB6<br>PINB6<br>PORTD6<br>DDD6 | DDB5<br>PINB5<br>PORTD5<br>DDD5 | DDB4<br>PINB4<br>PORTD4<br>DDD4 | DDB3<br>PINB3<br>PORTD3<br>DDD3 | DDB2<br>PINB2<br>PORTD2<br>DDD2 | PINB1<br>PORTD1<br>DDD1 | PINB0<br>PORTD0<br>DDD0 | page 29<br>page 34<br>page 34                       |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10<br>\$0F     | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND<br>Reserved<br>Reserved | DDB7<br>PINB7<br>-<br>- | DDB6<br>PINB6<br>PORTD6<br>DDD6 | DDB5<br>PINB5<br>PORTD5<br>DDD5 | DDB4<br>PINB4<br>PORTD4<br>DDD4 | DDB3<br>PINB3<br>PORTD3<br>DDD3 | DDB2<br>PINB2<br>PORTD2<br>DDD2 | PINB1<br>PORTD1<br>DDD1 | PINB0<br>PORTD0<br>DDD0 | page 29<br>page 34<br>page 34                       |

| \$18<br>\$17<br>\$16<br>\$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10<br>\$0F<br> | PORTB<br>DDRB<br>PINB<br>Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND<br>Reserved             | DDB7<br>PINB7<br>-<br>- | DDB6<br>PINB6<br>PORTD6<br>DDD6 | DDB5<br>PINB5<br>PORTD5<br>DDD5 | DDB4<br>PINB4<br>PORTD4<br>DDD4 | DDB3<br>PINB3<br>PORTD3<br>DDD3 | DDB2<br>PINB2<br>PORTD2<br>DDD2 | PINB1<br>PORTD1<br>DDD1 | PINB0<br>PORTD0<br>DDD0 | page 29<br>page 34<br>page 34<br>page 34<br>page 27 |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

# Instruction Set Summary

| Mnemonic         | Operands        | Description                            | Operation                                                                 | Flags        | # Clocks |

|------------------|-----------------|----------------------------------------|---------------------------------------------------------------------------|--------------|----------|

|                  | ND LOGIC INST   |                                        |                                                                           | · · · · ·    |          |

| ADD              | Rd, Rr          | Add Two Registers                      | Rd ← Rd + Rr                                                              | Z,C,N,V,H    | 1        |

| ADC              | Rd, Rr          | Add with Carry Two Registers           | $Rd \leftarrow Rd + Rr + C$                                               | Z,C,N,V,H    | 1        |

| SUB              | Rd, Rr          | Subtract Two Registers                 | Rd ← Rd - Rr                                                              | Z,C,N,V,H    | 1        |

| SUBI             | Rd, K           | Subtract Constant from Register        | Rd ← Rd - K                                                               | Z,C,N,V,H    | 1        |

| SBC              | Rd, Rr          | Subtract with Carry Two Registers      | $Rd \leftarrow Rd - Rr - C$                                               | Z,C,N,V,H    | 1        |

| SBCI             | Rd, K           | Subtract with Carry Constant from Reg. | $Rd \leftarrow Rd - K - C$                                                | Z,C,N,V,H    | 1        |

| AND              | Rd, Rr          | Logical AND Registers                  | Rd ← Rd • Rr                                                              | Z,N,V        | 1        |

| ANDI             | Rd, K           | Logical AND Register and Constant      | $Rd \leftarrow Rd \bullet K$                                              | Z,N,V        | 1        |

| OR               | Rd, Rr          | Logical OR Registers                   | Rd ← Rd v Rr                                                              | Z,N,V        | 1        |

| ORI              | Rd, K           | Logical OR Register and Constant       | $Rd \leftarrow Rd \lor K$                                                 | Z,N,V        | 1        |

| EOR              | Rd, Rr          | Exclusive OR Registers                 | $Rd \leftarrow Rd \oplus Rr$                                              | Z,N,V        | 1        |

| СОМ              | Rd              | One's Complement                       | Rd ← \$FF - Rd                                                            | Z,C,N,V      | 1        |

| NEG              | Rd              | Two's Complement                       | Rd ← \$00 - Rd                                                            | Z,C,N,V,H    | 1        |

| SBR              | Rd, K           | Set Bit(s) in Register                 | $Rd \leftarrow Rd \lor K$                                                 | Z,N,V        | 1        |

| CBR              | Rd, K           | Clear Bit(s) in Register               | $Rd \leftarrow Rd \bullet (FFh - K)$                                      | Z,N,V        | 1        |

| INC              | Rd              | Increment                              | $Rd \leftarrow Rd + 1$                                                    | Z,N,V        | 1        |

| DEC              | Rd              | Decrement                              | Rd ← Rd - 1                                                               | Z,N,V        | 1        |

| TST              | Rd              | Test for Zero or Minus                 | Rd ← Rd • Rd                                                              | Z,N,V        | 1        |

| CLR              | Rd              | Clear Register                         | $Rd \leftarrow Rd \oplus Rd$                                              | Z,N,V        | 1        |

| SER              | Rd              | Set Register                           | Rd ← \$FF                                                                 | None         | 1        |

| BRANCH INSTR     |                 | Cott togistor                          |                                                                           |              | •        |

| RJMP             | k               | Relative Jump                          | $PC \leftarrow PC + k + 1$                                                | None         | 2        |

| RCALL            | k               | Relative Subroutine Call               | $PC \leftarrow PC + k + 1$                                                | None         | 3        |

| RET              | ĸ               | Subroutine Return                      | $PC \leftarrow STACK$                                                     | None         | 4        |

| RETI             |                 | Interrupt Return                       | PC ← STACK                                                                | INOTICE      | 4        |

| CPSE             | Rd, Rr          | Compare, Skip if Equal                 | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3                                  | None         | 1/2      |

| CP3E             | Rd, Rr          | Compare                                | Rd - Rr                                                                   | Z,N,V,C,H    | 1/2      |

|                  | · ·             | •                                      | -                                                                         |              |          |

|                  | Rd, Rr          | Compare with Carry                     | Rd - Rr - C<br>Rd - K                                                     | Z,N,V,C,H    | 1        |

| CPI              | Rd, K           | Compare Register with Immediate        |                                                                           | Z,N,V,C,H    | 1        |

| SBRC             | Rr, b           | Skip if Bit in Register Cleared        | if $(\text{Rr}(b) = 0) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$ | None         | 1/2      |

| SBRS             | Rr, b           | Skip if Bit in Register is Set         | if $(\text{Rr}(b) = 1) \text{ PC} \leftarrow \text{PC} + 2 \text{ or } 3$ | None         | 1/2      |

| SBIC             | P, b            | Skip if Bit in I/O Register Cleared    | if $(P(b)=0) PC \leftarrow PC + 2 \text{ or } 3$                          | None         | 1/2      |

| SBIS             | P, b            | Skip if Bit in I/O Register is Set     | if (P(b) = 1) PC $\leftarrow$ PC + 2 or 3                                 | None         | 1/2      |

| BRBS             | s, k            | Branch if Status Flag Set              | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1                          | None         | 1/2      |

| BRBC             | s, k            | Branch if Status Flag Cleared          | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1                          | None         | 1/2      |

| BREQ             | k               | Branch if Equal                        | if (Z = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRNE             | k               | Branch if Not Equal                    | if (Z = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRCS             | k               | Branch if Carry Set                    | if (C = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRCC             | k               | Branch if Carry Cleared                | if (C = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRSH             | k               | Branch if Same or Higher               | if (C = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRLO             | k               | Branch if Lower                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRMI             | k               | Branch if Minus                        | if (N = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRPL             | k               | Branch if Plus                         | if (N = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRGE             | k               | Branch if Greater or Equal, Signed     | if (N $\oplus$ V = 0) then PC $\leftarrow$ PC + k + 1                     | None         | 1/2      |

| BRLT             | k               | Branch if Less than Zero, Signed       | if $(N \oplus V = 1)$ then PC $\leftarrow$ PC + k + 1                     | None         | 1/2      |

| BRHS             | k               | Branch if Half-carry Flag Set          | if (H = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRHC             | k               | Branch if Half-carry Flag Cleared      | if (H = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRTS             | k               | Branch if T-Flag Set                   | if $(T = 1)$ then PC $\leftarrow$ PC + k + 1                              | None         | 1/2      |

| BRTC             | k               | Branch if T-Flag Cleared               | if $(T = 0)$ then PC $\leftarrow$ PC + k + 1                              | None         | 1/2      |

| BRVS             | k               | Branch if Overflow Flag is Set         | if (V = 1) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRVC             | k               | Branch if Overflow Flag is Cleared     | if (V = 0) then PC $\leftarrow$ PC + k + 1                                | None         | 1/2      |

| BRIE             | k               | Branch if Interrupt Enabled            | if $(I = 1)$ then PC $\leftarrow$ PC + k + 1                              | None         | 1/2      |

| BRID             | k               | Branch if Interrupt Disabled           | if $(I = 0)$ then PC $\leftarrow$ PC + k + 1                              | None         | 1/2      |

|                  |                 | •                                      |                                                                           | 110110       | 1/6      |

| LD               | Rd, Z           | Load Register Indirect                 | Rd ← (Z)                                                                  | None         | 2        |

| ST               | Z, Rr           | Store Register Indirect                | $(Z) \leftarrow Rr$                                                       | None         | 2        |

|                  | Z, NI<br>Rd, Rr | Move between Registers                 | $(z) \leftarrow n$<br>Rd $\leftarrow$ Rr                                  | None         |          |

| MOV              |                 | INIOVE DELWEETT REGISTERS              | nu — ni                                                                   | NOTE         | 1        |

|                  |                 | Load Immodiate                         |                                                                           | None         | 4        |

| MOV<br>LDI<br>IN | Rd, K<br>Rd, P  | Load Immediate                         | Rd ← K<br>Rd ← P                                                          | None<br>None | 1        |

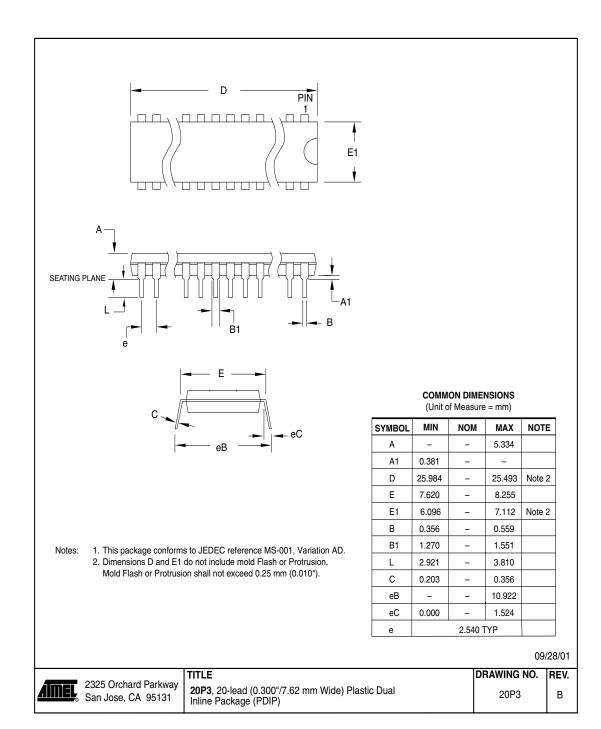

## **Packaging Information**

20P3

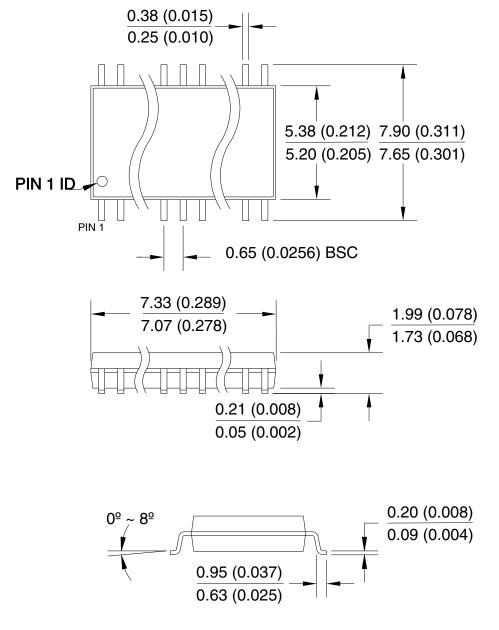

20Y, 20-lead Plastic Shrink Small Outline (SSOP), 5.3mm body Width. Dimensions in Millimeters and (inches)\*

\*Controlling dimension: millimeters

REV. A 04/11/2001

20Y

| Table of Contents | Features                                    | . 1 |

|-------------------|---------------------------------------------|-----|

|                   | Pin Configuration                           | . 1 |

|                   | Description                                 | . 2 |

|                   | Block Diagram                               | 2   |

|                   | Pin Descriptions                            | 3   |

|                   | Crystal Oscillator                          | 3   |

|                   | On-chip RC Oscillator                       | 4   |

|                   | Architectural Overview                      | . 5 |

|                   | General Purpose Register File               | 6   |

|                   | ALU – Arithmetic Logic Unit                 | 6   |

|                   | In-System Programmable Flash Program Memory | 6   |

|                   | Program and Data Addressing Modes           | 7   |

|                   | Subroutine and Interrupt Hardware Stack     | 8   |

|                   | EEPROM Data Memory                          | 9   |

|                   | Instruction Execution Timing                | 9   |

|                   | I/O Memory                                  | 10  |

|                   | Reset and Interrupt Handling                | 12  |

|                   | Sleep Modes                                 | 19  |

|                   | Timer/Counter0                              | 20  |

|                   | Timer/Counter0 Prescaler                    | 20  |

|                   | Watchdog Timer                              | 23  |

|                   | EEPROM Read/Write Access                    | 25  |

|                   | Prevent EEPROM Corruption                   | 26  |

|                   | Analog Comparator                           | 27  |

|                   | I/O Ports                                   | 29  |

|                   | Port B                                      | 29  |

|                   | Port D                                      | 34  |

|                   | Memory Programming                          | 37  |

|                   | Program and Data Memory Lock Bits           | 37  |

|                   | Fuse Bits                                   |     |

|                   | Signature Bytes                             |     |

|                   | Programming the Flash and EEPROM            |     |

|                   | Parallel Programming                        |     |

|                   | Parallel Programming Characteristics        |     |

|                   | Serial Downloading                          |     |

|                   | Serial Programming Characteristics          |     |