#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 12MHz                                                                     |

| Connectivity               | SPI                                                                       |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 15                                                                        |

| Program Memory Size        | 1KB (512 x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 64 x 8                                                                    |

| RAM Size                   | -                                                                         |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 6V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C                                                              |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90s1200a-12yi |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Operands are contained in register r (Rr) and d (Rd). The result is stored in register d (Rd).

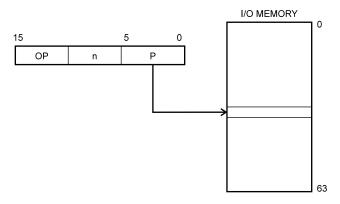

I/O Direct

Figure 9. I/O Direct Addressing

Operand address is contained in 6 bits of the instruction word. n is the destination or source register address.

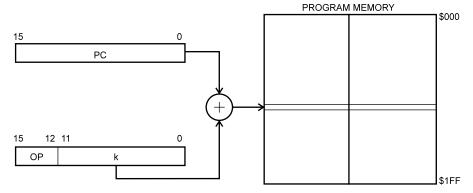

Relative Program Addressing, RJMP and RCALL Figure 10. Relative Program Memory Addressing

Program execution continues at address PC + k + 1. The relative address k is -2048 to 2047.

**Subroutine and Interrupt Hardware Stack** The AT90S1200 uses a 3 level deep hardware stack for subroutines and interrupts. The hardware stack is 9 bits wide and stores the Program Counter (PC) return address while subroutines and interrupts are executed.

RCALL instructions and interrupts push the PC return address onto stack level 0, and the data in the other stack levels 1 - 2 are pushed one level deeper in the stack. When a RET or RETI instruction is executed the returning PC is fetched from stack level 0, and the data in the other stack levels 1 - 2 are popped one level in the stack.

If more than three subsequent subroutine calls or interrupts are executed, the first values written to the stack are overwritten.

8

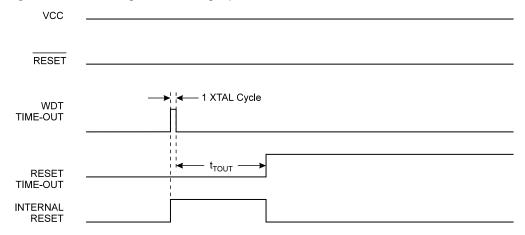

#### Figure 17. Watchdog Reset during Operation

#### Interrupt Handling

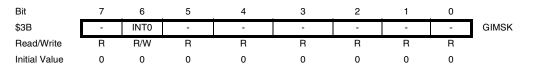

The AT90S1200 has two Interrupt Mask Control Registers: the GIMSK (General Interrupt Mask Register) at I/O space address \$3B and the TIMSK (Timer/Counter Interrupt Mask Register) at I/O address \$39.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared (zero) and all interrupts are disabled. The user software can set (one) the I-bit to enable interrupts. The I-bit is set (one) when a Return from Interrupt instruction (RETI) is executed.

When the Program Counter is vectored to the actual interrupt vector in order to execute the interrupt handling routine, hardware clears the corresponding flag that generated the interrupt. Some of the interrupt flags can also be cleared by writing a logic one to the flag bit position(s) to be cleared.

If an interrupt condition occurs when the corresponding interrupt enable bit is cleared (zero), the interrupt flag will be set and remembered until the interrupt is enabled, or the flag is cleared by software.

If one or more interrupt conditions occur when the global interrupt enable bit is cleared (zero), the corresponding interrupt flag(s) will be set and remembered until the global interrupt enable bit is set (one), and will be executed by order of priority.

Note that external level interrupt does not have a flag, and will only be remembered for as long as the interrupt condition is active.

Note that the Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt routine. This must be handled by software.

#### General Interrupt Mask Register – GIMSK

#### Bit 7 – Res: Reserved Bit

This bit is a reserved bit in the AT90S1200 and always reads as zero.

| Sleep Modes     | To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruc-<br>tion must be executed. If an enabled interrupt occurs while the MCU is in a sleep mode,<br>the MCU awakes, executes the interrupt routine, and resumes execution from the<br>instruction following SLEEP. The contents of the register file and the I/O memory are<br>unaltered. If a Reset occurs during sleep mode, the MCU wakes up and executes from<br>the Reset Vector.                                                                                                                                                                                                               |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ldle Mode       | When the SM bit is cleared (zero), the SLEEP instruction makes the MCU enter the Idle mode, stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog Reset. If wakeup from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status Register (ACSR). This will reduce power consumption in Idle mode. When the MCU wakes up from Idle mode, the CPU starts program execution immediately. |

| Power-down Mode | When the SM bit is set (one), the SLEEP instruction makes the MCU enter Power-down mode. In this mode, the External Oscillator is stopped while the External Interrupts and the Watchdog (if enabled) continue operating. Only an External Reset, a Watchdog Reset (if enabled), an external level interrupt on INT0 can wake up the MCU.                                                                                                                                                                                                                                                                                                                                           |

|                 | Note that when a level triggered interrupt is used for wake-up from Power-down, the low level must be held for a time longer than the reset delay time-out period t <sub>TOUT</sub> . Otherwise, the device will not wake up.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

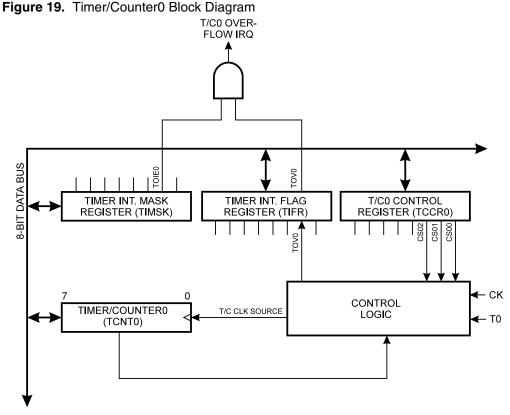

The 8-bit Timer/Counter0 can select clock source from CK, prescaled CK or an external pin. In addition it can be stopped as described in the specification for the Timer/Counter0 Control Register (TCCR0). The overflow status flag is found in the Timer/Counter Interrupt Flag Register (TIFR). Control signals are found in the Timer/Counter0 Control Register (TCCR0). The interrupt enable/disable settings for Timer/Counter0 are found in the Timer/Counter Interrupt Mask Register (TIMSK).

When Timer/Counter0 is externally clocked, the external signal is synchronized with the oscillator frequency of the CPU. To assure proper sampling of the external clock, the minimum time between two external clock transitions must be at least one internal CPU clock period. The external clock signal is sampled on the rising edge of the internal CPU clock.

The 8-bit Timer/Counter0 features both a high-resolution and a high-accuracy usage with the lower prescaling opportunities. Similarly, the high prescaling opportunities make the Timer/Counter0 useful for lower speed functions or exact timing functions with infrequent actions.

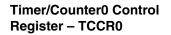

#### Bits 7..3 – Res: Reserved Bits

These bits are reserved bits in the AT90S1200 and always read as zero.

### • Bits 2, 1, 0 – CS02, CS01, CS00: Clock Select0, Bits 2, 1 and 0

The Clock Select0 bits 2, 1 and 0 define the prescaling source of Timer/Counter0.

| CS02 | CS01 | CS00 | Description                          |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | Stop, the Timer/Counter0 is stopped. |

| 0    | 0    | 1    | СК                                   |

| 0    | 1    | 0    | CK/8                                 |

| 0    | 1    | 1    | СК/64                                |

| 1    | 0    | 0    | CK/256                               |

| 1    | 0    | 1    | CK/1024                              |

| 1    | 1    | 0    | External Pin T0, falling edge        |

| 1    | 1    | 1    | External Pin T0, rising edge         |

Table 5. Clock 0 Prescale Select

The Stop condition provides a Timer Enable/Disable function. The CK down divided modes are scaled directly from the CK Oscillator clock. If the external pin modes are used for Timer/Counter0, transitions on PD4/(T0) will clock the counter even if the pin is configured as an output. This feature can give the user SW control of the counting.

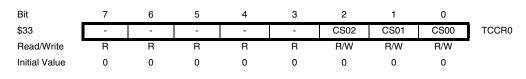

### Timer/Counter0 – TCNT0

The Timer/Counter0 is realized as an up-counter with read and write access. If the Timer/Counter0 is written and a clock source is present, the Timer/Counter0 continues counting in the timer clock cycle following the write operation.

| WDP2 | WDP1 | WDP0 | Number of WDT<br>Oscillator Cycles | Typical Time-out<br>at V <sub>CC</sub> = 3.0V | Typical Time-out<br>at V <sub>CC</sub> = 5.0V |

|------|------|------|------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 0    | 0    | 0    | 16K cycles                         | 47 ms                                         | 15 ms                                         |

| 0    | 0    | 1    | 32K cycles                         | 94 ms                                         | 30 ms                                         |

| 0    | 1    | 0    | 64K cycles                         | 0.19 s                                        | 60 ms                                         |

| 0    | 1    | 1    | 128K cycles                        | 0.38 s                                        | 0.12 s                                        |

| 1    | 0    | 0    | 256K cycles                        | 0.75 s                                        | 0,24 s                                        |

| 1    | 0    | 1    | 512K cycles                        | 1.5 s                                         | 0.49 s                                        |

| 1    | 1    | 0    | 1,024K cycles                      | 3.0 s                                         | 0.97 s                                        |

| 1    | 1    | 1    | 2,048K cycles                      | 6.0 s                                         | 1.9 s                                         |

Table 6. Watchdog Timer Prescale Select

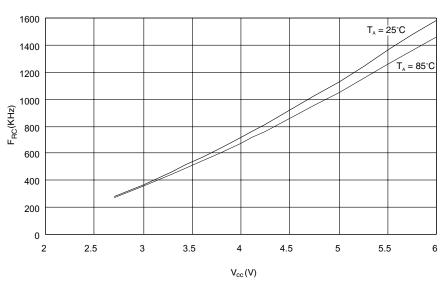

Note: The frequency of the Watchdog Oscillator is voltage dependent as shown in "Typical Characteristics" on page 51.

The WDR (Watchdog Reset) instruction should always be executed before the Watchdog Timer is enabled. This ensures that the reset period will be in accordance with the Watchdog Timer prescale settings. If the Watchdog Timer is enabled without Reset, the Watchdog Timer may not start to count from zero.

To avoid unintentional MCU resets, the Watchdog Timer should be disabled or reset before changing the Watchdog Timer Prescale Select.

## I/O Ports

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies for changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input).

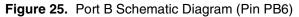

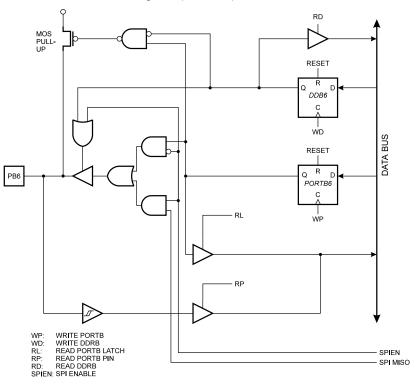

Port B

Port B is an 8-bit bi-directional I/O port.

Three I/O memory address locations are allocated for the Port B, one each for the Data Register – PORTB (\$18), Data Direction Register – DDRB (\$17), and the Port B Input Pins – PINB (\$16). The Port B Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

All port pins have individually selectable pull-up resistors. The Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated.

The Port B pins with alternate functions are shown in Table 8.

Table 8. Port B Pin Alternate Functions

| Port Pin | Alternate Functions                           |  |  |  |

|----------|-----------------------------------------------|--|--|--|

| PB0      | AIN0 (Analog Comparator positive input)       |  |  |  |

| PB1      | AIN1 (Analog Comparator negative input)       |  |  |  |

| PB5      | MOSI (Data Input line for memory downloading) |  |  |  |

| PB6      | MISO (Data Output line for memory uploading)  |  |  |  |

| PB7      | SCK (Serial Clock input)                      |  |  |  |

When the pins are used for the alternate function, the DDRB and PORTB register has to be set according to the alternate function description.

## Port B Data Register – PORTB

|                                | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|--------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|                                | \$18          | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Data Direction Register |               |        |        |        |        |        |        |        |        |       |

| – DDRB                         | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$17          | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | DDRB  |

|                                | Read/Write    | R/W    |       |

|                                | Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

| Port B Input Pin Address –     |               |        |        |        |        |        |        |        |        |       |

| PINB                           | Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|                                | \$16          | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | PINB  |

|                                | Read/Write    | R      | R      | R      | R      | R      | R      | R      | R      |       |

|                                | Initial Value | N/A    |       |

The Port B Input Pins address (PINB) is not a register, and this address enables access to the physical value on each Port B pin. When reading PORTB, the Port B Data Latch is read, and when reading PINB, the logical values present on the pins are read.

Figure 26. Port B Schematic Diagram (Pin PB7)

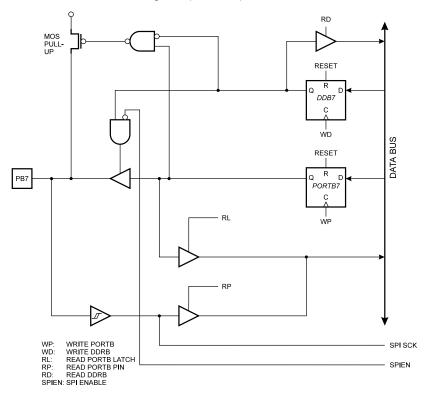

Port D

Three I/O memory address locations are allocated for Port D, one each for the Data Register – PORTD (\$12), Data Direction Register – DDRD (\$11), and the Port D Input Pins – PIND (\$10). The Port D Input Pins address is read-only, while the Data Register and the Data Direction Register are read/write.

Port D has seven bi-directional I/O pins with internal pull-up resistors, PD6..PD0. The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated.

Some Port D pins have alternate functions as shown in Table 10.

| Table 10 | Port D Pin | Alternate | Functions  |

|----------|------------|-----------|------------|

|          |            | Allemale  | i unctions |

| Port Pin | Alternate Function                  |  |  |  |

|----------|-------------------------------------|--|--|--|

| PD2      | INT0 (External Interrupt 0 input)   |  |  |  |

| PD4      | T0 (Timer/Counter 0 external input) |  |  |  |

#### Port D Data Register - PORTD

| •                              |                                                                                                                                                                                 |           |           |          |         |           |         |          |          |          |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|----------|---------|-----------|---------|----------|----------|----------|

|                                | Bit                                                                                                                                                                             | 7         | 6         | 5        | 4       | 3         | 2       | 1        | 0        |          |

|                                | \$12                                                                                                                                                                            | -         | PORTD6    | PORTD5   | PORTD4  | PORTD3    | PORTD2  | PORTD1   | PORTD0   | PORTD    |

|                                | Read/Write                                                                                                                                                                      | R         | R/W       | R/W      | R/W     | R/W       | R/W     | R/W      | R/W      |          |

|                                | Initial Value                                                                                                                                                                   | 0         | 0         | 0        | 0       | 0         | 0       | 0        | 0        |          |

| Port D Data Direction Register |                                                                                                                                                                                 |           |           |          |         |           |         |          |          |          |

| – DDRD                         | Bit                                                                                                                                                                             | 7         | 6         | 5        | 4       | 3         | 2       | 1        | 0        |          |

|                                | \$11                                                                                                                                                                            | -         | DDD6      | DDD5     | DDD4    | DDD3      | DDD2    | DDD1     | DDD0     | DDRD     |

|                                | Read/Write                                                                                                                                                                      | R         | R/W       | R/W      | R/W     | R/W       | R/W     | R/W      | R/W      |          |

|                                | Initial Value                                                                                                                                                                   | 0         | 0         | 0        | 0       | 0         | 0       | 0        | 0        |          |

| Port D Input Pins Address –    |                                                                                                                                                                                 |           |           |          |         |           |         |          |          |          |

| PIND                           | Bit                                                                                                                                                                             | 7         | 6         | 5        | 4       | 3         | 2       | 1        | 0        |          |

|                                | \$10                                                                                                                                                                            | -         | PIND6     | PIND5    | PIND4   | PIND3     | PIND2   | PIND1    | PIND0    | PIND     |

|                                | Read/Write                                                                                                                                                                      | R         | R         | R        | R       | R         | R       | R        | R        |          |

|                                | Initial Value                                                                                                                                                                   | 0         | N/A       | N/A      | N/A     | N/A       | N/A     | N/A      | N/A      |          |

|                                | The Port D<br>to the physi<br>is read; and                                                                                                                                      | ical valu | ie on eac | h Port D | pin. Wh | en readii | ng PORT | D, the F | ort D Da | ta Latch |

| Port D as General Digital I/O  | PDn, general I/O pin: The DDDn bit in the DDRD Register selects the direction of this pin. If DDDn is set (one), PDn is configured as an output pin. If DDDn is cleared (zero), |           |           |          |         |           |         |          |          |          |

PDn, general I/O pin: The DDDn bit in the DDRD Register selects the direction of this pin. If DDDn is set (one), PDn is configured as an output pin. If DDDn is cleared (zero), PDn is configured as an input pin. If PORTDn is set (one) when DDDn is configured as an input pin, the MOS pull-up resistor is activated. To switch the pull-up resistor off, the PORTDn bit has to be cleared (zero) or the pin has to be configured as an output pin. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not active.

| DDDn | PORTDn | I/O    | Pull-up | Comment                                     |

|------|--------|--------|---------|---------------------------------------------|

| 0    | 0      | Input  | No      | Tri-state (High-Z)                          |

| 0    | 1      | Input  | Yes     | PDn will source current if ext. pulled low. |

| 1    | 0      | Output | No      | Push-pull Zero Output                       |

| 1    | 1      | Output | No      | Push-pull One Output                        |

Table 11. DDDn Bits' Effect on Port D Pins

Note: n: 6...0, pin number.

Alternate Functions for Port D The alternate functions of Port D are:

## • T0 – Port D, Bit 4

T0, Timer/Counter0 clock source. See the timer description for further details.

### • INT0 - Port D, Bit 2

INTO, External Interrupt source 0. See the interrupt description for further details.

**Port D Schematics** Note that all port pins are synchronized. The synchronization latches are, however, not shown in the figures.

## Figure 27. Port D Schematic Diagram (Pins PD0, PD1, PD3, PD5, and PD6)

Table 15. XA1 and XA0 Coding

| XA1 | XA0 | Action when XTAL1 is Pulsed                                                         |

|-----|-----|-------------------------------------------------------------------------------------|

| 0   | 0   | Load Flash or EEPROM Address (High or low address byte for Flash determined by BS). |

| 0   | 1   | Load Data (High or low data byte for Flash determined by BS).                       |

| 1   | 0   | Load Command                                                                        |

| 1   | 1   | No Action, Idle                                                                     |

Table 16. Command Byte Coding

| Command Byte | Command Executed        |

|--------------|-------------------------|

| 1000 0000    | Chip Erase              |

| 0100 0000    | Write Fuse Bits         |

| 0010 0000    | Write Lock Bits         |

| 0001 0000    | Write Flash             |

| 0001 0001    | Write EEPROM            |

| 0000 1000    | Read Signature Bytes    |

| 0000 0100    | Read Fuse and Lock Bits |

| 0000 0010    | Read Flash              |

| 0000 0011    | Read EEPROM             |

The following algorithm puts the device in Parallel Programming mode:

- 1. Apply supply voltage according to Table 13, between V<sub>CC</sub> and GND.

- 2. Set the RESET and BS pin to "0" and wait at least 100 ns.

- Apply 11.5 12.5V to RESET. Any activity on BS within 100 ns after +12V has been applied to RESET, will cause the device to fail entering Programming mode.

The Chip Erase command will erase the Flash and EEPROM memories, and the Lock bits. The Lock bits are not Reset until the Flash and EEPROM have been completely erased. The Fuse bits are not changed. Chip Erase must be performed before the Flash or EEPROM is reprogrammed.

Load Command "Chip Erase"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS to "0".

- 3. Set DATA to "1000 0000". This is the command for Chip Erase.

- 4. Give XTAL1 a positive pulse. This loads the command.

- Give WR a t<sub>WLWH\_CE</sub> wide negative pulse to execute Chip Erase, t<sub>WLWH\_CE</sub> is found in Table 17. Chip Erase does not generate any activity on the RDY/BSY pin.

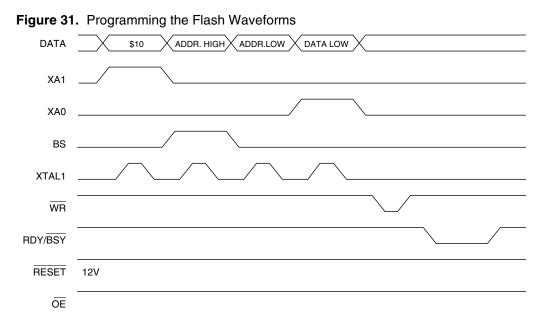

Programming the Flash

**Enter Programming Mode**

**Chip Erase**

- A: Load Command "Write Flash"

- 1. Set XA1, XA0 to "10". This enables command loading.

- 2. Set BS to "0".

- 3. Set DATA to "0001 0000". This is the command for Write Flash.

# AT90S1200

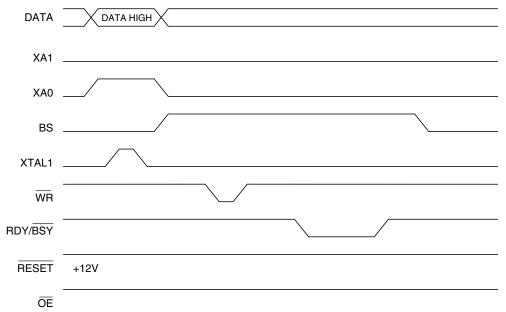

#### Figure 32. Programming the Flash Waveforms (Continued)

## **Reading the Flash**

The algorithm for reading the Flash memory is as follows (refer to "Programming the Flash" for details on command and address loading):

- 1. A: Load Command "0000 0010".

- 2. B: Load Address High Byte (\$00 \$01).

- 3. C: Load Address Low Byte (\$00 \$FF).

- 4. Set  $\overline{OE}$  to "0", and BS to "0". The Flash word low byte can now be read at DATA.

- 5. Set BS to "1". The Flash word high byte can now be read from DATA.

- 6. Set OE to "1".

## **Reading the Signature Bytes**

**Parallel Programming**

**Characteristics**

The algorithm for reading the signature bytes is as follows (refer to "Programming the Flash" on page 39 for details on command and address loading):

- 1. A: Load Command "0000 1000".

- 2. C: Load Address Low Byte (\$00 \$02).

Set  $\overline{OE}$  to "0", and BS to "0". The selected signature byte can now be read at DATA. Set OE to "1".

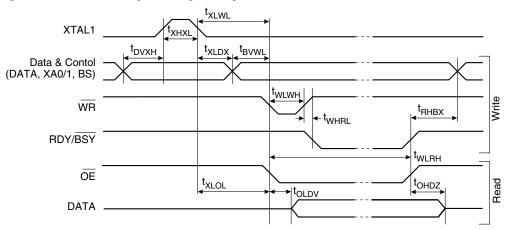

Figure 33. Parallel Programming Timing

| Symbol                | Parameter                                        | Min  | Тур  | Max   | Units |

|-----------------------|--------------------------------------------------|------|------|-------|-------|

| V <sub>PP</sub>       | Programming Enable Voltage                       | 11.5 |      | 12.5  | V     |

| I <sub>PP</sub>       | Programming Enable Current                       |      |      | 250.0 | μA    |

| t <sub>DVXH</sub>     | Data and Control Setup before XTAL1 High         | 67.0 |      |       | ns    |

| t <sub>XHXL</sub>     | XTAL1 Pulse Width High                           | 67.0 |      |       | ns    |

| t <sub>XLDX</sub>     | Data and Control Hold after XTAL1 Low            | 67.0 |      |       | ns    |

| t <sub>XLWL</sub>     | XTAL1 Low to WR Low                              | 67.0 |      |       | ns    |

| t <sub>BVWL</sub>     | BS Valid to WR Low                               | 67.0 |      |       | ns    |

| t <sub>RHBX</sub>     | BS Hold after RDY/BSY High                       |      |      |       | ns    |

| t <sub>wLWH</sub>     | WR Pulse Width Low <sup>(1)</sup>                | 67.0 |      |       | ns    |

| t <sub>WHRL</sub>     | WR High to RDY/BSY Low <sup>(2)</sup>            |      | 20.0 |       | ns    |

| t <sub>WLRH</sub>     | WR Low to RDY/BSY High <sup>(2)</sup>            | 0.5  | 0.7  | 0.9   | ms    |

| t <sub>xLOL</sub>     | XTAL1 Low to OE Low                              | 67.0 |      |       | ns    |

| t <sub>OLDV</sub>     | OE Low to DATA Valid                             |      | 20.0 |       | ns    |

| t <sub>OHDZ</sub>     | OE High to DATA Tri-stated                       |      |      | 20.0  | ns    |

| t <sub>WLWH_CE</sub>  | WR Pulse Width Low for Chip Erase                | 5.0  | 10.0 | 15.0  | ms    |

| t <sub>wLWH_PFB</sub> | WR Pulse Width Low for Programming the Fuse Bits | 1.0  | 1.5  | 1.8   | ms    |

Notes:

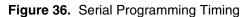

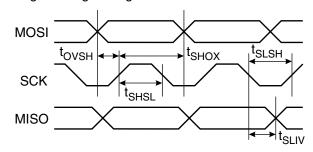

## Serial Programming Characteristics

| Symbol              | Parameter                                      | Min                    | Тур  | Max  | Units |

|---------------------|------------------------------------------------|------------------------|------|------|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 2.7 - 4.0V$ ) | 0                      |      | 4.0  | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period ( $V_{CC} = 2.7 - 4.0V$ )    | 250.0                  |      |      | ns    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 4.0 - 6.0V$ ) | 0                      |      | 12.0 | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period ( $V_{CC} = 4.0 - 6.0V$ )    | 83.3                   |      |      | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High                           | 4.0 t <sub>CLCL</sub>  |      |      | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low                            | t <sub>CLCL</sub>      |      |      | ns    |

| t <sub>OVSH</sub>   | MOSI Setup to SCK High                         | 1.25 t <sub>CLCL</sub> |      |      | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High                       | 2.5 t <sub>CLCL</sub>  |      |      | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid                          | 10.0                   | 16.0 | 32.0 | ns    |

Table 21. Minimum Wait Delay after the Chip Erase Instruction

| Symbol                | 3.2V  | 3.6V  | 4.0V  | 5.0V |

|-----------------------|-------|-------|-------|------|

| t <sub>WD_ERASE</sub> | 18 ms | 14 ms | 12 ms | 8 ms |

Table 22. Minimum Wait Delay after Writing a Flash or EEPROM Location

| Symbol               | 3.2V | 3.6V | 4.0V | 5.0V |

|----------------------|------|------|------|------|

| t <sub>WD_PROG</sub> | 9 ms | 7 ms | 6 ms | 4 ms |

## **DC Characteristics**

| Symbol            | Parameter                                  | Condition                            | Min   | Тур            | Max  | Units |

|-------------------|--------------------------------------------|--------------------------------------|-------|----------------|------|-------|

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$ |       |                | 40.0 | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$<br>$V_{in} = V_{CC}/2$ | -50.0 |                | 50.0 | nA    |

| t <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$      |       | 750.0<br>500.0 |      | ns    |

$T_A = -40 \times C$  to  $85 \times C$ ,  $V_{CC} = 2.7V$  to 6.0V (unless otherwise noted) (Continued)

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low.

2. "Min" means the lowest value where the pin is guaranteed to be read as high.

Although each I/O port can sink more than the test conditions (20 mA at V<sub>CC</sub> = 5V, 10 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all  $I_{OL}$ , for all ports, should not exceed 200 mA.

2] The sum of all  $I_{OL}$ , for port D0 - D5 and XTAL2, should not exceed 100 mA.

3] The sum of all  $I_{OL}$ , for ports B0 - B7 and D6, should not exceed 100 mA.

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

Although each I/O port can source more than the test conditions (3 mA at V<sub>CC</sub> = 5V, 1.5 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all  $\rm I_{OH},$  for all ports, should not exceed 200 mA.

2] The sum of all  $I_{OH}$ , for port D0 - D5 and XTAL2, should not exceed 100 mA.

3] The sum of all  $I_{OH}$ , for ports B0 - B7 and D6, should not exceed 100 mA.

If  $I_{OH}$  exceeds the test condition,  $V_{OH}$  may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for power-down is 2V.

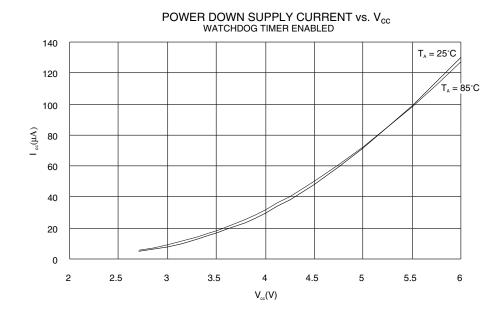

Figure 45. Power-down Supply Current vs.  $V_{\text{CC}},$  Watchdog Timer Enabled

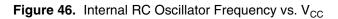

INTERNAL RC OSCILLATOR FREQUENCY vs.  $\rm V_{cc}$

## AT90S1200 Register Summary

| Address                                                  | Name                                                                  | Bit 7  | Bit 6          | Bit 5          | Bit 4          | Bit 3          | Bit 2          | Bit 1          | Bit 0          | Page                                     |

|----------------------------------------------------------|-----------------------------------------------------------------------|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------------------------------------|

| \$3F                                                     | SREG                                                                  | I      | Т              | Н              | S              | V              | N              | Z              | С              | page 1                                   |

| \$3E                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$3D                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$3C                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$3B                                                     | GIMSK                                                                 | -      | INT0           | -              | -              | -              | -              | -              | -              | page 1                                   |

| \$3A                                                     | Reserved                                                              |        |                |                |                |                |                |                | -              |                                          |

| \$39                                                     | TIMSK                                                                 | -      | -              | -              | -              | -              | -              | TOIE0          | -              | page 16                                  |

| \$38                                                     | TIFR                                                                  | -      | -              | -              | -              | -              | -              | TOV0           | -              | page 16                                  |

| \$37                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$36                                                     | Reserved                                                              |        |                |                |                |                |                |                | -              |                                          |

| \$35                                                     | MCUCR                                                                 | -      | -              | SE             | SM             | -              | -              | ISC01          | ISC00          | page 18                                  |

| \$34                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$33                                                     | TCCR0                                                                 | -      | -              | -              | -              | -              | CS02           | CS01           | CS00           | page 2                                   |

| \$32                                                     | TCNT0                                                                 |        |                |                | Timer/Cou      | nter0 (8 Bits) |                |                |                | page 22                                  |

| \$31                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$30                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2F                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2E                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2D                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2C                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2B                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$2A                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$29                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$28                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$27                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$26                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$25                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$24                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$23                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$22                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$21                                                     | WDTCR                                                                 | -      | -              | -              | -              | WDE            | WDP2           | WDP1           | WDP0           | page 23                                  |

| \$20                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$1F                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$1E                                                     | EEAR                                                                  | -      |                |                | EEP            | ROM Address R  | egister        |                |                | page 25                                  |

| \$1D                                                     | EEDR                                                                  |        |                |                | EEPROM         | Data Register  |                |                |                | page 25                                  |

| \$1C                                                     | EECR                                                                  | -      | -              | -              | -              | -              | -              | EEWE           | EERE           | page 25                                  |

| \$1B                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$1A                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$19                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$18                                                     | PORTB                                                                 | PORTB7 | PORTB6         | PORTB5         | PORTB4         | PORTB3         | PORTB2         | PORTB1         | PORTB0         | page 29                                  |

| \$17                                                     | DDRB                                                                  | DDB7   | DDB6           | DDB5           | DDB4           | DDB3           | DDB2           | DDB1           | DDB0           | page 29                                  |

|                                                          | PINB                                                                  | PINB7  | PINB6          | PINB5          | PINB4          | PINB3          | PINB2          | PINB1          | PINB0          | page 29                                  |

| \$16                                                     |                                                                       |        |                |                |                |                |                |                |                | -                                        |

| \$16<br>\$15                                             | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

|                                                          | Reserved<br>Reserved                                                  |        |                |                |                |                |                |                |                |                                          |

| \$15                                                     | Reserved                                                              |        |                |                |                |                |                |                |                |                                          |

| \$15<br>\$14<br>\$13                                     | Reserved<br>Reserved                                                  |        | PORTD6         | PORTD5         | PORTD4         | PORTD3         | PORTD2         | PORTD1         | PORTD0         | page 34                                  |

| \$15<br>\$14<br>\$13<br>\$12                             | Reserved                                                              | -<br>- | PORTD6<br>DDD6 | PORTD5<br>DDD5 | PORTD4<br>DDD4 | PORTD3<br>DDD3 | PORTD2<br>DDD2 | PORTD1<br>DDD1 | PORTD0<br>DDD0 |                                          |

| \$15<br>\$14<br>\$13<br>\$12<br>\$11                     | Reserved<br>Reserved<br>PORTD<br>DDRD                                 |        | DDD6           | DDD5           | DDD4           | DDD3           | DDD2           | DDD1           | DDD0           | page 34                                  |

| \$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10             | Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND                         | -      |                |                |                |                |                |                | 1              | page 34                                  |

| \$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10<br>\$0F     | Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND<br>Reserved             | -      | DDD6           | DDD5           | DDD4           | DDD3           | DDD2           | DDD1           | DDD0           | page 34                                  |

| \$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10<br>\$0F<br> | Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND<br>Reserved<br>Reserved | -      | DDD6           | DDD5           | DDD4           | DDD3           | DDD2           | DDD1           | DDD0           | page 34                                  |

| \$15<br>\$14<br>\$13<br>\$12<br>\$11<br>\$10<br>\$0F     | Reserved<br>Reserved<br>PORTD<br>DDRD<br>PIND<br>Reserved             | -      | DDD6           | DDD5           | DDD4           | DDD3           | DDD2           | DDD1           | DDD0           | page 34<br>page 34<br>page 34<br>page 27 |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

2. Some of the status flags are cleared by writing a logical "1" to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a "1" back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers \$00 to \$1F only.

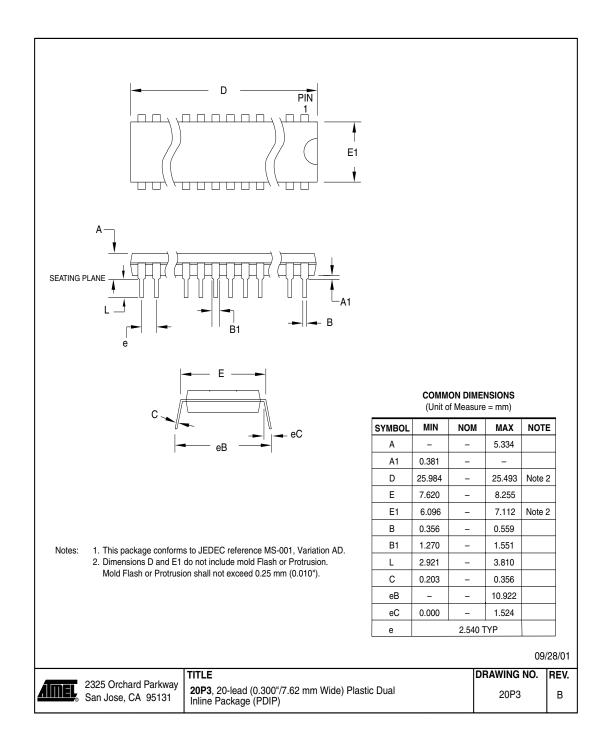

# Ordering Information<sup>(1)</sup>

| Speed (MHz) | Power Supply | Ordering Code  | Package | Operation Range |

|-------------|--------------|----------------|---------|-----------------|

| 4           | 2.7 - 6.0V   | AT90S1200-4PC  | 20P3    | Commercial      |

|             |              | AT90S1200-4SC  | 20S     | (0°C to 70°C)   |

|             |              | AT90S1200-4YC  | 20Y     |                 |

|             |              | AT90S1200-4PI  | 20P3    | Industrial      |

|             |              | AT90S1200-4SI  | 20S     | (-40°C to 85°C) |

|             |              | AT90S1200-4YI  | 20Y     |                 |

| 12          | 4.0 - 6.0V   | AT90S1200-12PC | 20P3    | Commercial      |

|             |              | AT90S1200-12SC | 20S     | (0°C to 70°C)   |

|             |              | AT90S1200-12YC | 20Y     |                 |

|             |              | AT90S1200-12PI | 20P3    | Industrial      |

|             |              | AT90S1200-12SI | 20S     | (-40°C to 85°C) |

|             |              | AT90S1200-12YI | 20Y     |                 |

Note: 1. Order AT90S1200A-XXX for devices with the RCEN Fuse programmed.

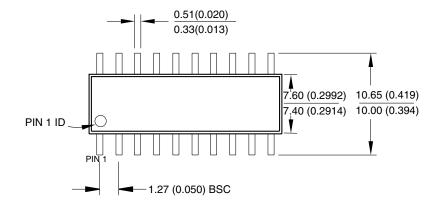

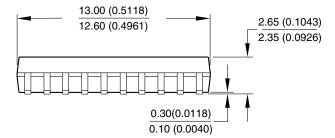

|      | Package Type                                                      |

|------|-------------------------------------------------------------------|

| 20P3 | 20-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)          |

| 20S  | 20-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)      |

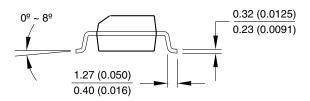

| 20Y  | 20-lead, 5.3 mm Wide, Plastic Shrink Small Outline Package (SSOP) |

## **Packaging Information**

20P3

20S, 20-lead, Plastic Gull Wing Small Outline (SOIC), 0.300" body. Dimensions in Millineters and (Inches)\* JEDEC STANDARD MS-013

20S

\*Controlling dimension: Inches

REV. A 04/11/2001