Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | ·                                                                          |

| Total RAM Bits                 | 516096                                                                     |

| Number of I/O                  | 620                                                                        |

| Number of Gates                | 300000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 896-BGA                                                                    |

| Supplier Device Package        | 896-FBGA (31x31)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe3000-2fgg896 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                    | VMV<br>(V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|--------------------|------------|----------------------------------------|---------------------------------------------|

| HSTL (I)           | 1.5        | 0.17                                   | 2.03                                        |

| HSTL (II)          | 1.5        | 0.17                                   | 2.03                                        |

| SSTL2 (I)          | 2.5        | 1.38                                   | 4.48                                        |

| SSTL2 (II)         | 2.5        | 1.38                                   | 4.48                                        |

| SSTL3 (I)          | 3.3        | 3.21                                   | 9.26                                        |

| SSTL3 (II)         | 3.3        | 3.21                                   | 9.26                                        |

| Differential       |            | •                                      | -                                           |

| LVDS/B-LVDS/M-LVDS | 2.5        | 2.26                                   | 1.50                                        |

| LVPECL             | 3.3        | 5.71                                   | 2.17                                        |

### Table 2-8 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings (continued)

Notes:

1. PDC2 is the static power (where applicable) measured on VMV.

2. PAC9 is the total dynamic power measured on VCC and VMV.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8b specification.

### Table 2-9 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>

|                                            | C <sub>LOAD</sub><br>(pF) | VCCI<br>(V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------------|---------------------------|-------------|----------------------------------------|----------------------------------------------|

| Single-Ended                               | •                         |             |                                        |                                              |

| 3.3 V LVTTL/LVCMOS                         | 35                        | 3.3         | -                                      | 474.70                                       |

| 3.3 V LVTTL/LVCMOS Wide Range <sup>4</sup> | 35                        | 3.3         | -                                      | 474.70                                       |

| 2.5 V LVCMOS                               | 35                        | 2.5         | -                                      | 270.73                                       |

| 1.8 V LVCMOS                               | 35                        | 1.8         | -                                      | 151.78                                       |

| 1.5 V LVCMOS (JESD8-11)                    | 35                        | 1.5         | -                                      | 104.55                                       |

| 3.3 V PCI                                  | 10                        | 3.3         | -                                      | 204.61                                       |

| 3.3 V PCI-X                                | 10                        | 3.3         | -                                      | 204.61                                       |

| Voltage-Referenced                         |                           |             |                                        |                                              |

| 3.3 V GTL                                  | 10                        | 3.3         | -                                      | 24.08                                        |

| 2.5 V GTL                                  | 10                        | 2.5         | -                                      | 13.52                                        |

| 3.3 V GTL+                                 | 10                        | 3.3         | -                                      | 24.10                                        |

| 2.5 V GTL+                                 | 10                        | 2.5         | -                                      | 13.54                                        |

| HSTL (I)                                   | 20                        | 1.5         | 7.08                                   | 26.22                                        |

| HSTL (II)                                  | 20                        | 1.5         | 13.88                                  | 27.22                                        |

| SSTL2 (I)                                  | 30                        | 2.5         | 16.69                                  | 105.56                                       |

| SSTL2 (II)                                 | 30                        | 2.5         | 25.91                                  | 116.60                                       |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. PDC3 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

### **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

|                                  |                    | Equivalent         |              |           | VIL         | VIH             |           | VOL         | VOH         | IOL <sup>3</sup> | IOH <sup>3</sup> |

|----------------------------------|--------------------|--------------------|--------------|-----------|-------------|-----------------|-----------|-------------|-------------|------------------|------------------|

| I/O Standard                     | Drive<br>Strength  |                    | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V       | Max.<br>V | Max.<br>V   | Min.<br>V   | mA               | mA               |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS | 12 mA              | 12 mA              | High         | -0.3      | 0.8         | 2               | 3.6       | 0.4         | 2.4         | 12               | 12               |

| 3.3 V<br>LVCMOS<br>Wide Range    | 100 µA             | 12 mA              | High         | -0.3      | 0.8         | 2               | 3.6       | 0.2         | VCCI – 0.2  | 0.1              | 0.1              |

| 2.5 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.7         | 1.7             | 3.6       | 0.7         | 1.7         | 12               | 12               |

| 1.8 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.45        | VCCI – 0.45 | 12               | 12               |

| 1.5 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.30 * VCCI | 0.7 * VCCI      | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12               | 12               |

| 3.3 V PCI                        |                    |                    |              |           | Per PC      | CI Specificatio | n         |             |             |                  |                  |

| 3.3 V PCI-X                      |                    |                    |              |           | Per PCI     | -X Specificati  | on        |             |             |                  |                  |

| 3.3 V GTL                        | 20 mA <sup>2</sup> | 20 mA <sup>2</sup> | High         | -0.3      | VREF – 0.05 | VREF + 0.05     | 3.6       | 0.4         | -           | 20               | 20               |

| 2.5 V GTL                        | 20 mA <sup>2</sup> | 20 mA <sup>2</sup> | High         | -0.3      | VREF – 0.05 | VREF + 0.05     | 3.6       | 0.4         | _           | 20               | 20               |

| 3.3 V GTL+                       | 35 mA              | 35 mA              | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.6         | -           | 35               | 35               |

| 2.5 V GTL+                       | 33 mA              | 33 mA              | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.6         | -           | 33               | 33               |

| HSTL (I)                         | 8 mA               | 8 mA               | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.4         | VCCI - 0.4  | 8                | 8                |

| HSTL (II)                        | 15 mA <sup>2</sup> | 15 mA <sup>2</sup> | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.4         | VCCI - 0.4  | 15               | 15               |

| SSTL2 (I)                        | 15 mA              | 15 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.54        | VCCI – 0.62 | 15               | 15               |

| SSTL2 (II)                       | 18 mA              | 18 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.35        | VCCI – 0.43 | 18               | 18               |

| SSTL3 (I)                        | 14 mA              | 14 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.7         | VCCI – 1.1  | 14               | 14               |

| SSTL3 (II)                       | 21 mA              | 21 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.5         | VCCI - 0.9  | 21               | 21               |

Table 2-13 • Summary of Maximum and Minimum DC Input and Output Levels

Applicable to Commercial and Industrial Conditions

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. Output drive strength is below JEDEC specification.

3. Currents are measured at 85°C junction temperature.

4. Output Slew Rates can be extracted from IBIS Models, located at http://www.microsemi.com/index.php?option=com\_content&id=1671&lang=en&view=article.

# **Microsemi**.

ProASIC3E DC and Switching Characteristics

### 3.3 V PCI, 3.3 V PCI-X

Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

#### Table 2-45 • Minimum and Maximum DC Input and Output Levels

| 3.3 V PCI/PCI-X       | V         | VIL VIH        |           | VOL       | VOH       | IOL       | IOH | IOSL | IOSH                    | IIL¹                    | IIH <sup>2</sup> |                 |

|-----------------------|-----------|----------------|-----------|-----------|-----------|-----------|-----|------|-------------------------|-------------------------|------------------|-----------------|

| Drive Strength        | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA   | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup> |

| Per PCI specification |           | Per PCI curves |           |           |           |           |     |      |                         |                         | 10               | 10              |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V< VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

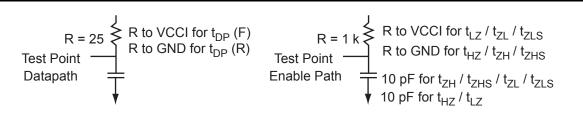

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-11.

### Figure 2-11 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the datapath; Microsemi loading for tristate is described in Table 2-46.

#### Table 2-46 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                                         | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|--------------------------------------------------------------|-----------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for $t_{DP(R)}$<br>0.615 * VCCI for $t_{DP(F)}$ | -               | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-47 • 3.3 V PCI/PCI-X

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.81            | 0.04             | 1.05            | 1.67             | 0.43              | 2.86            | 2.00            | 3.28            | 3.61            | 5.09             | 4.23             | ns    |

| –1             | 0.56              | 2.39            | 0.04             | 0.89            | 1.42             | 0.36              | 2.43            | 1.70            | 2.79            | 3.07            | 4.33             | 3.60             | ns    |

| -2             | 0.49              | 2.09            | 0.03             | 0.78            | 1.25             | 0.32              | 2.13            | 1.49            | 2.45            | 2.70            | 3.80             | 3.16             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

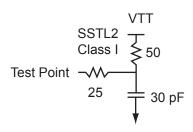

### SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). ProASIC3E devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class I     |           | VIL        |            | VOL       | VOH       | IOL         | IOH | IOSL | IOSH                    | IIL                     | IIH |     |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|------|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA   | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 15 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI – 0.62 | 15  | 15   | 87                      | 83                      | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

### Figure 2-18 • AC Loading

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                    | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-68 • SSTL 2 Class I

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 2.3 V, VREF = 1.25 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 1.33            | 0.43              | 2.17            | 1.85            |                 |                 | 4.40             | 4.08             | ns    |

| –1             | 0.56              | 1.81            | 0.04             | 1.14            | 0.36              | 1.84            | 1.57            |                 |                 | 3.74             | 3.47             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.00            | 0.32              | 1.62            | 1.38            |                 |                 | 3.29             | 3.05             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

# **Microsemi**

ProASIC3E DC and Switching Characteristics

| DC Parameter     | Description                               | Min.  | Тур.  | Max.  | Units |

|------------------|-------------------------------------------|-------|-------|-------|-------|

| VCCI             | Supply Voltage                            | 2.375 | 2.5   | 2.625 | V     |

| VOL              | Output Low Voltage                        | 0.9   | 1.075 | 1.25  | V     |

| VOH              | Output High Voltage                       | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup> | Output Lower Current                      | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup> | Output High Current                       | 0.65  | 0.91  | 1.16  | mA    |

| VI               | Input Voltage                             |       |       | 2.925 | V     |

| IIH <sup>2</sup> | Input High Leakage Current                |       |       | 10    | μA    |

| IIL <sup>2</sup> | IL <sup>2</sup> Input Low Leakage Current |       |       | 10    | μA    |

| VODIFF           | Differential Output Voltage               | 250   | 350   | 450   | mV    |

| VOCM             | Output Common Mode Voltage                | 1.125 | 1.25  | 1.375 | V     |

| VICM             | Input Common Mode Voltage                 | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF           | Input Differential Voltage <sup>2</sup>   | 100   | 350   |       | mV    |

### Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels

Notes:

1. IOL/IOH defined by VODIFF/(Resistor Network).

2. Currents are measured at 85°C junction temperature.

### Table 2-79 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | -               |

*Note:* \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

### Table 2-80 • LVDS

Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.87            | 0.04             | 1.82            | ns    |

| -1          | 0.56              | 1.59            | 0.04             | 1.55            | ns    |

| -2          | 0.49              | 1.40            | 0.03             | 1.36            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

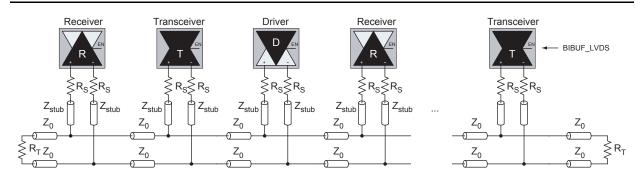

### B-LVDS/M-LVDS

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-23. The input and output buffer delays are available in the LVDS section in Table 2-80.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 2-23 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

# **Microsemi**

ProASIC3E DC and Switching Characteristics

### Table 2-84 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | K, H                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | K, H                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

Note: \*See Figure 2-25 on page 2-53 for more information.

Figure 2-35 • Timing Model and Waveforms

# **Global Resource Characteristics**

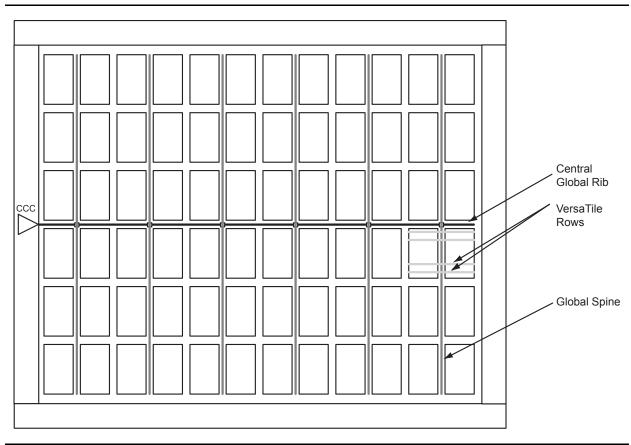

## A3PE600 Clock Tree Topology

Clock delays are device-specific. Figure 2-38 is an example of a global tree used for clock routing. The global tree presented in Figure 2-38 is driven by a CCC located on the west side of the A3PE600 device. It is used to drive all D-flip-flops in the device.

Figure 2-38 • Example of Global Tree Use in an A3PE600 Device for Clock Routing

### **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-70. Table 2-95 on page 2-69, Table 2-96 on page 2-69, and Table 2-97 on page 2-69 present minimum and maximum global clock delays within the device. Minimum and maximum delays are measured with minimum and maximum loading.

ProASIC3E DC and Switching Characteristics

# **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

**Timing Characteristics**

### Table 2-98 • ProASIC3E CCC/PLL Specification

| Parameter                                                         |                                     | Minimum                     | Typical          | Maximum                   | Units |

|-------------------------------------------------------------------|-------------------------------------|-----------------------------|------------------|---------------------------|-------|

| Clock Conditioning Circuitry Inp                                  | out Frequency f <sub>IN_CCC</sub>   | 1.5                         |                  | 350                       | MHz   |

| Clock Conditioning Circuitry Ou                                   | tput Frequency f <sub>OUT_CCC</sub> | 0.75                        |                  | 350                       | MHz   |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>     |                                     |                             | 160 <sup>3</sup> |                           | ps    |

| Serial Clock (SCLK) for Dynam                                     | ic PLL <sup>4</sup>                 |                             |                  | 125                       | MHz   |

| Number of Programmable Values in Each<br>Programmable Delay Block |                                     |                             |                  | 32                        |       |

| Input Period Jitter                                               |                                     |                             |                  | 1.5                       | ns    |

| CCC Output Peak-to-Peak Per                                       | Max                                 | <pre>     Peak-to-Pe </pre> | ak Period Jitter |                           |       |

|                                                                   |                                     | 1 Global<br>Network Used    |                  | 3 Global<br>Networks Used |       |

| 0.75 MHz to 24 MHz                                                |                                     | 0.50%                       |                  | 0.70%                     |       |

| 24 MHz to 100 MHz                                                 |                                     | 1.00%                       |                  | 1.20%                     |       |

| 100 MHz to 250 MHz                                                |                                     | 1.75%                       |                  | 2.00%                     |       |

| 250 MHz to 350 MHz                                                |                                     | 2.50%                       |                  | 5.60%                     |       |

| Acquisition Time                                                  | LockControl = 0                     |                             |                  | 300                       | μs    |

|                                                                   | LockControl = 1                     |                             |                  | 6.0                       | ms    |

| Tracking Jitter <sup>5</sup>                                      | LockControl = 0                     |                             |                  | 1.6                       | ns    |

|                                                                   | LockControl = 1                     |                             |                  | 0.8                       | ns    |

| Output Duty Cycle                                                 |                                     | 48.5                        |                  | 51.5                      | %     |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>        |                                     | 0.6                         |                  | 5.56                      | ns    |

| Delay Range in Block: Program                                     | imable Delay 2 <sup>1,2</sup>       | 0.025                       |                  | 5.56                      | ns    |

| Delay Range in Block: Fixed D                                     | elay <sup>1,4</sup>                 |                             | 2.2              |                           | ns    |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-5 for deratings

2.  $T_J = 25^{\circ}C$ , VCC = 1.5 V.

3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help for more information.

4. Maximum value obtained for a -2 speed-grade device in worst-case commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

**Wicrosemi**. ProASIC3E DC and Switching Characteristics

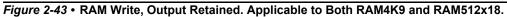

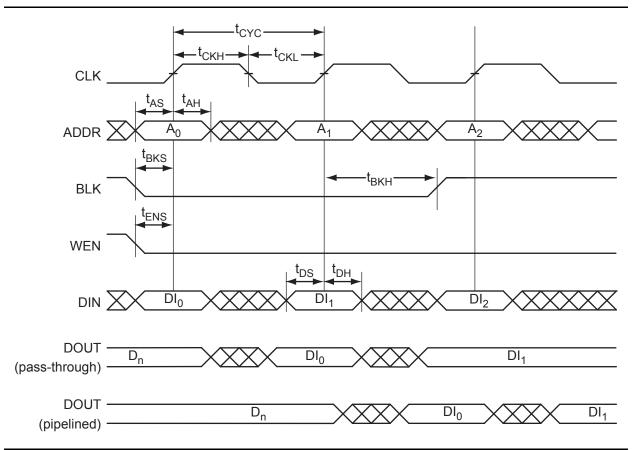

Figure 2-44 • RAM Write, Output as Write Data. Applicable to RAM4K9 Only.

# 🌜 Microsemi.

Package Pin Assignments

|            | FG324            |            | FG324            |            | FG324            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA    |

| G1         | GND              | J1         | IO267NDB6V4      | L1         | IO263NDB6V3      |

| G2         | IO287PDB7V1      | J2         | GFA0/IO273NDB6V4 | L2         | VCCIB6           |

| G3         | IO287NDB7V1      | J3         | VCOMPLF          | L3         | IO259PDB6V3      |

| G4         | IO283PPB7V1      | J4         | GFA2/IO272PDB6V4 | L4         | IO259NDB6V3      |

| G5         | VCCIB7           | J5         | GFB0/IO274NPB7V0 | L5         | GND              |

| G6         | IO279PDB7V0      | J6         | GFC0/IO275NDB7V0 | L6         | IO270NPB6V4      |

| G7         | IO291NPB7V2      | J7         | GFC1/IO275PDB7V0 | L7         | VCC              |

| G8         | VCC              | J8         | GND              | L8         | VCC              |

| G9         | IO26NDB0V3       | J9         | GND              | L9         | GND              |

| G10        | IO34NDB0V4       | J10        | GND              | L10        | GND              |

| G11        | VCC              | J11        | GND              | L11        | VCC              |

| G12        | IO94NPB2V1       | J12        | GCA2/IO115PDB3V0 | L12        | VCC              |

| G13        | IO98PDB2V2       | J13        | GCA1/IO114PDB3V0 | L13        | IO132PDB3V2      |

| G14        | VCCIB2           | J14        | GCA0/IO114NDB3V0 | L14        | GND              |

| G15        | GCC0/IO112NPB2V3 | J15        | GCB0/IO113NDB2V3 | L15        | IO117NDB3V0      |

| G16        | IO104PDB2V2      | J16        | VCOMPLC          | L16        | IO128NPB3V1      |

| G17        | IO104NDB2V2      | J17        | IO120NPB3V0      | L17        | VCCIB3           |

| G18        | GND              | J18        | IO108NDB2V3      | L18        | IO124PPB3V1      |

| H1         | IO267PDB6V4      | K1         | IO263PDB6V3      | M1         | GND              |

| H2         | VCCIB7           | K2         | GFA1/IO273PDB6V4 | M2         | IO255PDB6V2      |

| H3         | IO283NPB7V1      | K3         | VCCPLF           | M3         | IO255NDB6V2      |

| H4         | GFB1/IO274PPB7V0 | K4         | IO272NDB6V4      | M4         | IO251PPB6V2      |

| H5         | GND              | K5         | GFC2/IO270PPB6V4 | M5         | VCCIB6           |

| H6         | IO279NDB7V0      | K6         | GFB2/IO271PDB6V4 | M6         | GEB0/IO235NDB6V0 |

| H7         | VCC              | K7         | IO271NDB6V4      | M7         | GEB1/IO235PDB6V0 |

| H8         | VCC              | K8         | GND              | M8         | VCC              |

| H9         | GND              | K9         | GND              | M9         | IO192PPB4V4      |

| H10        | GND              | K10        | GND              | M10        | IO154NPB4V0      |

| H11        | VCC              | K11        | GND              | M11        | VCC              |

| H12        | VCC              | K12        | IO115NDB3V0      | M12        | GDA0/IO153NPB3V4 |

| H13        | IO98NDB2V2       | K13        | GCB2/IO116PDB3V0 | M13        | IO132NDB3V2      |

| H14        | GND              | K14        | IO116NDB3V0      | M14        | VCCIB3           |

| H15        | GCB1/IO113PDB2V3 | K15        | GCC2/IO117PDB3V0 | M15        | IO134NDB3V2      |

| H16        | GCC1/IO112PPB2V3 | K16        | VCCPLC           | M16        | IO134PDB3V2      |

| H17        | VCCIB2           | K17        | IO124NPB3V1      | M17        | IO128PPB3V1      |

| H18        | IO108PDB2V3      | K18        | IO120PPB3V0      | M18        | GND              |

|            | FG484             |            | FG484             |

|------------|-------------------|------------|-------------------|

| Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function |

| N17        | IO91NPB3V0        | R9         | VCCIB5            |

| N18        | IO90NPB3V0        | R10        | VCCIB5            |

| N19        | IO91PPB3V0        | R11        | IO135NDB5V0       |

| N20        | GNDQ              | R12        | IO135PDB5V0       |

| N21        | IO93NDB3V0        | R13        | VCCIB4            |

| N22        | IO95PDB3V1        | R14        | VCCIB4            |

| P1         | NC                | R15        | VMV3              |

| P2         | IO183PDB6V2       | R16        | VCCPLD            |

| P3         | IO187NPB6V2       | R17        | GDB1/IO109PPB3V2  |

| P4         | IO184NPB6V2       | R18        | GDC1/IO108PDB3V2  |

| P5         | IO176PPB6V1       | R19        | IO99NDB3V1        |

| P6         | IO182PDB6V1       | R20        | VCC               |

| P7         | IO182NDB6V1       | R21        | IO98NDB3V1        |

| P8         | VCCIB6            | R22        | IO101PDB3V1       |

| P9         | GND               | T1         | NC                |

| P10        | VCC               | T2         | IO177NDB6V1       |

| P11        | VCC               | Т3         | NC                |

| P12        | VCC               | T4         | IO171PDB6V0       |

| P13        | VCC               | Т5         | IO171NDB6V0       |

| P14        | GND               | Т6         | GEC1/IO169PPB6V0  |

| P15        | VCCIB3            | T7         | VCOMPLE           |

| P16        | GDB0/IO109NPB3V2  | Т8         | GNDQ              |

| P17        | IO97NDB3V1        | Т9         | GEA2/IO166PPB5V3  |

| P18        | IO97PDB3V1        | T10        | IO145NDB5V1       |

| P19        | IO99PDB3V1        | T11        | IO141NDB5V0       |

| P20        | VMV3              | T12        | IO139NDB5V0       |

| P21        | IO98PDB3V1        | T13        | IO119NDB4V1       |

| P22        | IO95NDB3V1        | T14        | IO119PDB4V1       |

| R1         | NC                | T15        | GNDQ              |

| R2         | IO177PDB6V1       | T16        | VCOMPLD           |

| R3         | VCC               | T17        | VJTAG             |

| R4         | IO176NPB6V1       | T18        | GDC0/IO108NDB3V2  |

| R5         | IO174NDB6V0       | T19        | GDA1/IO110PDB3V2  |

| R6         | IO174PDB6V0       | T20        | NC                |

| R7         | GEC0/IO169NPB6V0  | T21        | IO103PDB3V2       |

| R8         | VMV5              | T22        | IO101NDB3V1       |

|            |                   |            |                   |

|            | FG484             |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| U1         | IO175PPB6V1       |

| U2         | IO173PDB6V0       |

| U3         | IO173NDB6V0       |

| U4         | GEB1/IO168PDB6V0  |

| U5         | GEB0/IO168NDB6V0  |

| U6         | VMV6              |

| U7         | VCCPLE            |

| U8         | IO166NPB5V3       |

| U9         | IO157PPB5V2       |

| U10        | IO145PDB5V1       |

| U11        | IO141PDB5V0       |

| U12        | IO139PDB5V0       |

| U13        | IO121NDB4V1       |

| U14        | IO121PDB4V1       |

| U15        | VMV4              |

| U16        | ТСК               |

| U17        | VPUMP             |

| U18        | TRST              |

| U19        | GDA0/IO110NDB3V2  |

| U20        | NC                |

| U21        | IO103NDB3V2       |

| U22        | IO105PDB3V2       |

| V1         | NC                |

| V2         | IO175NPB6V1       |

| V3         | GND               |

| V4         | GEA1/IO167PDB6V0  |

| V5         | GEA0/IO167NDB6V0  |

| V6         | GNDQ              |

| V7         | GEC2/IO164PDB5V3  |

| V8         | IO157NPB5V2       |

| V9         | IO151NDB5V2       |

| V10        | IO151PDB5V2       |

| V11        | IO137NDB5V0       |

| V12        | IO137PDB5V0       |

| V13        | IO123NDB4V1       |

| V14        | IO123PDB4V1       |

|            | FG484             |            | FG484             |            | FG484             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| H19        | IO100PDB2V2       | K11        | GND               | M3         | IO272NDB6V4       |

| H20        | VCC               | K12        | GND               | M4         | GFA2/IO272PDB6V4  |

| H21        | VMV2              | K13        | GND               | M5         | GFA1/IO273PDB6V4  |

| H22        | IO105PDB2V2       | K14        | VCC               | M6         | VCCPLF            |

| J1         | IO285NDB7V1       | K15        | VCCIB2            | M7         | IO271NDB6V4       |

| J2         | IO285PDB7V1       | K16        | GCC1/IO112PPB2V3  | M8         | GFB2/IO271PDB6V4  |

| J3         | VMV7              | K17        | IO108NDB2V3       | M9         | VCC               |

| J4         | IO279PDB7V0       | K18        | IO108PDB2V3       | M10        | GND               |

| J5         | IO283PDB7V1       | K19        | IO110NPB2V3       | M11        | GND               |

| J6         | IO281PDB7V0       | K20        | IO106NPB2V3       | M12        | GND               |

| J7         | IO287NDB7V1       | K21        | IO109NDB2V3       | M13        | GND               |

| J8         | VCCIB7            | K22        | IO107NDB2V3       | M14        | VCC               |

| J9         | GND               | L1         | IO257PSB6V2       | M15        | GCB2/IO116PPB3V0  |

| J10        | VCC               | L2         | IO276PDB7V0       | M16        | GCA1/IO114PPB3V0  |

| J11        | VCC               | L3         | IO276NDB7V0       | M17        | GCC2/IO117PPB3V0  |

| J12        | VCC               | L4         | GFB0/IO274NPB7V0  | M18        | VCCPLC            |

| J13        | VCC               | L5         | GFA0/IO273NDB6V4  | M19        | GCA2/IO115PDB3V0  |

| J14        | GND               | L6         | GFB1/IO274PPB7V0  | M20        | IO115NDB3V0       |

| J15        | VCCIB2            | L7         | VCOMPLF           | M21        | IO126PDB3V1       |

| J16        | IO84NDB2V0        | L8         | GFC0/IO275NPB7V0  | M22        | IO124PSB3V1       |

| J17        | IO104NDB2V2       | L9         | VCC               | N1         | IO255PPB6V2       |

| J18        | IO104PDB2V2       | L10        | GND               | N2         | IO253NDB6V2       |

| J19        | IO106PPB2V3       | L11        | GND               | N3         | VMV6              |

| J20        | GNDQ              | L12        | GND               | N4         | GFC2/IO270PPB6V4  |

| J21        | IO109PDB2V3       | L13        | GND               | N5         | IO261PPB6V3       |

| J22        | IO107PDB2V3       | L14        | VCC               | N6         | IO263PDB6V3       |

| K1         | IO277NDB7V0       | L15        | GCC0/IO112NPB2V3  | N7         | IO263NDB6V3       |

| K2         | IO277PDB7V0       | L16        | GCB1/IO113PPB2V3  | N8         | VCCIB6            |

| K3         | GNDQ              | L17        | GCA0/IO114NPB3V0  | N9         | VCC               |

| K4         | IO279NDB7V0       | L18        | VCOMPLC           | N10        | GND               |

| K5         | IO283NDB7V1       | L19        | GCB0/IO113NPB2V3  | N11        | GND               |

| K6         | IO281NDB7V0       | L20        | IO110PPB2V3       | N12        | GND               |

| K7         | GFC1/IO275PPB7V0  | L21        | IO111NDB2V3       | N13        | GND               |

| K8         | VCCIB7            | L22        | IO111PDB2V3       | N14        | VCC               |

| K9         | VCC               | M1         | GNDQ              | N15        | VCCIB3            |

| K10        | GND               | M2         | IO255NPB6V2       | N16        | IO116NPB3V0       |

|            | FG676             |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| W25        | IO96PDB3V1        |

| W26        | IO94NDB3V0        |

| Y1         | IO175NDB6V1       |

| Y2         | IO175PDB6V1       |

| Y3         | IO173NDB6V0       |

| Y4         | IO173PDB6V0       |

| Y5         | GEC1/IO169PPB6V0  |

| Y6         | GNDQ              |

| Y7         | VMV6              |

| Y8         | VCCIB5            |

| Y9         | IO163NDB5V3       |

| Y10        | IO159PDB5V3       |

| Y11        | IO153PDB5V2       |

| Y12        | IO147PDB5V1       |

| Y13        | IO139PDB5V0       |

| Y14        | IO137PDB5V0       |

| Y15        | IO125NDB4V1       |

| Y16        | IO125PDB4V1       |

| Y17        | IO115NDB4V0       |

| Y18        | IO115PDB4V0       |

| Y19        | VCC               |

| Y20        | VPUMP             |

| Y21        | VCOMPLD           |

| Y22        | VCCPLD            |

| Y23        | IO100NDB3V1       |

| Y24        | IO100PDB3V1       |

| Y25        | IO96NDB3V1        |

| Y26        | IO98PDB3V1        |

|            |                   |

|            | FG896             |            | FG896             |            | FG896             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| AG9        | IO225NPB5V3       | AH15       | IO195NDB5V0       | AJ21       | IO173PDB4V2       |

| AG10       | IO223NPB5V3       | AH16       | IO185NDB4V3       | AJ22       | IO163NDB4V1       |

| AG11       | IO221PDB5V3       | AH17       | IO185PDB4V3       | AJ23       | IO163PDB4V1       |

| AG12       | IO221NDB5V3       | AH18       | IO181PDB4V3       | AJ24       | IO167NPB4V1       |

| AG13       | IO205NPB5V1       | AH19       | IO177NDB4V2       | AJ25       | VCC               |

| AG14       | IO199NDB5V0       | AH20       | IO171NPB4V2       | AJ26       | IO156NPB4V0       |

| AG15       | IO199PDB5V0       | AH21       | IO165PPB4V1       | AJ27       | VCC               |

| AG16       | IO187NDB4V4       | AH22       | IO161PPB4V0       | AJ28       | TMS               |

| AG17       | IO187PDB4V4       | AH23       | IO157NDB4V0       | AJ29       | GND               |

| AG18       | IO181NDB4V3       | AH24       | IO157PDB4V0       | AJ30       | GND               |

| AG19       | IO171PPB4V2       | AH25       | IO155NDB4V0       | AK2        | GND               |

| AG20       | IO165NPB4V1       | AH26       | VCCIB4            | AK3        | GND               |

| AG21       | IO161NPB4V0       | AH27       | TDI               | AK4        | IO217PPB5V2       |

| AG22       | IO159NDB4V0       | AH28       | VCC               | AK5        | GND               |

| AG23       | IO159PDB4V0       | AH29       | VPUMP             | AK6        | IO215PPB5V2       |

| AG24       | IO158PPB4V0       | AH30       | GND               | AK7        | GND               |

| AG25       | GDB2/IO155PDB4V0  | AJ1        | GND               | AK8        | IO207NDB5V1       |

| AG26       | GDA2/IO154PPB4V0  | AJ2        | GND               | AK9        | IO207PDB5V1       |

| AG27       | GND               | AJ3        | GEA2/IO233PPB5V4  | AK10       | IO201NDB5V0       |

| AG28       | VJTAG             | AJ4        | VCC               | AK11       | IO201PDB5V0       |

| AG29       | VCC               | AJ5        | IO217NPB5V2       | AK12       | IO193NDB4V4       |

| AG30       | IO149NDB3V4       | AJ6        | VCC               | AK13       | IO193PDB4V4       |

| AH1        | GND               | AJ7        | IO215NPB5V2       | AK14       | IO197PDB5V0       |

| AH2        | IO233NPB5V4       | AJ8        | IO213NDB5V2       | AK15       | IO191NDB4V4       |

| AH3        | VCC               | AJ9        | IO213PDB5V2       | AK16       | IO191PDB4V4       |

| AH4        | GEB2/IO232PPB5V4  | AJ10       | IO209NDB5V1       | AK17       | IO189NDB4V4       |

| AH5        | VCCIB5            | AJ11       | IO209PDB5V1       | AK18       | IO189PDB4V4       |

| AH6        | IO219NDB5V3       | AJ12       | IO203NDB5V1       | AK19       | IO179PPB4V3       |

| AH7        | IO219PDB5V3       | AJ13       | IO203PDB5V1       | AK20       | IO175NDB4V2       |

| AH8        | IO227NDB5V4       | AJ14       | IO197NDB5V0       | AK21       | IO175PDB4V2       |

| AH9        | IO227PDB5V4       | AJ15       | IO195PDB5V0       | AK22       | IO169NDB4V1       |

| AH10       | IO225PPB5V3       | AJ16       | IO183NDB4V3       | AK23       | IO169PDB4V1       |

| AH11       | IO223PPB5V3       | AJ17       | IO183PDB4V3       | AK24       | GND               |

| AH12       | IO211NDB5V2       | AJ18       | IO179NPB4V3       | AK25       | IO167PPB4V1       |

| AH13       | IO211PDB5V2       | AJ19       | IO177PDB4V2       | AK26       | GND               |

| AH14       | IO205PPB5V1       | AJ20       | IO173NDB4V2       | AK27       | GDC2/IO156PPB4V0  |

Package Pin Assignments

|            | FG896             |            | FG896             |            | FG896             |  |  |

|------------|-------------------|------------|-------------------|------------|-------------------|--|--|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |  |  |

| T11        | VCC               | U17        | GND               | V23        | IO128NDB3V1       |  |  |

| T12        | GND               | U18        | GND               | V24        | IO132PDB3V2       |  |  |

| T13        | GND               | U19        | GND               | V25        | IO130PPB3V2       |  |  |

| T14        | GND               | U20        | VCC               | V26        | IO126NDB3V1       |  |  |

| T15        | GND               | U21        | VCCIB3            | V27        | IO129NDB3V1       |  |  |

| T16        | GND               | U22        | IO120PDB3V0       | V28        | IO127NDB3V1       |  |  |

| T17        | GND               | U23        | IO128PDB3V1       | V29        | IO125NDB3V1       |  |  |

| T18        | GND               | U24        | IO124PDB3V1       | V30        | IO123PDB3V1       |  |  |

| T19        | GND               | U25        | IO124NDB3V1       | W1         | IO266NDB6V4       |  |  |

| T20        | VCC               | U26        | IO126PDB3V1       | W2         | IO262NDB6V3       |  |  |

| T21        | VCCIB3            | U27        | IO129PDB3V1       | W3         | IO260NDB6V3       |  |  |

| T22        | IO109NPB2V3       | U28        | IO127PDB3V1       | W4         | IO252NDB6V2       |  |  |

| T23        | IO116NDB3V0       | U29        | IO125PDB3V1       | W5         | IO251NDB6V2       |  |  |

| T24        | IO118NDB3V0       | U30        | IO121NDB3V0       | W6         | IO251PDB6V2       |  |  |

| T25        | IO122NPB3V1       | V1         | IO268NDB6V4       | W7         | IO255NDB6V2       |  |  |

| T26        | GCA1/IO114PPB3V0  | V2         | IO262PDB6V3       | W8         | IO249PPB6V1       |  |  |

| T27        | GCB0/IO113NPB2V3  | V3         | IO260PDB6V3       | W9         | IO253PDB6V2       |  |  |

| T28        | GCA2/IO115PPB3V0  | V4         | IO252PDB6V2       | W10        | VCCIB6            |  |  |

| T29        | VCCPLC            | V5         | IO257NPB6V2       | W11        | VCC               |  |  |

| T30        | IO121PDB3V0       | V6         | IO261NPB6V3       | W12        | GND               |  |  |

| U1         | IO268PDB6V4       | V7         | IO255PDB6V2       | W13        | GND               |  |  |

| U2         | IO264NDB6V3       | V8         | IO259PDB6V3       | W14        | GND               |  |  |

| U3         | IO264PDB6V3       | V9         | IO259NDB6V3       | W15        | GND               |  |  |

| U4         | IO258PDB6V3       | V10        | VCCIB6            | W16        | GND               |  |  |

| U5         | IO258NDB6V3       | V11        | VCC               | W17        | GND               |  |  |

| U6         | IO257PPB6V2       | V12        | GND               | W18        | GND               |  |  |

| U7         | IO261PPB6V3       | V13        | GND               | W19        | GND               |  |  |

| U8         | IO265NDB6V3       | V14        | GND               | W20        | VCC               |  |  |

| U9         | IO263NDB6V3       | V15        | GND               | W21        | VCCIB3            |  |  |

| U10        | VCCIB6            | V16        | GND               | W22        | IO134PDB3V2       |  |  |

| U11        | VCC               | V17        | GND               | W23        | IO138PDB3V3       |  |  |

| U12        | GND               | V18        | GND               | W24        | IO132NDB3V2       |  |  |

| U13        | GND               | V19        | GND               | W25        | IO136NPB3V2       |  |  |

| U14        | GND               | V20        | VCC               | W26        | IO130NPB3V2       |  |  |

| U15        | GND               | V21        | VCCIB3            | W27        | IO141PDB3V3       |  |  |

| U16        | GND               | V22        | IO120NDB3V0       | W28        | IO135PDB3V2       |  |  |

Datasheet Information

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Revision 11<br>(August 2012) | Added a Note stating "VMV pins must be connected to the corresponding VCCI pins.<br>See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further<br>information." to Table 2-1 • Absolute Maximum Ratings and Table 2-2<br>• Recommended Operating Conditions <sup>1</sup> (SAR 38322).                                                                                                                                                                                                                | 2-1<br>3-1<br>2-1            |

|                              | The drive strength, IOL, and IOH value for 3.3 V GTL and 2.5 V GTL was changed from 25 mA to 20 mA in the following tables (SAR 31924):<br>"Summary of Maximum and Minimum DC Input and Output Levels" table<br>"Summary of I/O Timing Characteristics—Software Default Settings" table<br>"I/O Output Buffer Maximum Resistances <sup>1</sup> " table<br>"Minimum and Maximum DC Input and Output Levels" table)                                                                                                   | 2-16<br>2-19<br>2-20<br>2-39 |

|                              | "Minimum and Maximum DC Input and Output Levels" table<br>Also added note stating "Output drive strength is below JEDEC specification" for<br>Tables 2-17 and 2-19.<br>Additionally, the IOL and IOH values for 3.3 V GTL+ and 2.5 V GTL+ were<br>corrected from 51 to 35 (for 3.3 V GTL+) and from 40 to 33 (for 2.5 V GTL+) in<br>table Table 2-13 (SAR 39714).                                                                                                                                                   | 2-40                         |

|                              | "Duration of Short Circuit Event Before Failure" table was revised to change the maximum temperature from 110°C to 100°C, with an example of six months instead of three months (SAR 37934).                                                                                                                                                                                                                                                                                                                        | 2-22                         |

|                              | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 34796):<br>"It uses a 5 V-tolerant input buffer and push-pull output buffer." This change was<br>made in revision 10 and omitted from the change table in error.                                                                                                                                                                                                                                                                            | 2-30                         |

| Revision 11<br>(continued)   | Figure 2-11 was updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34889).                                                                                                                                                                                                                                                                                                                                                                         | 2-38                         |

|                              | In Table 2-81 VIL and VIH were revised so that the maximum is 3.6 V for all listed values of VCCI (SAR 37222).                                                                                                                                                                                                                                                                                                                                                                                                      | 2-52                         |

|                              | Figure 2-47 and Figure 2-48 are new (SAR 34848).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-79                         |

|                              | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions and Packaging" chapter: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38322). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1                          |

Datasheet Information

| Revision                                                                 | Changes                                                                                                                                                                                                                        | Page      |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Revision 3 (Apr 2008)<br>Packaging v1.2                                  | The following pins had duplicates and the extra pins were deleted from the "PQ208" A3PE3000 table:                                                                                                                             | 4-2       |

|                                                                          | 36, 62, 171                                                                                                                                                                                                                    |           |

|                                                                          | Note: There were no pin function changes in this update.                                                                                                                                                                       |           |

|                                                                          | The following pins had duplicates and the extra pins were deleted from the "FG324" table:                                                                                                                                      | 4-12      |

|                                                                          | E2, E3, E16, E17, P2, P3, T16, U17                                                                                                                                                                                             |           |

|                                                                          | Note: There were no pin function changes in this update.                                                                                                                                                                       |           |

|                                                                          | The "FG256" pin table was updated for the A3PE600 device because the old PAT were based on the IFX die, and this is the final UMC die version.                                                                                 | 4-9       |

|                                                                          | The "FG484" was updated for the A3PE600 device because the old PAT were based on the IFX die, and this is the final UMC die version.                                                                                           | 4-22      |

|                                                                          | The following pins had duplicates and the extra pins were deleted from the "FG896" table:                                                                                                                                      | 4-41      |

|                                                                          | AD6, AE5, AE28, AF29, F5, F26, G6, G25                                                                                                                                                                                         |           |

|                                                                          | Note: There were no pin function changes in this update.                                                                                                                                                                       |           |

| Revision 2 (Mar 2008)<br>Product Brief rev. 1                            | The FG324 package was added to the "ProASIC3E Product Family" table, the "I/Os Per Package1" table, and the "Temperature Grade Offerings" table for A3PE3000.                                                                  | I, II, IV |

| <b>Revision 1 (Feb 2008)</b><br>DC and Switching<br>Characteristics v1.1 | In Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature 1, Maximum Operating Junction Temperature was changed from 110°C to 100°C for both commercial and industrial grades.                    | 2         |

|                                                                          | The "PLL Behavior at Brownout Condition" section is new.                                                                                                                                                                       | 2-4       |

|                                                                          | In the "PLL Contribution—PPLL" section, the following was deleted:<br>FCLKIN is the input clock frequency.                                                                                                                     | 2-10      |

|                                                                          | In Table 2-14 • Summary of Maximum and Minimum DC Input Levels, the note was incorrect. It previously said $T_J$ and it was corrected and changed to $T_A$ .                                                                   | 2-17      |

|                                                                          | In Table 2-98 • ProASIC3E CCC/PLL Specification, the SCLK parameter and note 1 are new.                                                                                                                                        | 2-70      |

|                                                                          | Table 2-103 • JTAG 1532 was populated with the parameter data, which was not in the previous version of the document.                                                                                                          | 2-83      |

| Revision 1 (cont'd)<br>Packaging v1.1                                    | The "PQ208" pin table for A3PE3000 was updated.                                                                                                                                                                                | 4-2       |

|                                                                          | The "FG324" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-13      |

|                                                                          | The "FG484" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-17      |

|                                                                          | The "FG896" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-41      |

| Revision 0 (Jan 2008)                                                    | This document was previously in datasheet v2.1. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is 51700098-001-0.                                               | N/A       |

| v2.1<br>(July 2007)                                                      | CoreMP7 information was removed from the "Features and Benefits" section.                                                                                                                                                      | 1-I       |

|                                                                          | The M1 device part numbers have been updated in ProASIC3E Product Family,<br>"Packaging Tables", "Temperature Grade Offerings", "Speed Grade and<br>Temperature Grade Matrix", and "Speed Grade and Temperature Grade Matrix". | 1-1       |

| Revision                    | Changes                                                                                                                                                                              | Page |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advance v0.5<br>(continued) | The "RESET" section was updated.                                                                                                                                                     | 2-25 |

|                             | The "RESET" section was updated.                                                                                                                                                     | 2-27 |

|                             | The "Introduction" of the "Introduction" section was updated.                                                                                                                        | 2-28 |

|                             | PCI-X 3.3 V was added to the Compatible Standards for 3.3 V in Table 2-<br>11 • VCCI Voltages and Compatible Standards                                                               | 2-29 |

|                             | Table 2-35 • ProASIC3E I/O Features was updated.                                                                                                                                     | 2-54 |

|                             | The "Double Data Rate (DDR) Support" section was updated to include information concerning implementation of the feature.                                                            | 2-32 |

|                             | The "Electrostatic Discharge (ESD) Protection" section was updated to include testing information.                                                                                   | 2-35 |

|                             | Level 3 and 4 descriptions were updated in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices.                                                       | 2-64 |

|                             | The notes in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices were updated.                                                                       | 2-64 |

|                             | The "Simultaneous Switching Outputs (SSOs) and Printed Circuit Board Layout" section is new.                                                                                         | 2-41 |

|                             | A footnote was added to Table 2-37 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected). | 2-55 |

|                             | Table 2-48 • ProASIC3E I/O Attributes vs. I/O Standard Applications                                                                                                                  | 2-81 |

|                             | Table 2-55 • ProASIC3 I/O Standards—SLEW and Output Drive (OUT_DRIVE) Settings                                                                                                       | 2-85 |

|                             | The "x" was updated in the "Pin Descriptions" section.                                                                                                                               | 2-50 |

|                             | The "VCC Core Supply Voltage" pin description was updated.                                                                                                                           | 2-50 |

|                             | The "VMVx I/O Supply Voltage (quiet)" pin description was updated to include information concerning leaving the pin unconnected.                                                     | 2-50 |

|                             | EXTFB was removed from Figure 2-24 • ProASIC3E CCC Options.                                                                                                                          | 2-24 |

|                             | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-13 • ProASIC3E CCC/PLL Specification.                                                          | 2-30 |

|                             | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                                                                                  | 2-28 |

|                             | The LVPECL specification in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices was updated.                                                         | 2-64 |

|                             | Table 2-15 • Levels of Hot-Swap Support was updated.                                                                                                                                 | 2-34 |

|                             | The "Cold-Sparing Support" section was updated.                                                                                                                                      | 2-34 |

|                             | "Electrostatic Discharge (ESD) Protection" section was updated.                                                                                                                      | 2-35 |

|                             | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                                                                                   | 2-50 |

|                             | The "VJTAG JTAG Supply Voltage" pin description was updated.                                                                                                                         | 2-50 |

|                             | The "VPUMP Programming Supply Voltage" pin description was updated to include information on what happens when the pin is tied to ground.                                            | 2-50 |