Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 110592                                                                   |

| Number of I/O                  | 165                                                                      |

| Number of Gates                | 600000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 256-LBGA                                                                 |

| Supplier Device Package        | 256-FPBGA (17x17)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pe600-1fg256 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| ProASIC3E Device Family Overview                                        |  |

|-------------------------------------------------------------------------|--|

| General Description                                                     |  |

| ProASIC3E DC and Switching Characteristics                              |  |

| General Specifications                                                  |  |

| Calculating Power Dissipation                                           |  |

| User I/O Characteristics                                                |  |

| VersaTile Characteristics                                               |  |

| Global Resource Characteristics                                         |  |

| Clock Conditioning Circuits                                             |  |

| Embedded SRAM and FIFO Characteristics                                  |  |

| Din Descriptions and Deckering                                          |  |

| Pin Descriptions and Packaging                                          |  |

| Supply Pins                                                             |  |

| User-Defined Supply Pins                                                |  |

| User Pins                                                               |  |

| JTAG Pins                                                               |  |

| Special Function Pins                                                   |  |

| Packaging                                                               |  |

| Related Documents                                                       |  |

| Package Pin Assignments                                                 |  |

| PQ208                                                                   |  |

| FG256                                                                   |  |

| FG324                                                                   |  |

| FG484                                                                   |  |

| FG676                                                                   |  |

| FG896                                                                   |  |

| Datasheet Information                                                   |  |

| List of Changes                                                         |  |

| Datasheet Categories                                                    |  |

| Safety Critical, Life Support, and High-Reliability Applications Policy |  |

Revision 15

### **User I/O Characteristics**

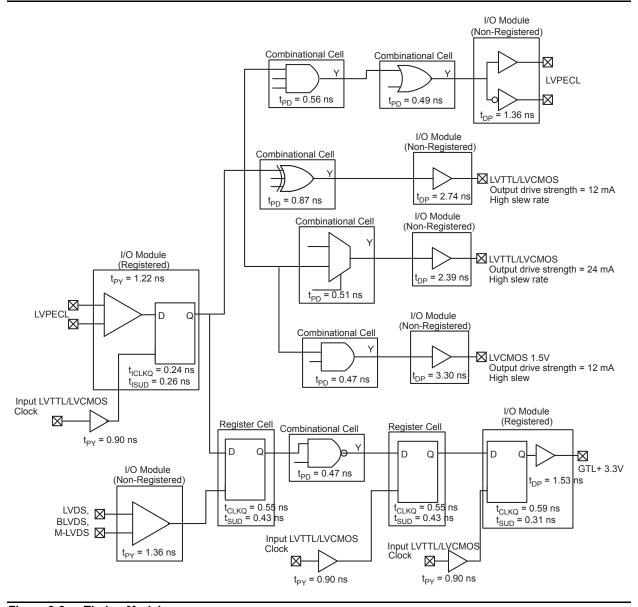

### **Timing Model**

Figure 2-2 • Timing Model

Operating Conditions: –2 Speed, Commercial Temperature Range (T<sub>J</sub> = 70°C), Worst-Case

VCC = 1.425 V

2-12 Revision 15

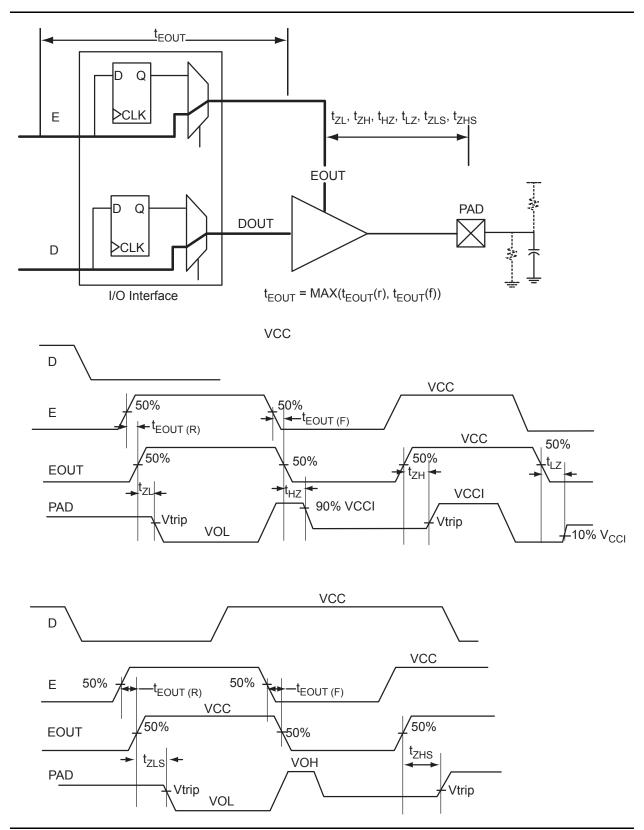

Figure 2-5 • Tristate Output Buffer Timing Model and Delays (example)

Table 2-22 • Duration of Short Circuit Event Before Failure (continued)

| Temperature | Time before Failure |

|-------------|---------------------|

| 85°C        | 2 years             |

| 100°C       | 6 months            |

Table 2-23 • Schmitt Trigger Input Hysteresis

Hysteresis Voltage Value (typ.) for Schmitt Mode Input Buffers

| Input Buffer Configuration                          | Hysteresis Value (typ.) |

|-----------------------------------------------------|-------------------------|

| 3.3 V LVTTL/LVCMOS/PCI/PCI-X (Schmitt trigger mode) | 240 mV                  |

| 2.5 V LVCMOS (Schmitt trigger mode)                 | 140 mV                  |

| 1.8 V LVCMOS (Schmitt trigger mode)                 | 80 mV                   |

| 1.5 V LVCMOS (Schmitt trigger mode)                 | 60 mV                   |

Table 2-24 • I/O Input Rise Time, Fall Time, and Related I/O Reliability\*

| Input Buffer                               | Input Rise/Fall Time (min.) | Input Rise/Fall Time (max.)                                               | Reliability         |

|--------------------------------------------|-----------------------------|---------------------------------------------------------------------------|---------------------|

| LVTTL/LVCMOS<br>(Schmitt trigger disabled) | No requirement              | 10 ns *                                                                   | 20 years<br>(110°C) |

| LVTTL/LVCMOS<br>(Schmitt trigger enabled)  | No requirement              | No requirement, but input noise voltage cannot exceed Schmitt hysteresis. | ,                   |

| HSTL/SSTL/GTL                              | No requirement              | 10 ns *                                                                   | 10 years<br>(100°C) |

| LVDS/B-LVDS/M-LVDS/<br>LVPECL              | No requirement              | 10 ns *                                                                   | 10 years<br>(100°C) |

Note: \*For clock signals and similar edge-generating signals, refer to the "ProASIC3/E SSO and Pin Placement Guidelines" chapter of the ProASIC3E FPGA Fabric User's Guide. The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

### **Voltage-Referenced I/O Characteristics**

### 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          |           | VIL VIH     |             | VIH       |           | VOH       | IOL IOH |    | IOSL                    | IOSH                    | IIL             | IIH             |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|---------|----|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA      | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA <sup>2</sup> | μA <sup>2</sup> |

| 20 mA <sup>3</sup> | -0.3      | VREF - 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20      | 20 | 181                     | 268                     | 10              | 10              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

- 3. Output drive strength is below JEDEC specification.

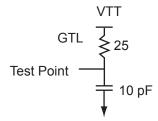

Figure 2-12 • AC Loading

Table 2-49 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF - 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-50 • 3.3 V GTL

Commercial-Case Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.08            | 0.04             | 2.93            | 0.43              | 2.04            | 2.08            |                 |                 | 4.27             | 4.31             | ns    |

| <b>-1</b>      | 0.51              | 1.77            | 0.04             | 2.50            | 0.36              | 1.73            | 1.77            |                 |                 | 3.63             | 3.67             | ns    |

| -2             | 0.45              | 1.55            | 0.03             | 2.19            | 0.32              | 1.52            | 1.55            |                 |                 | 3.19             | 3.22             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

### SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). ProASIC3E devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-66 • Minimum and Maximum DC Input and Output Levels

| SSTL2 Class I     |           | VIL VIH    |            | VIH VOL   |           |             | IOL | ЮН | IOSL                    | IOSH                    | IIL             | IIH             |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|----|-------------------------|-------------------------|-----------------|-----------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA <sup>2</sup> | μA <sup>2</sup> |

| 15 mA             | _0 3      | VREF _ 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI - 0.62 | 15  | 15 | 87                      | 83                      | 10              | 10              |

#### Notes:

- 1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 2. Currents are measured at 85°C junction temperature.

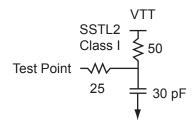

Figure 2-18 • AC Loading

Table 2-67 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.25                    | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-68 • SSTL 2 Class I

Commercial-Case Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.25 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zhs</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 1.33            | 0.43              | 2.17            | 1.85            |                 |                 | 4.40             | 4.08             | ns    |

| <b>-1</b>      | 0.56              | 1.81            | 0.04             | 1.14            | 0.36              | 1.84            | 1.57            |                 |                 | 3.74             | 3.47             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.00            | 0.32              | 1.62            | 1.38            |                 |                 | 3.29             | 3.05             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

### Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels

| DC Parameter     | Description                             | Min.  | Тур.  | Max.  | Units |

|------------------|-----------------------------------------|-------|-------|-------|-------|

| VCCI             | Supply Voltage                          | 2.375 | 2.5   | 2.625 | V     |

| VOL              | Output Low Voltage                      | 0.9   | 1.075 | 1.25  | V     |

| VOH              | Output High Voltage                     | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup> | Output Lower Current                    | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup> | Output High Current                     | 0.65  | 0.91  | 1.16  | mA    |

| VI               | Input Voltage                           | 0     |       | 2.925 | V     |

| IIH <sup>2</sup> | Input High Leakage Current              |       |       | 10    | μΑ    |

| IIL <sup>2</sup> | Input Low Leakage Current               |       |       | 10    | μΑ    |

| VODIFF           | Differential Output Voltage             | 250   | 350   | 450   | mV    |

| VOCM             | Output Common Mode Voltage              | 1.125 | 1.25  | 1.375 | V     |

| VICM             | Input Common Mode Voltage               | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF           | Input Differential Voltage <sup>2</sup> | 100   | 350   |       | mV    |

#### Notes:

- 1. IOL/IOH defined by VODIFF/(Resistor Network).

- 2. Currents are measured at 85°C junction temperature.

### Table 2-79 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | _               |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

2-50 Revision 15

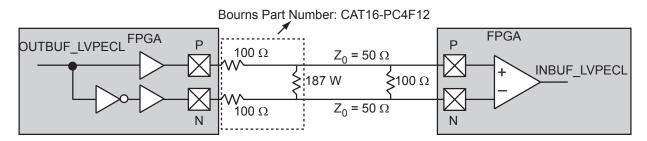

### **LVPECL**

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-24. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

Figure 2-24 • LVPECL Circuit Diagram and Board-Level Implementation

Table 2-81 • Minimum and Maximum DC Input and Output Levels

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCI         | Supply Voltage                 | 3.    | 0    | 3.    | 3    | 3.    | 6    | V     |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

Table 2-82 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.64          | 1.94           | Cross point          | -               |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-83 • LVPECL Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.83            | 0.04             | 1.63            | ns    |

| _1          | 0.56              | 1.55            | 0.04             | 1.39            | ns    |

| -2          | 0.49              | 1.36            | 0.03             | 1.22            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

2-52 Revision 15

Table 2-84 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                             | Measuring Nodes (from, to)* |

|-----------------------|------------------------------------------------------------------|-----------------------------|

| t <sub>OCLKQ</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                     |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                        |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                        |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                        |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                        |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                     |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                        |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                        |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                     |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                   | J, H                        |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                        |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | K, H                        |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | K, H                        |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                     |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                        |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                        |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                        |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                        |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                        |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                        |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                        |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                        |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                        |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                        |

Note: \*See Figure 2-25 on page 2-53 for more information.

2-54 Revision 15

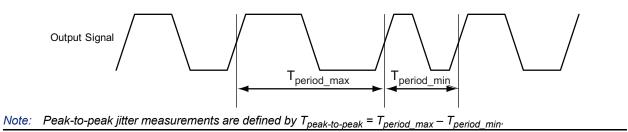

Figure 2-39 • Peak-to-Peak Jitter Definition

Pin Descriptions and Packaging

### **Special Function Pins**

NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

### **Packaging**

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

### **Related Documents**

### **User's Guides**

ProASIC3E FPGA Fabric User's Guide

http://www.microsemi.com/document-portal/doc\_download/130883-proasic3e-fpga-fabric-user-squide

### **Packaging**

The following documents provide packaging information and device selection for low power flash devices.

### **Product Catalog**

http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

### Package Mechanical Drawings

http://www.microsemi.com/document-portal/doc\_download/131095-package-mechanical-drawings

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials: http://www.microsemi.com/products/fpga-soc/solutions.

3-4 Revision 15

| PQ208      |                  |  |

|------------|------------------|--|

| Pin Number | A3PE600 Function |  |

| 108        | TDO              |  |

| 109        | TRST             |  |

| 110        | VJTAG            |  |

| 111        | VMV3             |  |

| 112        | GDA0/IO67NPB3V1  |  |

| 113        | GDB0/IO66NPB3V1  |  |

| 114        | GDA1/IO67PPB3V1  |  |

| 115        | GDB1/IO66PPB3V1  |  |

| 116        | GDC0/IO65NDB3V1  |  |

| 117        | GDC1/IO65PDB3V1  |  |

| 118        | IO62NDB3V1       |  |

| 119        | IO62PDB3V1       |  |

| 120        | IO58NDB3V0       |  |

| 121        | IO58PDB3V0       |  |

| 122        | GND              |  |

| 123        | VCCIB3           |  |

| 124        | GCC2/IO55PSB3V0  |  |

| 125        | GCB2/IO54PSB3V0  |  |

| 126        | NC               |  |

| 127        | IO53NDB3V0       |  |

| 128        | GCA2/IO53PDB3V0  |  |

| 129        | GCA1/IO52PPB3V0  |  |

| 130        | GND              |  |

| 131        | VCCPLC           |  |

| 132        | GCA0/IO52NPB3V0  |  |

| 133        | VCOMPLC          |  |

| 134        | GCB0/IO51NDB2V1  |  |

| 135        | GCB1/IO51PDB2V1  |  |

| 136        | GCC1/IO50PSB2V1  |  |

| 137        | IO49NDB2V1       |  |

| 138        | IO49PDB2V1       |  |

| 139        | IO48PSB2V1       |  |

| 140        | VCCIB2           |  |

| 141        | GND              |  |

| 142        | VCC              |  |

| 143        | IO47NDB2V1       |  |

| PQ208 Pin Number A3PE600 Function |  |  |  |  |

|-----------------------------------|--|--|--|--|

| A3PE600 Function                  |  |  |  |  |

| IO47PDB2V1                        |  |  |  |  |

| IO44NDB2V1                        |  |  |  |  |

| IO44PDB2V1                        |  |  |  |  |

| IO43NDB2V0                        |  |  |  |  |

| IO43PDB2V0                        |  |  |  |  |

| IO40NDB2V0                        |  |  |  |  |

| IO40PDB2V0                        |  |  |  |  |

| GBC2/IO38PSB2V0                   |  |  |  |  |

| GBA2/IO36PSB2V0                   |  |  |  |  |

| GBB2/IO37PSB2V0                   |  |  |  |  |

| VMV2                              |  |  |  |  |

| GNDQ                              |  |  |  |  |

| GND                               |  |  |  |  |

| VMV1                              |  |  |  |  |

| GNDQ                              |  |  |  |  |

| GBA1/IO35PDB1V1                   |  |  |  |  |

| GBA0/IO35NDB1V1                   |  |  |  |  |

| GBB1/IO34PDB1V1                   |  |  |  |  |

| GND                               |  |  |  |  |

| GBB0/IO34NDB1V1                   |  |  |  |  |

| GBC1/IO33PDB1V1                   |  |  |  |  |

| GBC0/IO33NDB1V1                   |  |  |  |  |

| IO31PDB1V1                        |  |  |  |  |

| IO31NDB1V1                        |  |  |  |  |

| IO27PDB1V0                        |  |  |  |  |

| IO27NDB1V0                        |  |  |  |  |

| VCCIB1                            |  |  |  |  |

| VCC                               |  |  |  |  |

| IO23PPB1V0                        |  |  |  |  |

| IO22PSB1V0                        |  |  |  |  |

| IO23NPB1V0                        |  |  |  |  |

| IO21PDB1V0                        |  |  |  |  |

| IO21NDB1V0                        |  |  |  |  |

| IO19PPB0V2                        |  |  |  |  |

| GND                               |  |  |  |  |

| IO18PPB0V2                        |  |  |  |  |

|                                   |  |  |  |  |

| PQ208      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | A3PE600 Function |  |  |

| 180        | IO19NPB0V2       |  |  |

| 181        | IO18NPB0V2       |  |  |

| 182        | IO17PPB0V2       |  |  |

| 183        | IO16PPB0V2       |  |  |

| 184        | IO17NPB0V2       |  |  |

| 185        | IO16NPB0V2       |  |  |

| 186        | VCCIB0           |  |  |

| 187        | VCC              |  |  |

| 188        | IO15PDB0V2       |  |  |

| 189        | IO15NDB0V2       |  |  |

| 190        | IO13PDB0V2       |  |  |

| 191        | IO13NDB0V2       |  |  |

| 192        | IO11PSB0V1       |  |  |

| 193        | IO09PDB0V1       |  |  |

| 194        | IO09NDB0V1       |  |  |

| 195        | GND              |  |  |

| 196        | IO07PDB0V1       |  |  |

| 197        | IO07NDB0V1       |  |  |

| 198        | IO05PDB0V0       |  |  |

| 199        | IO05NDB0V0       |  |  |

| 200        | VCCIB0           |  |  |

| 201        | GAC1/IO02PDB0V0  |  |  |

| 202        | GAC0/IO02NDB0V0  |  |  |

| 203        | GAB1/IO01PDB0V0  |  |  |

| 204        | GAB0/IO01NDB0V0  |  |  |

| 205        | GAA1/IO00PDB0V0  |  |  |

| 206        | GAA0/IO00NDB0V0  |  |  |

| 207        | GNDQ             |  |  |

| 208        | VMV0             |  |  |

|            | PQ208             |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| 1          | GND               |

| 2          | GNDQ              |

| 3          | VMV7              |

| 4          | GAB2/IO220PSB7V3  |

| 5          | GAA2/IO221PDB7V3  |

| 6          | IO221NDB7V3       |

| 7          | GAC2/IO219PDB7V3  |

| 8          | IO219NDB7V3       |

| 9          | IO215PDB7V3       |

| 10         | IO215NDB7V3       |

| 11         | IO212PDB7V2       |

| 12         | IO212NDB7V2       |

| 13         | IO208PDB7V2       |

| 14         | IO208NDB7V2       |

| 15         | IO204PSB7V1       |

| 16         | VCC               |

| 17         | GND               |

| 18         | VCCIB7            |

| 19         | IO200PDB7V1       |

| 20         | IO200NDB7V1       |

| 21         | IO196PSB7V0       |

| 22         | GFC1/IO192PSB7V0  |

| 23         | GFB1/IO191PDB7V0  |

| 24         | GFB0/IO191NDB7V0  |

| 25         | VCOMPLF           |

| 26         | GFA0/IO190NPB6V2  |

| 27         | VCCPLF            |

| 28         | GFA1/IO190PPB6V2  |

| 29         | GND               |

| 30         | GFA2/IO189PDB6V2  |

| 31         | IO189NDB6V2       |

| 32         | GFB2/IO188PPB6V2  |

| 33         | GFC2/IO187PPB6V2  |

| 34         | IO188NPB6V2       |

| 35         | IO187NPB6V2       |

| 36         | VCC               |

| PQ208      |                   |  |  |  |

|------------|-------------------|--|--|--|

| Pin Number | A3PE1500 Function |  |  |  |

| 37         | IO184PDB6V2       |  |  |  |

| 38         | IO184NDB6V2       |  |  |  |

| 39         | IO180PSB6V1       |  |  |  |

| 40         | VCCIB6            |  |  |  |

| 41         | GND               |  |  |  |

| 42         | IO176PDB6V1       |  |  |  |

| 43         | IO176NDB6V1       |  |  |  |

| 44         | GEC1/IO169PDB6V0  |  |  |  |

| 45         | GEC0/IO169NDB6V0  |  |  |  |

| 46         | GEB1/IO168PPB6V0  |  |  |  |

| 47         | GEA1/IO167PPB6V0  |  |  |  |

| 48         | GEB0/IO168NPB6V0  |  |  |  |

| 49         | GEA0/IO167NPB6V0  |  |  |  |

| 50         | VMV6              |  |  |  |

| 51         | GNDQ              |  |  |  |

| 52         | GND               |  |  |  |

| 53         | VMV5              |  |  |  |

| 54         | GNDQ              |  |  |  |

| 55         | IO166NDB5V3       |  |  |  |

| 56         | GEA2/IO166PDB5V3  |  |  |  |

| 57         | IO165NDB5V3       |  |  |  |

| 58         | GEB2/IO165PDB5V3  |  |  |  |

| 59         | IO164NDB5V3       |  |  |  |

| 60         | GEC2/IO164PDB5V3  |  |  |  |

| 61         | IO163PSB5V3       |  |  |  |

| 62         | VCCIB5            |  |  |  |

| 63         | IO161PSB5V3       |  |  |  |

| 64         | IO157NDB5V2       |  |  |  |

| 65         | GND               |  |  |  |

| 66         | IO157PDB5V2       |  |  |  |

| 67         | IO153NDB5V2       |  |  |  |

| 68         | IO153PDB5V2       |  |  |  |

| 69         | IO149NDB5V1       |  |  |  |

| 70         | IO149PDB5V1       |  |  |  |

| 71         | VCC               |  |  |  |

| 72         | VCCIB5            |  |  |  |

| D0000      |                   |  |  |  |

|------------|-------------------|--|--|--|

| PQ208      |                   |  |  |  |

| Pin Number | A3PE1500 Function |  |  |  |

| 73         | IO145NDB5V1       |  |  |  |

| 74         | IO145PDB5V1       |  |  |  |

| 75         | IO143NDB5V1       |  |  |  |

| 76         | IO143PDB5V1       |  |  |  |

| 77         | IO137NDB5V0       |  |  |  |

| 78         | IO137PDB5V0       |  |  |  |

| 79         | IO135NDB5V0       |  |  |  |

| 80         | IO135PDB5V0       |  |  |  |

| 81         | GND               |  |  |  |

| 82         | IO131NDB4V2       |  |  |  |

| 83         | IO131PDB4V2       |  |  |  |

| 84         | IO129NDB4V2       |  |  |  |

| 85         | IO129PDB4V2       |  |  |  |

| 86         | IO127NDB4V2       |  |  |  |

| 87         | IO127PDB4V2       |  |  |  |

| 88         | VCC               |  |  |  |

| 89         | VCCIB4            |  |  |  |

| 90         | IO121NDB4V1       |  |  |  |

| 91         | IO121PDB4V1       |  |  |  |

| 92         | IO119NDB4V1       |  |  |  |

| 93         | IO119PDB4V1       |  |  |  |

| 94         | IO113NDB4V0       |  |  |  |

| 95         | GDC2/IO113PDB4V0  |  |  |  |

| 96         | IO112NDB4V0       |  |  |  |

| 97         | GND               |  |  |  |

| 98         | GDB2/IO112PDB4V0  |  |  |  |

| 99         | GDA2/IO111PSB4V0  |  |  |  |

| 100        | GNDQ              |  |  |  |

| 101        | TCK               |  |  |  |

| 102        | TDI               |  |  |  |

| 103        | TMS               |  |  |  |

| 104        | VMV4              |  |  |  |

| 105        | GND               |  |  |  |

| 106        | VPUMP             |  |  |  |

| 107        | GNDQ              |  |  |  |

| 108        | TDO               |  |  |  |

4-4 Revision 15

|            | FG256            |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3PE600 Function |  |  |  |

| P9         | IO82PDB5V0       |  |  |  |

| P10        | IO76NDB4V1       |  |  |  |

| P11        | IO76PDB4V1       |  |  |  |

| P12        | VMV4             |  |  |  |

| P13        | TCK              |  |  |  |

| P14        | VPUMP            |  |  |  |

| P15        | TRST             |  |  |  |

| P16        | GDA0/IO67NDB3V1  |  |  |  |

| R1         | GEA1/IO102PDB6V0 |  |  |  |

| R2         | GEA0/IO102NDB6V0 |  |  |  |

| R3         | GNDQ             |  |  |  |

| R4         | GEC2/IO99PDB5V2  |  |  |  |

| R5         | IO95NPB5V1       |  |  |  |

| R6         | IO91NDB5V1       |  |  |  |

| R7         | IO91PDB5V1       |  |  |  |

| R8         | IO83NDB5V0       |  |  |  |

| R9         | IO83PDB5V0       |  |  |  |

| R10        | IO77NDB4V1       |  |  |  |

| R11        | IO77PDB4V1       |  |  |  |

| R12        | IO69NDB4V0       |  |  |  |

| R13        | GDB2/IO69PDB4V0  |  |  |  |

| R14        | TDI              |  |  |  |

| R15        | GNDQ             |  |  |  |

| R16        | TDO              |  |  |  |

| T1         | GND              |  |  |  |

| T2         | IO100NDB5V2      |  |  |  |

| Т3         | GEB2/IO100PDB5V2 |  |  |  |

| T4         | IO99NDB5V2       |  |  |  |

| T5         | IO88NDB5V0       |  |  |  |

| T6         | IO88PDB5V0       |  |  |  |

| T7         | IO89NSB5V0       |  |  |  |

| Т8         | IO80NSB4V1       |  |  |  |

| Т9         | IO81NDB4V1       |  |  |  |

| T10        | IO81PDB4V1       |  |  |  |

| T11        | IO70NDB4V0       |  |  |  |

| T12        | GDC2/IO70PDB4V0  |  |  |  |

| FG256      |                  |  |

|------------|------------------|--|

| Pin Number | A3PE600 Function |  |

| T13        | IO68NDB4V0       |  |

| T14        | GDA2/IO68PDB4V0  |  |

| T15        | TMS              |  |

| T16        | GND              |  |

| 50404      |                  |  |

|------------|------------------|--|

|            | FG484            |  |

| Pin Number | A3PE600 Function |  |

| V15        | IO69NDB4V0       |  |

| V16        | GDB2/IO69PDB4V0  |  |

| V17        | TDI              |  |

| V18        | GNDQ             |  |

| V19        | TDO              |  |

| V20        | GND              |  |

| V21        | NC               |  |

| V22        | IO63NDB3V1       |  |

| W1         | NC               |  |

| W2         | NC               |  |

| W3         | NC               |  |

| W4         | GND              |  |

| W5         | IO100NDB5V2      |  |

| W6         | GEB2/IO100PDB5V2 |  |

| W7         | IO99NDB5V2       |  |

| W8         | IO88NDB5V0       |  |

| W9         | IO88PDB5V0       |  |

| W10        | IO89NDB5V0       |  |

| W11        | IO80NDB4V1       |  |

| W12        | IO81NDB4V1       |  |

| W13        | IO81PDB4V1       |  |

| W14        | IO70NDB4V0       |  |

| W15        | GDC2/IO70PDB4V0  |  |

| W16        | IO68NDB4V0       |  |

| W17        | GDA2/IO68PDB4V0  |  |

| W18        | TMS              |  |

| W19        | GND              |  |

| W20        | NC               |  |

| W21        | NC               |  |

| W22        | NC               |  |

| Y1         | VCCIB6           |  |

| Y2         | NC               |  |

| Y3         | NC               |  |

| Y4         | IO98NDB5V2       |  |

| Y5         | GND              |  |

| Y6         | IO94NDB5V1       |  |

| <u> </u>   |                  |  |

| FG484      |                  |  |

|------------|------------------|--|

| Pin Number | A3PE600 Function |  |

| Y7         | IO94PDB5V1       |  |

| Y8         | VCC              |  |

| Y9         | VCC              |  |

| Y10        | IO89PDB5V0       |  |

| Y11        | IO80PDB4V1       |  |

| Y12        | IO78NPB4V1       |  |

| Y13        | NC               |  |

| Y14        | VCC              |  |

| Y15        | VCC              |  |

| Y16        | NC               |  |

| Y17        | NC               |  |

| Y18        | GND              |  |

| Y19        | NC               |  |

| Y20        | NC               |  |

| Y21        | NC               |  |

| Y22        | VCCIB3           |  |

|                              | FG676       |

|------------------------------|-------------|

| Pin Number A3PE1500 Function |             |

| L17                          | GND         |

| L18                          | VCC         |

| L19                          | VCCIB2      |

| L20                          | IO67PDB2V1  |

| L21                          | IO67NDB2V1  |

| L22                          | IO71PDB2V2  |

| L23                          | IO71NDB2V2  |

| L24                          | GNDQ        |

| L25                          | IO82PDB2V3  |

| L26                          | IO84NDB2V3  |

| M1                           | IO198NPB7V0 |

| M2                           | IO202PDB7V1 |

| M3                           | IO202NDB7V1 |

| M4                           | IO206NDB7V1 |

| M5                           | IO206PDB7V1 |

| M6                           | IO204NDB7V1 |

| M7                           | IO204PDB7V1 |

| M8                           | VCCIB7      |

| M9                           | VCC         |

| M10                          | GND         |

| M11                          | GND         |

| M12                          | GND         |

| M13                          | GND         |

| M14                          | GND         |

| M15                          | GND         |

| M16                          | GND         |

| M17                          | GND         |

| M18                          | VCC         |

| M19                          | VCCIB2      |

| M20                          | IO73NDB2V2  |

| M21                          | IO73PDB2V2  |

| M22                          | IO81PPB2V3  |

| M23                          | IO77PDB2V2  |

| M24                          | IO77NDB2V2  |

| M25                          | IO82NDB2V3  |

| M26                          | IO83PDB2V3  |

|            | FG676             |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| N1         | GFB0/IO191NPB7V0  |

| N2         | VCOMPLF           |

| N3         | GFB1/IO191PPB7V0  |

| N4         | IO196PDB7V0       |

| N5         | GFA0/IO190NDB6V2  |

| N6         | IO200PDB7V1       |

| N7         | IO200NDB7V1       |

| N8         | VCCIB7            |

| N9         | VCC               |

| N10        | GND               |

| N11        | GND               |

| N12        | GND               |

| N13        | GND               |

| N14        | GND               |

| N15        | GND               |

| N16        | GND               |

| N17        | GND               |

| N18        | VCC               |

| N19        | VCCIB2            |

| N20        | IO79PDB2V3        |

| N21        | IO79NDB2V3        |

| N22        | GCA2/IO88PPB3V0   |

| N23        | IO81NPB2V3        |

| N24        | GCA0/IO87NDB3V0   |

| N25        | GCB0/IO86NPB2V3   |

| N26        | IO83NDB2V3        |

| P1         | GFA2/IO189PDB6V2  |

| P2         | VCCPLF            |

| P3         | IO193PPB7V0       |

| P4         | IO196NDB7V0       |

| P5         | GFA1/IO190PDB6V2  |

| P6         | IO194PDB7V0       |

| P7         | IO194NDB7V0       |

| P8         | VCCIB6            |

| P9         | VCC               |

| P10        | GND               |

| FG676      |                   |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| P11        | GND               |

| P12        | GND               |

| P13        | GND               |

| P14        | GND               |

| P15        | GND               |

| P16        | GND               |

| P17        | GND               |

| P18        | VCC               |

| P19        | VCCIB3            |

| P20        | GCC0/IO85NDB2V3   |

| P21        | GCC1/IO85PDB2V3   |

| P22        | GCB1/IO86PPB2V3   |

| P23        | IO88NPB3V0        |

| P24        | GCA1/IO87PDB3V0   |

| P25        | VCCPLC            |

| P26        | VCOMPLC           |

| R1         | IO189NDB6V2       |

| R2         | IO185PDB6V2       |

| R3         | IO187NPB6V2       |

| R4         | IO193NPB7V0       |

| R5         | GFC2/IO187PPB6V2  |

| R6         | GFC1/IO192PDB7V0  |

| R7         | GFC0/IO192NDB7V0  |

| R8         | VCCIB6            |

| R9         | VCC               |

| R10        | GND               |

| R11        | GND               |

| R12        | GND               |

| R13        | GND               |

| R14        | GND               |

| R15        | GND               |

| R16        | GND               |

| R17        | GND               |

| R18        | VCC               |

| R19        | VCCIB3            |

| R20        | NC                |

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page       |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 10<br>(March 2012) | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34669).                                                                                                                                                                                                                     | l, 1-1     |

|                             | The Y security option and Licensed DPA Logo were added to the "ProASIC3E Ordering Information" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 34727).                                                                                                                                                                                                                                 | III        |

|                             | The following sentence was removed from the "Advanced Architecture" section: "In addition, extensive on-chip programming circuitry allows for rapid, single-voltage (3.3 V) programming of IGLOOe devices via an IEEE 1532 JTAG interface" (SAR 34689).                                                                                                                                                                                                                                  | 1-3        |

|                             | The "Specifying I/O States During Programming" section is new (SAR 34699).                                                                                                                                                                                                                                                                                                                                                                                                               | 1-6        |

|                             | VCCPLL in Table 2-2 • Recommended Operating Conditions <sup>1</sup> was corrected from "1.4 to 1.6 V" to "1.425 to 1.575 V" (SAR 33851).                                                                                                                                                                                                                                                                                                                                                 | 2-2        |

|                             | The $T_J$ symbol was added to the table and notes regarding $T_A$ and $T_J$ were removed. The second of two parameters in the VCCI and VMV row, called "3.3 V DC supply voltage," was corrected to "3.0 V DC supply voltage" (SAR 37227).                                                                                                                                                                                                                                                |            |

|                             | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—P <sub>CLOCK</sub> " section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>ProASIC3E FPGA Fabric User's Guide</i> (SAR 34735).                                                                                                                                                                                                  | 2-9        |

|                             | $t_{\text{DOUT}}$ was corrected to $t_{\text{DIN}}$ in Figure 2-3 $\bullet$ Input Buffer Timing Model and Delays (example) (SAR 37109).                                                                                                                                                                                                                                                                                                                                                  | 2-13       |

|                             | The typo related to the values for 3.3 V LVCMOS Wide Range in Table 2-17 • Summary of I/O Timing Characteristics—Software Default Settings was corrected (SAR 37227).                                                                                                                                                                                                                                                                                                                    | 2-19       |

|                             | The notes regarding drive strength in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section and "3.3 V LVCMOS Wide Range" section and tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100~\mu A$ . The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 34763). | 2-18, 2-27 |

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page          |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 10<br>(continued) | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-19 • I/O Output Buffer Maximum Resistances <sup>1</sup> and Table 2-21 • I/O Short Currents IOSH/IOSL was replaced by "Same as regular 3.3 V LVCMOS" (SAR 33853).                                                                                                                                                                                                                             | 2-20,<br>2-27 |

|                            | 3.3 V LVCMOS Wide Range information was separated from regular 3.3 V LVCMOS and placed into its own new section, "3.3 V LVCMOS Wide Range". Values of IOSH and IOSL were added in Table 2-29 • Minimum and Maximum DC Input and Output Levels (SAR 33853).                                                                                                                                                                                 |               |

|                            | The formulas in the table notes for Table 2-20 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 34755).                                                                                                                                                                                                                                                                                                                        | 2-21          |

|                            | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34889).                                                                                                                                                                                                                                  |               |

|                            | The titles and subtitles for Table 2-31 • 3.3 V LVCMOS Wide Range High Slew and Table 2-32 • 3.3 V LVCMOS Wide Range Low Slew were corrected (SAR 37227).                                                                                                                                                                                                                                                                                  | 2-28, 2-29    |

|                            | The following notes were removed from Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels (SAR 34812): ±5%                                                                                                                                                                                                                                                                                                                    | 2-50          |

|                            | Differential input voltage = ±350 mV                                                                                                                                                                                                                                                                                                                                                                                                       |               |

|                            | Minimum pulse width High and Low values were added to the tables in the "Global Tree Timing Characteristics" section. The maximum frequency for global clock parameter was removed from these tables because a frequency on the global is only an indication of what the global network can do. There are other limiters such as the SRAM, I/Os, and PLL. SmartTime software should be used to determine the design frequency (SAR 36957). |               |

|                            | A note was added to Table 2-98 • ProASIC3E CCC/PLL Specification indicating that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 34824).                                                                                                                                                                                                | 2-70          |

|                            | The following figures were deleted. Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 34872).                                                                                                                                                                                                            |               |

|                            | Figure 2-44 • Write Access after Write onto Same Address                                                                                                                                                                                                                                                                                                                                                                                   | 2-82          |

|                            | Figure 2-45 • Read Access after Write onto Same Address                                                                                                                                                                                                                                                                                                                                                                                    |               |

|                            | Figure 2-46 • Write Access after Read onto Same Address                                                                                                                                                                                                                                                                                                                                                                                    |               |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-49 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SAR 35750).                                                                                                                                                                                                        |               |

|                            | The "Pin Descriptions and Packaging" chapter is new (SAR 34771).                                                                                                                                                                                                                                                                                                                                                                           | 3-1           |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 34771).                                                                                                                                                                                                                                                                                       | 4-1           |

|                            | Pin E6 for the FG256 package was corrected from VvB0 to VCCIB0 (SARs 30364, 31597, 26243).                                                                                                                                                                                                                                                                                                                                                 | 4-9           |

| July 2010                  | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "ProASIC3E Device Status" table on page II indicates the status for each device in the device family.                                                                                                                                                                             |               |

5-4 Revision 15

| Revision                       | Changes                                                                                                                                                                                 | Page             |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| v2.0<br>(continued)            | Table 3-6 • Temperature and Voltage Derating Factors for Timing Delays was updated.                                                                                                     | 3-5              |

|                                | Table 3-5 • Package Thermal Resistivities was updated.                                                                                                                                  | 3-5              |

|                                | Table 3-10 • Different Components Contributing to the Dynamic Power Consumption in ProASIC3E Devices was updated.                                                                       | 3-8              |

|                                | $t_{WRO}$ and $t_{CCKH}$ were added to Table 3-94 • RAM4K9 and Table 3-95 • RAM512X18.                                                                                                  | 3-74 to<br>3-74  |

|                                | The note in Table 3-24 • I/O Input Rise Time, Fall Time, and Related I/O Reliability was updated.                                                                                       | 3-23             |

|                                | Figure 3-43 • Write Access After Write onto Same Address, Figure 3-44 • Read Access After Write onto Same Address, and Figure 3-45 • Write Access After Read onto Same Address are new. | 3-71 to 3-<br>73 |

|                                | Figure 3-53 • Timing Diagram was updated.                                                                                                                                               | 3-80             |

|                                | Notes were added to the package diagrams identifying if they were top or bottom view.                                                                                                   | N/A              |

|                                | The A3PE1500 "208-Pin PQFP" table is new.                                                                                                                                               | 4-4              |

|                                | The A3PE1500 "484-Pin FBGA" table is new.                                                                                                                                               | 4-18             |

|                                | The A3PE1500 "A3PE1500 Function" table is new.                                                                                                                                          | 4-24             |

| Advance v0.6<br>(January 2007) | In the "Packaging Tables" table, the number of I/Os for the A3PE1500 was changed for the FG484 and FG676 packages.                                                                      | ii               |

| Advance v0.5<br>(April 2006)   | B-LVDS and M-LDVS are new I/O standards added to the datasheet.                                                                                                                         | N/A              |

|                                | The term flow-through was changed to pass-through.                                                                                                                                      | N/A              |

|                                | Figure 2-8 • Very-Long-Line Resources was updated.                                                                                                                                      | 2-8              |

|                                | The footnotes in Figure 2-27 • CCC/PLL Macro were updated.                                                                                                                              | 2-28             |

|                                | The Delay Increments in the Programmable Delay Blocks specification in Figure 2-24 • ProASIC3E CCC Options.                                                                             | 2-24             |

|                                | The "SRAM and FIFO" section was updated.                                                                                                                                                | 2-21             |

| The "RES                       | The "RESET" section was updated.                                                                                                                                                        | 2-25             |

|                                | The "WCLK and RCLK" section was updated.                                                                                                                                                | 2-25             |

|                                | The "RESET" section was updated.                                                                                                                                                        | 2-25             |

|                                | The "RESET" section was updated.                                                                                                                                                        | 2-27             |

|                                | B-LVDS and M-LDVS are new I/O standards added to the datasheet.                                                                                                                         | N/A              |

|                                | The term flow-through was changed to pass-through.                                                                                                                                      | N/A              |

|                                | Figure 2-8 • Very-Long-Line Resources was updated.                                                                                                                                      | 2-8              |

|                                | The footnotes in Figure 2-27 • CCC/PLL Macro were updated.                                                                                                                              | 2-28             |

|                                | The Delay Increments in the Programmable Delay Blocks specification in Figure 2-24 • ProASIC3E CCC Options.                                                                             | 2-24             |

|                                | The "SRAM and FIFO" section was updated.                                                                                                                                                | 2-21             |

|                                | The "RESET" section was updated.                                                                                                                                                        | 2-25             |

|                                | The "WCLK and RCLK" section was updated.                                                                                                                                                | 2-25             |

5-8 Revision 15

### **Datasheet Categories**

### **Categories**

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3E Device Status" table on page II, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

#### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

#### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

### **Preliminary**

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

#### **Production**

This version contains information that is considered to be final.

### **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at *Microsemi SoC Reliability Report*. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.

5-12 Revision 15