# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                    |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 147                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 208-BFQFP                                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe1500-1pq208 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# static Microsemi.

ProASIC3E Flash Family FPGAs

# I/Os Per Package<sup>1</sup>

| ProASIC3E Devices              | Devices A3PE600 A3PE1500 <sup>3</sup> |                        | 1500 <sup>3</sup>             | A3PE3000 <sup>3</sup>  |                               |                        |

|--------------------------------|---------------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|

| Cortex-M1 Devices <sup>2</sup> |                                       | M1A3PE1500 M1A3PE300   |                               |                        |                               | PE3000                 |

|                                |                                       | I/O Types              |                               |                        |                               |                        |

| Package                        | Single-Ended I/O <sup>1</sup>         | Differential I/O Pairs | Single-Ended I/O <sup>1</sup> | Differential I/O Pairs | Single-Ended I/O <sup>1</sup> | Differential I/O Pairs |

| PQ208                          | 147                                   | 65                     | 147                           | 65                     | 147                           | 65                     |

| FG256                          | 165                                   | 79                     | -                             | -                      | -                             | -                      |

| FG324                          | -                                     | -                      | -                             | -                      | 221                           | 110                    |

| FG484                          | 270                                   | 135                    | 280                           | 139                    | 341                           | 168                    |

| FG676                          | -                                     | -                      | 444                           | 222                    | _                             | -                      |

| FG896                          | -                                     | -                      | -                             | -                      | 620                           | 310                    |

Notes:

1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3E FPGA Fabric User's Guide to ensure compliance with design and board migration requirements.

- 2. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

- 3. For A3PE1500 and A3PE3000 devices, the usage of certain I/O standards is limited as follows:

- SSTL3(I) and (II): up to 40 I/Os per north or south bank

- LVPECL / GTL+ 3.3 V / GTL 3.3 V: up to 48 I/Os per north or south bank

- SSTL2(I) and (II) / GTL+ 2.5 V/ GTL 2.5 V: up to 72 I/Os per north or south bank

- 4. FG256 and FG484 are footprint-compatible packages.

- 5. When using voltage-referenced I/O standards, one I/O pin should be assigned as a voltage-referenced pin (VREF) per minibank (group of I/Os).

- 6. "G" indicates RoHS-compliant packages. Refer to the "ProASIC3E Ordering Information" on page III for the location of the "G" in the part number.

| Package                         | PQ208   | FG256   | FG324   | FG484   | FG676   | FG896   |

|---------------------------------|---------|---------|---------|---------|---------|---------|

| Length × Width (mm\mm)          | 28 × 28 | 17 × 17 | 19 × 19 | 23 × 23 | 27 × 27 | 31 × 31 |

| Nominal Area (mm <sup>2</sup> ) | 784     | 289     | 361     | 529     | 729     | 961     |

| Pitch (mm)                      | 0.5     | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     |

| Height (mm)                     | 3.40    | 1.60    | 1.63    | 2.23    | 2.23    | 2.23    |

### Table 1-2 • ProASIC3E FPGAs Package Sizes Dimensions

# **ProASIC3E** Device Status

| ProASIC3E Devices | Status     | M1 ProASIC3E Devices | Status     |

|-------------------|------------|----------------------|------------|

| A3PE600           | Production |                      |            |

| A3PE1500          | Production | M1A3PE1500           | Production |

| A3PE3000          | Production | M1A3PE3000           | Production |

| om file Save to file. |                       |            | 🗍 Show BSR D            |

|-----------------------|-----------------------|------------|-------------------------|

| Port Name             | Macro Cell            | Pin Number | 1/O State (Output Only) |

| BIST                  | ADLIB:INBUF           | T2         | 1                       |

| BYPASS_IO             | ADLIB:INBUF           | K1         | 1                       |

| CLK                   | ADLIB:INBUF           | B1         | 1                       |

| ENOUT                 | ADLIB:INBUF           | J16        | 1                       |

| LED                   | ADLIB:OUTBUF          | M3         | 0                       |

| MONITOR[0]            | ADLIB:OUTBUF          | B5         | 0                       |

| MONITOR[1]            | ADLIB:OUTBUF          | C7         | Z                       |

| MONITOR[2]            | ADLIB:OUTBUF          | D9         | Z                       |

| MONITOR[3]            | ADLIB:OUTBUF          | D7         | Z                       |

| MONITOR[4]            | ADLIB:OUTBUF          | A11        | Z                       |

| OEa                   | ADLIB:INBUF           | E4         | Z                       |

| ОЕЬ                   | ADLIB:INBUF           | F1         | Z                       |

| OSC_EN                | ADLIB:INBUF           | K3         | Z                       |

| PAD[10]               | ADLIB:BIBUF_LVCMOS33U | M8         | Z                       |

| PAD[11]               | ADLIB:BIBUF_LVCMOS33D | R7         | Z                       |

| PAD[12]               | ADLIB:BIBUF_LVCMOS33U | D11        | Z                       |

| PAD[13]               | ADLIB:BIBUF_LVCMOS33D | C12        | Z                       |

| PAD[14]               | ADLIB:BIBUF_LVCMOS33U | R6         | Z                       |

|                       |                       |            |                         |

### *Figure 1-3* • I/O States During Programming Window

- 6. Click OK to return to the FlashPoint Programming File Generator window.

- I/O States during programming are saved to the ADB and resulting programming files after completing programming file generation.

| VCCI and VMV  | Average VCCI–GND Overshoot or<br>Undershoot Duration<br>as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                                 | 1.4 V                                         |

| ľ             | 5%                                                                                                  | 1.49 V                                        |

| 3 V           | 10%                                                                                                 | 1.1 V                                         |

| F             | 5%                                                                                                  | 1.19 V                                        |

| 3.3 V         | 10%                                                                                                 | 0.79 V                                        |

| -             | 5%                                                                                                  | 0.88 V                                        |

| 3.6 V         | 10%                                                                                                 | 0.45 V                                        |

| F             | 5%                                                                                                  | 0.54 V                                        |

#### Table 2-4 • Overshoot and Undershoot Limits <sup>1</sup>

Notes:

1. Based on reliability requirements at 85°C.

2. The duration is allowed at one out of six clock cycles. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

3. This table does not provide PCI overshoot/undershoot limits.

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every ProASIC<sup>®</sup>3E device. These circuits ensure easy transition from the powered-off state to the powered-up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 2-1 on page 2-4.

There are five regions to consider during power-up.

ProASIC3E I/Os are activated only if ALL of the following three conditions are met:

1. VCC and VCCI are above the minimum specified trip points (Figure 2-1 on page 2-4).

- 2. VCCI > VCC 0.75 V (typical)

- 3. Chip is in the operating mode.

#### VCCI Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.2 V Ramping down: 0.5 V < trip\_point\_down < 1.1 V

#### VCC Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

ProASIC3E DC and Switching Characteristics

# Table 2-9 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings (continued) (continued)<sup>1</sup>

|                    | C <sub>LOAD</sub><br>(pF) | VCCI<br>(V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------|---------------------------|-------------|----------------------------------------|----------------------------------------------|

| SSTL3 (I)          | 30                        | 3.3         | 26.02                                  | 114.87                                       |

| SSTL3 (II)         | 30                        | 3.3         | 42.21                                  | 131.76                                       |

| Differential       | •                         |             |                                        |                                              |

| LVDS/B-LVDS/M-LVDS | -                         | 2.5         | 7.70                                   | 89.62                                        |

| LVPECL             | -                         | 3.3         | 19.42                                  | 168.02                                       |

| Notes:             | •                         |             | 1                                      | 1                                            |

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. PDC3 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

### **Power Consumption of Various Internal Resources**

Table 2-10 • Different Components Contributing to the Dynamic Power Consumption in ProASIC3E Devices

|           |                                                                | Device-Specific Dynamic Contributions<br>(µW/MHz) |          |          |  |

|-----------|----------------------------------------------------------------|---------------------------------------------------|----------|----------|--|

| Parameter | Definition                                                     | A3PE600                                           | A3PE1500 | A3PE3000 |  |

| PAC1      | Clock contribution of a Global Rib                             | 12.77 16.21 19.                                   |          |          |  |

| PAC2      | Clock contribution of a Global Spine                           | 1.85 3.06 4.10                                    |          |          |  |

| PAC3      | Clock contribution of a VersaTile row                          |                                                   | 0.88     |          |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  |                                                   | 0.12     |          |  |

| PAC5      | First contribution of a VersaTile used as a sequential module  | 0.07                                              |          |          |  |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.29                                              |          |          |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     | 0.29                                              |          |          |  |

| PAC8      | Average contribution of a routing net                          | 0.70                                              |          |          |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          | See Table 2-8 on page 2-6.                        |          |          |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         | See Table 2-9 on page 2-7                         |          |          |  |

| PAC11     | Average contribution of a RAM block during a read operation    | 25.00                                             |          |          |  |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00                                             |          |          |  |

| PAC13     | Static PLL contribution                                        | 2.55 mW                                           |          |          |  |

| PAC14     | Dynamic contribution for PLL                                   | 2.60                                              |          |          |  |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power calculator or SmartPower in Libero SoC.

| Com              | Commercial <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | strial <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IIL <sup>3</sup> | IIH <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                    | IIL <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IIH <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| μA               | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                  | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  | IIL <sup>3</sup> μA           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10 | IIL <sup>3</sup> IIH <sup>4</sup> $\mu$ A $\mu$ A           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10 | IIL <sup>3</sup> IIH <sup>4</sup> IIL <sup>3</sup> $\mu A$ $\mu A$ $\mu A$ 10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10 |

| Table 2-14 • Summary of Maximum and Minimum DC Input Levels |

|-------------------------------------------------------------|

| Applicable to Commercial and Industrial Conditions          |

Notes:

1. Commercial range (0°C <  $T_A$  < 70°C) 2. Industrial range (-40°C <  $T_A$  < 85°C)

3. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

| Table 2-19 • I/O Output Buffer Maximum Resistances <sup>1</sup> (c | continued) |  |

|--------------------------------------------------------------------|------------|--|

|--------------------------------------------------------------------|------------|--|

| Standard   | Drive Strength     | R <sub>PULL-DOWN</sub> (Ω) <sup>2</sup> | $R_{PULL-UP}(\Omega)^3$ |

|------------|--------------------|-----------------------------------------|-------------------------|

| 3.3 V GTL+ | 35 mA              | 12                                      | -                       |

| 2.5 V GTL+ | 33 mA              | 15                                      | -                       |

| HSTL (I)   | 8 mA               | 50                                      | 50                      |

| HSTL (II)  | 15 mA <sup>4</sup> | 25                                      | 25                      |

| SSTL2 (I)  | 15 mA              | 27                                      | 31                      |

| SSTL2 (II) | 18 mA              | 13                                      | 15                      |

| SSTL3 (I)  | 14 mA              | 44                                      | 69                      |

| SSTL3 (II) | 21 mA              | 18                                      | 32                      |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website at www.microsemi.com/index.php?option=com\_content&id=1671&lang=en&view=article.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / IOLspec

- 3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax VOHspec) / IOHspec

- 4. Output drive strength is below JEDEC specification.

### Table 2-20 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|                            |      | CPULL-UP) <sup>1</sup><br>(Ω) | R <sub>(WEAK PULL-DOWN)</sub> <sup>2</sup><br>(Ω) |       |  |  |  |

|----------------------------|------|-------------------------------|---------------------------------------------------|-------|--|--|--|

| VCCI                       | Min. | Max.                          | Min.                                              | Max.  |  |  |  |

| 3.3 V                      | 10 k | 45 k                          | 10 k                                              | 45 k  |  |  |  |

| 3.3 V (Wide<br>Range I/Os) | 10 k | 45 k                          | 10 k                                              | 45 k  |  |  |  |

| 2.5 V                      | 11 k | 55 k                          | 12 k                                              | 74 k  |  |  |  |

| 1.8 V                      | 18 k | 70 k                          | 17 k                                              | 110 k |  |  |  |

| 1.5 V                      | 19 k | 90 k                          | 19 k                                              | 140 k |  |  |  |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R(WEAK PULL-DOWN-MAX) = (VOLspec) / I(WEAK PULL-DOWN-MIN)

# static Microsemi.

ProASIC3E DC and Switching Characteristics

### **Single-Ended I/O Characteristics**

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. The 3.3 V LVCMOS standard is supported as part of the 3.3 V LVTTL support.

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | ΊL        | v          | н         | VOL       | vон       | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.,<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 12  | 12 | 109                     | 103                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 16  | 16 | 127                     | 132                     | 10               | 10               |

| 24 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 24  | 24 | 181                     | 268                     | 10               | 10               |

### Table 2-25 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V< VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

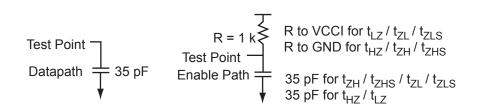

### Figure 2-6 • AC Loading

#### Table 2-26 • 3.3 V LVTTL / 3.3 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | -               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

| Table 2-32 • 3.3 V LVCMOS Wide Range Low Slew                                                        |

|------------------------------------------------------------------------------------------------------|

| Commercial-Case Conditions: T <sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V |

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade |      | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zhs</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 4 mA                                                                          | Std.           | 0.66 | 17.02           | 0.04             | 1.83            | 2.38             | 0.43              | 17.02           | 13.74           | 4.16            | 3.78            | 20.42            | 17.14            | ns    |

|                   |                                                                               | -1             | 0.56 | 14.48           | 0.04             | 1.55            | 2.02             | 0.36              | 14.48           | 11.69           | 3.54            | 3.21            | 17.37            | 14.58            | ns    |

|                   |                                                                               | -2             | 0.49 | 12.71           | 0.03             | 1.36            | 1.78             | 0.32              | 12.71           | 10.26           | 3.11            | 2.82            | 15.25            | 12.80            | ns    |

| 100 µA            | 8 mA                                                                          | Std.           | 0.66 | 12.16           | 0.04             | 1.83            | 2.38             | 0.43              | 12.16           | 9.78            | 4.70            | 4.74            | 15.55            | 13.17            | ns    |

|                   |                                                                               | -1             | 0.56 | 10.34           | 0.04             | 1.55            | 2.02             | 0.36              | 10.34           | 8.32            | 4.00            | 4.03            | 13.23            | 11.20            | ns    |

|                   |                                                                               | -2             | 0.49 | 9.08            | 0.03             | 1.36            | 1.78             | 0.32              | 9.08            | 7.30            | 3.51            | 3.54            | 11.61            | 9.84             | ns    |

| 100µA             | 12 mA                                                                         | Std.           | 0.66 | 9.32            | 0.04             | 1.83            | 2.38             | 0.43              | 9.32            | 7.62            | 5.06            | 5.36            | 12.71            | 11.02            | ns    |

|                   |                                                                               | -1             | 0.56 | 7.93            | 0.04             | 1.55            | 2.02             | 0.36              | 7.93            | 6.48            | 4.31            | 4.56            | 10.81            | 9.37             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.96            | 0.03             | 1.36            | 1.78             | 0.32              | 6.96            | 5.69            | 3.78            | 4.00            | 9.49             | 8.23             | ns    |

| 100 µA            | 16 mA                                                                         | Std.           | 0.66 | 8.69            | 0.04             | 1.83            | 2.38             | 0.43              | 8.69            | 7.17            | 5.14            | 5.53            | 12.08            | 10.57            | ns    |

|                   |                                                                               | -1             | 0.56 | 7.39            | 0.04             | 1.55            | 2.02             | 0.36              | 7.39            | 6.10            | 4.37            | 4.71            | 10.28            | 8.99             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.49            | 0.03             | 1.36            | 1.78             | 0.32              | 6.49            | 5.36            | 3.83            | 4.13            | 9.02             | 7.89             | ns    |

| 100 µA            | 24 mA                                                                         | Std.           | 0.66 | 8.11            | 0.04             | 1.83            | 2.38             | 0.43              | 8.11            | 7.13            | 5.23            | 6.13            | 11.50            | 10.52            | ns    |

|                   |                                                                               | -1             | 0.56 | 6.90            | 0.04             | 1.55            | 2.02             | 0.36              | 6.90            | 6.06            | 4.45            | 5.21            | 9.78             | 8.95             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.05            | 0.03             | 1.36            | 1.78             | 0.32              | 6.05            | 5.32            | 3.91            | 4.57            | 8.59             | 7.86             | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

Software default extension birblighted in grave

2. Software default selection highlighted in gray.

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

ProASIC3E DC and Switching Characteristics

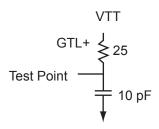

### 2.5 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-57 • Minimum and Maximum DC Input and Output Levels

| 2.5 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 33 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 33  | 33 | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

### Figure 2-15 • AC Loading

Table 2-58 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                     | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-59 • 2.5 V GTL+

```

Commercial-Case Conditions: T_J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.0 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|