Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 276480                                                                       |

| Number of I/O                  | 444                                                                          |

| Number of Gates                | 1500000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 676-BGA                                                                      |

| Supplier Device Package        | 676-FBGA (27x27)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe1500-2fg676i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – ProASIC3E Device Family Overview

## **General Description**

ProASIC3E, the third-generation family of Microsemi flash FPGAs, offers performance, density, and features beyond those of the ProASIC<sup>PLUS®</sup> family. Nonvolatile flash technology gives ProASIC3E devices the advantage of being a secure, low power, single-chip solution that is Instant On. ProASIC3E is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

ProASIC3E devices offer 1 kbit of on-chip, programmable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on six integrated phase-locked loops (PLLs). ProASIC3E devices have up to three million system gates, supported with up to 504 kbits of true dual-port SRAM and up to 620 user I/Os.

Several ProASIC3E devices support the Cortex-M1 soft IP cores, and the ARM-Enabled devices have Microsemi ordering numbers that begin with M1A3PE.

## **Flash Advantages**

### Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAMbased FPGAs, flash-based ProASIC3E devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property (IP) cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The ProASIC3E family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the ProASIC3E family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/ communications, computing, and avionics markets.

#### Security

The nonvolatile, flash-based ProASIC3E devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. ProASIC3E devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

ProASIC3E devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of protection in the FPGA industry for programmed intellectual property and configuration data. In addition, all FlashROM data in ProASIC3E devices can be encrypted prior to loading, using the industryleading AES-128 (FIPS192) bit block cipher encryption standard. The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. ProASIC3E devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. ProASIC3E devices with AES-based security provide a high level of protection for secure, remote field updates over public networks such as the Internet, and ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of the ProASIC3E family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The ProASIC3E family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3E device provides the best available security for programmable logic designs.

ProASIC3E DC and Switching Characteristics

## PLL Behavior at Brownout Condition

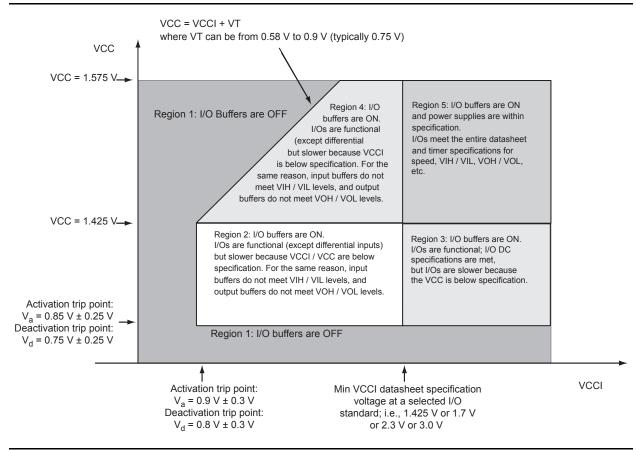

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper power-up behavior. Power ramp-up should be monotonic at least until VCC and VCCPLXL exceed brownout activation levels. The VCC activation level is specified as 1.1 V worst-case (see Figure 2-1 on page 2-4 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels ( $0.75 V \pm 0.25 V$ ), the PLL output lock signal goes low and/or the output clock is lost. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" chapter of the *ProASIC3E FPGA Fabric User's Guide* for information on clock and lock recovery.

### Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

Figure 2-1 • I/O State as a Function of VCCI and VCC Voltage Levels

|                    | VMV<br>(V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|--------------------|------------|----------------------------------------|---------------------------------------------|

| HSTL (I)           | 1.5        | 0.17                                   | 2.03                                        |

| HSTL (II)          | 1.5        | 0.17                                   | 2.03                                        |

| SSTL2 (I)          | 2.5        | 1.38                                   | 4.48                                        |

| SSTL2 (II)         | 2.5        | 1.38                                   | 4.48                                        |

| SSTL3 (I)          | 3.3        | 3.21                                   | 9.26                                        |

| SSTL3 (II)         | 3.3        | 3.21                                   | 9.26                                        |

| Differential       |            | •                                      | -                                           |

| LVDS/B-LVDS/M-LVDS | 2.5        | 2.26                                   | 1.50                                        |

| LVPECL             | 3.3        | 5.71                                   | 2.17                                        |

#### Table 2-8 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings (continued)

Notes:

1. PDC2 is the static power (where applicable) measured on VMV.

2. PAC9 is the total dynamic power measured on VCC and VMV.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8b specification.

#### Table 2-9 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>

|                                            | C <sub>LOAD</sub><br>(pF) | VCCI<br>(V) | Static Power<br>PDC3 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |

|--------------------------------------------|---------------------------|-------------|----------------------------------------|----------------------------------------------|

| Single-Ended                               | •                         |             |                                        |                                              |

| 3.3 V LVTTL/LVCMOS                         | 35                        | 3.3         | -                                      | 474.70                                       |

| 3.3 V LVTTL/LVCMOS Wide Range <sup>4</sup> | 35                        | 3.3         | -                                      | 474.70                                       |

| 2.5 V LVCMOS                               | 35                        | 2.5         | -                                      | 270.73                                       |

| 1.8 V LVCMOS                               | 35                        | 1.8         | -                                      | 151.78                                       |

| 1.5 V LVCMOS (JESD8-11)                    | 35                        | 1.5         | -                                      | 104.55                                       |

| 3.3 V PCI                                  | 10                        | 3.3         | -                                      | 204.61                                       |

| 3.3 V PCI-X                                | 10                        | 3.3         | -                                      | 204.61                                       |

| Voltage-Referenced                         |                           |             |                                        |                                              |

| 3.3 V GTL                                  | 10                        | 3.3         | -                                      | 24.08                                        |

| 2.5 V GTL                                  | 10                        | 2.5         | -                                      | 13.52                                        |

| 3.3 V GTL+                                 | 10                        | 3.3         | -                                      | 24.10                                        |

| 2.5 V GTL+                                 | 10                        | 2.5         | -                                      | 13.54                                        |

| HSTL (I)                                   | 20                        | 1.5         | 7.08                                   | 26.22                                        |

| HSTL (II)                                  | 20                        | 1.5         | 13.88                                  | 27.22                                        |

| SSTL2 (I)                                  | 30                        | 2.5         | 16.69                                  | 105.56                                       |

| SSTL2 (II)                                 | 30                        | 2.5         | 25.91                                  | 116.60                                       |

Notes:

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. PDC3 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

ProASIC3E DC and Switching Characteristics

#### Combinatorial Cells Contribution—P<sub>C-CELL</sub>

$P_{C-CELL} = N_{C-CELL} * \alpha_1 / 2 * PAC7 * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_{1}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-11 on page 2-11.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

### Routing Net Contribution—P<sub>NET</sub>

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * \alpha_1 / 2 * PAC8 * F_{CLK}$

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

$N_{C\text{-}CELL}$  is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-11 on page 2-11.

F<sub>CLK</sub> is the global clock signal frequency.

#### I/O Input Buffer Contribution—PINPUTS

$P_{INPUTS} = N_{INPUTS} * \alpha_2 / 2 * PAC9 * F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-11 on page 2-11.

$F_{CLK}$  is the global clock signal frequency.

#### I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * PAC10 * F_{CLK}$

$N_{\mbox{OUTPUTS}}$  is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-11 on page 2-11.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-12 on page 2-11.

F<sub>CLK</sub> is the global clock signal frequency.

#### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{PAC11} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ-CLOCK}} * \beta_2 + \mathsf{PAC12} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE-CLOCK}} * \beta_3$

$N_{\mbox{\scriptsize BLOCKS}}$  is the number of RAM blocks used in the design.

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations—guidelines are provided in Table 2-12 on page 2-11.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-12 on page 2-11.

## PLL Contribution—P<sub>PLL</sub>

P<sub>PLL</sub> = PAC13 + PAC14 \* F<sub>CLKOUT</sub>

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (PAC14 \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

| Table 2-19 • I/O Output Buffer Maximum Resistances <sup>1</sup> (c | continued) |  |

|--------------------------------------------------------------------|------------|--|

|--------------------------------------------------------------------|------------|--|

| Standard   | Drive Strength     | R <sub>PULL-DOWN</sub> (Ω) <sup>2</sup> | $R_{PULL-UP}(\Omega)^3$ |

|------------|--------------------|-----------------------------------------|-------------------------|

| 3.3 V GTL+ | 35 mA              | 12                                      | -                       |

| 2.5 V GTL+ | 33 mA              | 15                                      | -                       |

| HSTL (I)   | 8 mA               | 50                                      | 50                      |

| HSTL (II)  | 15 mA <sup>4</sup> | 25                                      | 25                      |

| SSTL2 (I)  | 15 mA              | 27                                      | 31                      |

| SSTL2 (II) | 18 mA              | 13                                      | 15                      |

| SSTL3 (I)  | 14 mA              | 44                                      | 69                      |

| SSTL3 (II) | 21 mA              | 18                                      | 32                      |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website at www.microsemi.com/index.php?option=com\_content&id=1671&lang=en&view=article.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / IOLspec

- 3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax VOHspec) / IOHspec

- 4. Output drive strength is below JEDEC specification.

#### Table 2-20 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|                            |      | CPULL-UP) <sup>1</sup><br>(Ω) | ${\sf R}_{({\sf WEAK PULL-DOWN})}^2$ ( $\Omega$ ) |       |  |  |

|----------------------------|------|-------------------------------|---------------------------------------------------|-------|--|--|

| VCCI                       | Min. | Max.                          | Min.                                              | Max.  |  |  |

| 3.3 V                      | 10 k | 45 k                          | 10 k                                              | 45 k  |  |  |

| 3.3 V (Wide<br>Range I/Os) | 10 k | 45 k                          | 10 k                                              | 45 k  |  |  |

| 2.5 V                      | 11 k | 55 k                          | 12 k                                              | 74 k  |  |  |

| 1.8 V                      | 18 k | 70 k                          | 17 k                                              | 110 k |  |  |

| 1.5 V                      | 19 k | 90 k                          | 19 k                                              | 140 k |  |  |

Notes:

1. R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>(WEAK PULL-UP-MIN)</sub>

2. R(WEAK PULL-DOWN-MAX) = (VOLspec) / I(WEAK PULL-DOWN-MIN)

## 3.3 V LVCMOS Wide Range

| 3.3 V<br>LVCMOS<br>Wide<br>Range | Equivalent<br>Software<br>Default<br>Drive | v         | IL        | v         | н         | VOL       | VOH       | IOL | юн  | IOSL                    | IOSH                    | IIL <sup>2</sup> | IIH <sup>3</sup> |

|----------------------------------|--------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength                | Strength<br>Option <sup>1</sup>            | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | μA  | μA  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                           | 2 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 4 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 6 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 8 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 12 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 109                     | 103                     | 10               | 10               |

| 100 µA                           | 16 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 127                     | 132                     | 10               | 10               |

| 100 µA                           | 24 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 181                     | 268                     | 10               | 10               |

#### Table 2-29 • Minimum and Maximum DC Input and Output Levels

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

4. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

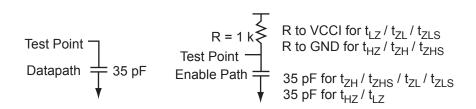

#### Figure 2-7 • AC Loading

#### Table 2-30 • 3.3 V LVCMOS Wide Range AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | _               | 35                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

| Table 2-32 • 3.3 V LVCMOS Wide Range Low Slew                                                        |

|------------------------------------------------------------------------------------------------------|

| Commercial-Case Conditions: T <sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V |

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade |      | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zhs</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 4 mA                                                                          | Std.           | 0.66 | 17.02           | 0.04             | 1.83            | 2.38             | 0.43              | 17.02           | 13.74           | 4.16            | 3.78            | 20.42            | 17.14            | ns    |

|                   |                                                                               | -1             | 0.56 | 14.48           | 0.04             | 1.55            | 2.02             | 0.36              | 14.48           | 11.69           | 3.54            | 3.21            | 17.37            | 14.58            | ns    |

|                   |                                                                               | -2             | 0.49 | 12.71           | 0.03             | 1.36            | 1.78             | 0.32              | 12.71           | 10.26           | 3.11            | 2.82            | 15.25            | 12.80            | ns    |

| 100 µA            | 8 mA                                                                          | Std.           | 0.66 | 12.16           | 0.04             | 1.83            | 2.38             | 0.43              | 12.16           | 9.78            | 4.70            | 4.74            | 15.55            | 13.17            | ns    |

|                   |                                                                               | -1             | 0.56 | 10.34           | 0.04             | 1.55            | 2.02             | 0.36              | 10.34           | 8.32            | 4.00            | 4.03            | 13.23            | 11.20            | ns    |

|                   |                                                                               | -2             | 0.49 | 9.08            | 0.03             | 1.36            | 1.78             | 0.32              | 9.08            | 7.30            | 3.51            | 3.54            | 11.61            | 9.84             | ns    |

| 100µA             | 12 mA                                                                         | Std.           | 0.66 | 9.32            | 0.04             | 1.83            | 2.38             | 0.43              | 9.32            | 7.62            | 5.06            | 5.36            | 12.71            | 11.02            | ns    |

|                   |                                                                               | -1             | 0.56 | 7.93            | 0.04             | 1.55            | 2.02             | 0.36              | 7.93            | 6.48            | 4.31            | 4.56            | 10.81            | 9.37             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.96            | 0.03             | 1.36            | 1.78             | 0.32              | 6.96            | 5.69            | 3.78            | 4.00            | 9.49             | 8.23             | ns    |

| 100 µA            | 16 mA                                                                         | Std.           | 0.66 | 8.69            | 0.04             | 1.83            | 2.38             | 0.43              | 8.69            | 7.17            | 5.14            | 5.53            | 12.08            | 10.57            | ns    |

|                   |                                                                               | -1             | 0.56 | 7.39            | 0.04             | 1.55            | 2.02             | 0.36              | 7.39            | 6.10            | 4.37            | 4.71            | 10.28            | 8.99             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.49            | 0.03             | 1.36            | 1.78             | 0.32              | 6.49            | 5.36            | 3.83            | 4.13            | 9.02             | 7.89             | ns    |

| 100 µA            | 24 mA                                                                         | Std.           | 0.66 | 8.11            | 0.04             | 1.83            | 2.38             | 0.43              | 8.11            | 7.13            | 5.23            | 6.13            | 11.50            | 10.52            | ns    |

|                   |                                                                               | -1             | 0.56 | 6.90            | 0.04             | 1.55            | 2.02             | 0.36              | 6.90            | 6.06            | 4.45            | 5.21            | 9.78             | 8.95             | ns    |

|                   |                                                                               | -2             | 0.49 | 6.05            | 0.03             | 1.36            | 1.78             | 0.32              | 6.05            | 5.32            | 3.91            | 4.57            | 8.59             | 7.86             | ns    |

Notes:

The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

Software default extension birblighted in grave

2. Software default selection highlighted in gray.

ProASIC3E DC and Switching Characteristics

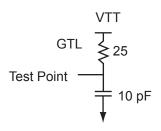

## 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-51 • Minimum and Maximum DC Input and Output Levels

| 2.5 GTL            | VIL        |             | VIH         |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL | IIH |

|--------------------|------------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength  | Min.,<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 20 mA <sup>3</sup> | -0.3       | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20  | 20  | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

#### Figure 2-13 • AC Loading

#### Table 2-52 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-53 • 2.5 V GTL

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.13            | 0.04             | 2.46            | 0.43              | 2.16            | 2.13            |                 |                 | 4.40             | 4.36             | ns    |

| -1             | 0.51              | 1.81            | 0.04             | 2.09            | 0.36              | 1.84            | 1.81            |                 |                 | 3.74             | 3.71             | ns    |

| -2             | 0.45              | 1.59            | 0.03             | 1.83            | 0.32              | 1.61            | 1.59            |                 |                 | 3.28             | 3.26             | ns    |

ProASIC3E DC and Switching Characteristics

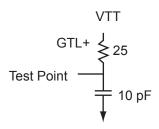

### 2.5 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-57 • Minimum and Maximum DC Input and Output Levels

| 2.5 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 33 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | _         | 33  | 33 | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

#### Figure 2-15 • AC Loading

Table 2-58 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                     | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-59 • 2.5 V GTL+

```

Commercial-Case Conditions: T_J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.0 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.21            | 0.04             | 1.51            | 0.43              | 2.25            | 2.10            |                 |                 | 4.48             | 4.34             | ns    |

| –1             | 0.51              | 1.88            | 0.04             | 1.29            | 0.36              | 1.91            | 1.79            |                 |                 | 3.81             | 3.69             | ns    |

| -2             | 0.45              | 1.65            | 0.03             | 1.13            | 0.32              | 1.68            | 1.57            |                 |                 | 3.35             | 3.24             | ns    |

## static Microsemi.

ProASIC3E DC and Switching Characteristics

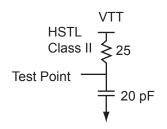

### HSTL Class II

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). ProASIC3E devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

| HSTL Class II      | VIL       |            | VIH        |           | VOL        | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|--------------------|-----------|------------|------------|-----------|------------|------------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength  | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.,<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 15 mA <sup>3</sup> | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4        | VCCI – 0.4 | 15  | 15 | 55                      | 66                      | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

#### Figure 2-17 • AC Loading

Table 2-64 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                    | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### Timing Characteristics

Table 2-65 • HSTL Class II

Commercial-Case Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V, VREF = 0.75 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 3.02            | 0.04             | 2.12            | 0.43              | 3.08            | 2.71            |                 |                 | 5.32             | 4.95             | ns    |

| -1             | 0.56              | 2.57            | 0.04             | 1.81            | 0.36              | 2.62            | 2.31            |                 |                 | 4.52             | 4.21             | ns    |

| -2             | 0.49              | 2.26            | 0.03             | 1.59            | 0.32              | 2.30            | 2.03            |                 |                 | 3.97             | 3.70             | ns    |

ProASIC3E DC and Switching Characteristics

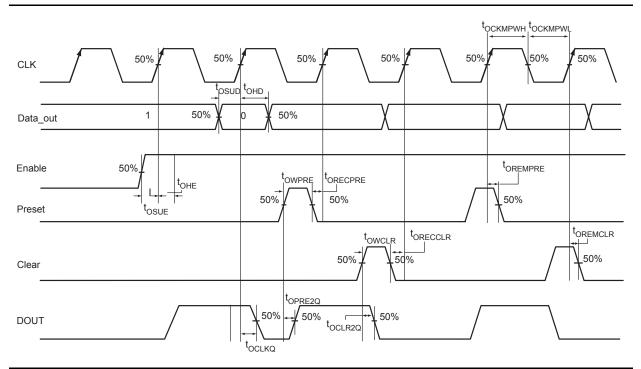

## **Output Register**

#### **Timing Characteristics**

Table 2-87 • Output Data Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -2   | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.59 | 0.67 | 0.79 | ns    |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                         | 0.31 | 0.36 | 0.42 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.44 | 0.50 | 0.59 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.37 | 0.43 | ns    |

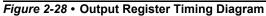

#### Figure 2-31 • Input DDR Timing Diagram

#### Timing Characteristics

# Table 2-90 • Input DDR Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                          | -2   | -1   | Std. | Units |

|-------------------------|------------------------------------------------------|------|------|------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.39 | 0.44 | 0.52 | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.27 | 0.31 | 0.37 | ns    |

| t <sub>DDRISUD</sub>    | Data Setup for Input DDR                             | 0.28 | 0.32 | 0.38 | ns    |

| t <sub>DDRIHD</sub>     | Data Hold for Input DDR                              | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear to Out Out_QR for Input DDR       | 0.57 | 0.65 | 0.76 | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 0.46 | 0.53 | 0.62 | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.32 | 0.37 | 0.43 | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 1404 | 1232 | 1048 | MHz   |

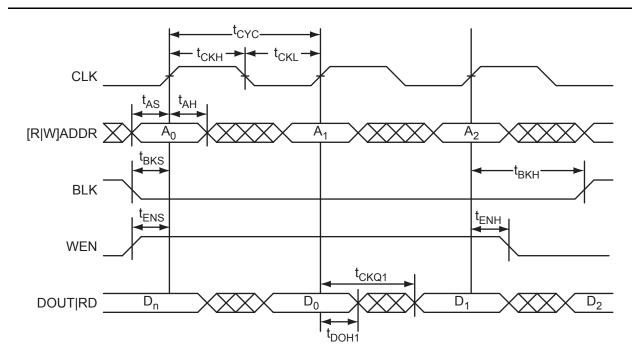

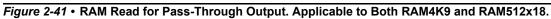

## Timing Waveforms

Figure 2-42 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

ProASIC3E DC and Switching Characteristics

## **Timing Characteristics**

### Table 2-99 • RAM4K9

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -2   | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.14 | 0.16 | 0.19 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 0.23 | 0.27 | 0.31 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 1.79 | 2.03 | 2.39 | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Closing Edge        | 0.33 | 0.28 | 0.25 | ns    |

| t <sub>C2CWWH</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Rising Edge         | 0.30 | 0.26 | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.45 | 0.38 | 0.34 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.49 | 0.42 | 0.37 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DO (flow-through)                                                                      | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to Data Out Low on DO (pipelined)                                                                         | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

# 3 – Pin Descriptions and Packaging

## **Supply Pins**

#### GND

#### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ

#### Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

#### **Core Supply Voltage**

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

#### VCCIBx

#### I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to eight I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. In general, unused I/O banks should have their corresponding VCCIX pins tied to GND. If an output pad is terminated to ground through any resistor and if the corresponding VCCIX is left floating, then the leakage current to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 3 uA. For unused banks the aforementioned behavior is to be taken into account while deciding if it's better to float VCCIX of unused bank or tie it to GND.

#### VMVx

#### I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

#### VCCPLA/B/C/D/E/F

#### PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *ProASIC3E FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There are six VCCPLX pins on ProASIC3E devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There are six VCOMPL pins (PLL ground) on ProASIC3E devices.

Package Pin Assignments

|            | PQ208             |            | PQ208             |            | PQ208             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| 1          | GND               | 40         | VCCIB6            | 79         | IO194NDB5V0       |

| 2          | GNDQ              | 41         | GND               | 80         | IO194PDB5V0       |

| 3          | VMV7              | 42         | IO244PDB6V1       | 81         | GND               |

| 4          | GAB2/IO308PSB7V4  | 43         | IO244NDB6V1       | 82         | IO184NDB4V3       |

| 5          | GAA2/IO309PDB7V4  | 44         | GEC1/IO236PDB6V0  | 83         | IO184PDB4V3       |

| 6          | IO309NDB7V4       | 45         | GEC0/IO236NDB6V0  | 84         | IO180NDB4V3       |

| 7          | GAC2/IO307PDB7V4  | 46         | GEB1/IO235PPB6V0  | 85         | IO180PDB4V3       |

| 8          | IO307NDB7V4       | 47         | GEA1/IO234PPB6V0  | 86         | IO176NDB4V2       |

| 9          | IO303PDB7V3       | 48         | GEB0/IO235NPB6V0  | 87         | IO176PDB4V2       |

| 10         | IO303NDB7V3       | 49         | GEA0/IO234NPB6V0  | 88         | VCC               |

| 11         | IO299PDB7V3       | 50         | VMV6              | 89         | VCCIB4            |

| 12         | IO299NDB7V3       | 51         | GNDQ              | 90         | IO170NDB4V2       |

| 13         | IO295PDB7V2       | 52         | GND               | 91         | IO170PDB4V2       |

| 14         | IO295NDB7V2       | 53         | VMV5              | 92         | IO166NDB4V1       |

| 15         | IO291PSB7V2       | 54         | GNDQ              | 93         | IO166PDB4V1       |

| 16         | VCC               | 55         | IO233NDB5V4       | 94         | IO156NDB4V0       |

| 17         | GND               | 56         | GEA2/IO233PDB5V4  | 95         | GDC2/IO156PDB4V0  |

| 18         | VCCIB7            | 57         | IO232NDB5V4       | 96         | IO154NPB4V0       |

| 19         | IO285PDB7V1       | 58         | GEB2/IO232PDB5V4  | 97         | GND               |

| 20         | IO285NDB7V1       | 59         | IO231NDB5V4       | 98         | GDB2/IO155PSB4V0  |

| 21         | IO279PSB7V0       | 60         | GEC2/IO231PDB5V4  | 99         | GDA2/IO154PPB4V0  |

| 22         | GFC1/IO275PSB7V0  | 61         | IO230PSB5V4       | 100        | GNDQ              |

| 23         | GFB1/IO274PDB7V0  | 62         | VCCIB5            | 101        | ТСК               |

| 24         | GFB0/IO274NDB7V0  | 63         | IO218NDB5V3       | 102        | TDI               |

| 25         | VCOMPLF           | 64         | IO218PDB5V3       | 103        | TMS               |

| 26         | GFA0/IO273NPB6V4  | 65         | GND               | 104        | VMV4              |

| 27         | VCCPLF            | 66         | IO214PSB5V2       | 105        | GND               |

| 28         | GFA1/IO273PPB6V4  | 67         | IO212NDB5V2       | 106        | VPUMP             |

| 29         | GND               | 68         | IO212PDB5V2       | 107        | GNDQ              |

| 30         | GFA2/IO272PDB6V4  | 69         | IO208NDB5V1       | 108        | TDO               |

| 31         | IO272NDB6V4       | 70         | IO208PDB5V1       | 109        | TRST              |

| 32         | GFB2/IO271PPB6V4  | 71         | VCC               | 110        | VJTAG             |

| 33         | GFC2/IO270PPB6V4  | 72         | VCCIB5            | 111        | VMV3              |

| 34         | IO271NPB6V4       | 73         | IO202NDB5V1       | 112        | GDA0/IO153NPB3V4  |

| 35         | IO270NPB6V4       | 74         | IO202PDB5V1       | 113        | GDB0/IO152NPB3V4  |

| 36         | VCC               | 75         | IO198NDB5V0       | 114        | GDA1/IO153PPB3V4  |

| 37         | IO252PDB6V2       | 76         | IO198PDB5V0       | 115        | GDB1/IO152PPB3V4  |

| 38         | IO252NDB6V2       | 77         | IO197NDB5V0       | 116        | GDC0/IO151NDB3V4  |

| 39         | IO248PSB6V1       | 78         | IO197PDB5V0       | 117        | GDC1/IO151PDB3V4  |

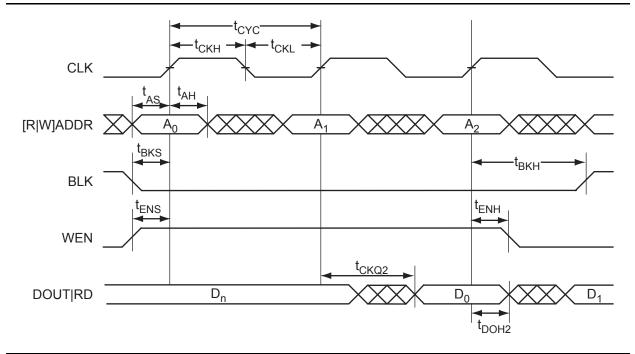

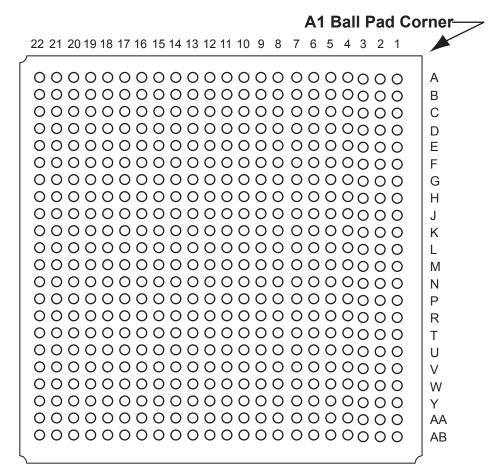

## FG256

*Note:* This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

## FG484

Note: This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

| FG896      |                   | FG896      |                   | FG896      |                   |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| AG9        | IO225NPB5V3       | AH15       | IO195NDB5V0       | AJ21       | IO173PDB4V2       |

| AG10       | IO223NPB5V3       | AH16       | IO185NDB4V3       | AJ22       | IO163NDB4V1       |

| AG11       | IO221PDB5V3       | AH17       | IO185PDB4V3       | AJ23       | IO163PDB4V1       |

| AG12       | IO221NDB5V3       | AH18       | IO181PDB4V3       | AJ24       | IO167NPB4V1       |

| AG13       | IO205NPB5V1       | AH19       | IO177NDB4V2       | AJ25       | VCC               |

| AG14       | IO199NDB5V0       | AH20       | IO171NPB4V2       | AJ26       | IO156NPB4V0       |

| AG15       | IO199PDB5V0       | AH21       | IO165PPB4V1       | AJ27       | VCC               |

| AG16       | IO187NDB4V4       | AH22       | IO161PPB4V0       | AJ28       | TMS               |

| AG17       | IO187PDB4V4       | AH23       | IO157NDB4V0       | AJ29       | GND               |

| AG18       | IO181NDB4V3       | AH24       | IO157PDB4V0       | AJ30       | GND               |

| AG19       | IO171PPB4V2       | AH25       | IO155NDB4V0       | AK2        | GND               |

| AG20       | IO165NPB4V1       | AH26       | VCCIB4            | AK3        | GND               |

| AG21       | IO161NPB4V0       | AH27       | TDI               | AK4        | IO217PPB5V2       |

| AG22       | IO159NDB4V0       | AH28       | VCC               | AK5        | GND               |

| AG23       | IO159PDB4V0       | AH29       | VPUMP             | AK6        | IO215PPB5V2       |

| AG24       | IO158PPB4V0       | AH30       | GND               | AK7        | GND               |

| AG25       | GDB2/IO155PDB4V0  | AJ1        | GND               | AK8        | IO207NDB5V1       |

| AG26       | GDA2/IO154PPB4V0  | AJ2        | GND               | AK9        | IO207PDB5V1       |

| AG27       | GND               | AJ3        | GEA2/IO233PPB5V4  | AK10       | IO201NDB5V0       |

| AG28       | VJTAG             | AJ4        | VCC               | AK11       | IO201PDB5V0       |

| AG29       | VCC               | AJ5        | IO217NPB5V2       | AK12       | IO193NDB4V4       |

| AG30       | IO149NDB3V4       | AJ6        | VCC               | AK13       | IO193PDB4V4       |

| AH1        | GND               | AJ7        | IO215NPB5V2       | AK14       | IO197PDB5V0       |

| AH2        | IO233NPB5V4       | AJ8        | IO213NDB5V2       | AK15       | IO191NDB4V4       |

| AH3        | VCC               | AJ9        | IO213PDB5V2       | AK16       | IO191PDB4V4       |

| AH4        | GEB2/IO232PPB5V4  | AJ10       | IO209NDB5V1       | AK17       | IO189NDB4V4       |

| AH5        | VCCIB5            | AJ11       | IO209PDB5V1       | AK18       | IO189PDB4V4       |

| AH6        | IO219NDB5V3       | AJ12       | IO203NDB5V1       | AK19       | IO179PPB4V3       |

| AH7        | IO219PDB5V3       | AJ13       | IO203PDB5V1       | AK20       | IO175NDB4V2       |

| AH8        | IO227NDB5V4       | AJ14       | IO197NDB5V0       | AK21       | IO175PDB4V2       |

| AH9        | IO227PDB5V4       | AJ15       | IO195PDB5V0       | AK22       | IO169NDB4V1       |

| AH10       | IO225PPB5V3       | AJ16       | IO183NDB4V3       | AK23       | IO169PDB4V1       |

| AH11       | IO223PPB5V3       | AJ17       | IO183PDB4V3       | AK24       | GND               |

| AH12       | IO211NDB5V2       | AJ18       | IO179NPB4V3       | AK25       | IO167PPB4V1       |

| AH13       | IO211PDB5V2       | AJ19       | IO177PDB4V2       | AK26       | GND               |

| AH14       | IO205PPB5V1       | AJ20       | IO173NDB4V2       | AK27       | GDC2/IO156PPB4V0  |

Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| Revision 10<br>(continued) | "TBD" for 3.3 V LVCMOS Wide Range in Table 2-19 • I/O Output Buffer Maximum Resistances <sup>1</sup> and Table 2-21 • I/O Short Currents IOSH/IOSL was replaced by "Same as regular 3.3 V LVCMOS" (SAR 33853).                                                                                                                                                                                                                             |      |  |  |

|                            | 3.3 V LVCMOS Wide Range information was separated from regular 3.3 V LVCMOS and placed into its own new section, "3.3 V LVCMOS Wide Range". Values of IOSH and IOSL were added in Table 2-29 • Minimum and Maximum DC Input and Output Levels (SAR 33853).                                                                                                                                                                                 |      |  |  |

|                            | The formulas in the table notes for Table 2-20 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 34755).                                                                                                                                                                                                                                                                                                                        |      |  |  |

|                            | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34889).                                                                                                                                                                                                                                  |      |  |  |

|                            | The titles and subtitles for Table 2-31 • 3.3 V LVCMOS Wide Range High Slew and Table 2-32 • 3.3 V LVCMOS Wide Range Low Slew were corrected (SAR 37227).                                                                                                                                                                                                                                                                                  |      |  |  |

|                            | The following notes were removed from Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels (SAR 34812): ±5%                                                                                                                                                                                                                                                                                                                    |      |  |  |

|                            | Differential input voltage = ±350 mV                                                                                                                                                                                                                                                                                                                                                                                                       |      |  |  |

|                            | Minimum pulse width High and Low values were added to the tables in the "Global Tree Timing Characteristics" section. The maximum frequency for global clock parameter was removed from these tables because a frequency on the global is only an indication of what the global network can do. There are other limiters such as the SRAM, I/Os, and PLL. SmartTime software should be used to determine the design frequency (SAR 36957). |      |  |  |

|                            | A note was added to Table 2-98 • ProASIC3E CCC/PLL Specification indicating that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 34824).                                                                                                                                                                                                |      |  |  |

|                            | The following figures were deleted. Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 34872). Figure 2-44 • Write Access after Write onto Same Address                                                                                                                                                   |      |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |  |  |

|                            | Figure 2-45 • Read Access after Write onto Same Address                                                                                                                                                                                                                                                                                                                                                                                    |      |  |  |

|                            | Figure 2-46 • Write Access after Read onto Same Address                                                                                                                                                                                                                                                                                                                                                                                    |      |  |  |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-49 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SAR 35750).                                                                                                                                                                                                        |      |  |  |

|                            | The "Pin Descriptions and Packaging" chapter is new (SAR 34771).                                                                                                                                                                                                                                                                                                                                                                           | 3-1  |  |  |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 34771).                                                                                                                                                                                                                                                                                       |      |  |  |

|                            | Pin E6 for the FG256 package was corrected from VvB0 to VCCIB0 (SARs 30364, 31597, 26243).                                                                                                                                                                                                                                                                                                                                                 | 4-9  |  |  |

| July 2010                  | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "ProASIC3E Device Status" table on page II indicates the status for each device in the device family.                                                                                                                                                                             | N/A  |  |  |