Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E-XF

| Details                        |                                                                               |

|--------------------------------|-------------------------------------------------------------------------------|

| Product Status                 | Active                                                                        |

| Number of LABs/CLBs            | -                                                                             |

| Number of Logic Elements/Cells | -                                                                             |

| Total RAM Bits                 | 276480                                                                        |

| Number of I/O                  | 444                                                                           |

| Number of Gates                | 1500000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                               |

| Mounting Type                  | Surface Mount                                                                 |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                            |

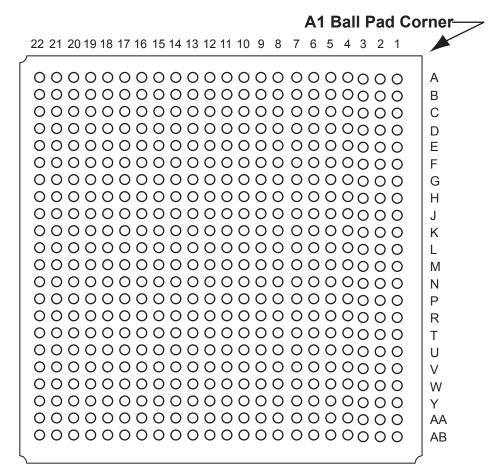

| Package / Case                 | 676-BGA                                                                       |

| Supplier Device Package        | 676-FBGA (27x27)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe1500-2fgg676i |

|                                |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

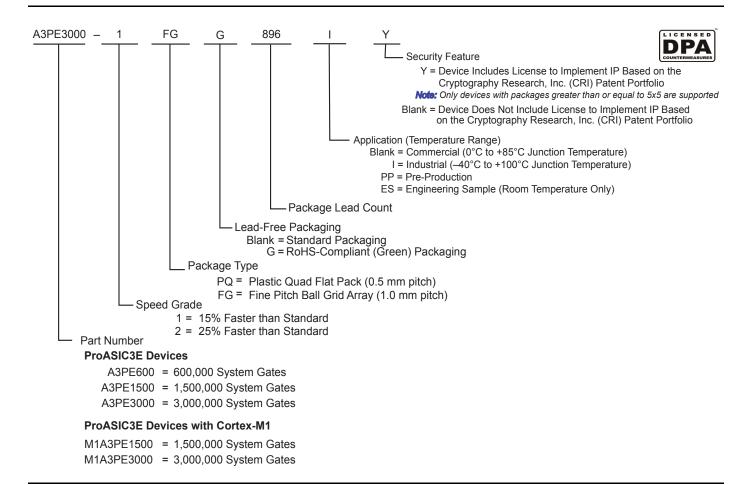

# **ProASIC3E Ordering Information**

## **Microsemi**.

ProASIC3E DC and Switching Characteristics

| Symbol                    | Para                                 | meter                         | Commercial     | Industrial     | Units |

|---------------------------|--------------------------------------|-------------------------------|----------------|----------------|-------|

| T <sub>A</sub>            | Ambient temperature                  |                               | 0 to +70       | -40 to +85     | °C    |

| TJ                        | Junction temperature                 |                               | 0 to +85       | -40 to +100    | °C    |

| VCC                       | 1.5 V DC core supply volta           | age                           | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VJTAG                     | JTAG DC voltage                      |                               | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP                     | Programming voltage                  | Programming Mode <sup>2</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                           |                                      | Operation <sup>3</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL                    | Analog power supply (PLL             | _)                            | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCI and VMV <sup>4</sup> | 1.5 V DC supply voltage              |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                           | 1.8 V DC supply voltage              |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                           | 2.5 V DC supply voltage              |                               | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                           | 3.3 V DC supply voltage              |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

|                           | 3.0 V DC supply voltage <sup>5</sup> |                               | 2.7 to 3.6     | 2.7 to 3.6     | V     |

|                           | LVDS/B-LVDS/M-LVDS dif               | fferential I/O                | 2.375 to 2.625 | 2.375 to 2.625 | V     |

|                           | LVPECL differential I/O              |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

#### Table 2-2 • Recommended Operating Conditions<sup>1</sup>

Notes:

1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

2. The programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to  $85^{\circ}C$ .

3. VPUMP can be left floating during normal operation (not programming mode).

- 4. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-13 on page 2-16. VMV and VCCI should be at the same voltage within a given I/O bank. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

- 5. To ensure targeted reliability standards are met across ambient and junction operating temperatures, Microsemi recommends that the user follow best design practices using Microsemi's timing and power simulation tools.

- 6. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

#### Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature<sup>1</sup>

| Product Grade | Programming<br>Cycles | Program Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|---------------|-----------------------|----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|

| Commercial    | 500                   | 20 years                               | 110                                                               | 100                                                                        |

| Industrial    | 500                   | 20 years                               | 110                                                               | 100                                                                        |

Notes:

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

ProASIC3E DC and Switching Characteristics

## PLL Behavior at Brownout Condition

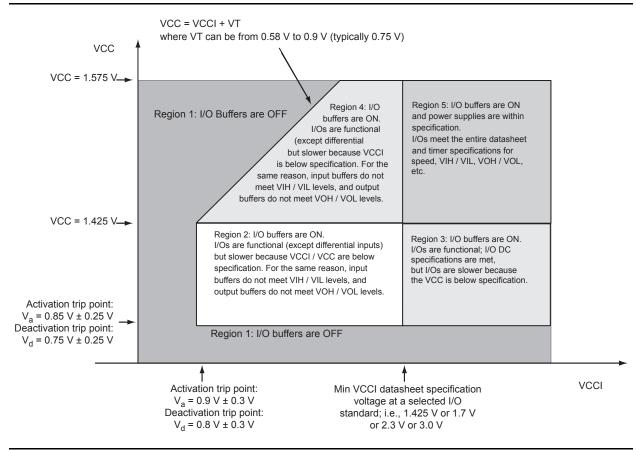

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper power-up behavior. Power ramp-up should be monotonic at least until VCC and VCCPLXL exceed brownout activation levels. The VCC activation level is specified as 1.1 V worst-case (see Figure 2-1 on page 2-4 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels ( $0.75 V \pm 0.25 V$ ), the PLL output lock signal goes low and/or the output clock is lost. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" chapter of the *ProASIC3E FPGA Fabric User's Guide* for information on clock and lock recovery.

### Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

Figure 2-1 • I/O State as a Function of VCCI and VCC Voltage Levels

## Power Calculation Methodology

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-11 on page 2-11.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-12 on page 2-11.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-12 on page 2-11. The calculation should be repeated for each clock domain defined in the design.

## Methodology

#### Total Power Consumption—PTOTAL

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

P<sub>STAT</sub> = PDC1 + N<sub>INPUTS</sub> \* PDC2 + N<sub>OUTPUTS</sub> \* PDC3

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub>

## Global Clock Contribution—P<sub>CLOCK</sub>

P<sub>CLOCK</sub> = (PAC1 + N<sub>SPINE</sub> \* PAC2 + N<sub>ROW</sub> \* PAC3 + N<sub>S-CELL</sub> \* PAC4) \* F<sub>CLK</sub>

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3E FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3E FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

PAC1, PAC2, PAC3, and PAC4 are device-dependent.

### Sequential Cells Contribution—P<sub>S-CELL</sub>

$P_{S-CELL}$  =  $N_{S-CELL}$  \* (PAC5 +  $\alpha_1$  / 2 \* PAC6) \*  $F_{CLK}$

$N_{S\text{-}CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-11 on page 2-11.

F<sub>CLK</sub> is the global clock signal frequency.

| Com              | mercial <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                | Industrial <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IIL <sup>3</sup> | IIH <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                    | IIL <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IIH <sup>4</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| μA               | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                  | μΑ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 10               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                  | IIL <sup>3</sup> μA           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10           10 | $\mu$ A $\mu$ A           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10           10         10 | IIL <sup>3</sup> IIH <sup>4</sup> IIL <sup>3</sup> $\mu A$ $\mu A$ $\mu A$ 10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10         15           10         10 |  |

| Table 2-14 • Summary of Maximum and Minimum DC Input Levels |

|-------------------------------------------------------------|

| Applicable to Commercial and Industrial Conditions          |

Notes:

1. Commercial range (0°C <  $T_A$  < 70°C) 2. Industrial range (-40°C <  $T_A$  < 85°C)

3. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

## 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 12.00           | 0.04             | 1.51            | 1.66             | 0.43              | 12.23           | 11.61           | 2.72            | 2.20            | 14.46            | 13.85            | ns    |

|                   | -1             | 0.56              | 10.21           | 0.04             | 1.29            | 1.41             | 0.36              | 10.40           | 9.88            | 2.31            | 1.87            | 12.30            | 11.78            | ns    |

|                   | -2             | 0.49              | 8.96            | 0.03             | 1.13            | 1.24             | 0.32              | 9.13            | 8.67            | 2.03            | 1.64            | 10.80            | 10.34            | ns    |

| 8 mA              | Std.           | 0.66              | 8.73            | 0.04             | 1.51            | 1.66             | 0.43              | 8.89            | 8.01            | 3.10            | 2.93            | 11.13            | 10.25            | ns    |

|                   | -1             | 0.56              | 7.43            | 0.04             | 1.29            | 1.41             | 0.36              | 7.57            | 6.82            | 2.64            | 2.49            | 9.47             | 8.72             | ns    |

|                   | -2             | 0.49              | 6.52            | 0.03             | 1.13            | 1.24             | 0.32              | 6.64            | 5.98            | 2.32            | 2.19            | 8.31             | 7.65             | ns    |

| 12 mA             | Std.           | 0.66              | 6.77            | 0.04             | 1.51            | 1.66             | 0.43              | 6.90            | 6.11            | 3.37            | 3.39            | 9.14             | 8.34             | ns    |

|                   | -1             | 0.56              | 5.76            | 0.04             | 1.29            | 1.41             | 0.36              | 5.87            | 5.20            | 2.86            | 2.89            | 7.77             | 7.10             | ns    |

|                   | -2             | 0.49              | 5.06            | 0.03             | 1.13            | 1.24             | 0.32              | 5.15            | 4.56            | 2.51            | 2.53            | 6.82             | 6.23             | ns    |

| 16 mA             | Std.           | 0.66              | 6.31            | 0.04             | 1.51            | 1.66             | 0.43              | 6.42            | 5.73            | 3.42            | 3.52            | 8.66             | 7.96             | ns    |

|                   | -1             | 0.56              | 5.37            | 0.04             | 1.29            | 1.41             | 0.36              | 5.46            | 4.87            | 2.91            | 3.00            | 7.37             | 6.77             | ns    |

|                   | -2             | 0.49              | 4.71            | 0.03             | 1.13            | 1.24             | 0.32              | 4.80            | 4.28            | 2.56            | 2.63            | 6.47             | 5.95             | ns    |

| 24 mA             | Std.           | 0.66              | 5.93            | 0.04             | 1.51            | 1.66             | 0.43              | 6.04            | 5.70            | 3.49            | 4.00            | 8.28             | 7.94             | ns    |

|                   | -1             | 0.56              | 5.05            | 0.04             | 1.29            | 1.41             | 0.36              | 5.14            | 4.85            | 2.97            | 3.40            | 7.04             | 6.75             | ns    |

|                   | -2             | 0.49              | 4.43            | 0.03             | 1.13            | 1.24             | 0.32              | 4.51            | 4.26            | 2.61            | 2.99            | 6.18             | 5.93             | ns    |

### Table 2-36 • 2.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

## **Voltage-Referenced I/O Characteristics**

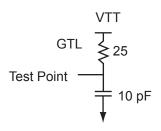

## 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          | VIL       |             | VIH         |           | VIL VIH   |           | VOL | VOH | IOL                     | ЮН                      | IOSL | IOSH | IIL | IIH |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------|------|-----|-----|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA²  | μA²  |     |     |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20  | 20  | 181                     | 268                     | 10   | 10   |     |     |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

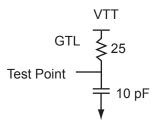

#### Figure 2-12 • AC Loading

#### Table 2-49 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

#### Timing Characteristics

Table 2-50 • 3.3 V GTL

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.08            | 0.04             | 2.93            | 0.43              | 2.04            | 2.08            |                 |                 | 4.27             | 4.31             | ns    |

| -1             | 0.51              | 1.77            | 0.04             | 2.50            | 0.36              | 1.73            | 1.77            |                 |                 | 3.63             | 3.67             | ns    |

| -2             | 0.45              | 1.55            | 0.03             | 2.19            | 0.32              | 1.52            | 1.55            |                 |                 | 3.19             | 3.22             | ns    |

## 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

## 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-51 • Minimum and Maximum DC Input and Output Levels

| 2.5 GTL            |            | VIL         | VIH         |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL | IIH |

|--------------------|------------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength  | Min.,<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 20 mA <sup>3</sup> | -0.3       | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20  | 20  | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

#### Figure 2-13 • AC Loading

#### Table 2-52 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-53 • 2.5 V GTL

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.13            | 0.04             | 2.46            | 0.43              | 2.16            | 2.13            |                 |                 | 4.40             | 4.36             | ns    |

| -1             | 0.51              | 1.81            | 0.04             | 2.09            | 0.36              | 1.84            | 1.81            |                 |                 | 3.74             | 3.71             | ns    |

| -2             | 0.45              | 1.59            | 0.03             | 1.83            | 0.32              | 1.61            | 1.59            |                 |                 | 3.28             | 3.26             | ns    |

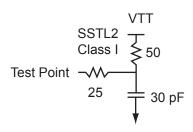

## SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). ProASIC3E devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class I     |           | VIL        | VIH        |           | VOL       | VOH         | IOL | IOH | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|-----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 15 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI – 0.62 | 15  | 15  | 87                      | 83                      | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

#### Figure 2-18 • AC Loading

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                    | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-68 • SSTL 2 Class I

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 2.3 V, VREF = 1.25 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 1.33            | 0.43              | 2.17            | 1.85            |                 |                 | 4.40             | 4.08             | ns    |

| –1             | 0.56              | 1.81            | 0.04             | 1.14            | 0.36              | 1.84            | 1.57            |                 |                 | 3.74             | 3.47             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.00            | 0.32              | 1.62            | 1.38            |                 |                 | 3.29             | 3.05             | ns    |

## **Differential I/O Characteristics**

## Physical Implementation

Configuration of the I/O modules as a differential pair is handled by the Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and DDR. However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

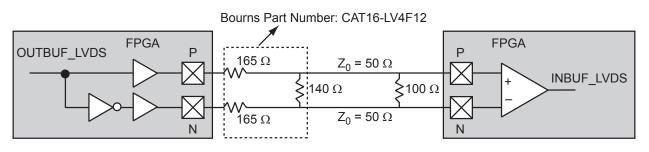

## LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-22. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, ProASIC3E also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-22 • LVDS Circuit Diagram and Board-Level Implementation

# **Microsemi**

ProASIC3E DC and Switching Characteristics

#### Table 2-84 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| tOESUD                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | K, H                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | K, H                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

Note: \*See Figure 2-25 on page 2-53 for more information.

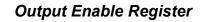

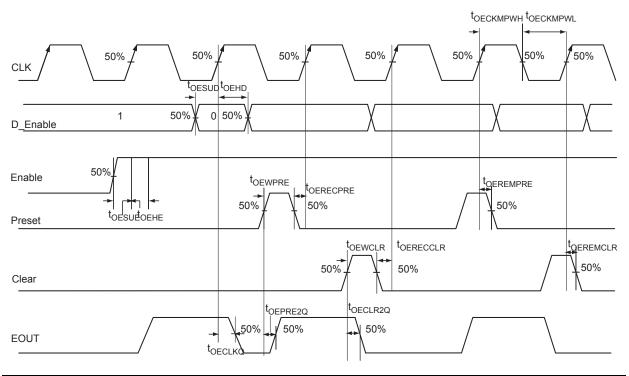

#### Figure 2-29 • Output Enable Register Timing Diagram

#### **Timing Characteristics**

# Table 2-88 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | -2   | -1   | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.59 | 0.67 | 0.79 | ns    |

| tOESUD                | Data Setup Time for the Output Enable Register                         | 0.31 | 0.36 | 0.42 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                       | 0.44 | 0.50 | 0.58 | ns    |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.67 | 0.76 | 0.89 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.67 | 0.76 | 0.89 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OECKMPWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.32 | 0.37 | 0.43 | ns    |

# 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

## Timing Characteristics

#### *Table 2-93* • Combinatorial Cell Propagation Delays Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | -2   | -1   | Std. | Units |

|--------------------|---------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.56 | 0.64 | 0.75 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

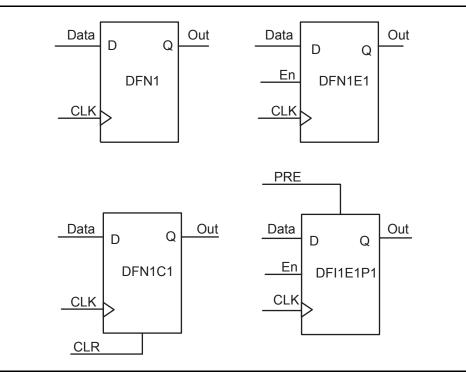

## VersaTile Specifications as a Sequential Module