# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 147                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 208-BFQFP                                                                   |

| Supplier Device Package        | 208-PQFP (28x28)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe1500-pqg208 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

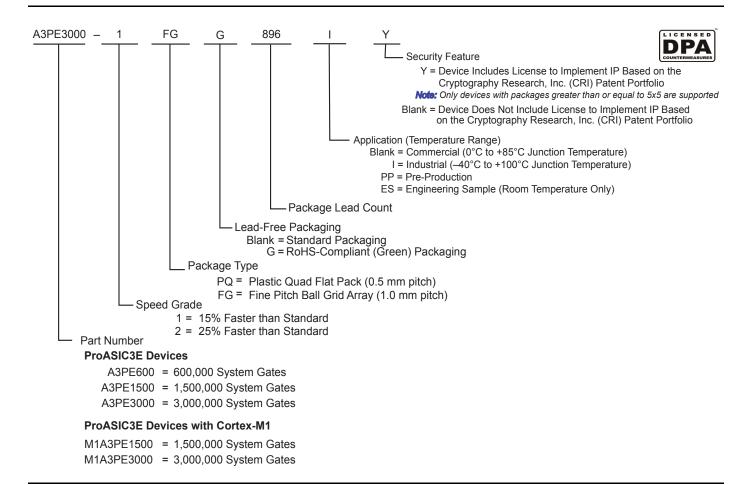

### **ProASIC3E Ordering Information**

ProASIC3E Device Family Overview

### VersaTiles

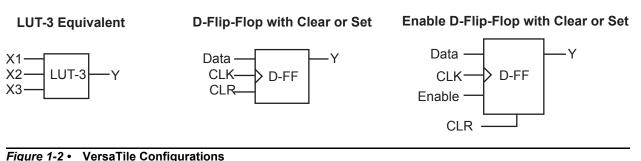

The ProASIC3E core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The ProASIC3E VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-2 for VersaTile configurations.

### User Nonvolatile FlashROM

ProASIC3E devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Internet protocol addressing (wireless or fixed)

- System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- Version management

The FlashROM is written using the standard ProASIC3E IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks, as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The ProASIC3E development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

## 2 – ProASIC3E DC and Switching Characteristics

### **General Specifications**

DC and switching characteristics for –F speed grade targets are based only on simulation.

The characteristics provided for the –F speed grade are subject to change after establishing FPGA specifications. Some restrictions might be added and will be reflected in future revisions of this document. The –F speed grade is only supported in the commercial temperature range.

### **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

| Symbol                        | Parameter                           | Limits                                                                                                                                                                                      | Units |  |  |  |  |

|-------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

| VCC                           | DC core supply voltage              | -0.3 to 1.65                                                                                                                                                                                |       |  |  |  |  |

| VJTAG                         | JTAG DC voltage                     | -0.3 to 3.75                                                                                                                                                                                | V     |  |  |  |  |

| VPUMP                         | Programming voltage                 | -0.3 to 3.75                                                                                                                                                                                | V     |  |  |  |  |

| VCCPLL                        | Analog power supply (PLL)           | -0.3 to 1.65                                                                                                                                                                                | V     |  |  |  |  |

| VCCI <sup>2</sup>             | DC I/O output buffer supply voltage | -0.3 to 3.75                                                                                                                                                                                | V     |  |  |  |  |

| VMV <sup>2</sup>              | DC I/O input buffer supply voltage  | -0.3 to 3.75                                                                                                                                                                                | V     |  |  |  |  |

| VI                            | I/O input voltage                   | <ul> <li>-0.3 V to 3.6 V (when I/O hot insertion mode is enabled)</li> <li>-0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is disabled)</li> </ul> | V     |  |  |  |  |

| T <sub>STG</sub> <sup>3</sup> | Storage temperature                 | -65 to +150                                                                                                                                                                                 | °C    |  |  |  |  |

| T <sub>J</sub> <sup>3</sup>   | Junction temperature                | +125                                                                                                                                                                                        | °C    |  |  |  |  |

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-3 on page 2-2.

VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

3. For flash programming and retention maximum limits, refer to Table 2-3 on page 2-2, and for recommended operating limits, refer to Table 2-2 on page 2-2.

### **Microsemi**.

ProASIC3E DC and Switching Characteristics

| Symbol                    | Para                                 | meter                         | Commercial     | Industrial     | Units |

|---------------------------|--------------------------------------|-------------------------------|----------------|----------------|-------|

| T <sub>A</sub>            | Ambient temperature                  |                               | 0 to +70       | -40 to +85     | °C    |

| TJ                        | Junction temperature                 |                               | 0 to +85       | -40 to +100    | °C    |

| VCC                       | 1.5 V DC core supply volta           | age                           | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VJTAG                     | JTAG DC voltage                      |                               | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP                     | Programming voltage                  | Programming Mode <sup>2</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                           |                                      | Operation <sup>3</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL                    | Analog power supply (PLL             | _)                            | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCI and VMV <sup>4</sup> | 1.5 V DC supply voltage              |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                           | 1.8 V DC supply voltage              |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                           | 2.5 V DC supply voltage              |                               | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                           | 3.3 V DC supply voltage              |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

|                           | 3.0 V DC supply voltage <sup>5</sup> |                               | 2.7 to 3.6     | 2.7 to 3.6     | V     |

|                           | LVDS/B-LVDS/M-LVDS dif               | fferential I/O                | 2.375 to 2.625 | 2.375 to 2.625 | V     |

|                           | LVPECL differential I/O              |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

#### Table 2-2 • Recommended Operating Conditions<sup>1</sup>

Notes:

1. All parameters representing voltages are measured with respect to GND unless otherwise specified.

2. The programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to  $85^{\circ}C$ .

3. VPUMP can be left floating during normal operation (not programming mode).

- 4. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-13 on page 2-16. VMV and VCCI should be at the same voltage within a given I/O bank. VMV pins must be connected to the corresponding VCCI pins. See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further information.

- 5. To ensure targeted reliability standards are met across ambient and junction operating temperatures, Microsemi recommends that the user follow best design practices using Microsemi's timing and power simulation tools.

- 6. 3.3 V wide range is compliant to the JESD8-B specification and supports 3.0 V VCCI operation.

#### Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature<sup>1</sup>

| Product Grade | Programming<br>Cycles | Program Retention<br>(biased/unbiased) | Maximum Storage<br>Temperature T <sub>STG</sub> (°C) <sup>2</sup> | Maximum Operating Junction<br>Temperature T <sub>J</sub> (°C) <sup>2</sup> |

|---------------|-----------------------|----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------|

| Commercial    | 500                   | 20 years                               | 110                                                               | 100                                                                        |

| Industrial    | 500                   | 20 years                               | 110                                                               | 100                                                                        |

Notes:

1. This is a stress rating only; functional operation at any condition other than those indicated is not implied.

2. These limits apply for program/data retention only. Refer to Table 2-1 on page 2-1 and Table 2-2 for device operating conditions and absolute limits.

### 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

### Table 2-9 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings (continued) (continued)<sup>1</sup>

|                    | C <sub>LOAD</sub><br>(pF) |     |       | Dynamic Power<br>PAC10 (µW/MHz) <sup>3</sup> |  |

|--------------------|---------------------------|-----|-------|----------------------------------------------|--|

| SSTL3 (I)          | 30                        | 3.3 | 26.02 | 114.87                                       |  |

| SSTL3 (II)         | 30                        | 3.3 | 42.21 | 131.76                                       |  |

| Differential       | •                         |     |       |                                              |  |

| LVDS/B-LVDS/M-LVDS | -                         | 2.5 | 7.70  | 89.62                                        |  |

| LVPECL             | -                         | 3.3 | 19.42 | 168.02                                       |  |

| Notes:             | •                         |     | 1     | 1                                            |  |

1. Dynamic power consumption is given for standard load and software default drive strength and output slew.

2. PDC3 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

4. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8-B specification.

### **Power Consumption of Various Internal Resources**

Table 2-10 • Different Components Contributing to the Dynamic Power Consumption in ProASIC3E Devices

|           |                                                                     | Device-Specific Dynamic Contributions<br>(µW/MHz) |                  |          |  |  |  |

|-----------|---------------------------------------------------------------------|---------------------------------------------------|------------------|----------|--|--|--|

| Parameter | Definition                                                          | A3PE600                                           | A3PE1500         | A3PE3000 |  |  |  |

| PAC1      | Clock contribution of a Global Rib                                  | 12.77                                             | 16.21            | 19.7     |  |  |  |

| PAC2      | Clock contribution of a Global Spine                                | 1.85                                              | 3.06             | 4.16     |  |  |  |

| PAC3      | Clock contribution of a VersaTile row                               |                                                   | 0.88             |          |  |  |  |

| PAC4      | Clock contribution of a VersaTile used as a sequential module       | 0.12                                              |                  |          |  |  |  |

| PAC5      | First contribution of a VersaTile used as a sequential module       | as a sequential 0.07                              |                  |          |  |  |  |

| PAC6      | Second contribution of a VersaTile used as a sequential 0.29 module |                                                   |                  |          |  |  |  |

| PAC7      | Contribution of a VersaTile used as a combinatorial module          | 0.29                                              |                  |          |  |  |  |

| PAC8      | Average contribution of a routing net                               |                                                   | 0.70             |          |  |  |  |

| PAC9      | Contribution of an I/O input pin (standard-dependent)               | See 7                                             | Table 2-8 on pag | ge 2-6.  |  |  |  |

| PAC10     | Contribution of an I/O output pin (standard-dependent)              | See                                               | Table 2-9 on pag | ge 2-7   |  |  |  |

| PAC11     | Average contribution of a RAM block during a read operation         |                                                   | 25.00            |          |  |  |  |

| PAC12     | Average contribution of a RAM block during a write operation        |                                                   | 30.00            |          |  |  |  |

| PAC13     | Static PLL contribution                                             |                                                   | 2.55 mW          |          |  |  |  |

| PAC14     | Dynamic contribution for PLL                                        |                                                   | 2.60             |          |  |  |  |

Note: For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power calculator or SmartPower in Libero SoC.

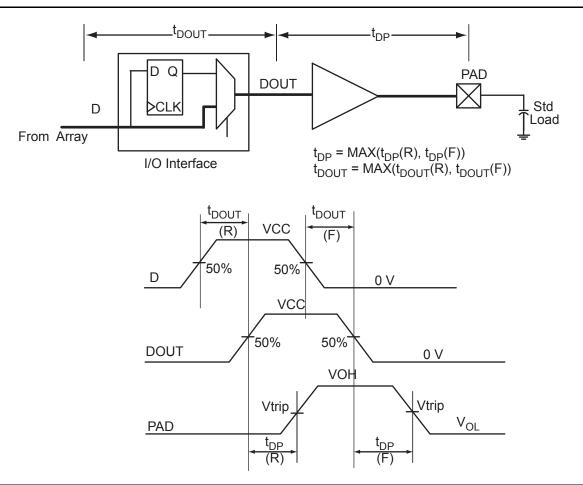

Figure 2-4 • Output Buffer Model and Delays (example)

### **Detailed I/O DC Characteristics**

#### Table 2-18 • Input Capacitance

| Symbol          | Definition                         | Conditions           | Min. | Max. | Units |

|-----------------|------------------------------------|----------------------|------|------|-------|

| C <sub>IN</sub> | Input capacitance                  | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

| CINCLK          | Input capacitance on the clock pin | VIN = 0, f = 1.0 MHz |      | 8    | pF    |

### Table 2-19 • I/O Output Buffer Maximum Resistances<sup>1</sup>

| Standard                   | Drive Strength              | R <sub>PULL-DOWN</sub> (Ω) <sup>2</sup> | R <sub>PULL-UP</sub> (Ω) <sup>3</sup> |

|----------------------------|-----------------------------|-----------------------------------------|---------------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 4 mA                        | 100                                     | 300                                   |

|                            | 8 mA                        | 50                                      | 150                                   |

|                            | 12 mA                       | 25                                      | 75                                    |

|                            | 16 mA                       | 17                                      | 50                                    |

|                            | 24 mA                       | 11                                      | 33                                    |

| 3.3 V LVCMOS Wide Range    | 100 µA                      | Same as regular<br>3.3 V LVCMOS         | Same as regular<br>3.3 V LVCMOS       |

| 2.5 V LVCMOS               | 4 mA                        | 100                                     | 200                                   |

| Ī                          | 8 mA                        | 50                                      | 100                                   |

| T                          | 12 mA                       | 25                                      | 50                                    |

|                            | 16 mA                       | 20                                      | 40                                    |

| Ī                          | 24 mA                       | 11                                      | 22                                    |

| 1.8 V LVCMOS               | 2 mA                        | 200                                     | 225                                   |

|                            | 4 mA                        | 100                                     | 112                                   |

|                            | 6 mA                        | 50                                      | 56                                    |

|                            | 8 mA                        | 50                                      | 56                                    |

|                            | 12 mA                       | 20                                      | 22                                    |

|                            | 16 mA                       | 20                                      | 22                                    |

| 1.5 V LVCMOS               | 2 mA                        | 200                                     | 224                                   |

|                            | 4 mA                        | 100                                     | 112                                   |

|                            | 6 mA                        | 67                                      | 75                                    |

|                            | 8 mA                        | 33                                      | 37                                    |

|                            | 12 mA                       | 33                                      | 37                                    |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 25                                      | 75                                    |

| 3.3 V GTL                  | 20 mA <sup>4</sup>          | 11                                      | _                                     |

| 2.5 V GTL                  | 20 mA <sup>4</sup>          | 14                                      | _                                     |

Notes:

- These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCCI, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website at www.microsemi.com/index.php?option=com\_content&id=1671&lang=en&view=article.

- 2. R<sub>(PULL-DOWN-MAX)</sub> = (VOLspec) / IOLspec

- 3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax VOHspec) / IOHspec

- 4. Output drive strength is below JEDEC specification.

### 3.3 V LVCMOS Wide Range

| 3.3 V<br>LVCMOS<br>Wide<br>Range | Equivalent<br>Software<br>Default<br>Drive | v         | IL        | v         | н         | VOL       | VOH       | IOL | юн  | IOSL                    | IOSH                    | IIL <sup>2</sup> | IIH <sup>3</sup> |

|----------------------------------|--------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength                | Strength<br>Option <sup>1</sup>            | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | μA  | μA  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                           | 2 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 4 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 6 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 8 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 12 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 109                     | 103                     | 10               | 10               |

| 100 µA                           | 16 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 127                     | 132                     | 10               | 10               |

| 100 µA                           | 24 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 181                     | 268                     | 10               | 10               |

#### Table 2-29 • Minimum and Maximum DC Input and Output Levels

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

4. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

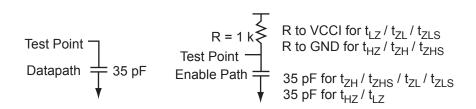

### Figure 2-7 • AC Loading

### Table 2-30 • 3.3 V LVCMOS Wide Range AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | _               | 35                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

### 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

### 2.5 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-57 • Minimum and Maximum DC Input and Output Levels

| 2.5 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 33 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 33  | 33 | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

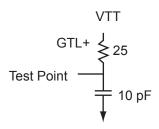

### Figure 2-15 • AC Loading

Table 2-58 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                     | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-59 • 2.5 V GTL+

```

Commercial-Case Conditions: T_J = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.0 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.21            | 0.04             | 1.51            | 0.43              | 2.25            | 2.10            |                 |                 | 4.48             | 4.34             | ns    |

| –1             | 0.51              | 1.88            | 0.04             | 1.29            | 0.36              | 1.91            | 1.79            |                 |                 | 3.81             | 3.69             | ns    |

| -2             | 0.45              | 1.65            | 0.03             | 1.13            | 0.32              | 1.68            | 1.57            |                 |                 | 3.35             | 3.24             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

### 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

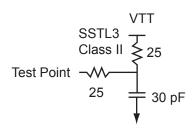

### SSTL3 Class II

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). ProASIC3E devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-75 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class II    |           | VIL        | VIH        |           | VOL       | VOH        | IOL | IOH | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|-----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 21 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.5       | VCCI – 0.9 | 21  | 21  | 109                     | 103                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

### Figure 2-21 • AC Loading

Table 2-76 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.5                     | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-77 • SSTL3 Class II

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 3.0 V, VREF = 1.5 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.07            | 0.04             | 1.25            | 0.43              | 2.10            | 1.67            |                 |                 | 4.34             | 3.91             | ns    |

| -1             | 0.56              | 1.76            | 0.04             | 1.06            | 0.36              | 1.79            | 1.42            |                 |                 | 3.69             | 3.32             | ns    |

| -2             | 0.49              | 1.54            | 0.03             | 0.93            | 0.32              | 1.57            | 1.25            |                 |                 | 3.24             | 2.92             | ns    |

*Note:* For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

**Wicrosemi**. ProASIC3E DC and Switching Characteristics

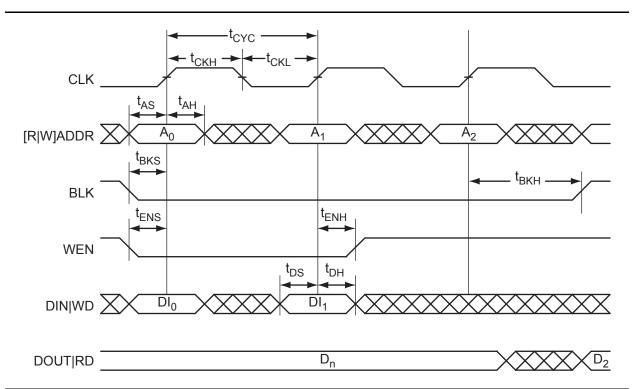

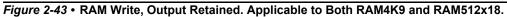

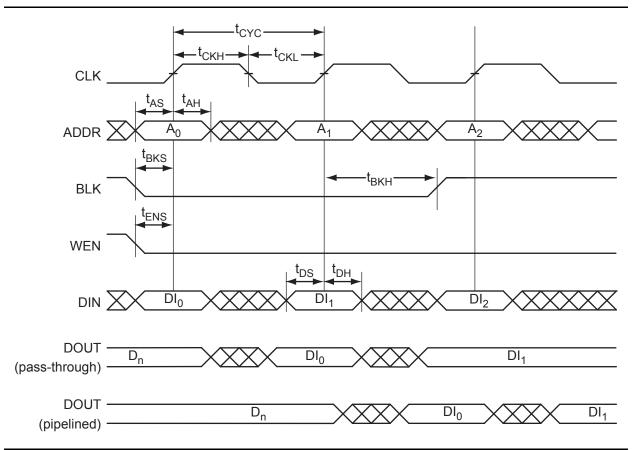

Figure 2-44 • RAM Write, Output as Write Data. Applicable to RAM4K9 Only.

Refer to the I/O Structure section of the *ProASIC3E FPGA Fabric User's Guide* for an explanation of the naming of global pins.

### **JTAG Pins**

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the part must be supplied to allow JTAG signals to transition the device. Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pullup/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500 W to 1 k $\Omega$  will satisfy the requirements. Refer to Table 3-1 for more information.

| VJTAG          | Tie-Off Resistance           |

|----------------|------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                |

#### Table 3-1 • Recommended Tie-Off Values for the TCK and TRST Pins

Notes:

- 1. Equivalent parallel resistance if more than one device is on the JTAG chain

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin is pulled down.

### TDI

TMS

### Test Data Input

**Test Data Output**

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

### TDO

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

### Test Mode Select

The TMS pin controls the use of the IEEE 1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

### TRST Boundary Scan Reset Pin

The TRST pin functions as an active-low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the test access port (TAP) is held in reset mode. The resistor values must be chosen from Table 3-1 and must satisfy the parallel resistance value requirement. The values in Table 3-1 correspond to the resistor recommended when a single device is used, and the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entrance to an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

Pin Descriptions and Packaging

### **Special Function Pins**

### NC

#### **No Connect**

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC

#### Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

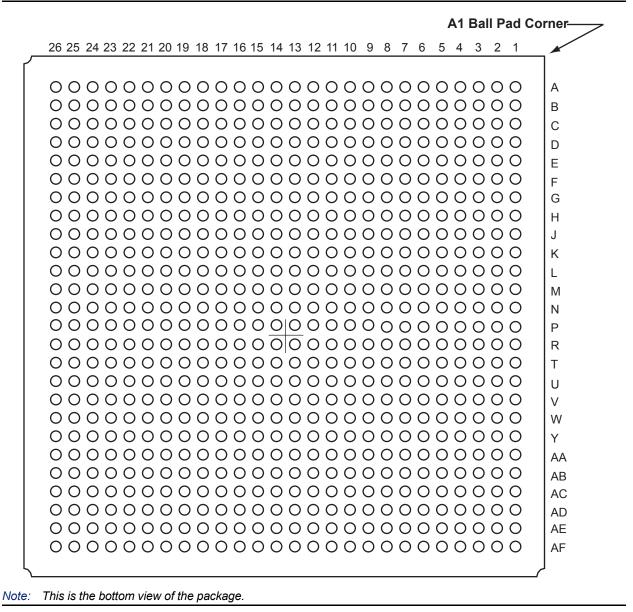

### Packaging

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

### **Related Documents**

### **User's Guides**

ProASIC3E FPGA Fabric User's Guide

http://www.microsemi.com/document-portal/doc\_download/130883-proasic3e-fpga-fabric-user-s-guide

### Packaging

The following documents provide packaging information and device selection for low power flash devices.

### Product Catalog

http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

### Package Mechanical Drawings

http://www.microsemi.com/document-portal/doc\_download/131095-package-mechanical-drawings

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials: http://www.microsemi.com/products/fpga-soc/solutions.

|            | PQ208            |            | PQ208            |            | PQ208            |  |  |

|------------|------------------|------------|------------------|------------|------------------|--|--|

| Pin Number | A3PE600 Function | Pin Number | A3PE600 Function | Pin Number | A3PE600 Function |  |  |

| 108        | TDO              | 144        | IO47PDB2V1       | 180        | IO19NPB0V2       |  |  |

| 109        | TRST             | 145        | IO44NDB2V1       | 181        | IO18NPB0V2       |  |  |

| 110        | VJTAG            | 146        | IO44PDB2V1       | 182        | IO17PPB0V2       |  |  |

| 111        | VMV3             | 147        | IO43NDB2V0       | 183        | IO16PPB0V2       |  |  |

| 112        | GDA0/IO67NPB3V1  | 148        | IO43PDB2V0       | 184        | IO17NPB0V2       |  |  |

| 113        | GDB0/IO66NPB3V1  | 149        | IO40NDB2V0       | 185        | IO16NPB0V2       |  |  |

| 114        | GDA1/IO67PPB3V1  | 150        | IO40PDB2V0       | 186        | VCCIB0           |  |  |

| 115        | GDB1/IO66PPB3V1  | 151        | GBC2/IO38PSB2V0  | 187        | VCC              |  |  |

| 116        | GDC0/IO65NDB3V1  | 152        | GBA2/IO36PSB2V0  | 188        | IO15PDB0V2       |  |  |

| 117        | GDC1/IO65PDB3V1  | 153        | GBB2/IO37PSB2V0  | 189        | IO15NDB0V2       |  |  |

| 118        | IO62NDB3V1       | 154        | VMV2             | 190        | IO13PDB0V2       |  |  |

| 119        | IO62PDB3V1       | 155        | GNDQ             | 191        | IO13NDB0V2       |  |  |

| 120        | IO58NDB3V0       | 156        | GND              | 192        | IO11PSB0V1       |  |  |

| 121        | IO58PDB3V0       | 157        | VMV1             | 193        | IO09PDB0V1       |  |  |

| 122        | GND              | 158        | GNDQ             | 194        | IO09NDB0V1       |  |  |

| 123        | VCCIB3           | 159        | GBA1/IO35PDB1V1  | 195        | GND              |  |  |

| 124        | GCC2/IO55PSB3V0  | 160        | GBA0/IO35NDB1V1  | 196        | IO07PDB0V1       |  |  |

| 125        | GCB2/IO54PSB3V0  | 161        | GBB1/IO34PDB1V1  | 197        | IO07NDB0V1       |  |  |

| 126        | NC               | 162        | GND              | 198        | IO05PDB0V0       |  |  |

| 127        | IO53NDB3V0       | 163        | GBB0/IO34NDB1V1  | 199        | IO05NDB0V0       |  |  |

| 128        | GCA2/IO53PDB3V0  | 164        | GBC1/IO33PDB1V1  | 200        | VCCIB0           |  |  |

| 129        | GCA1/IO52PPB3V0  | 165        | GBC0/IO33NDB1V1  | 201        | GAC1/IO02PDB0V0  |  |  |

| 130        | GND              | 166        | IO31PDB1V1       | 202        | GAC0/IO02NDB0V0  |  |  |

| 131        | VCCPLC           | 167        | IO31NDB1V1       | 203        | GAB1/IO01PDB0V0  |  |  |

| 132        | GCA0/IO52NPB3V0  | 168        | IO27PDB1V0       | 204        | GAB0/IO01NDB0V0  |  |  |

| 133        | VCOMPLC          | 169        | IO27NDB1V0       | 205        | GAA1/IO00PDB0V0  |  |  |

| 134        | GCB0/IO51NDB2V1  | 170        | VCCIB1           | 206        | GAA0/IO00NDB0V0  |  |  |

| 135        | GCB1/IO51PDB2V1  | 171        | VCC              | 207        | GNDQ             |  |  |

| 136        | GCC1/IO50PSB2V1  | 172        | IO23PPB1V0       | 208        | VMV0             |  |  |

| 137        | IO49NDB2V1       | 173        | IO22PSB1V0       |            |                  |  |  |

| 138        | IO49PDB2V1       | 174        | IO23NPB1V0       |            |                  |  |  |

| 139        | IO48PSB2V1       | 175        | IO21PDB1V0       |            |                  |  |  |

| 140        | VCCIB2           | 176        | IO21NDB1V0       |            |                  |  |  |

| 141        | GND              | 177        | IO19PPB0V2       |            |                  |  |  |

| 142        | VCC              | 178        | GND              |            |                  |  |  |

| 143        | IO47NDB2V1       | 179        | IO18PPB0V2       |            |                  |  |  |

Package Pin Assignments

|            | PQ208             |            | PQ208             |            | PQ208             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| 1          | GND               | 40         | VCCIB6            | 79         | IO194NDB5V0       |

| 2          | GNDQ              | 41         | GND               | 80         | IO194PDB5V0       |

| 3          | VMV7              | 42         | IO244PDB6V1       | 81         | GND               |

| 4          | GAB2/IO308PSB7V4  | 43         | IO244NDB6V1       | 82         | IO184NDB4V3       |

| 5          | GAA2/IO309PDB7V4  | 44         | GEC1/IO236PDB6V0  | 83         | IO184PDB4V3       |

| 6          | IO309NDB7V4       | 45         | GEC0/IO236NDB6V0  | 84         | IO180NDB4V3       |

| 7          | GAC2/IO307PDB7V4  | 46         | GEB1/IO235PPB6V0  | 85         | IO180PDB4V3       |

| 8          | IO307NDB7V4       | 47         | GEA1/IO234PPB6V0  | 86         | IO176NDB4V2       |

| 9          | IO303PDB7V3       | 48         | GEB0/IO235NPB6V0  | 87         | IO176PDB4V2       |

| 10         | IO303NDB7V3       | 49         | GEA0/IO234NPB6V0  | 88         | VCC               |

| 11         | IO299PDB7V3       | 50         | VMV6              | 89         | VCCIB4            |

| 12         | IO299NDB7V3       | 51         | GNDQ              | 90         | IO170NDB4V2       |

| 13         | IO295PDB7V2       | 52         | GND               | 91         | IO170PDB4V2       |

| 14         | IO295NDB7V2       | 53         | VMV5              | 92         | IO166NDB4V1       |

| 15         | IO291PSB7V2       | 54         | GNDQ              | 93         | IO166PDB4V1       |

| 16         | VCC               | 55         | IO233NDB5V4       | 94         | IO156NDB4V0       |

| 17         | GND               | 56         | GEA2/IO233PDB5V4  | 95         | GDC2/IO156PDB4V0  |

| 18         | VCCIB7            | 57         | IO232NDB5V4       | 96         | IO154NPB4V0       |

| 19         | IO285PDB7V1       | 58         | GEB2/IO232PDB5V4  | 97         | GND               |

| 20         | IO285NDB7V1       | 59         | IO231NDB5V4       | 98         | GDB2/IO155PSB4V0  |

| 21         | IO279PSB7V0       | 60         | GEC2/IO231PDB5V4  | 99         | GDA2/IO154PPB4V0  |

| 22         | GFC1/IO275PSB7V0  | 61         | IO230PSB5V4       | 100        | GNDQ              |

| 23         | GFB1/IO274PDB7V0  | 62         | VCCIB5            | 101        | ТСК               |

| 24         | GFB0/IO274NDB7V0  | 63         | IO218NDB5V3       | 102        | TDI               |

| 25         | VCOMPLF           | 64         | IO218PDB5V3       | 103        | TMS               |

| 26         | GFA0/IO273NPB6V4  | 65         | GND               | 104        | VMV4              |

| 27         | VCCPLF            | 66         | IO214PSB5V2       | 105        | GND               |

| 28         | GFA1/IO273PPB6V4  | 67         | IO212NDB5V2       | 106        | VPUMP             |

| 29         | GND               | 68         | IO212PDB5V2       | 107        | GNDQ              |

| 30         | GFA2/IO272PDB6V4  | 69         | IO208NDB5V1       | 108        | TDO               |

| 31         | IO272NDB6V4       | 70         | IO208PDB5V1       | 109        | TRST              |

| 32         | GFB2/IO271PPB6V4  | 71         | VCC               | 110        | VJTAG             |

| 33         | GFC2/IO270PPB6V4  | 72         | VCCIB5            | 111        | VMV3              |

| 34         | IO271NPB6V4       | 73         | IO202NDB5V1       | 112        | GDA0/IO153NPB3V4  |

| 35         | IO270NPB6V4       | 74         | IO202PDB5V1       | 113        | GDB0/IO152NPB3V4  |

| 36         | VCC               | 75         | IO198NDB5V0       | 114        | GDA1/IO153PPB3V4  |

| 37         | IO252PDB6V2       | 76         | IO198PDB5V0       | 115        | GDB1/IO152PPB3V4  |

| 38         | IO252NDB6V2       | 77         | IO197NDB5V0       | 116        | GDC0/IO151NDB3V4  |

| 39         | IO248PSB6V1       | 78         | IO197PDB5V0       | 117        | GDC1/IO151PDB3V4  |

Package Pin Assignments

|            | FG256            |            | FG256            |            | FG256            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3PE600 Function | Pin Number | A3PE600 Function | Pin Number | A3PE600 Function |

| G13        | GCC1/IO50PPB2V1  | K1         | GFC2/IO115PSB6V1 | M5         | VMV5             |

| G14        | IO44NDB2V1       | K2         | IO113PPB6V1      | M6         | VCCIB5           |

| G15        | IO44PDB2V1       | K3         | IO112PDB6V1      | M7         | VCCIB5           |

| G16        | IO49NSB2V1       | K4         | IO112NDB6V1      | M8         | IO84NDB5V0       |

| H1         | GFB0/IO119NPB7V0 | K5         | VCCIB6           | M9         | IO84PDB5V0       |

| H2         | GFA0/IO118NDB6V1 | K6         | VCC              | M10        | VCCIB4           |

| H3         | GFB1/IO119PPB7V0 | K7         | GND              | M11        | VCCIB4           |

| H4         | VCOMPLF          | K8         | GND              | M12        | VMV3             |

| H5         | GFC0/IO120NPB7V0 | K9         | GND              | M13        | VCCPLD           |

| H6         | VCC              | K10        | GND              | M14        | GDB1/IO66PPB3V1  |

| H7         | GND              | K11        | VCC              | M15        | GDC1/IO65PDB3V1  |

| H8         | GND              | K12        | VCCIB3           | M16        | IO61NDB3V1       |

| H9         | GND              | K13        | IO54NPB3V0       | N1         | IO105PDB6V0      |

| H10        | GND              | K14        | IO57NPB3V0       | N2         | IO105NDB6V0      |

| H11        | VCC              | K15        | IO55NPB3V0       | N3         | GEC1/IO104PPB6V0 |

| H12        | GCC0/IO50NPB2V1  | K16        | IO57PPB3V0       | N4         | VCOMPLE          |

| H13        | GCB1/IO51PPB2V1  | L1         | IO113NPB6V1      | N5         | GNDQ             |

| H14        | GCA0/IO52NPB3V0  | L2         | IO109PPB6V0      | N6         | GEA2/IO101PPB5V2 |

| H15        | VCOMPLC          | L3         | IO108PDB6V0      | N7         | IO92NDB5V1       |

| H16        | GCB0/IO51NPB2V1  | L4         | IO108NDB6V0      | N8         | IO90NDB5V1       |

| J1         | GFA2/IO117PSB6V1 | L5         | VCCIB6           | N9         | IO82NDB5V0       |

| J2         | GFA1/IO118PDB6V1 | L6         | GND              | N10        | IO74NDB4V1       |

| J3         | VCCPLF           | L7         | VCC              | N11        | IO74PDB4V1       |

| J4         | IO116NDB6V1      | L8         | VCC              | N12        | GNDQ             |

| J5         | GFB2/IO116PDB6V1 | L9         | VCC              | N13        | VCOMPLD          |

| J6         | VCC              | L10        | VCC              | N14        | VJTAG            |

| J7         | GND              | L11        | GND              | N15        | GDC0/IO65NDB3V1  |

| J8         | GND              | L12        | VCCIB3           | N16        | GDA1/IO67PDB3V1  |

| J9         | GND              | L13        | GDB0/IO66NPB3V1  | P1         | GEB1/IO103PDB6V0 |

| J10        | GND              | L14        | IO60NDB3V1       | P2         | GEB0/IO103NDB6V0 |

| J11        | VCC              | L15        | IO60PDB3V1       | P3         | VMV6             |

| J12        | GCB2/IO54PPB3V0  | L16        | IO61PDB3V1       | P4         | VCCPLE           |

| J13        | GCA1/IO52PPB3V0  | M1         | IO109NPB6V0      | P5         | IO101NPB5V2      |

| J14        | GCC2/IO55PPB3V0  | M2         | IO106NDB6V0      | P6         | IO95PPB5V1       |

| J15        | VCCPLC           | M3         | IO106PDB6V0      | P7         | IO92PDB5V1       |

| J16        | GCA2/IO53PSB3V0  | M4         | GEC0/IO104NPB6V0 | P8         | IO90PDB5V1       |

### FG676

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

|            | FG676             |

|------------|-------------------|

| Pin Number | A3PE1500 Function |

| W25        | IO96PDB3V1        |

| W26        | IO94NDB3V0        |

| Y1         | IO175NDB6V1       |

| Y2         | IO175PDB6V1       |

| Y3         | IO173NDB6V0       |

| Y4         | IO173PDB6V0       |

| Y5         | GEC1/IO169PPB6V0  |

| Y6         | GNDQ              |

| Y7         | VMV6              |

| Y8         | VCCIB5            |

| Y9         | IO163NDB5V3       |

| Y10        | IO159PDB5V3       |

| Y11        | IO153PDB5V2       |

| Y12        | IO147PDB5V1       |

| Y13        | IO139PDB5V0       |

| Y14        | IO137PDB5V0       |

| Y15        | IO125NDB4V1       |

| Y16        | IO125PDB4V1       |

| Y17        | IO115NDB4V0       |

| Y18        | IO115PDB4V0       |

| Y19        | VCC               |

| Y20        | VPUMP             |

| Y21        | VCOMPLD           |

| Y22        | VCCPLD            |

| Y23        | IO100NDB3V1       |

| Y24        | IO100PDB3V1       |

| Y25        | IO96NDB3V1        |

| Y26        | IO98PDB3V1        |

|            |                   |

|            | FG896             |            | FG896             |            | FG896             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| AG9        | IO225NPB5V3       | AH15       | IO195NDB5V0       | AJ21       | IO173PDB4V2       |

| AG10       | IO223NPB5V3       | AH16       | IO185NDB4V3       | AJ22       | IO163NDB4V1       |

| AG11       | IO221PDB5V3       | AH17       | IO185PDB4V3       | AJ23       | IO163PDB4V1       |

| AG12       | IO221NDB5V3       | AH18       | IO181PDB4V3       | AJ24       | IO167NPB4V1       |

| AG13       | IO205NPB5V1       | AH19       | IO177NDB4V2       | AJ25       | VCC               |

| AG14       | IO199NDB5V0       | AH20       | IO171NPB4V2       | AJ26       | IO156NPB4V0       |

| AG15       | IO199PDB5V0       | AH21       | IO165PPB4V1       | AJ27       | VCC               |

| AG16       | IO187NDB4V4       | AH22       | IO161PPB4V0       | AJ28       | TMS               |

| AG17       | IO187PDB4V4       | AH23       | IO157NDB4V0       | AJ29       | GND               |

| AG18       | IO181NDB4V3       | AH24       | IO157PDB4V0       | AJ30       | GND               |

| AG19       | IO171PPB4V2       | AH25       | IO155NDB4V0       | AK2        | GND               |

| AG20       | IO165NPB4V1       | AH26       | VCCIB4            | AK3        | GND               |

| AG21       | IO161NPB4V0       | AH27       | TDI               | AK4        | IO217PPB5V2       |

| AG22       | IO159NDB4V0       | AH28       | VCC               | AK5        | GND               |

| AG23       | IO159PDB4V0       | AH29       | VPUMP             | AK6        | IO215PPB5V2       |

| AG24       | IO158PPB4V0       | AH30       | GND               | AK7        | GND               |

| AG25       | GDB2/IO155PDB4V0  | AJ1        | GND               | AK8        | IO207NDB5V1       |

| AG26       | GDA2/IO154PPB4V0  | AJ2        | GND               | AK9        | IO207PDB5V1       |

| AG27       | GND               | AJ3        | GEA2/IO233PPB5V4  | AK10       | IO201NDB5V0       |

| AG28       | VJTAG             | AJ4        | VCC               | AK11       | IO201PDB5V0       |

| AG29       | VCC               | AJ5        | IO217NPB5V2       | AK12       | IO193NDB4V4       |

| AG30       | IO149NDB3V4       | AJ6        | VCC               | AK13       | IO193PDB4V4       |

| AH1        | GND               | AJ7        | IO215NPB5V2       | AK14       | IO197PDB5V0       |

| AH2        | IO233NPB5V4       | AJ8        | IO213NDB5V2       | AK15       | IO191NDB4V4       |

| AH3        | VCC               | AJ9        | IO213PDB5V2       | AK16       | IO191PDB4V4       |

| AH4        | GEB2/IO232PPB5V4  | AJ10       | IO209NDB5V1       | AK17       | IO189NDB4V4       |

| AH5        | VCCIB5            | AJ11       | IO209PDB5V1       | AK18       | IO189PDB4V4       |

| AH6        | IO219NDB5V3       | AJ12       | IO203NDB5V1       | AK19       | IO179PPB4V3       |

| AH7        | IO219PDB5V3       | AJ13       | IO203PDB5V1       | AK20       | IO175NDB4V2       |

| AH8        | IO227NDB5V4       | AJ14       | IO197NDB5V0       | AK21       | IO175PDB4V2       |

| AH9        | IO227PDB5V4       | AJ15       | IO195PDB5V0       | AK22       | IO169NDB4V1       |

| AH10       | IO225PPB5V3       | AJ16       | IO183NDB4V3       | AK23       | IO169PDB4V1       |

| AH11       | IO223PPB5V3       | AJ17       | IO183PDB4V3       | AK24       | GND               |

| AH12       | IO211NDB5V2       | AJ18       | IO179NPB4V3       | AK25       | IO167PPB4V1       |

| AH13       | IO211PDB5V2       | AJ19       | IO177PDB4V2       | AK26       | GND               |

| AH14       | IO205PPB5V1       | AJ20       | IO173NDB4V2       | AK27       | GDC2/IO156PPB4V0  |

| Revision                                                                 | Changes                                                                                                                                                                                                                                                                                                         | Page |  |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| Revision 9 (Aug 2009)                                                    | All references to speed grade –F have been removed from this document.                                                                                                                                                                                                                                          | N/A  |  |  |  |  |

| Product Brief v1.2                                                       |                                                                                                                                                                                                                                                                                                                 |      |  |  |  |  |

|                                                                          | The "Pro I/Os with Advanced I/O Standards" section was revised to add definitions of hot-swap and cold-sparing.                                                                                                                                                                                                 | 1-6  |  |  |  |  |

| DC and Switching<br>Characteristics v1.3                                 | 3.3 V LVCMOS and 1.2 V LVCMOS Wide Range support was added to the datasheet. This affects all tables that contained 3.3 V LVCMOS and 1.2 V LVCMOS data.                                                                                                                                                         | N/A  |  |  |  |  |

|                                                                          | IIL and IIH input leakage current information was added to all "Minimum and Maximum DC Input and Output Levels" tables.                                                                                                                                                                                         |      |  |  |  |  |

|                                                                          | -F was removed from the datasheet. The speed grade is no longer supported.                                                                                                                                                                                                                                      | N/A  |  |  |  |  |

|                                                                          | In the Table 2-2 • Recommended Operating Conditions <sup>1</sup> "3.0 V DC supply voltage" and note 4 are new.                                                                                                                                                                                                  |      |  |  |  |  |

|                                                                          | The Table 2-4 • Overshoot and Undershoot Limits <sup>1</sup> table was updated.                                                                                                                                                                                                                                 |      |  |  |  |  |

|                                                                          | The Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays table was updated.                                                                                                                                                                                                                   |      |  |  |  |  |

|                                                                          | There are new parameters and data was updated in the Table 2-99 • RAM4K9 table.                                                                                                                                                                                                                                 |      |  |  |  |  |

|                                                                          | There are new parameters and data was updated in the Table 2-100 • RAM512X18 table.                                                                                                                                                                                                                             | 2-77 |  |  |  |  |

| Revision 8 (Feb 2008)                                                    | Table 1-2 • ProASIC3E FPGAs Package Sizes Dimensions is new.                                                                                                                                                                                                                                                    | 1-II |  |  |  |  |

| Product Brief v1.1                                                       |                                                                                                                                                                                                                                                                                                                 |      |  |  |  |  |

| <b>Revision 7 (Jun 2008)</b><br>DC and Switching<br>Characteristics v1.2 | The title of Table 2-4 • Overshoot and Undershoot Limits <sup>1</sup> was modified to remove "as measured on quiet I/Os." Table note 2 was revised to remove "estimated SSO density over cycles." Table note 3 was deleted.                                                                                     | 2-3  |  |  |  |  |

|                                                                          | Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels was updated.                                                                                                                                                                                                                                   |      |  |  |  |  |

| Revision 6 (Jun 2008)                                                    | The A3PE600 "FG484" table was missing G22. The pin and its function were added to the table.                                                                                                                                                                                                                    | 4-27 |  |  |  |  |

| <b>Revision 5 (Jun 2008)</b><br>Packaging v1.4                           | The naming conventions changed for the following pins in the "FG484" for the A3PE600:                                                                                                                                                                                                                           | 4-22 |  |  |  |  |

|                                                                          | Pin Number New Function Name                                                                                                                                                                                                                                                                                    |      |  |  |  |  |

|                                                                          | J19 IO45PPB2V1                                                                                                                                                                                                                                                                                                  |      |  |  |  |  |

|                                                                          | K20 IO45NPB2V1                                                                                                                                                                                                                                                                                                  |      |  |  |  |  |

|                                                                          | M2 IO114NPB6V1                                                                                                                                                                                                                                                                                                  |      |  |  |  |  |

|                                                                          | N1 IO114PPB6V1                                                                                                                                                                                                                                                                                                  |      |  |  |  |  |

|                                                                          | N4 GFC2/IO115PPB6V1                                                                                                                                                                                                                                                                                             |      |  |  |  |  |

|                                                                          | P3 IO115NPB6V1                                                                                                                                                                                                                                                                                                  |      |  |  |  |  |

| Revision 4 (Apr 2008)<br>Product Brief v1.0                              | The product brief portion of the datasheet was divided into two sections and given<br>a version number, starting at v1.0. The first section of the document includes<br>features, benefits, ordering information, and temperature and speed grade<br>offerings. The second section is a device family overview. | N/A  |  |  |  |  |

| Packaging v1.3                                                           | The "FG324" package diagram was replaced.                                                                                                                                                                                                                                                                       | 4-12 |  |  |  |  |