Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            |                                                                             |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 341                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

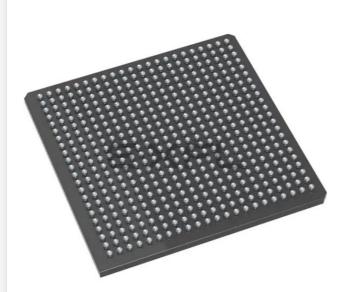

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

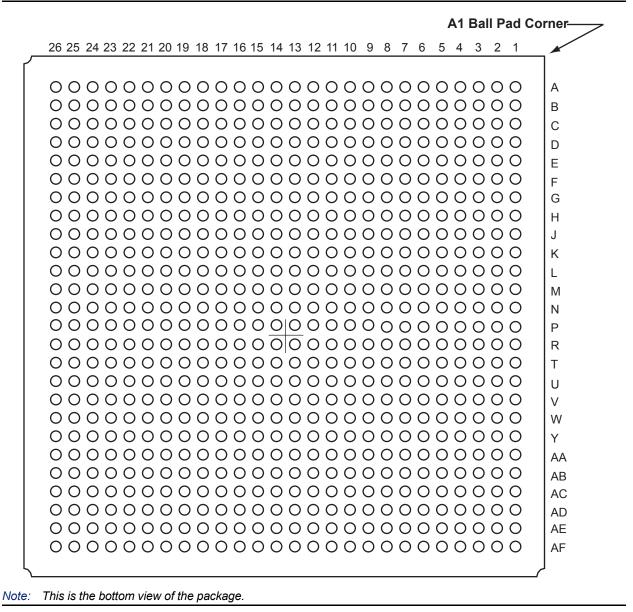

| Package / Case                 | 484-BGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000-1fg484 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# static Microsemi.

ProASIC3E Flash Family FPGAs

# I/Os Per Package<sup>1</sup>

| ProASIC3E Devices              | A3P                           | E600                   | A3PE                          | 1500 <sup>3</sup>      | A3PE                          | 3000 <sup>3</sup>      |  |  |  |  |  |

|--------------------------------|-------------------------------|------------------------|-------------------------------|------------------------|-------------------------------|------------------------|--|--|--|--|--|

| Cortex-M1 Devices <sup>2</sup> |                               |                        | M1A3F                         | PE1500                 | M1A3F                         | PE3000                 |  |  |  |  |  |

|                                |                               | I/O Types              |                               |                        |                               |                        |  |  |  |  |  |

| Package                        | Single-Ended I/O <sup>1</sup> | Differential I/O Pairs | Single-Ended I/O <sup>1</sup> | Differential I/O Pairs | Single-Ended I/O <sup>1</sup> | Differential I/O Pairs |  |  |  |  |  |

| PQ208                          | 147                           | 65                     | 147                           | 65                     | 147                           | 65                     |  |  |  |  |  |

| FG256                          | 165                           | 79                     | -                             | -                      | -                             | -                      |  |  |  |  |  |

| FG324                          | -                             | -                      | -                             | -                      | 221                           | 110                    |  |  |  |  |  |

| FG484                          | 270                           | 135                    | 280                           | 139                    | 341                           | 168                    |  |  |  |  |  |

| FG676                          | -                             | -                      | 444                           | 222                    | _                             | -                      |  |  |  |  |  |

| FG896                          | -                             | -                      | -                             | -                      | 620                           | 310                    |  |  |  |  |  |

Notes:

1. When considering migrating your design to a lower- or higher-density device, refer to the ProASIC3E FPGA Fabric User's Guide to ensure compliance with design and board migration requirements.

- 2. Each used differential I/O pair reduces the number of single-ended I/Os available by two.

- 3. For A3PE1500 and A3PE3000 devices, the usage of certain I/O standards is limited as follows:

- SSTL3(I) and (II): up to 40 I/Os per north or south bank

- LVPECL / GTL+ 3.3 V / GTL 3.3 V: up to 48 I/Os per north or south bank

- SSTL2(I) and (II) / GTL+ 2.5 V/ GTL 2.5 V: up to 72 I/Os per north or south bank

- 4. FG256 and FG484 are footprint-compatible packages.

- 5. When using voltage-referenced I/O standards, one I/O pin should be assigned as a voltage-referenced pin (VREF) per minibank (group of I/Os).

- 6. "G" indicates RoHS-compliant packages. Refer to the "ProASIC3E Ordering Information" on page III for the location of the "G" in the part number.

| Package                         | PQ208   | FG256   | FG324   | FG484   | FG676   | FG896   |

|---------------------------------|---------|---------|---------|---------|---------|---------|

| Length × Width (mm\mm)          | 28 × 28 | 17 × 17 | 19 × 19 | 23 × 23 | 27 × 27 | 31 × 31 |

| Nominal Area (mm <sup>2</sup> ) | 784     | 289     | 361     | 529     | 729     | 961     |

| Pitch (mm)                      | 0.5     | 1.0     | 1.0     | 1.0     | 1.0     | 1.0     |

| Height (mm)                     | 3.40    | 1.60    | 1.63    | 2.23    | 2.23    | 2.23    |

### Table 1-2 • ProASIC3E FPGAs Package Sizes Dimensions

# **ProASIC3E** Device Status

| ProASIC3E Devices | Status     | M1 ProASIC3E Devices | Status     |

|-------------------|------------|----------------------|------------|

| A3PE600           | Production |                      |            |

| A3PE1500          | Production | M1A3PE1500           | Production |

| A3PE3000          | Production | M1A3PE3000           | Production |

# 1 – ProASIC3E Device Family Overview

## **General Description**

ProASIC3E, the third-generation family of Microsemi flash FPGAs, offers performance, density, and features beyond those of the ProASIC<sup>PLUS®</sup> family. Nonvolatile flash technology gives ProASIC3E devices the advantage of being a secure, low power, single-chip solution that is Instant On. ProASIC3E is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost. These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

ProASIC3E devices offer 1 kbit of on-chip, programmable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on six integrated phase-locked loops (PLLs). ProASIC3E devices have up to three million system gates, supported with up to 504 kbits of true dual-port SRAM and up to 620 user I/Os.

Several ProASIC3E devices support the Cortex-M1 soft IP cores, and the ARM-Enabled devices have Microsemi ordering numbers that begin with M1A3PE.

## **Flash Advantages**

## Reduced Cost of Ownership

Advantages to the designer extend beyond low unit cost, performance, and ease of use. Unlike SRAMbased FPGAs, flash-based ProASIC3E devices allow all functionality to be Instant On; no external boot PROM is required. On-board security mechanisms prevent access to all the programming information and enable secure remote updates of the FPGA logic. Designers can perform secure remote in-system reprogramming to support future design iterations and field upgrades with confidence that valuable intellectual property (IP) cannot be compromised or copied. Secure ISP can be performed using the industry-standard AES algorithm. The ProASIC3E family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the ProASIC3E family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/ communications, computing, and avionics markets.

## Security

The nonvolatile, flash-based ProASIC3E devices do not require a boot PROM, so there is no vulnerable external bitstream that can be easily copied. ProASIC3E devices incorporate FlashLock, which provides a unique combination of reprogrammability and design security without external overhead, advantages that only an FPGA with nonvolatile flash programming can offer.

ProASIC3E devices utilize a 128-bit flash-based lock and a separate AES key to provide the highest level of protection in the FPGA industry for programmed intellectual property and configuration data. In addition, all FlashROM data in ProASIC3E devices can be encrypted prior to loading, using the industryleading AES-128 (FIPS192) bit block cipher encryption standard. The AES standard was adopted by the National Institute of Standards and Technology (NIST) in 2000 and replaces the 1977 DES standard. ProASIC3E devices have a built-in AES decryption engine and a flash-based AES key that make them the most comprehensive programmable logic device security solution available today. ProASIC3E devices with AES-based security provide a high level of protection for secure, remote field updates over public networks such as the Internet, and ensure that valuable IP remains out of the hands of system overbuilders, system cloners, and IP thieves.

Security, built into the FPGA fabric, is an inherent component of the ProASIC3E family. The flash cells are located beneath seven metal layers, and many device design and layout techniques have been used to make invasive attacks extremely difficult. The ProASIC3E family, with FlashLock and AES security, is unique in being highly resistant to both invasive and noninvasive attacks. Your valuable IP is protected with industry-standard security, making remote ISP possible. A ProASIC3E device provides the best available security for programmable logic designs.

## **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

|                                  |                    | Equivalent         |              |           | VIL         | VIH             |           | VOL         | VOH         | IOL <sup>3</sup> | IOH <sup>3</sup> |

|----------------------------------|--------------------|--------------------|--------------|-----------|-------------|-----------------|-----------|-------------|-------------|------------------|------------------|

| I/O Standard                     | Drive<br>Strength  |                    | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V       | Max.<br>V | Max.<br>V   | Min.<br>V   | mA               | mA               |

| 3.3 V LVTTL /<br>3.3 V<br>LVCMOS | 12 mA              | 12 mA              | High         | -0.3      | 0.8         | 2               | 3.6       | 0.4         | 2.4         | 12               | 12               |

| 3.3 V<br>LVCMOS<br>Wide Range    | 100 µA             | 12 mA              | High         | -0.3      | 0.8         | 2               | 3.6       | 0.2         | VCCI – 0.2  | 0.1              | 0.1              |

| 2.5 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.7         | 1.7             | 3.6       | 0.7         | 1.7         | 12               | 12               |

| 1.8 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI     | 3.6       | 0.45        | VCCI – 0.45 | 12               | 12               |

| 1.5 V<br>LVCMOS                  | 12 mA              | 12 mA              | High         | -0.3      | 0.30 * VCCI | 0.7 * VCCI      | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12               | 12               |

| 3.3 V PCI                        |                    |                    |              |           | Per PC      | CI Specificatio | n         |             |             |                  |                  |

| 3.3 V PCI-X                      |                    |                    |              |           | Per PCI     | -X Specificati  | on        |             |             |                  |                  |

| 3.3 V GTL                        | 20 mA <sup>2</sup> | 20 mA <sup>2</sup> | High         | -0.3      | VREF – 0.05 | VREF + 0.05     | 3.6       | 0.4         | -           | 20               | 20               |

| 2.5 V GTL                        | 20 mA <sup>2</sup> | 20 mA <sup>2</sup> | High         | -0.3      | VREF – 0.05 | VREF + 0.05     | 3.6       | 0.4         | _           | 20               | 20               |

| 3.3 V GTL+                       | 35 mA              | 35 mA              | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.6         | -           | 35               | 35               |

| 2.5 V GTL+                       | 33 mA              | 33 mA              | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.6         | -           | 33               | 33               |

| HSTL (I)                         | 8 mA               | 8 mA               | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.4         | VCCI - 0.4  | 8                | 8                |

| HSTL (II)                        | 15 mA <sup>2</sup> | 15 mA <sup>2</sup> | High         | -0.3      | VREF – 0.1  | VREF + 0.1      | 3.6       | 0.4         | VCCI - 0.4  | 15               | 15               |

| SSTL2 (I)                        | 15 mA              | 15 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.54        | VCCI – 0.62 | 15               | 15               |

| SSTL2 (II)                       | 18 mA              | 18 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.35        | VCCI – 0.43 | 18               | 18               |

| SSTL3 (I)                        | 14 mA              | 14 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.7         | VCCI – 1.1  | 14               | 14               |

| SSTL3 (II)                       | 21 mA              | 21 mA              | High         | -0.3      | VREF – 0.2  | VREF + 0.2      | 3.6       | 0.5         | VCCI - 0.9  | 21               | 21               |

Table 2-13 • Summary of Maximum and Minimum DC Input and Output Levels

Applicable to Commercial and Industrial Conditions

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. Output drive strength is below JEDEC specification.

3. Currents are measured at 85°C junction temperature.

4. Output Slew Rates can be extracted from IBIS Models, located at http://www.microsemi.com/index.php?option=com\_content&id=1671&lang=en&view=article.

# 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 12.00           | 0.04             | 1.51            | 1.66             | 0.43              | 12.23           | 11.61           | 2.72            | 2.20            | 14.46            | 13.85            | ns    |

|                   | -1             | 0.56              | 10.21           | 0.04             | 1.29            | 1.41             | 0.36              | 10.40           | 9.88            | 2.31            | 1.87            | 12.30            | 11.78            | ns    |

|                   | -2             | 0.49              | 8.96            | 0.03             | 1.13            | 1.24             | 0.32              | 9.13            | 8.67            | 2.03            | 1.64            | 10.80            | 10.34            | ns    |

| 8 mA              | Std.           | 0.66              | 8.73            | 0.04             | 1.51            | 1.66             | 0.43              | 8.89            | 8.01            | 3.10            | 2.93            | 11.13            | 10.25            | ns    |

|                   | -1             | 0.56              | 7.43            | 0.04             | 1.29            | 1.41             | 0.36              | 7.57            | 6.82            | 2.64            | 2.49            | 9.47             | 8.72             | ns    |

|                   | -2             | 0.49              | 6.52            | 0.03             | 1.13            | 1.24             | 0.32              | 6.64            | 5.98            | 2.32            | 2.19            | 8.31             | 7.65             | ns    |

| 12 mA             | Std.           | 0.66              | 6.77            | 0.04             | 1.51            | 1.66             | 0.43              | 6.90            | 6.11            | 3.37            | 3.39            | 9.14             | 8.34             | ns    |

|                   | -1             | 0.56              | 5.76            | 0.04             | 1.29            | 1.41             | 0.36              | 5.87            | 5.20            | 2.86            | 2.89            | 7.77             | 7.10             | ns    |

|                   | -2             | 0.49              | 5.06            | 0.03             | 1.13            | 1.24             | 0.32              | 5.15            | 4.56            | 2.51            | 2.53            | 6.82             | 6.23             | ns    |

| 16 mA             | Std.           | 0.66              | 6.31            | 0.04             | 1.51            | 1.66             | 0.43              | 6.42            | 5.73            | 3.42            | 3.52            | 8.66             | 7.96             | ns    |

|                   | -1             | 0.56              | 5.37            | 0.04             | 1.29            | 1.41             | 0.36              | 5.46            | 4.87            | 2.91            | 3.00            | 7.37             | 6.77             | ns    |

|                   | -2             | 0.49              | 4.71            | 0.03             | 1.13            | 1.24             | 0.32              | 4.80            | 4.28            | 2.56            | 2.63            | 6.47             | 5.95             | ns    |

| 24 mA             | Std.           | 0.66              | 5.93            | 0.04             | 1.51            | 1.66             | 0.43              | 6.04            | 5.70            | 3.49            | 4.00            | 8.28             | 7.94             | ns    |

|                   | -1             | 0.56              | 5.05            | 0.04             | 1.29            | 1.41             | 0.36              | 5.14            | 4.85            | 2.97            | 3.40            | 7.04             | 6.75             | ns    |

|                   | -2             | 0.49              | 4.43            | 0.03             | 1.13            | 1.24             | 0.32              | 4.51            | 4.26            | 2.61            | 2.99            | 6.18             | 5.93             | ns    |

## Table 2-36 • 2.5 V LVCMOS Low Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

## **Voltage-Referenced I/O Characteristics**

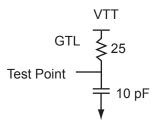

## 3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-48 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          |           | VIL         | VIH         |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20  | 20 | 181                     | 268                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

## Figure 2-12 • AC Loading

#### Table 2-49 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                     | 0.8             | 1.2            | 10                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

## Timing Characteristics

Table 2-50 • 3.3 V GTL

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.08            | 0.04             | 2.93            | 0.43              | 2.04            | 2.08            |                 |                 | 4.27             | 4.31             | ns    |

| -1             | 0.51              | 1.77            | 0.04             | 2.50            | 0.36              | 1.73            | 1.77            |                 |                 | 3.63             | 3.67             | ns    |

| -2             | 0.45              | 1.55            | 0.03             | 2.19            | 0.32              | 1.52            | 1.55            |                 |                 | 3.19             | 3.22             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

ProASIC3E DC and Switching Characteristics

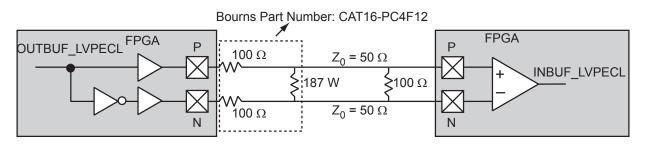

## LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-24. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

#### Figure 2-24 • LVPECL Circuit Diagram and Board-Level Implementation

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCI         | Supply Voltage                 | 3.    | 3.0  |       | 3.3  |       | 3.6  |       |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

#### Table 2-81 • Minimum and Maximum DC Input and Output Levels

Table 2-82 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.64          | 1.94           | Cross point          | -               |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-83 • LVPECL

#### Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.83            | 0.04             | 1.63            | ns    |

| -1          | 0.56              | 1.55            | 0.04             | 1.39            | ns    |

| -2          | 0.49              | 1.36            | 0.03             | 1.22            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

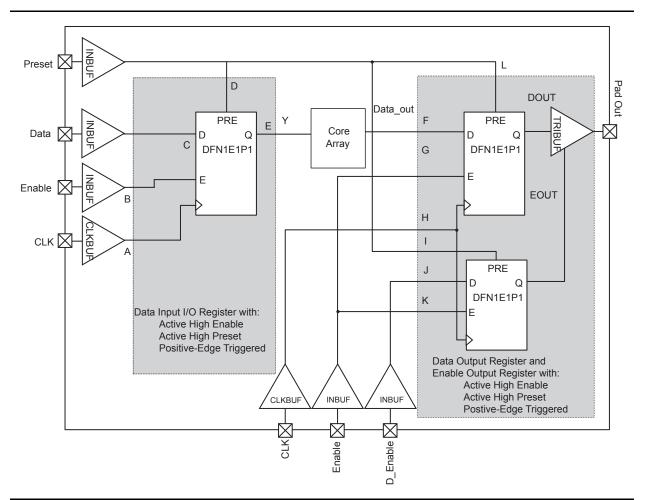

## **I/O Register Specifications**

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

Figure 2-25 • Timing Model of Registered I/O Buffers with Synchronous Enable and Asynchronous Preset

# **Microsemi**

ProASIC3E DC and Switching Characteristics

## Table 2-84 • Parameter Definition and Measuring Nodes

| Parameter Name        | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L, DOUT                        |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| toesud                | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | K, H                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

Note: \*See Figure 2-25 on page 2-53 for more information.

## Timing Waveforms

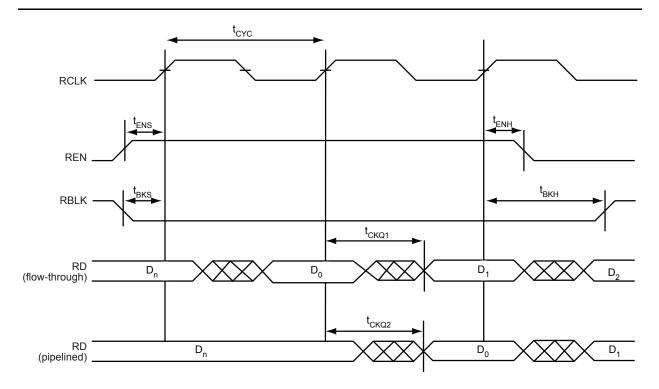

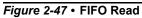

Figure 2-48 • FIFO Write

Pin Descriptions and Packaging

# **Special Function Pins**

### NC

#### **No Connect**

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC

#### Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

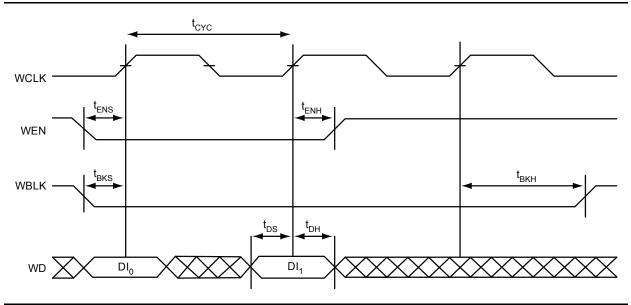

# Packaging

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

# **Related Documents**

## **User's Guides**

ProASIC3E FPGA Fabric User's Guide

http://www.microsemi.com/document-portal/doc\_download/130883-proasic3e-fpga-fabric-user-s-guide

## Packaging

The following documents provide packaging information and device selection for low power flash devices.

## Product Catalog

http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

## Package Mechanical Drawings

http://www.microsemi.com/document-portal/doc\_download/131095-package-mechanical-drawings

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials: http://www.microsemi.com/products/fpga-soc/solutions.

# **Microsemi**

Package Pin Assignments

|            | PQ208            |            | PQ208            | PQ208      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3PE600 Function | Pin Number | A3PE600 Function | Pin Number | A3PE600 Function |

| 1          | GND              | 37         | IO112PDB6V1      | 72         | VCCIB5           |

| 2          | GNDQ             | 38         | IO112NDB6V1      | 73         | IO85NPB5V0       |

| 3          | VMV7             | 39         | IO108PSB6V0      | 74         | IO84NPB5V0       |

| 4          | GAB2/IO133PSB7V1 | 40         | VCCIB6           | 75         | IO85PPB5V0       |

| 5          | GAA2/IO134PDB7V1 | 41         | GND              | 76         | IO84PPB5V0       |

| 6          | IO134NDB7V1      | 42         | IO106PDB6V0      | 77         | IO83NPB5V0       |

| 7          | GAC2/IO132PDB7V1 | 43         | IO106NDB6V0      | 78         | IO82NPB5V0       |

| 8          | IO132NDB7V1      | 44         | GEC1/IO104PDB6V0 | 79         | IO83PPB5V0       |

| 9          | IO130PDB7V1      | 45         | GEC0/IO104NDB6V  | 80         | IO82PPB5V0       |

| 10         | IO130NDB7V1      |            | 0                | 81         | GND              |

| 11         | IO127PDB7V1      | 46         | GEB1/IO103PPB6V0 | 82         | IO80NDB4V1       |

| 12         | IO127NDB7V1      | 47         | GEA1/IO102PPB6V0 | 83         | IO80PDB4V1       |

| 13         | IO126PDB7V0      | 48         | GEB0/IO103NPB6V0 | 84         | IO79NPB4V1       |

| 14         | IO126NDB7V0      | 49         | GEA0/IO102NPB6V0 | 85         | IO78NPB4V1       |

| 15         | IO124PSB7V0      | 50         | VMV6             | 86         | IO79PPB4V1       |

| 16         | VCC              | 51         | GNDQ             | 87         | IO78PPB4V1       |

| 17         | GND              | 52         | GND              | 88         | VCC              |

| 18         | VCCIB7           | 53         | VMV5             | 89         | VCCIB4           |

| 19         | IO122PPB7V0      | 54         | GNDQ             | 90         | IO76NDB4V1       |

| 20         | IO121PSB7V0      | 55         | IO101NDB5V2      | 91         | IO76PDB4V1       |

| 21         | IO122NPB7V0      | 56         | GEA2/IO101PDB5V2 | 92         | IO72NDB4V0       |

| 22         | GFC1/IO120PSB7V0 | 57         | IO100NDB5V2      | 93         | IO72PDB4V0       |

| 23         | GFB1/IO119PDB7V0 | 58         | GEB2/IO100PDB5V2 | 94         | IO70NDB4V0       |

| 24         | GFB0/IO119NDB7V0 | 59         | IO99NDB5V2       | 95         | GDC2/IO70PDB4V0  |

| 25         | VCOMPLF          | 60         | GEC2/IO99PDB5V2  | 96         | IO68NDB4V0       |

| 26         | GFA0/IO118NPB6V1 | 61         | IO98PSB5V2       | 97         | GND              |

| 27         | VCCPLF           | 62         | VCCIB5           | 98         | GDA2/IO68PDB4V0  |

| 28         | GFA1/IO118PPB6V1 | 63         | IO96PSB5V2       | 99         | GDB2/IO69PSB4V0  |

| 29         | GND              | 64         | IO94NDB5V1       | 100        | GNDQ             |

| 30         | GFA2/IO117PDB6V1 | 65         | GND              | 101        | ТСК              |

| 31         | IO117NDB6V1      | 66         | IO94PDB5V1       | 102        | TDI              |

| 32         | GFB2/IO116PPB6V1 | 67         | IO92NDB5V1       | 102        | TMS              |

| 33         | GFC2/IO115PPB6V1 | 68         | IO92PDB5V1       | 104        | VMV4             |

| 34         | IO116NPB6V1      | 69         | IO88NDB5V0       | 105        | GND              |

| 35         | IO115NPB6V1      | 70         | IO88PDB5V0       | 106        | VPUMP            |

| 36         | VCC              | 71         | VCC              | 100        | GNDQ             |

| 50         | 000              | L          | ·J               | 107        |                  |

|            | PQ208            |            | PQ208            | PQ208      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3PE600 Function | Pin Number | A3PE600 Function | Pin Number | A3PE600 Function |

| 108        | TDO              | 144        | IO47PDB2V1       | 180        | IO19NPB0V2       |

| 109        | TRST             | 145        | IO44NDB2V1       | 181        | IO18NPB0V2       |

| 110        | VJTAG            | 146        | IO44PDB2V1       | 182        | IO17PPB0V2       |

| 111        | VMV3             | 147        | IO43NDB2V0       | 183        | IO16PPB0V2       |

| 112        | GDA0/IO67NPB3V1  | 148        | IO43PDB2V0       | 184        | IO17NPB0V2       |

| 113        | GDB0/IO66NPB3V1  | 149        | IO40NDB2V0       | 185        | IO16NPB0V2       |

| 114        | GDA1/IO67PPB3V1  | 150        | IO40PDB2V0       | 186        | VCCIB0           |

| 115        | GDB1/IO66PPB3V1  | 151        | GBC2/IO38PSB2V0  | 187        | VCC              |

| 116        | GDC0/IO65NDB3V1  | 152        | GBA2/IO36PSB2V0  | 188        | IO15PDB0V2       |

| 117        | GDC1/IO65PDB3V1  | 153        | GBB2/IO37PSB2V0  | 189        | IO15NDB0V2       |

| 118        | IO62NDB3V1       | 154        | VMV2             | 190        | IO13PDB0V2       |

| 119        | IO62PDB3V1       | 155        | GNDQ             | 191        | IO13NDB0V2       |

| 120        | IO58NDB3V0       | 156        | GND              | 192        | IO11PSB0V1       |

| 121        | IO58PDB3V0       | 157        | VMV1             | 193        | IO09PDB0V1       |

| 122        | GND              | 158        | GNDQ             | 194        | IO09NDB0V1       |

| 123        | VCCIB3           | 159        | GBA1/IO35PDB1V1  | 195        | GND              |

| 124        | GCC2/IO55PSB3V0  | 160        | GBA0/IO35NDB1V1  | 196        | IO07PDB0V1       |

| 125        | GCB2/IO54PSB3V0  | 161        | GBB1/IO34PDB1V1  | 197        | IO07NDB0V1       |

| 126        | NC               | 162        | GND              | 198        | IO05PDB0V0       |

| 127        | IO53NDB3V0       | 163        | GBB0/IO34NDB1V1  | 199        | IO05NDB0V0       |

| 128        | GCA2/IO53PDB3V0  | 164        | GBC1/IO33PDB1V1  | 200        | VCCIB0           |

| 129        | GCA1/IO52PPB3V0  | 165        | GBC0/IO33NDB1V1  | 201        | GAC1/IO02PDB0V0  |

| 130        | GND              | 166        | IO31PDB1V1       | 202        | GAC0/IO02NDB0V0  |

| 131        | VCCPLC           | 167        | IO31NDB1V1       | 203        | GAB1/IO01PDB0V0  |

| 132        | GCA0/IO52NPB3V0  | 168        | IO27PDB1V0       | 204        | GAB0/IO01NDB0V0  |

| 133        | VCOMPLC          | 169        | IO27NDB1V0       | 205        | GAA1/IO00PDB0V0  |

| 134        | GCB0/IO51NDB2V1  | 170        | VCCIB1           | 206        | GAA0/IO00NDB0V0  |

| 135        | GCB1/IO51PDB2V1  | 171        | VCC              | 207        | GNDQ             |

| 136        | GCC1/IO50PSB2V1  | 172        | IO23PPB1V0       | 208        | VMV0             |

| 137        | IO49NDB2V1       | 173        | IO22PSB1V0       |            |                  |

| 138        | IO49PDB2V1       | 174        | IO23NPB1V0       |            |                  |

| 139        | IO48PSB2V1       | 175        | IO21PDB1V0       |            |                  |

| 140        | VCCIB2           | 176        | IO21NDB1V0       |            |                  |

| 141        | GND              | 177        | IO19PPB0V2       |            |                  |

| 142        | VCC              | 178        | GND              |            |                  |

| 143        | IO47NDB2V1       | 179        | IO18PPB0V2       |            |                  |

## 🌜 Microsemi.

Package Pin Assignments

|            | PQ208             |            | PQ208             | PQ208      |                   |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function |

| 1          | GND               | 37         | IO184PDB6V2       | 73         | IO145NDB5V1       |

| 2          | GNDQ              | 38         | IO184NDB6V2       | 74         | IO145PDB5V1       |

| 3          | VMV7              | 39         | IO180PSB6V1       | 75         | IO143NDB5V1       |

| 4          | GAB2/IO220PSB7V3  | 40         | VCCIB6            | 76         | IO143PDB5V1       |

| 5          | GAA2/IO221PDB7V3  | 41         | GND               | 77         | IO137NDB5V0       |

| 6          | IO221NDB7V3       | 42         | IO176PDB6V1       | 78         | IO137PDB5V0       |

| 7          | GAC2/IO219PDB7V3  | 43         | IO176NDB6V1       | 79         | IO135NDB5V0       |

| 8          | IO219NDB7V3       | 44         | GEC1/IO169PDB6V0  | 80         | IO135PDB5V0       |

| 9          | IO215PDB7V3       | 45         | GEC0/IO169NDB6V0  | 81         | GND               |

| 10         | IO215NDB7V3       | 46         | GEB1/IO168PPB6V0  | 82         | IO131NDB4V2       |

| 11         | IO212PDB7V2       | 47         | GEA1/IO167PPB6V0  | 83         | IO131PDB4V2       |

| 12         | IO212NDB7V2       | 48         | GEB0/IO168NPB6V0  | 84         | IO129NDB4V2       |

| 13         | IO208PDB7V2       | 49         | GEA0/IO167NPB6V0  | 85         | IO129PDB4V2       |

| 14         | IO208NDB7V2       | 50         | VMV6              | 86         | IO127NDB4V2       |

| 15         | IO204PSB7V1       | 51         | GNDQ              | 87         | IO127PDB4V2       |

| 16         | VCC               | 52         | GND               | 88         | VCC               |

| 17         | GND               | 53         | VMV5              | 89         | VCCIB4            |

| 18         | VCCIB7            | 54         | GNDQ              | 90         | IO121NDB4V1       |

| 19         | IO200PDB7V1       | 55         | IO166NDB5V3       | 91         | IO121PDB4V1       |

| 20         | IO200NDB7V1       | 56         | GEA2/IO166PDB5V3  | 92         | IO119NDB4V1       |

| 21         | IO196PSB7V0       | 57         | IO165NDB5V3       | 93         | IO119PDB4V1       |

| 22         | GFC1/IO192PSB7V0  | 58         | GEB2/IO165PDB5V3  | 94         | IO113NDB4V0       |

| 23         | GFB1/IO191PDB7V0  | 59         | IO164NDB5V3       | 95         | GDC2/IO113PDB4V0  |

| 24         | GFB0/IO191NDB7V0  | 60         | GEC2/IO164PDB5V3  | 96         | IO112NDB4V0       |

| 25         | VCOMPLF           | 61         | IO163PSB5V3       | 97         | GND               |

| 26         | GFA0/IO190NPB6V2  | 62         | VCCIB5            | 98         | GDB2/IO112PDB4V0  |

| 27         | VCCPLF            | 63         | IO161PSB5V3       | 99         | GDA2/IO111PSB4V0  |

| 28         | GFA1/IO190PPB6V2  | 64         | IO157NDB5V2       | 100        | GNDQ              |

| 29         | GND               | 65         | GND               | 101        | ТСК               |

| 30         | GFA2/IO189PDB6V2  | 66         | IO157PDB5V2       | 102        | TDI               |

| 31         | IO189NDB6V2       | 67         | IO153NDB5V2       | 103        | TMS               |

| 32         | GFB2/IO188PPB6V2  | 68         | IO153PDB5V2       | 104        | VMV4              |

| 33         | GFC2/IO187PPB6V2  | 69         | IO149NDB5V1       | 105        | GND               |

| 34         | IO188NPB6V2       | 70         | IO149PDB5V1       | 106        | VPUMP             |

| 35         | IO187NPB6V2       | 71         | VCC               | 107        | GNDQ              |

| 36         | VCC               | 72         | VCCIB5            | 108        | TDO               |

# FG324

Note: This is the bottom view of the package.

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

## **Microsemi**

Package Pin Assignments

| FG484      |                   |  |  |  |

|------------|-------------------|--|--|--|

| Pin Number | A3PE1500 Function |  |  |  |

| V15        | IO112NDB4V0       |  |  |  |

| V16        | GDB2/IO112PDB4V0  |  |  |  |

| V17        | TDI               |  |  |  |

| V18        | GNDQ              |  |  |  |

| V19        | TDO               |  |  |  |

| V20        | GND               |  |  |  |

| V21        | NC                |  |  |  |

| V22        | IO105NDB3V2       |  |  |  |

| W1         | NC                |  |  |  |

| W2         | NC                |  |  |  |

| W3         | NC                |  |  |  |

| W4         | GND               |  |  |  |

| W5         | IO165NDB5V3       |  |  |  |

| W6         | GEB2/IO165PDB5V3  |  |  |  |

| W7         | IO164NDB5V3       |  |  |  |

| W8         | IO153NDB5V2       |  |  |  |

| W9         | IO153PDB5V2       |  |  |  |

| W10        | IO147NDB5V1       |  |  |  |

| W11        | IO133NDB4V2       |  |  |  |

| W12        | IO130NDB4V2       |  |  |  |

| W13        | IO130PDB4V2       |  |  |  |

| W14        | IO113NDB4V0       |  |  |  |

| W15        | GDC2/IO113PDB4V0  |  |  |  |

| W16        | IO111NDB4V0       |  |  |  |

| W17        | GDA2/IO111PDB4V0  |  |  |  |

| W18        | TMS               |  |  |  |

| W19        | GND               |  |  |  |

| W20        | NC                |  |  |  |

| W21        | NC                |  |  |  |

| W22        | NC                |  |  |  |

| Y1         | VCCIB6            |  |  |  |

| Y2         | NC                |  |  |  |

| Y3         | NC                |  |  |  |

| Y4         | IO161NDB5V3       |  |  |  |

| Y5         | GND               |  |  |  |

| Y6         | IO163NDB5V3       |  |  |  |

| FG484      |                   |  |  |  |

|------------|-------------------|--|--|--|

| Pin Number | A3PE1500 Function |  |  |  |

| Y7         | IO163PDB5V3       |  |  |  |

| Y8         | VCC               |  |  |  |

| Y9         | VCC               |  |  |  |

| Y10        | IO147PDB5V1       |  |  |  |

| Y11        | IO133PDB4V2       |  |  |  |

| Y12        | IO131NPB4V2       |  |  |  |

| Y13        | NC                |  |  |  |

| Y14        | VCC               |  |  |  |

| Y15        | VCC               |  |  |  |

| Y16        | NC                |  |  |  |

| Y17        | NC                |  |  |  |

| Y18        | GND               |  |  |  |

| Y19        | NC                |  |  |  |

| Y20        | NC                |  |  |  |

| Y21        | NC                |  |  |  |

| Y22        | VCCIB3            |  |  |  |

# FG676

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

|            | FG676             |            | FG676             |            | FG676             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function |

| L17        | GND               | N1         | GFB0/IO191NPB7V0  | P11        | GND               |

| L18        | VCC               | N2         | VCOMPLF           | P12        | GND               |

| L19        | VCCIB2            | N3         | GFB1/IO191PPB7V0  | P13        | GND               |

| L20        | IO67PDB2V1        | N4         | IO196PDB7V0       | P14        | GND               |

| L21        | IO67NDB2V1        | N5         | GFA0/IO190NDB6V2  | P15        | GND               |

| L22        | IO71PDB2V2        | N6         | IO200PDB7V1       | P16        | GND               |

| L23        | IO71NDB2V2        | N7         | IO200NDB7V1       | P17        | GND               |

| L24        | GNDQ              | N8         | VCCIB7            | P18        | VCC               |

| L25        | IO82PDB2V3        | N9         | VCC               | P19        | VCCIB3            |

| L26        | IO84NDB2V3        | N10        | GND               | P20        | GCC0/IO85NDB2V3   |

| M1         | IO198NPB7V0       | N11        | GND               | P21        | GCC1/IO85PDB2V3   |

| M2         | IO202PDB7V1       | N12        | GND               | P22        | GCB1/IO86PPB2V3   |

| M3         | IO202NDB7V1       | N13        | GND               | P23        | IO88NPB3V0        |

| M4         | IO206NDB7V1       | N14        | GND               | P24        | GCA1/IO87PDB3V0   |

| M5         | IO206PDB7V1       | N15        | GND               | P25        | VCCPLC            |

| M6         | IO204NDB7V1       | N16        | GND               | P26        | VCOMPLC           |

| M7         | IO204PDB7V1       | N17        | GND               | R1         | IO189NDB6V2       |

| M8         | VCCIB7            | N18        | VCC               | R2         | IO185PDB6V2       |

| M9         | VCC               | N19        | VCCIB2            | R3         | IO187NPB6V2       |

| M10        | GND               | N20        | IO79PDB2V3        | R4         | IO193NPB7V0       |

| M11        | GND               | N21        | IO79NDB2V3        | R5         | GFC2/IO187PPB6V2  |

| M12        | GND               | N22        | GCA2/IO88PPB3V0   | R6         | GFC1/IO192PDB7V0  |

| M13        | GND               | N23        | IO81NPB2V3        | R7         | GFC0/IO192NDB7V0  |

| M14        | GND               | N24        | GCA0/IO87NDB3V0   | R8         | VCCIB6            |

| M15        | GND               | N25        | GCB0/IO86NPB2V3   | R9         | VCC               |

| M16        | GND               | N26        | IO83NDB2V3        | R10        | GND               |

| M17        | GND               | P1         | GFA2/IO189PDB6V2  | R11        | GND               |

| M18        | VCC               | P2         | VCCPLF            | R12        | GND               |

| M19        | VCCIB2            | P3         | IO193PPB7V0       | R13        | GND               |

| M20        | IO73NDB2V2        | P4         | IO196NDB7V0       | R14        | GND               |

| M21        | IO73PDB2V2        | P5         | GFA1/IO190PDB6V2  | R15        | GND               |

| M22        | IO81PPB2V3        | P6         | IO194PDB7V0       | R16        | GND               |

| M23        | IO77PDB2V2        | P7         | IO194NDB7V0       | R17        | GND               |

| M24        | IO77NDB2V2        | P8         | VCCIB6            | R18        | VCC               |

| M25        | IO82NDB2V3        | P9         | VCC               | R19        | VCCIB3            |

| M26        | IO83PDB2V3        | P10        | GND               | R20        | NC                |

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Revision 10<br>(March 2012) | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34669).                                                                                                                                                                                                                      | I, 1-1     |

|                             | The Y security option and Licensed DPA Logo were added to the "ProASIC3E Ordering Information" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 34727).                                                                                                                                                                                                                                  | III        |

|                             | The following sentence was removed from the "Advanced Architecture" section:<br>"In addition, extensive on-chip programming circuitry allows for rapid, single-<br>voltage (3.3 V) programming of IGLOOe devices via an IEEE 1532 JTAG<br>interface" (SAR 34689).                                                                                                                                                                                                                         | 1-3        |

|                             | The "Specifying I/O States During Programming" section is new (SAR 34699).                                                                                                                                                                                                                                                                                                                                                                                                                | 1-6        |

|                             | VCCPLL in Table 2-2 • Recommended Operating Conditions <sup>1</sup> was corrected from "1.4 to 1.6 V" to "1.425 to 1.575 V" (SAR 33851).                                                                                                                                                                                                                                                                                                                                                  | 2-2        |

| rer                         | The T <sub>J</sub> symbol was added to the table and notes regarding T <sub>A</sub> and T <sub>J</sub> were removed. The second of two parameters in the VCCI and VMV row, called "3.3 V DC supply voltage," was corrected to "3.0 V DC supply voltage" (SAR 37227).                                                                                                                                                                                                                      |            |

|                             | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—P <sub>CLOCK</sub> " section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>ProASIC3E FPGA Fabric User's Guide</i> (SAR 34735).                                                                                                                                                                                                   | 2-9        |

|                             | $t_{\text{DOUT}}$ was corrected to $t_{\text{DIN}}$ in Figure 2-3 $\bullet$ Input Buffer Timing Model and Delays (example) (SAR 37109).                                                                                                                                                                                                                                                                                                                                                   | 2-13       |

|                             | The typo related to the values for 3.3 V LVCMOS Wide Range in Table 2-17<br>• Summary of I/O Timing Characteristics—Software Default Settings was<br>corrected (SAR 37227).                                                                                                                                                                                                                                                                                                               | 2-19       |

|                             | The notes regarding drive strength in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section and "3.3 V LVCMOS Wide Range" section and tables were revised for clarification. They now state that the minimum drive strength for the default software configuration when run in wide range is $\pm 100 \ \mu$ A. The drive strength displayed in software is supported in normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 34763). | 2-18, 2-27 |

| Revision                    | Changes                                                                                                                                                                              | Page |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advance v0.5<br>(continued) | The "RESET" section was updated.                                                                                                                                                     | 2-25 |

|                             | The "RESET" section was updated.                                                                                                                                                     | 2-27 |

|                             | The "Introduction" of the "Introduction" section was updated.                                                                                                                        | 2-28 |

|                             | PCI-X 3.3 V was added to the Compatible Standards for 3.3 V in Table 2-<br>11 • VCCI Voltages and Compatible Standards                                                               | 2-29 |

|                             | Table 2-35 • ProASIC3E I/O Features was updated.                                                                                                                                     | 2-54 |

|                             | The "Double Data Rate (DDR) Support" section was updated to include information concerning implementation of the feature.                                                            | 2-32 |

|                             | The "Electrostatic Discharge (ESD) Protection" section was updated to include testing information.                                                                                   | 2-35 |

|                             | Level 3 and 4 descriptions were updated in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices.                                                       | 2-64 |

|                             | The notes in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices were updated.                                                                       | 2-64 |

|                             | The "Simultaneous Switching Outputs (SSOs) and Printed Circuit Board Layout" section is new.                                                                                         | 2-41 |

|                             | A footnote was added to Table 2-37 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected). | 2-55 |

|                             | Table 2-48 • ProASIC3E I/O Attributes vs. I/O Standard Applications                                                                                                                  | 2-81 |

|                             | Table 2-55 • ProASIC3 I/O Standards—SLEW and Output Drive (OUT_DRIVE) Settings                                                                                                       | 2-85 |

|                             | The "x" was updated in the "Pin Descriptions" section.                                                                                                                               | 2-50 |

|                             | The "VCC Core Supply Voltage" pin description was updated.                                                                                                                           | 2-50 |

|                             | The "VMVx I/O Supply Voltage (quiet)" pin description was updated to include information concerning leaving the pin unconnected.                                                     | 2-50 |

|                             | EXTFB was removed from Figure 2-24 • ProASIC3E CCC Options.                                                                                                                          | 2-24 |

|                             | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-13 • ProASIC3E CCC/PLL Specification.                                                          | 2-30 |

|                             | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                                                                                  | 2-28 |

|                             | The LVPECL specification in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices was updated.                                                         | 2-64 |

|                             | Table 2-15 • Levels of Hot-Swap Support was updated.                                                                                                                                 | 2-34 |

|                             | The "Cold-Sparing Support" section was updated.                                                                                                                                      | 2-34 |

|                             | "Electrostatic Discharge (ESD) Protection" section was updated.                                                                                                                      | 2-35 |

|                             | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                                                                                   | 2-50 |

|                             | The "VJTAG JTAG Supply Voltage" pin description was updated.                                                                                                                         | 2-50 |

|                             | The "VPUMP Programming Supply Voltage" pin description was updated to include information on what happens when the pin is tied to ground.                                            | 2-50 |

# **Datasheet Categories**

## Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "ProASIC3E Device Status" table on page II, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

## **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

## Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

## Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

## Production

This version contains information that is considered to be final.

## **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at *Microsemi SoC Reliability Report*. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.