Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                     |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 516096                                                                       |

| Number of I/O                  | 147                                                                          |

| Number of Gates                | 300000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 208-BFQFP                                                                    |

| Supplier Device Package        | 208-PQFP (28x28)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000-1pq208i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ProASIC3E Device Family Overview

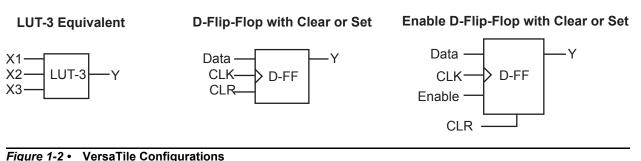

#### VersaTiles

The ProASIC3E core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The ProASIC3E VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-2 for VersaTile configurations.

#### User Nonvolatile FlashROM

ProASIC3E devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Internet protocol addressing (wireless or fixed)

- System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- Version management

The FlashROM is written using the standard ProASIC3E IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks, as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The ProASIC3E development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

# **Thermal Characteristics**

#### Introduction

The temperature variable in Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because dynamic and static power consumption cause the chip junction to be higher than the ambient temperature.

EQ 1 can be used to calculate junction temperature.

$T_J$  = Junction Temperature =  $\Delta T + T_A$

where:

T<sub>A</sub> = Ambient Temperature

$\Delta T$  = Temperature gradient between junction (silicon) and ambient  $\Delta T$  =  $\theta_{ia}$  \* P

$\theta_{ja}$  = Junction-to-ambient of the package.  $\theta_{ja}$  numbers are located in Table 2-5.

P = Power dissipation

#### Package Thermal Characteristics

The device junction-to-case thermal resistivity is  $\theta_{jc}$  and the junction-to-ambient air thermal resistivity is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown for two air flow rates. The absolute maximum junction temperature is 110°C. EQ 2 shows a sample calculation of the absolute maximum power dissipation allowed for an 896-pin FBGA package at commercial temperature and in still air.

Maximum Power Allowed =

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{ja}(°C/W)} = \frac{110°C - 70°C}{13.6°C/W} = 5.88 \text{ W}$$

|                                                                             |           |               | $	heta_{ja}$ |              |              |       |

|-----------------------------------------------------------------------------|-----------|---------------|--------------|--------------|--------------|-------|

| Package Type                                                                | Pin Count | $\theta_{jc}$ | Still Air    | 200 ft./min. | 500 ft./min. | Units |

| Plastic Quad Flat Package (PQFP)                                            | 208       | 8.0           | 26.1         | 22.5         | 20.8         | C/W   |

| Plastic Quad Flat Package (PQFP) with<br>embedded heat spreader in A3PE3000 | 208       | 3.8           | 16.2         | 13.3         | 11.9         | C/W   |

| Fine Pitch Ball Grid Array (FBGA)                                           | 256       | 3.8           | 26.9         | 22.8         | 21.5         | C/W   |

|                                                                             | 484       | 3.2           | 20.5         | 17.0         | 15.9         | C/W   |

|                                                                             | 676       | 3.2           | 16.4         | 13.0         | 12.0         | C/W   |

|                                                                             | 896       | 2.4           | 13.6         | 10.4         | 9.4          | C/W   |

#### Table 2-5 • Package Thermal Resistivities

### Temperature and Voltage Derating Factors

Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to  $T_J = 70^{\circ}$ C, VCC = 1.425 V)

| Array Voltage |       | Junction Temperature (°C) |      |      |      |       |  |  |  |  |  |

|---------------|-------|---------------------------|------|------|------|-------|--|--|--|--|--|

| VCC (V)       | –40°C | 0°C                       | 25°C | 70°C | 85°C | 100°C |  |  |  |  |  |

| 1.425         | 0.87  | 0.92                      | 0.95 | 1.00 | 1.02 | 1.04  |  |  |  |  |  |

| 1.500         | 0.83  | 0.88                      | 0.90 | 0.95 | 0.97 | 0.98  |  |  |  |  |  |

| 1.575         | 0.80  | 0.85                      | 0.87 | 0.92 | 0.93 | 0.95  |  |  |  |  |  |

EQ 1

EQ 2

### Power Calculation Methodology

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero SoC software.

The power calculation methodology described below uses the following variables:

- The number of PLLs as well as the number and the frequency of each output clock generated

- The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- The number and the standard of I/O pins used in the design

- The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-11 on page 2-11.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-12 on page 2-11.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-12 on page 2-11. The calculation should be repeated for each clock domain defined in the design.

#### Methodology

#### Total Power Consumption—PTOTAL

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—P<sub>STAT</sub>

P<sub>STAT</sub> = PDC1 + N<sub>INPUTS</sub> \* PDC2 + N<sub>OUTPUTS</sub> \* PDC3

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

#### Total Dynamic Power Consumption—P<sub>DYN</sub>

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub>

#### Global Clock Contribution—P<sub>CLOCK</sub>

P<sub>CLOCK</sub> = (PAC1 + N<sub>SPINE</sub> \* PAC2 + N<sub>ROW</sub> \* PAC3 + N<sub>S-CELL</sub> \* PAC4) \* F<sub>CLK</sub>

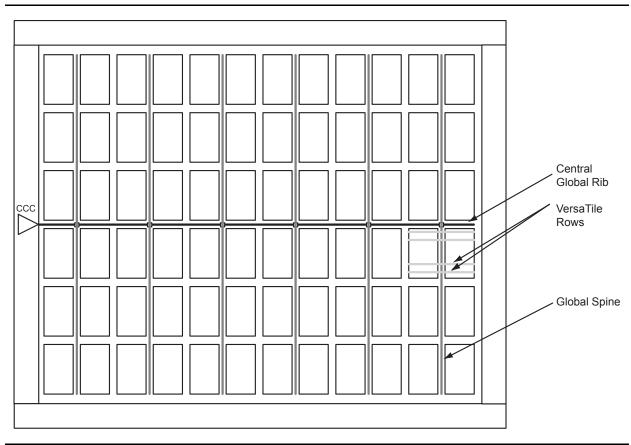

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3E FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *ProASIC3E FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

PAC1, PAC2, PAC3, and PAC4 are device-dependent.

#### Sequential Cells Contribution—P<sub>S-CELL</sub>

$P_{S-CELL}$  =  $N_{S-CELL}$  \* (PAC5 +  $\alpha_1$  / 2 \* PAC6) \*  $F_{CLK}$

$N_{S\text{-}CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_1$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-11 on page 2-11.

F<sub>CLK</sub> is the global clock signal frequency.

ProASIC3E DC and Switching Characteristics

# **User I/O Characteristics**

# **Timing Model**

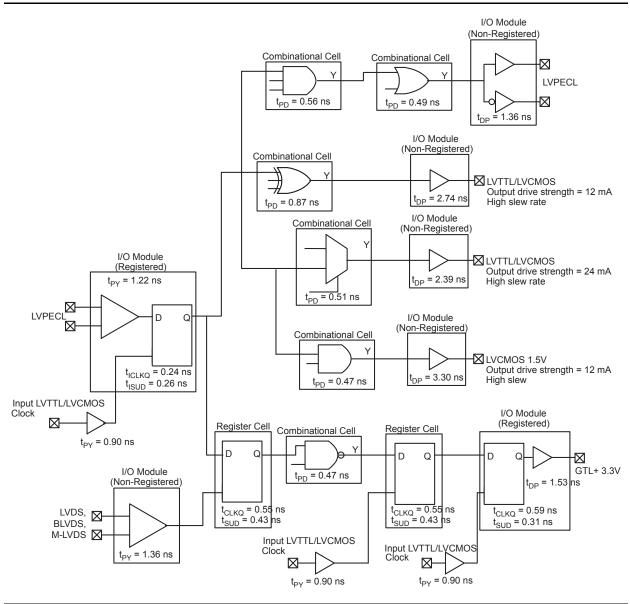

Figure 2-2 • Timing Model Operating Conditions: –2 Speed, Commercial Temperature Range (T<sub>J</sub> = 70°C), Worst-Case VCC = 1.425 V

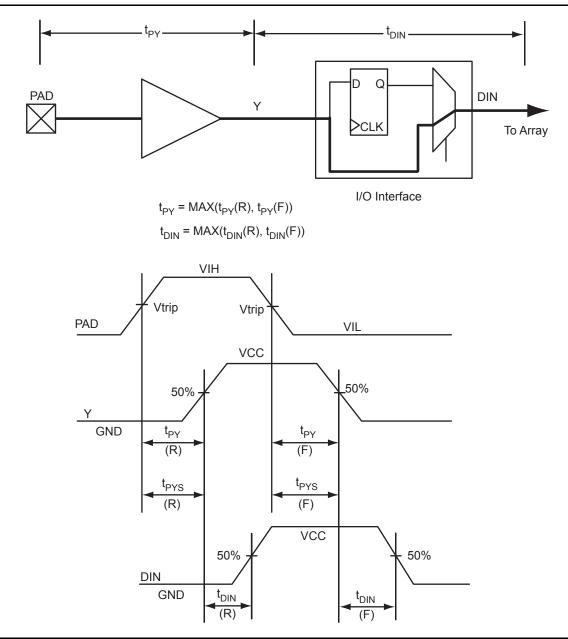

Figure 2-3 • Input Buffer Timing Model and Delays (example)

| Temperature | Time before Failure |

|-------------|---------------------|

| 85°C        | 2 years             |

| 100°C       | 6 months            |

### Table 2-23 • Schmitt Trigger Input Hysteresis

#### Hysteresis Voltage Value (typ.) for Schmitt Mode Input Buffers

| Input Buffer Configuration                          | Hysteresis Value (typ.) |

|-----------------------------------------------------|-------------------------|

| 3.3 V LVTTL/LVCMOS/PCI/PCI-X (Schmitt trigger mode) | 240 mV                  |

| 2.5 V LVCMOS (Schmitt trigger mode)                 | 140 mV                  |

| 1.8 V LVCMOS (Schmitt trigger mode)                 | 80 mV                   |

| 1.5 V LVCMOS (Schmitt trigger mode)                 | 60 mV                   |

#### Table 2-24 • I/O Input Rise Time, Fall Time, and Related I/O Reliability\*

| Input Buffer                               | Input Rise/Fall Time<br>(min.) | Input Rise/Fall Time (max.)                                                     | Reliability         |

|--------------------------------------------|--------------------------------|---------------------------------------------------------------------------------|---------------------|

| LVTTL/LVCMOS<br>(Schmitt trigger disabled) | No requirement                 | 10 ns *                                                                         | 20 years<br>(110°C) |

| LVTTL/LVCMOS<br>(Schmitt trigger enabled)  |                                | No requirement, but input noise<br>voltage cannot exceed Schmitt<br>hysteresis. | · <b>)</b> · · ·    |

| HSTL/SSTL/GTL                              | No requirement                 | 10 ns *                                                                         | 10 years<br>(100°C) |

| LVDS/B-LVDS/M-LVDS/<br>LVPECL              | No requirement                 | 10 ns *                                                                         | 10 years<br>(100°C) |

Note: \*For clock signals and similar edge-generating signals, refer to the "ProASIC3/E SSO and Pin Placement Guidelines" chapter of the ProASIC3E FPGA Fabric User's Guide. The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low, then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the rise/fall times, the more susceptible the input signal is to the board noise. Microsemi recommends signal integrity evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

# Kicrosemi.

ProASIC3E DC and Switching Characteristics

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 12 mA             | Std.           | 0.66              | 6.03            | 0.04             | 1.20            | 1.57             | 0.43              | 6.14            | 5.02            | 3.28            | 3.47            | 8.37             | 7.26             | ns    |

|                   | -1             | 0.56              | 5.13            | 0.04             | 1.02            | 1.33             | 0.36              | 5.22            | 4.27            | 2.79            | 2.95            | 7.12             | 6.17             | ns    |

|                   | -2             | 0.49              | 4.50            | 0.03             | 0.90            | 1.17             | 0.32              | 4.58            | 3.75            | 2.45            | 2.59            | 6.25             | 5.42             | ns    |

| 16 mA             | Std.           | 0.66              | 5.62            | 0.04             | 1.20            | 1.57             | 0.43              | 5.72            | 4.72            | 3.32            | 3.58            | 7.96             | 6.96             | ns    |

|                   | -1             | 0.56              | 4.78            | 0.04             | 1.02            | 1.33             | 0.36              | 4.87            | 4.02            | 2.83            | 3.04            | 6.77             | 5.92             | ns    |

|                   | -2             | 0.49              | 4.20            | 0.03             | 0.90            | 1.17             | 0.32              | 4.27            | 3.53            | 2.48            | 2.67            | 5.94             | 5.20             | ns    |

| 24 mA             | Std.           | 0.66              | 5.24            | 0.04             | 1.20            | 1.57             | 0.43              | 5.34            | 4.69            | 3.39            | 3.96            | 7.58             | 6.93             | ns    |

|                   | -1             | 0.56              | 4.46            | 0.04             | 1.02            | 1.33             | 0.36              | 4.54            | 3.99            | 2.88            | 3.37            | 6.44             | 5.89             | ns    |

|                   | -2             | 0.49              | 3.92            | 0.03             | 0.90            | 1.17             | 0.32              | 3.99            | 3.50            | 2.53            | 2.96            | 5.66             | 5.17             | ns    |

#### Table 2-28 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

ProASIC3E DC and Switching Characteristics

### 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-51 • Minimum and Maximum DC Input and Output Levels

| 2.5 GTL            |            | VIL         | VIH         |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|--------------------|------------|-------------|-------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength  | Min.,<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 20 mA <sup>3</sup> | -0.3       | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | _         | 20  | 20 | 124                     | 169                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

3. Output drive strength is below JEDEC specification.

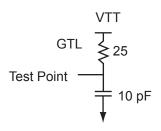

#### Figure 2-13 • AC Loading

#### Table 2-52 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Input High (V) Measuring VREF (typ. |     | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------------------|-----|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                                 | 0.8 | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-53 • 2.5 V GTL

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.13            | 0.04             | 2.46            | 0.43              | 2.16            | 2.13            |                 |                 | 4.40             | 4.36             | ns    |

| -1             | 0.51              | 1.81            | 0.04             | 2.09            | 0.36              | 1.84            | 1.81            |                 |                 | 3.74             | 3.71             | ns    |

| -2             | 0.45              | 1.59            | 0.03             | 1.83            | 0.32              | 1.61            | 1.59            |                 |                 | 3.28             | 3.26             | ns    |

#### HSTL Class I

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). ProASIC3E devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| HSTL Class I      |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 8 mA              | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI - 0.4 | 8   | 8  | 39                      | 32                      | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

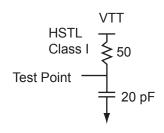

#### Figure 2-16 • AC Loading

#### Table 2-61 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point*<br>(V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                    | 0.75            | 0.75           | 20                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

#### Timing Characteristics

Table 2-62 • HSTL Class I

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = .4 V, VREF = 0.75 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 3.18            | 0.04             | 2.12            | 0.43              | 3.24            | 3.14            |                 |                 | 5.47             | 5.38             | ns    |

| -1             | 0.56              | 2.70            | 0.04             | 1.81            | 0.36              | 2.75            | 2.67            |                 |                 | 4.66             | 4.58             | ns    |

| -2             | 0.49              | 2.37            | 0.03             | 1.59            | 0.32              | 2.42            | 2.35            |                 |                 | 4.09             | 4.02             | ns    |

### **Differential I/O Characteristics**

#### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by the Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and DDR. However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

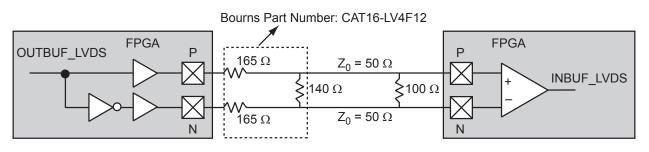

#### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-22. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, ProASIC3E also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-22 • LVDS Circuit Diagram and Board-Level Implementation

# **Global Resource Characteristics**

### A3PE600 Clock Tree Topology

Clock delays are device-specific. Figure 2-38 is an example of a global tree used for clock routing. The global tree presented in Figure 2-38 is driven by a CCC located on the west side of the A3PE600 device. It is used to drive all D-flip-flops in the device.

Figure 2-38 • Example of Global Tree Use in an A3PE600 Device for Clock Routing

### **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-70. Table 2-95 on page 2-69, Table 2-96 on page 2-69, and Table 2-97 on page 2-69 present minimum and maximum global clock delays within the device. Minimum and maximum delays are measured with minimum and maximum loading.

**Wicrosemi**. ProASIC3E DC and Switching Characteristics

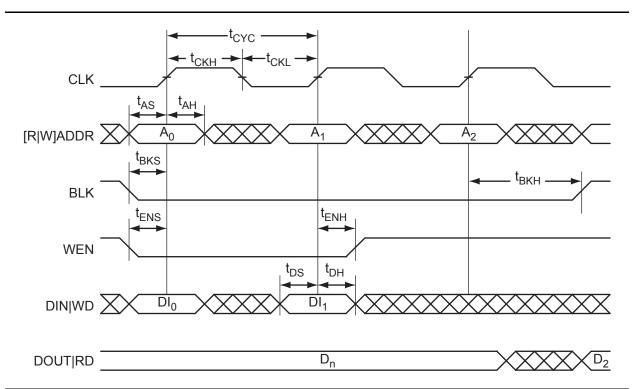

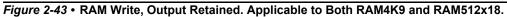

Figure 2-44 • RAM Write, Output as Write Data. Applicable to RAM4K9 Only.

ProASIC3E DC and Switching Characteristics

### **Timing Characteristics**

#### Table 2-99 • RAM4K9

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -2   | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.14 | 0.16 | 0.19 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 0.23 | 0.27 | 0.31 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 1.79 | 2.03 | 2.39 | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Closing Edge        | 0.33 | 0.28 | 0.25 | ns    |

| t <sub>C2CWWH</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Rising Edge         | 0.30 | 0.26 | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.45 | 0.38 | 0.34 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.49 | 0.42 | 0.37 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DO (flow-through)                                                                      | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to Data Out Low on DO (pipelined)                                                                         | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

ProASIC3E DC and Switching Characteristics

# **Timing Characteristics**

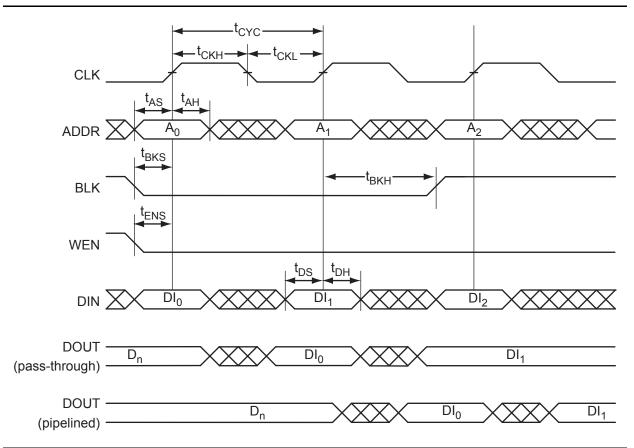

#### Table 2-101 • FIFO

Commercial-Case Conditions:  $T_J = 70^{\circ}C$ , VCC = 1.425 V

| Parameter            | Description                                       | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------|------|------|------|-------|

| t <sub>ENS</sub>     | REN, WEN Setup Time                               | 1.38 | 1.57 | 1.84 | ns    |

| t <sub>ENH</sub>     | REN, WEN Hold Time                                | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>BKS</sub>     | BLK Setup Time                                    | 0.19 | 0.22 | 0.26 | ns    |

| t <sub>BKH</sub>     | BLK Hold Time                                     | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DS</sub>      | Input Data (WD) Setup Time                        | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>      | Input Data (WD) Hold Time                         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>    | Clock High to New Data Valid on RD (pass-through) | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>    | Clock High to New Data Valid on RD (pipelined)    | 0.89 | 1.02 | 1.20 | ns    |

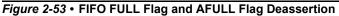

| t <sub>RCKEF</sub>   | RCLK High to Empty Flag Valid                     | 1.72 | 1.96 | 2.30 | ns    |

| t <sub>WCKFF</sub>   | WCLK High to Full Flag Valid                      | 1.63 | 1.86 | 2.18 | ns    |

| t <sub>CKAF</sub>    | Clock High to Almost Empty/Full Flag Valid        | 6.19 | 7.05 | 8.29 | ns    |

| t <sub>RSTFG</sub>   | RESET Low to Empty/Full Flag Valid                | 1.69 | 1.93 | 2.27 | ns    |

| t <sub>RSTAF</sub>   | RESET Low to Almost Empty/Full Flag Valid         | 6.13 | 6.98 | 8.20 | ns    |

| t <sub>RSTBQ</sub>   | RESET Low to Data Out Low on RD (pass-through)    | 0.92 | 1.05 | 1.23 | ns    |

|                      | RESET Low to Data Out Low on RD (pipelined)       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub> | RESET Removal                                     | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub> | RESET Recovery                                    | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub> | RESET Minimum Pulse Width                         | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>     | Clock Cycle Time                                  | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>     | Maximum Frequency                                 | 310  | 272  | 231  | MHz   |

# 3 – Pin Descriptions and Packaging

# **Supply Pins**

#### GND

#### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

#### GNDQ

#### Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

#### **Core Supply Voltage**

Supply voltage to the FPGA core, nominally 1.5 V. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

#### VCCIBx

#### I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are up to eight I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. In general, unused I/O banks should have their corresponding VCCIX pins tied to GND. If an output pad is terminated to ground through any resistor and if the corresponding VCCIX is left floating, then the leakage current to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 0uA. However, if an output pad is terminated to ground is ~ 3 uA. For unused banks the aforementioned behavior is to be taken into account while deciding if it's better to float VCCIX of unused bank or tie it to GND.

#### VMVx

#### I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

#### VCCPLA/B/C/D/E/F

#### PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V.

When the PLLs are not used, the place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *ProASIC3E FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There are six VCCPLX pins on ProASIC3E devices.

#### VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There are six VCOMPL pins (PLL ground) on ProASIC3E devices.

# **Microsemi**

Package Pin Assignments

|            | PQ208            |            | PQ208            |            | PQ208            |  |  |  |

|------------|------------------|------------|------------------|------------|------------------|--|--|--|

| Pin Number | A3PE600 Function | Pin Number | A3PE600 Function | Pin Number | A3PE600 Function |  |  |  |

| 1          | GND              | 37         | IO112PDB6V1      | 72         | VCCIB5           |  |  |  |

| 2          | GNDQ             | 38         | IO112NDB6V1      | 73         | IO85NPB5V0       |  |  |  |

| 3          | VMV7             | 39         | IO108PSB6V0      | 74         | IO84NPB5V0       |  |  |  |

| 4          | GAB2/IO133PSB7V1 | 40         | VCCIB6           | 75         | IO85PPB5V0       |  |  |  |

| 5          | GAA2/IO134PDB7V1 | 41         | GND              | 76         | IO84PPB5V0       |  |  |  |

| 6          | IO134NDB7V1      | 42         | IO106PDB6V0      | 77         | IO83NPB5V0       |  |  |  |

| 7          | GAC2/IO132PDB7V1 | 43         | IO106NDB6V0      | 78         | IO82NPB5V0       |  |  |  |

| 8          | IO132NDB7V1      | 44         | GEC1/IO104PDB6V0 | 79         | IO83PPB5V0       |  |  |  |

| 9          | IO130PDB7V1      | 45         | GEC0/IO104NDB6V  | 80         | IO82PPB5V0       |  |  |  |

| 10         | IO130NDB7V1      |            | 0                | 81         | GND              |  |  |  |

| 11         | IO127PDB7V1      | 46         | GEB1/IO103PPB6V0 | 82         | IO80NDB4V1       |  |  |  |

| 12         | IO127NDB7V1      | 47         | GEA1/IO102PPB6V0 | 83         | IO80PDB4V1       |  |  |  |

| 13         | IO126PDB7V0      | 48         | GEB0/IO103NPB6V0 | 84         | IO79NPB4V1       |  |  |  |

| 14         | IO126NDB7V0      | 49         | GEA0/IO102NPB6V0 | 85         | IO78NPB4V1       |  |  |  |

| 15         | IO124PSB7V0      | 50         | VMV6             | 86         | IO79PPB4V1       |  |  |  |

| 16         | VCC              | 51         | GNDQ             | 87         | IO78PPB4V1       |  |  |  |

| 17         | GND              | 52         | GND              | 88         | VCC              |  |  |  |

| 18         | VCCIB7           | 53         | VMV5             | 89         | VCCIB4           |  |  |  |

| 19         | IO122PPB7V0      | 54         | GNDQ             | 90         | IO76NDB4V1       |  |  |  |

| 20         | IO121PSB7V0      | 55         | IO101NDB5V2      | 91         | IO76PDB4V1       |  |  |  |

| 21         | IO122NPB7V0      | 56         | GEA2/IO101PDB5V2 | 92         | IO72NDB4V0       |  |  |  |

| 22         | GFC1/IO120PSB7V0 | 57         | IO100NDB5V2      | 93         | IO72PDB4V0       |  |  |  |

| 23         | GFB1/IO119PDB7V0 | 58         | GEB2/IO100PDB5V2 | 94         | IO70NDB4V0       |  |  |  |

| 24         | GFB0/IO119NDB7V0 | 59         | IO99NDB5V2       | 95         | GDC2/IO70PDB4V0  |  |  |  |

| 25         | VCOMPLF          | 60         | GEC2/IO99PDB5V2  | 96         | IO68NDB4V0       |  |  |  |

| 26         | GFA0/IO118NPB6V1 | 61         | IO98PSB5V2       | 97         | GND              |  |  |  |

| 27         | VCCPLF           | 62         | VCCIB5           | 98         | GDA2/IO68PDB4V0  |  |  |  |

| 28         | GFA1/IO118PPB6V1 | 63         | IO96PSB5V2       | 99         | GDB2/IO69PSB4V0  |  |  |  |

| 29         | GND              | 64         | IO94NDB5V1       | 100        | GNDQ             |  |  |  |

| 30         | GFA2/IO117PDB6V1 | 65         | GND              | 101        | ТСК              |  |  |  |

| 31         | IO117NDB6V1      | 66         | IO94PDB5V1       | 102        | TDI              |  |  |  |

| 32         | GFB2/IO116PPB6V1 | 67         | IO92NDB5V1       | 103        | TMS              |  |  |  |

| 33         | GFC2/IO115PPB6V1 | 68         | IO92PDB5V1       | 104        | VMV4             |  |  |  |

| 34         | IO116NPB6V1      | 69         | IO88NDB5V0       | 105        | GND              |  |  |  |

| 35         | IO115NPB6V1      | 70         | IO88PDB5V0       | 106        | VPUMP            |  |  |  |

| 36         | VCC              | 71         | VCC              | 100        | GNDQ             |  |  |  |

| 50         | 000              | L          | ·J               | 107        |                  |  |  |  |

Package Pin Assignments

|            | PQ208             |            | PQ208             |            | PQ208             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| 1          | GND               | 40         | VCCIB6            | 79         | IO194NDB5V0       |

| 2          | GNDQ              | 41         | GND               | 80         | IO194PDB5V0       |

| 3          | VMV7              | 42         | IO244PDB6V1       | 81         | GND               |

| 4          | GAB2/IO308PSB7V4  | 43         | IO244NDB6V1       | 82         | IO184NDB4V3       |

| 5          | GAA2/IO309PDB7V4  | 44         | GEC1/IO236PDB6V0  | 83         | IO184PDB4V3       |

| 6          | IO309NDB7V4       | 45         | GEC0/IO236NDB6V0  | 84         | IO180NDB4V3       |

| 7          | GAC2/IO307PDB7V4  | 46         | GEB1/IO235PPB6V0  | 85         | IO180PDB4V3       |

| 8          | IO307NDB7V4       | 47         | GEA1/IO234PPB6V0  | 86         | IO176NDB4V2       |

| 9          | IO303PDB7V3       | 48         | GEB0/IO235NPB6V0  | 87         | IO176PDB4V2       |

| 10         | IO303NDB7V3       | 49         | GEA0/IO234NPB6V0  | 88         | VCC               |

| 11         | IO299PDB7V3       | 50         | VMV6              | 89         | VCCIB4            |

| 12         | IO299NDB7V3       | 51         | GNDQ              | 90         | IO170NDB4V2       |

| 13         | IO295PDB7V2       | 52         | GND               | 91         | IO170PDB4V2       |

| 14         | IO295NDB7V2       | 53         | VMV5              | 92         | IO166NDB4V1       |

| 15         | IO291PSB7V2       | 54         | GNDQ              | 93         | IO166PDB4V1       |

| 16         | VCC               | 55         | IO233NDB5V4       | 94         | IO156NDB4V0       |

| 17         | GND               | 56         | GEA2/IO233PDB5V4  | 95         | GDC2/IO156PDB4V0  |

| 18         | VCCIB7            | 57         | IO232NDB5V4       | 96         | IO154NPB4V0       |

| 19         | IO285PDB7V1       | 58         | GEB2/IO232PDB5V4  | 97         | GND               |

| 20         | IO285NDB7V1       | 59         | IO231NDB5V4       | 98         | GDB2/IO155PSB4V0  |

| 21         | IO279PSB7V0       | 60         | GEC2/IO231PDB5V4  | 99         | GDA2/IO154PPB4V0  |

| 22         | GFC1/IO275PSB7V0  | 61         | IO230PSB5V4       | 100        | GNDQ              |

| 23         | GFB1/IO274PDB7V0  | 62         | VCCIB5            | 101        | ТСК               |

| 24         | GFB0/IO274NDB7V0  | 63         | IO218NDB5V3       | 102        | TDI               |

| 25         | VCOMPLF           | 64         | IO218PDB5V3       | 103        | TMS               |

| 26         | GFA0/IO273NPB6V4  | 65         | GND               | 104        | VMV4              |

| 27         | VCCPLF            | 66         | IO214PSB5V2       | 105        | GND               |

| 28         | GFA1/IO273PPB6V4  | 67         | IO212NDB5V2       | 106        | VPUMP             |

| 29         | GND               | 68         | IO212PDB5V2       | 107        | GNDQ              |

| 30         | GFA2/IO272PDB6V4  | 69         | IO208NDB5V1       | 108        | TDO               |

| 31         | IO272NDB6V4       | 70         | IO208PDB5V1       | 109        | TRST              |

| 32         | GFB2/IO271PPB6V4  | 71         | VCC               | 110        | VJTAG             |

| 33         | GFC2/IO270PPB6V4  | 72         | VCCIB5            | 111        | VMV3              |

| 34         | IO271NPB6V4       | 73         | IO202NDB5V1       | 112        | GDA0/IO153NPB3V4  |

| 35         | IO270NPB6V4       | 74         | IO202PDB5V1       | 113        | GDB0/IO152NPB3V4  |

| 36         | VCC               | 75         | IO198NDB5V0       | 114        | GDA1/IO153PPB3V4  |

| 37         | IO252PDB6V2       | 76         | IO198PDB5V0       | 115        | GDB1/IO152PPB3V4  |

| 38         | IO252NDB6V2       | 77         | IO197NDB5V0       | 116        | GDC0/IO151NDB3V4  |

| 39         | IO248PSB6V1       | 78         | IO197PDB5V0       | 117        | GDC1/IO151PDB3V4  |

Package Pin Assignments

|            | FG896             |            | FG896             | FG896      |                   |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| AK28       | GND               | C5         | VCCIB0            | D11        | IO11PDB0V1        |

| AK29       | GND               | C6         | IO03PDB0V0        | D12        | IO23NDB0V2        |

| B1         | GND               | C7         | IO03NDB0V0        | D13        | IO23PDB0V2        |

| B2         | GND               | C8         | GAB1/IO01PDB0V0   | D14        | IO27PDB0V3        |

| B3         | GAA2/IO309PPB7V4  | C9         | IO05PDB0V0        | D15        | IO40PDB0V4        |

| B4         | VCC               | C10        | IO15NPB0V1        | D16        | IO47NDB1V0        |

| B5         | IO14PPB0V1        | C11        | IO25NDB0V3        | D17        | IO47PDB1V0        |

| B6         | VCC               | C12        | IO25PDB0V3        | D18        | IO55NPB1V1        |

| B7         | IO07PPB0V0        | C13        | IO31NPB0V3        | D19        | IO65NDB1V3        |

| B8         | IO09PDB0V1        | C14        | IO27NDB0V3        | D20        | IO65PDB1V3        |

| B9         | IO15PPB0V1        | C15        | IO39NDB0V4        | D21        | IO71NDB1V3        |

| B10        | IO19NDB0V2        | C16        | IO39PDB0V4        | D22        | IO71PDB1V3        |

| B11        | IO19PDB0V2        | C17        | IO55PPB1V1        | D23        | IO73NDB1V4        |

| B12        | IO29NDB0V3        | C18        | IO51PDB1V1        | D24        | IO73PDB1V4        |

| B13        | IO29PDB0V3        | C19        | IO59NDB1V2        | D25        | IO74NDB1V4        |

| B14        | IO31PPB0V3        | C20        | IO63NDB1V2        | D26        | GBB0/IO80NPB1V4   |

| B15        | IO37NDB0V4        | C21        | IO63PDB1V2        | D27        | GND               |

| B16        | IO37PDB0V4        | C22        | IO67NDB1V3        | D28        | GBA0/IO81NPB1V4   |

| B17        | IO41PDB1V0        | C23        | IO67PDB1V3        | D29        | VCC               |

| B18        | IO51NDB1V1        | C24        | IO75NDB1V4        | D30        | GBA2/IO82PPB2V0   |

| B19        | IO59PDB1V2        | C25        | IO75PDB1V4        | E1         | GND               |

| B20        | IO53PDB1V1        | C26        | VCCIB1            | E2         | IO303NPB7V3       |

| B21        | IO53NDB1V1        | C27        | IO64PPB1V2        | E3         | VCCIB7            |

| B22        | IO61NDB1V2        | C28        | VCC               | E4         | IO305PPB7V3       |

| B23        | IO61PDB1V2        | C29        | GBA1/IO81PPB1V4   | E5         | VCC               |

| B24        | IO69NPB1V3        | C30        | GND               | E6         | GAC0/IO02NDB0V0   |

| B25        | VCC               | D1         | IO303PPB7V3       | E7         | VCCIB0            |

| B26        | GBC0/IO79NPB1V4   | D2         | VCC               | E8         | IO06PPB0V0        |

| B27        | VCC               | D3         | IO305NPB7V3       | E9         | IO24NDB0V2        |

| B28        | IO64NPB1V2        | D4         | GND               | E10        | IO24PDB0V2        |

| B29        | GND               | D5         | GAA1/IO00PPB0V0   | E11        | IO13NDB0V1        |

| B30        | GND               | D6         | GAC1/IO02PDB0V0   | E12        | IO13PDB0V1        |

| C1         | GND               | D7         | IO06NPB0V0        | E13        | IO34NDB0V4        |

| C2         | IO309NPB7V4       | D8         | GAB0/IO01NDB0V0   | E14        | IO34PDB0V4        |

| C3         | VCC               | D9         | IO05NDB0V0        | E15        | IO40NDB0V4        |

| C4         | GAA0/IO00NPB0V0   | D10        | IO11NDB0V1        | E16        | IO49NDB1V1        |

| Revision             | Changes                                                                                                                                                                                                        | Page |  |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| v2.1<br>(continued)  | The words "ambient temperature" were added to the temperature range in the "Temperature Grade Offerings", "Speed Grade and Temperature Grade Matrix", and "Speed Grade and Temperature Grade Matrix" sections. | 1-1  |  |  |  |  |

|                      | The "Clock Conditioning Circuit (CCC) and PLL" section was updated.                                                                                                                                            |      |  |  |  |  |

|                      | The caption "Main (chip)" in Figure 2-9 • Overview of Automotive ProASIC3 VersaNet Global Network was changed to "Chip (main)."                                                                                |      |  |  |  |  |

|                      | The $T_J$ parameter in Table 3-2 • Recommended Operating Conditions was changed to $T_A$ , ambient temperature, and table notes 4–6 were added.                                                                | 3-2  |  |  |  |  |

|                      | The "PLL Macro" section was updated to add information on the VCO and PLL outputs during power-up.                                                                                                             | 2-15 |  |  |  |  |

| v2.0<br>(April 2007) | In the "Temperature Grade Offerings" section, Ambient was deleted.                                                                                                                                             | iii  |  |  |  |  |

|                      | Ambient was deleted from "Temperature Grade Offerings".                                                                                                                                                        | iii  |  |  |  |  |

|                      | Ambient was deleted from the "Speed Grade and Temperature Grade Matrix".                                                                                                                                       | iv   |  |  |  |  |

|                      | The "PLL Macro" section was updated to include power-up information.                                                                                                                                           | 2-15 |  |  |  |  |

|                      | Table 2-13 • ProASIC3E CCC/PLL Specification was updated.                                                                                                                                                      |      |  |  |  |  |

|                      | Figure 2-19 • Peak-to-Peak Jitter Definition is new.                                                                                                                                                           |      |  |  |  |  |

|                      | The "SRAM and FIFO" section was updated with operation and timing requirement information.                                                                                                                     | 2-21 |  |  |  |  |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                               | 2-25 |  |  |  |  |

|                      | The "RESET" section was updated with read and write information.                                                                                                                                               |      |  |  |  |  |

|                      | The "Introduction" in the "Advanced I/Os" section was updated to include information on input and output buffers being disabled.                                                                               | 2-28 |  |  |  |  |

|                      | In the Table 2-15 • Levels of Hot-Swap Support, the ProASIC3 compliance descriptions were updated for levels 3 and 4.                                                                                          | 2-34 |  |  |  |  |

|                      | Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices was updated.                                                                                                               | 2-64 |  |  |  |  |

|                      | Notes 3, 4, and 5 were added to Table 2-17 $\cdot$ Comparison Table for 5 V–<br>Compliant Receiver Scheme. 5 x 52.72 was changed to 52.7 and the Maximum<br>current was updated from 4 x 52.7 to 5 x 52.7.     | 2-40 |  |  |  |  |

|                      | The "VCCPLF PLL Supply Voltage" section was updated.                                                                                                                                                           | 2-50 |  |  |  |  |

|                      | The "VPUMP Programming Supply Voltage" section was updated.                                                                                                                                                    | 2-50 |  |  |  |  |

|                      | The "GL Globals" section was updated to include information about direct input into quadrant clocks.                                                                                                           | 2-51 |  |  |  |  |

|                      | VJTAG was deleted from the "TCK Test Clock" section.                                                                                                                                                           | 2-51 |  |  |  |  |

|                      | In Table 2-22 • Recommended Tie-Off Values for the TCK and TRST Pins, TSK was changed to TCK in note 2. Note 3 was also updated.                                                                               | 2-51 |  |  |  |  |

|                      | Ambient was deleted from Table 3-2 • Recommended Operating Conditions. VPUMP programming mode was changed from "3.0 to 3.6" to "3.15 to 3.45".                                                                 | 3-2  |  |  |  |  |

|                      | Note 3 is new in Table 3-4 • Overshoot and Undershoot Limits (as measured on quiet I/Os).                                                                                                                      | 3-2  |  |  |  |  |

|                      | In EQ 3-2, 150 was changed to 110 and the result changed to 5.88.                                                                                                                                              | 3-5  |  |  |  |  |