Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| 2012.02                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 516096                                                                      |

| Number of I/O                  | 341                                                                         |

| Number of Gates                | 300000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 484-BGA                                                                     |

| Supplier Device Package        | 484-FPBGA (23x23)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000-2fg484 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Advanced Architecture**

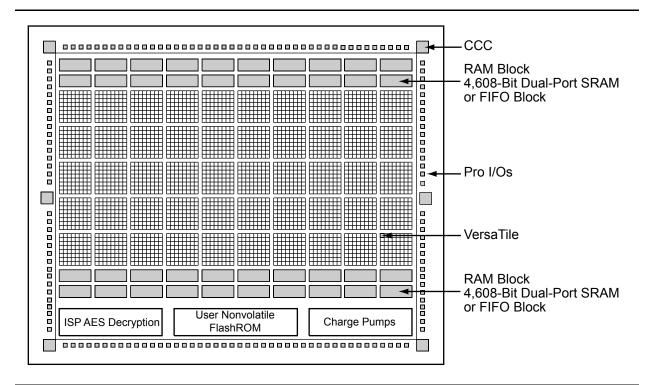

The proprietary ProASIC3E architecture provides granularity comparable to standard-cell ASICs. The ProASIC3E device consists of five distinct and programmable architectural features (Figure 1-1 on page 3):

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory

- Extensive CCCs and PLLs

- Pro I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the ProASIC3E core tile as either a three-input lookup table (LUT) equivalent or as a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC family of third-generation architecture Flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

Figure 1-1 • ProASIC3E Device Architecture Overview

### 3.3 V LVCMOS Wide Range

| 3.3 V<br>LVCMOS<br>Wide<br>Range | Equivalent<br>Software<br>Default<br>Drive | v         | IL        | v         | н         | VOL       | VOH       | IOL | юн  | IOSL                    | IOSH                    | IIL <sup>2</sup> | IIH <sup>3</sup> |

|----------------------------------|--------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength                | Strength<br>Option <sup>1</sup>            | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | μA  | μA  | Max.<br>mA <sup>4</sup> | Max.<br>mA <sup>4</sup> | μA <sup>5</sup>  | μA <sup>5</sup>  |

| 100 µA                           | 2 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 4 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 27                      | 25                      | 10               | 10               |

| 100 µA                           | 6 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 8 mA                                       | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 54                      | 51                      | 10               | 10               |

| 100 µA                           | 12 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 109                     | 103                     | 10               | 10               |

| 100 µA                           | 16 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 127                     | 132                     | 10               | 10               |

| 100 µA                           | 24 mA                                      | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 181                     | 268                     | 10               | 10               |

#### Table 2-29 • Minimum and Maximum DC Input and Output Levels

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

4. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

5. Currents are measured at 85°C junction temperature.

6. Software default selection highlighted in gray.

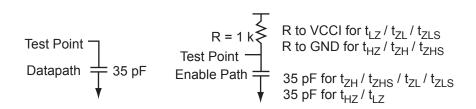

#### Figure 2-7 • AC Loading

#### Table 2-30 • 3.3 V LVCMOS Wide Range AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | _               | 35                     |

*Note:* \**Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.*

ProASIC3E DC and Switching Characteristics

### Timing Characteristics

### Table 2-31 • 3.3 V LVCMOS Wide Range High Slew

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.7 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>eout</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zhs</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 100 µA            | 4 mA                                                                          | Std.           | 0.66              | 12.19           | 0.04             | 1.83            | 2.38             | 0.43              | 12.19           | 10.17           | 4.16            | 4.00            | 15.58            | 13.57            | ns    |

|                   |                                                                               | -1             | 0.56              | 10.37           | 0.04             | 1.55            | 2.02             | 0.36              | 10.37           | 8.66            | 3.54            | 3.41            | 13.26            | 11.54            | ns    |

|                   |                                                                               | -2             | 0.49              | 9.10            | 0.03             | 1.36            | 1.78             | 0.32              | 9.10            | 7.60            | 3.11            | 2.99            | 11.64            | 10.13            | ns    |

| 100 µA            | 8 mA                                                                          | Std.           | 0.66              | 7.85            | 0.04             | 1.83            | 2.38             | 0.43              | 7.85            | 6.29            | 4.71            | 4.97            | 11.24            | 9.68             | ns    |

|                   |                                                                               | -1             | 0.56              | 6.68            | 0.04             | 1.55            | 2.02             | 0.36              | 6.68            | 5.35            | 4.01            | 4.22            | 9.57             | 8.24             | ns    |

|                   |                                                                               | -2             | 0.49              | 5.86            | 0.03             | 1.36            | 1.78             | 0.32              | 5.86            | 4.70            | 3.52            | 3.71            | 8.40             | 7.23             | ns    |

| 100 µA            | 12 mA                                                                         | Std.           | 0.66              | 5.67            | 0.04             | 1.83            | 2.38             | 0.43              | 5.67            | 4.36            | 5.06            | 5.59            | 9.07             | 7.75             | ns    |

|                   |                                                                               | -1             | 0.56              | 4.82            | 0.04             | 1.55            | 2.02             | 0.36              | 4.82            | 3.71            | 4.31            | 4.75            | 7.71             | 6.59             | ns    |

|                   |                                                                               | -2             | 0.49              | 4.24            | 0.03             | 1.36            | 1.78             | 0.32              | 4.24            | 3.25            | 3.78            | 4.17            | 6.77             | 5.79             | ns    |

| 100 µA            | 16 mA                                                                         | Std.           | 0.66              | 5.35            | 0.04             | 1.83            | 2.38             | 0.43              | 5.35            | 3.96            | 5.15            | 5.76            | 8.75             | 7.35             | ns    |

|                   |                                                                               | -1             | 0.56              | 4.55            | 0.04             | 1.55            | 2.02             | 0.36              | 4.55            | 3.36            | 4.38            | 4.90            | 7.44             | 6.25             | ns    |

|                   |                                                                               | -2             | 0.49              | 4.00            | 0.03             | 1.36            | 1.78             | 0.32              | 4.00            | 2.95            | 3.85            | 4.30            | 6.53             | 5.49             | ns    |

| 100 µA            | 24 mA                                                                         | Std.           | 0.66              | 4.96            | 0.04             | 1.83            | 2.38             | 0.43              | 4.96            | 3.27            | 5.23            | 6.38            | 8.35             | 6.67             | ns    |

|                   |                                                                               | -1             | 0.56              | 4.22            | 0.04             | 1.55            | 2.02             | 0.36              | 4.22            | 2.78            | 4.45            | 5.43            | 7.11             | 5.67             | ns    |

|                   |                                                                               | -2             | 0.49              | 3.70            | 0.03             | 1.36            | 1.78             | 0.32              | 3.70            | 2.44            | 3.91            | 4.76            | 6.24             | 4.98             | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm 100 \ \mu$ A. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. Software default selection highlighted in gray.

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

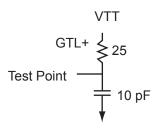

### 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-54 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        |           | VIL        | VIH        | VIH       |           | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 35 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | _         | 35  | 35 | 181                     | 268                     | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

#### Figure 2-14 • AC Loading

Table 2-55 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                     | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-56 • 3.3 V GTL+

```

Commercial-Case Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.0 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.60              | 2.06            | 0.04             | 1.59            | 0.43              | 2.09            | 2.06            |                 |                 | 4.33             | 4.29             | ns    |

| -1             | 0.51              | 1.75            | 0.04             | 1.35            | 0.36              | 1.78            | 1.75            |                 |                 | 3.68             | 3.65             | ns    |

| -2             | 0.45              | 1.53            | 0.03             | 1.19            | 0.32              | 1.56            | 1.53            |                 |                 | 3.23             | 3.20             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

## **Differential I/O Characteristics**

### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by the Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and DDR. However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

### LVDS

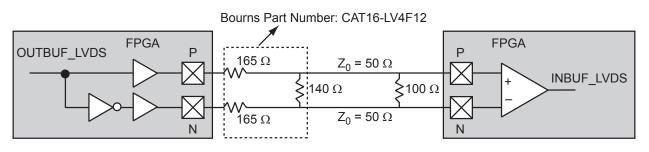

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-22. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, ProASIC3E also supports Bus LVDS structure and Multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-22 • LVDS Circuit Diagram and Board-Level Implementation

### **Timing Characteristics**

#### Table 2-80 • LVDS

Commercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 1.87            | 0.04             | 1.82            | ns    |

| -1          | 0.56              | 1.59            | 0.04             | 1.55            | ns    |

| -2          | 0.49              | 1.40            | 0.03             | 1.36            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

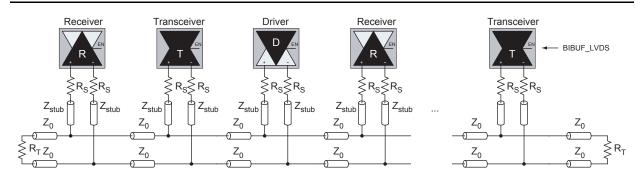

### B-LVDS/M-LVDS

Bus LVDS (B-LVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations may contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by B-LVDS and M-LVDS to accommodate the loading. The drivers require series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus since the driver can be located anywhere on the bus. These configurations can be implemented using the TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-23. The input and output buffer delays are available in the LVDS section in Table 2-80.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case Industrial operating conditions, at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 2-23 • B-LVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

## **VersaTile Characteristics**

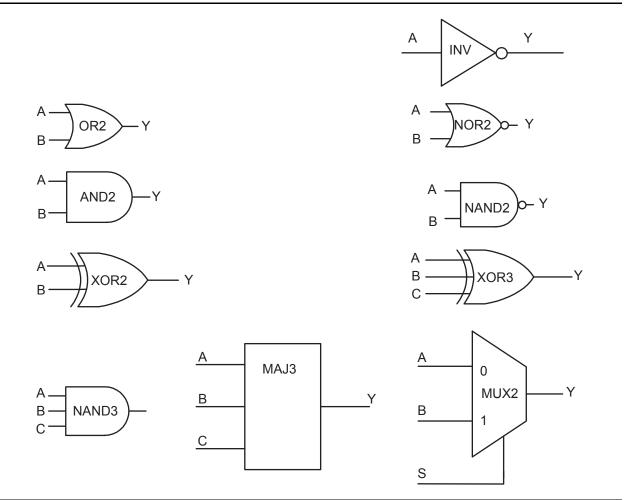

## VersaTile Specifications as a Combinatorial Module

The ProASIC3E library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library. For more details, refer to the *Fusion*, *IGLOO®/e*, *and ProASIC3/E Macro Library Guide*.

Figure 2-34 • Sample of Combinatorial Cells

ProASIC3E DC and Switching Characteristics

### Timing Characteristics

#### *Table 2-93* • Combinatorial Cell Propagation Delays Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | -2   | -1   | Std. | Units |

|--------------------|---------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | $Y = A \cdot B$           | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.56 | 0.64 | 0.75 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

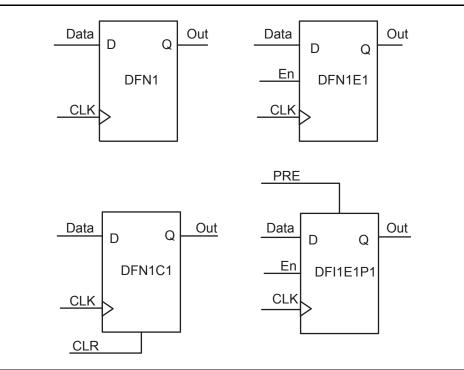

## VersaTile Specifications as a Sequential Module

The ProASIC3E library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *Fusion, IGLOO/e, and ProASIC3/E Macro Library Guide*.

Figure 2-36 • Sample of Sequential Cells

ProASIC3E DC and Switching Characteristics

## **Clock Conditioning Circuits**

### **CCC Electrical Specifications**

**Timing Characteristics**

### Table 2-98 • ProASIC3E CCC/PLL Specification

| Parameter                                               |                                     | Minimum                  | Typical                     | Maximum                   | Units |

|---------------------------------------------------------|-------------------------------------|--------------------------|-----------------------------|---------------------------|-------|

| Clock Conditioning Circuitry Inp                        | out Frequency f <sub>IN_CCC</sub>   | 1.5                      |                             | 350                       | MHz   |

| Clock Conditioning Circuitry Ou                         | tput Frequency f <sub>OUT_CCC</sub> | 0.75                     |                             | 350                       | MHz   |

| Delay Increments in Programm                            | able Delay Blocks <sup>1, 2</sup>   |                          | 160 <sup>3</sup>            |                           | ps    |

| Serial Clock (SCLK) for Dynam                           | ic PLL <sup>4</sup>                 |                          |                             | 125                       | MHz   |

| Number of Programmable Valu<br>Programmable Delay Block | es in Each                          |                          |                             | 32                        |       |

| Input Period Jitter                                     |                                     |                          |                             | 1.5                       | ns    |

| CCC Output Peak-to-Peak Per                             | od Jitter F <sub>CCC_OUT</sub>      | Max                      | <pre>     Peak-to-Pe </pre> | ak Period Jitter          |       |

|                                                         |                                     | 1 Global<br>Network Used |                             | 3 Global<br>Networks Used |       |

| 0.75 MHz to 24 MHz                                      |                                     | 0.50%                    |                             | 0.70%                     |       |

| 24 MHz to 100 MHz                                       |                                     | 1.00%                    |                             | 1.20%                     |       |

| 100 MHz to 250 MHz                                      |                                     | 1.75%                    |                             | 2.00%                     |       |

| 250 MHz to 350 MHz                                      |                                     | 2.50%                    |                             | 5.60%                     |       |

| Acquisition Time                                        | LockControl = 0                     |                          |                             | 300                       | μs    |

|                                                         | LockControl = 1                     |                          |                             | 6.0                       | ms    |

| Tracking Jitter <sup>5</sup>                            | LockControl = 0                     |                          |                             | 1.6                       | ns    |

|                                                         | LockControl = 1                     |                          |                             | 0.8                       | ns    |

| Output Duty Cycle                                       |                                     | 48.5                     |                             | 51.5                      | %     |

| Delay Range in Block: Program                           | 0.6                                 |                          | 5.56                        | ns                        |       |

| Delay Range in Block: Program                           | 0.025                               |                          | 5.56                        | ns                        |       |

| Delay Range in Block: Fixed D                           | elay <sup>1,4</sup>                 |                          | 2.2                         |                           | ns    |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-5 for deratings

2.  $T_J = 25^{\circ}C$ , VCC = 1.5 V.

3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help for more information.

4. Maximum value obtained for a -2 speed-grade device in worst-case commercial conditions. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

5. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to the PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by the period jitter parameter.

## Timing Waveforms

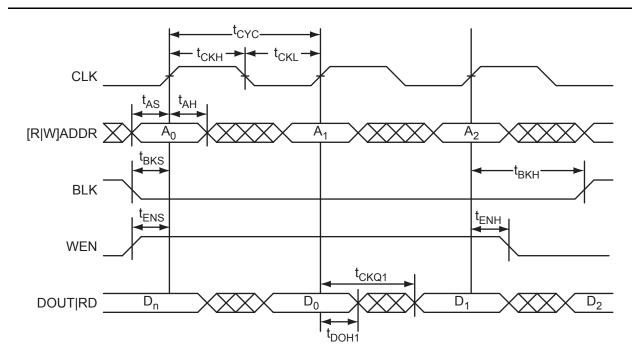

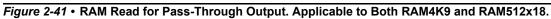

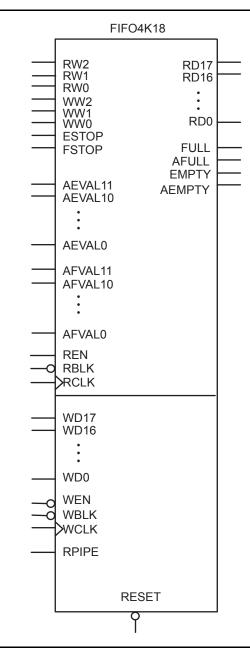

Figure 2-42 • RAM Read for Pipelined Output. Applicable to Both RAM4K9 and RAM512x18.

### Table 2-100 • RAM512X18

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -2   | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.18 | 0.20 | 0.24 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.06 | 0.07 | 0.08 | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                          | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                           | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                                | 2.16 | 2.46 | 2.89 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                      | 0.90 | 1.02 | 1.20 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.50 | 0.43 | 0.38 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.59 | 0.50 | 0.44 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow-through)                                                                      | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                         | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

ProASIC3E DC and Switching Characteristics

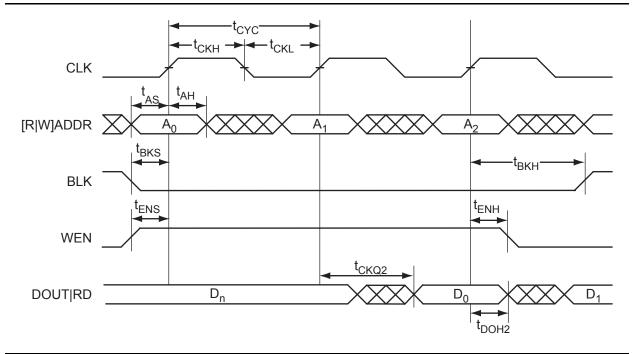

### FIFO

Figure 2-46 • FIFO Model

# 4 – Package Pin Assignments

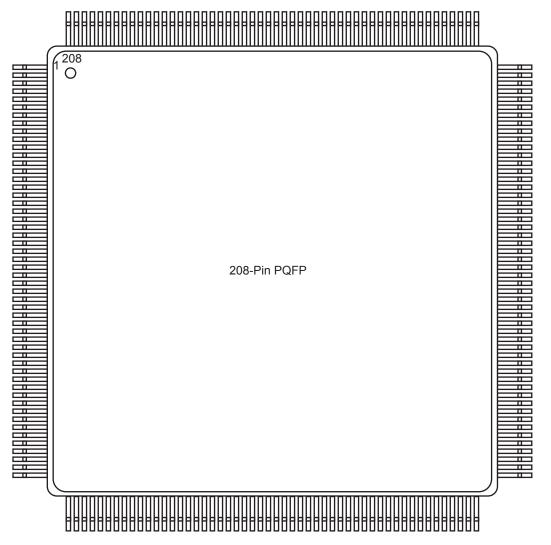

## **PQ208**

Note: This is the top view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

Package Pin Assignments

|            | PQ208             |            | PQ208             |            | PQ208             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function |

| 1          | GND               | 37         | IO184PDB6V2       | 73         | IO145NDB5V1       |

| 2          | GNDQ              | 38         | IO184NDB6V2       | 74         | IO145PDB5V1       |

| 3          | VMV7              | 39         | IO180PSB6V1       | 75         | IO143NDB5V1       |

| 4          | GAB2/IO220PSB7V3  | 40         | VCCIB6            | 76         | IO143PDB5V1       |

| 5          | GAA2/IO221PDB7V3  | 41         | GND               | 77         | IO137NDB5V0       |

| 6          | IO221NDB7V3       | 42         | IO176PDB6V1       | 78         | IO137PDB5V0       |

| 7          | GAC2/IO219PDB7V3  | 43         | IO176NDB6V1       | 79         | IO135NDB5V0       |

| 8          | IO219NDB7V3       | 44         | GEC1/IO169PDB6V0  | 80         | IO135PDB5V0       |

| 9          | IO215PDB7V3       | 45         | GEC0/IO169NDB6V0  | 81         | GND               |

| 10         | IO215NDB7V3       | 46         | GEB1/IO168PPB6V0  | 82         | IO131NDB4V2       |

| 11         | IO212PDB7V2       | 47         | GEA1/IO167PPB6V0  | 83         | IO131PDB4V2       |

| 12         | IO212NDB7V2       | 48         | GEB0/IO168NPB6V0  | 84         | IO129NDB4V2       |

| 13         | IO208PDB7V2       | 49         | GEA0/IO167NPB6V0  | 85         | IO129PDB4V2       |

| 14         | IO208NDB7V2       | 50         | VMV6              | 86         | IO127NDB4V2       |

| 15         | IO204PSB7V1       | 51         | GNDQ              | 87         | IO127PDB4V2       |

| 16         | VCC               | 52         | GND               | 88         | VCC               |

| 17         | GND               | 53         | VMV5              | 89         | VCCIB4            |

| 18         | VCCIB7            | 54         | GNDQ              | 90         | IO121NDB4V1       |

| 19         | IO200PDB7V1       | 55         | IO166NDB5V3       | 91         | IO121PDB4V1       |

| 20         | IO200NDB7V1       | 56         | GEA2/IO166PDB5V3  | 92         | IO119NDB4V1       |

| 21         | IO196PSB7V0       | 57         | IO165NDB5V3       | 93         | IO119PDB4V1       |

| 22         | GFC1/IO192PSB7V0  | 58         | GEB2/IO165PDB5V3  | 94         | IO113NDB4V0       |

| 23         | GFB1/IO191PDB7V0  | 59         | IO164NDB5V3       | 95         | GDC2/IO113PDB4V0  |

| 24         | GFB0/IO191NDB7V0  | 60         | GEC2/IO164PDB5V3  | 96         | IO112NDB4V0       |

| 25         | VCOMPLF           | 61         | IO163PSB5V3       | 97         | GND               |

| 26         | GFA0/IO190NPB6V2  | 62         | VCCIB5            | 98         | GDB2/IO112PDB4V0  |

| 27         | VCCPLF            | 63         | IO161PSB5V3       | 99         | GDA2/IO111PSB4V0  |

| 28         | GFA1/IO190PPB6V2  | 64         | IO157NDB5V2       | 100        | GNDQ              |

| 29         | GND               | 65         | GND               | 101        | ТСК               |

| 30         | GFA2/IO189PDB6V2  | 66         | IO157PDB5V2       | 102        | TDI               |

| 31         | IO189NDB6V2       | 67         | IO153NDB5V2       | 103        | TMS               |

| 32         | GFB2/IO188PPB6V2  | 68         | IO153PDB5V2       | 104        | VMV4              |

| 33         | GFC2/IO187PPB6V2  | 69         | IO149NDB5V1       | 105        | GND               |

| 34         | IO188NPB6V2       | 70         | IO149PDB5V1       | 106        | VPUMP             |

| 35         | IO187NPB6V2       | 71         | VCC               | 107        | GNDQ              |

| 36         | VCC               | 72         | VCCIB5            | 108        | TDO               |

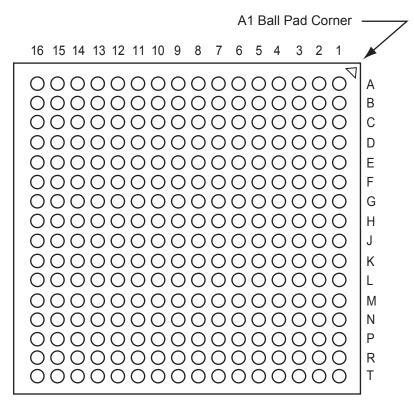

## FG256

*Note:* This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

| FG256                       |                  | FG256                       |                  | FG256      |                  |

|-----------------------------|------------------|-----------------------------|------------------|------------|------------------|

| Pin Number A3PE600 Function |                  | Pin Number A3PE600 Function |                  | Pin Number | A3PE600 Function |

| A1                          | GND              | C5                          | GAC0/IO02NDB0V0  | E9         | IO21NDB1V0       |

| A2                          | GAA0/IO00NDB0V0  | C6                          | GAC1/IO02PDB0V0  | E10        | VCCIB1           |

| A3                          | GAA1/IO00PDB0V0  | C7                          | IO15NDB0V2       | E11        | VCCIB1           |

| A4                          | GAB0/IO01NDB0V0  | C8                          | IO15PDB0V2       | E12        | VMV1             |

| A5                          | IO05PDB0V0       | C9                          | IO20PDB1V0       | E13        | GBC2/IO38PDB2V0  |

| A6                          | IO10PDB0V1       | C10                         | IO25NDB1V0       | E14        | IO37NDB2V0       |

| A7                          | IO12PDB0V2       | C11                         | IO27PDB1V0       | E15        | IO41NDB2V0       |

| A8                          | IO16NDB0V2       | C12                         | GBC0/IO33NDB1V1  | E16        | IO41PDB2V0       |

| A9                          | IO23NDB1V0       | C13                         | VCCPLB           | F1         | IO124PDB7V0      |

| A10                         | IO23PDB1V0       | C14                         | VMV2             | F2         | IO125PDB7V0      |

| A11                         | IO28NDB1V1       | C15                         | IO36NDB2V0       | F3         | IO126PDB7V0      |

| A12                         | IO28PDB1V1       | C16                         | IO42PDB2V0       | F4         | IO130NDB7V1      |

| A13                         | GBB1/IO34PDB1V1  | D1                          | IO128PDB7V1      | F5         | VCCIB7           |

| A14                         | GBA0/IO35NDB1V1  | D2                          | IO129PDB7V1      | F6         | GND              |

| A15                         | GBA1/IO35PDB1V1  | D3                          | GAC2/IO132PDB7V1 | F7         | VCC              |

| A16                         | GND              | D4                          | VCOMPLA          | F8         | VCC              |

| B1                          | GAB2/IO133PDB7V1 | D5                          | GNDQ             | F9         | VCC              |

| B2                          | GAA2/IO134PDB7V1 | D6                          | IO09NDB0V1       | F10        | VCC              |

| B3                          | GNDQ             | D7                          | IO09PDB0V1       | F11        | GND              |

| B4                          | GAB1/IO01PDB0V0  | D8                          | IO13PDB0V2       | F12        | VCCIB2           |

| B5                          | IO05NDB0V0       | D9                          | IO21PDB1V0       | F13        | IO38NDB2V0       |

| B6                          | IO10NDB0V1       | D10                         | IO25PDB1V0       | F14        | IO40NDB2V0       |

| B7                          | IO12NDB0V2       | D11                         | IO27NDB1V0       | F15        | IO40PDB2V0       |

| B8                          | IO16PDB0V2       | D12                         | GNDQ             | F16        | IO45PSB2V1       |

| B9                          | IO20NDB1V0       | D13                         | VCOMPLB          | G1         | IO124NDB7V0      |

| B10                         | IO24NDB1V0       | D14                         | GBB2/IO37PDB2V0  | G2         | IO125NDB7V0      |

| B11                         | IO24PDB1V0       | D15                         | IO39PDB2V0       | G3         | IO126NDB7V0      |

| B12                         | GBC1/IO33PDB1V1  | D16                         | IO39NDB2V0       | G4         | GFC1/IO120PPB7V0 |

| B13                         | GBB0/IO34NDB1V1  | E1                          | IO128NDB7V1      | G5         | VCCIB7           |

| B14                         | GNDQ             | E2                          | IO129NDB7V1      | G6         | VCC              |

| B15                         | GBA2/IO36PDB2V0  | E3                          | IO132NDB7V1      | G7         | GND              |

| B16                         | IO42NDB2V0       | E4                          | IO130PDB7V1      | G8         | GND              |

| C1                          | IO133NDB7V1      | E5                          | VMV0             | G9         | GND              |

| C2                          | IO134NDB7V1      | E6                          | VCCIB0           | G10        | GND              |

| C3                          | VMV7             | E7                          | VCCIB0           | G11        | VCC              |

| C4                          | VCCPLA           | E8                          | IO13NDB0V2       | G12        | VCCIB2           |

| FG256      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | A3PE600 Function |  |  |  |

| P9         | IO82PDB5V0       |  |  |  |

| P10        | IO76NDB4V1       |  |  |  |

| P11        | IO76PDB4V1       |  |  |  |

| P12        | VMV4             |  |  |  |

| P13        | TCK              |  |  |  |

| P14        | VPUMP            |  |  |  |

| P15        | TRST             |  |  |  |

| P16        | GDA0/IO67NDB3V1  |  |  |  |

| R1         | GEA1/IO102PDB6V0 |  |  |  |

| R2         | GEA0/IO102NDB6V0 |  |  |  |

| R3         | GNDQ             |  |  |  |

| R4         | GEC2/IO99PDB5V2  |  |  |  |

| R5         | IO95NPB5V1       |  |  |  |

| R6         | IO91NDB5V1       |  |  |  |

| R7         | IO91PDB5V1       |  |  |  |

| R8         | IO83NDB5V0       |  |  |  |

| R9         | IO83PDB5V0       |  |  |  |

| R10        | IO77NDB4V1       |  |  |  |

| R11        | IO77PDB4V1       |  |  |  |

| R12        | IO69NDB4V0       |  |  |  |

| R13        | GDB2/IO69PDB4V0  |  |  |  |

| R14        | TDI              |  |  |  |

| R15        | GNDQ             |  |  |  |

| R16        | TDO              |  |  |  |

| T1         | GND              |  |  |  |

| T2         | IO100NDB5V2      |  |  |  |

| Т3         | GEB2/IO100PDB5V2 |  |  |  |

| T4         | IO99NDB5V2       |  |  |  |

| T5         | IO88NDB5V0       |  |  |  |

| Т6         | IO88PDB5V0       |  |  |  |

| T7         | IO89NSB5V0       |  |  |  |

| Т8         | IO80NSB4V1       |  |  |  |

| Т9         | IO81NDB4V1       |  |  |  |

| T10        | IO81PDB4V1       |  |  |  |

| T11        | IO70NDB4V0       |  |  |  |

| T12        | GDC2/IO70PDB4V0  |  |  |  |

| FG256      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | A3PE600 Function |  |  |

| T13        | IO68NDB4V0       |  |  |

| T14        | GDA2/IO68PDB4V0  |  |  |

| T15        | TMS              |  |  |

| T16        | GND              |  |  |

| FG324      |                  | FG324      |                  | FG324      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA    |

| N1         | IO247NDB6V1      | R1         | IO245NDB6V1      | U1         | IO241NDB6V0      |

| N2         | IO247PDB6V1      | R2         | VCCIB6           | U2         | GEA2/IO233PPB5V4 |

| N3         | IO251NPB6V2      | R3         | GEA1/IO234PPB6V0 | U3         | GEC2/IO231PPB5V4 |

| N4         | GEC0/IO236NDB6V0 | R4         | IO232NDB5V4      | U4         | VCCIB5           |

| N5         | VCOMPLE          | R5         | GEB2/IO232PDB5V4 | U5         | GNDQ             |

| N6         | IO212NDB5V2      | R6         | IO214NDB5V2      | U6         | IO208PDB5V1      |

| N7         | IO212PDB5V2      | R7         | IO202PDB5V1      | U7         | IO198PPB5V0      |

| N8         | IO192NPB4V4      | R8         | IO194PDB5V0      | U8         | VCCIB5           |

| N9         | IO174PDB4V2      | R9         | IO186PDB4V4      | U9         | IO182NPB4V3      |

| N10        | IO170PDB4V2      | R10        | IO178PDB4V3      | U10        | IO180NPB4V3      |

| N11        | GDA2/IO154PPB4V0 | R11        | IO168NSB4V1      | U11        | VCCIB4           |

| N12        | GDB2/IO155PPB4V0 | R12        | IO164PDB4V1      | U12        | IO166PPB4V1      |

| N13        | GDA1/IO153PPB3V4 | R13        | GDC2/IO156PDB4V0 | U13        | IO162PDB4V1      |

| N14        | VCOMPLD          | R14        | ТСК              | U14        | GNDQ             |

| N15        | GDB0/IO152NDB3V4 | R15        | VPUMP            | U15        | VCCIB4           |

| N16        | GDB1/IO152PDB3V4 | R16        | TRST             | U16        | TMS              |

| N17        | IO138NDB3V3      | R17        | VCCIB3           | U17        | VMV3             |

| N18        | IO138PDB3V3      | R18        | IO142NDB3V3      | U18        | IO146NDB3V4      |

| P1         | IO245PDB6V1      | T1         | IO241PDB6V0      | V1         | GND              |

| P2         | GNDQ             | T2         | GEA0/IO234NPB6V0 | V2         | IO218NDB5V3      |

| P3         | VMV6             | Т3         | IO233NPB5V4      | V3         | IO218PDB5V3      |

| P4         | GEC1/IO236PDB6V0 | T4         | IO231NPB5V4      | V4         | IO206NDB5V1      |

| P5         | VCCPLE           | T5         | VMV5             | V5         | IO206PDB5V1      |

| P6         | IO214PDB5V2      | Т6         | IO208NDB5V1      | V6         | IO198NPB5V0      |

| P7         | VCCIB5           | T7         | IO202NDB5V1      | V7         | GND              |

| P8         | GND              | Т8         | IO194NDB5V0      | V8         | IO190NDB4V4      |

| P9         | IO174NDB4V2      | Т9         | IO186NDB4V4      | V9         | IO190PDB4V4      |

| P10        | IO170NDB4V2      | T10        | IO178NDB4V3      | V10        | IO182PPB4V3      |

| P11        | GND              | T11        | IO166NPB4V1      | V11        | IO180PPB4V3      |

| P12        | VCCIB4           | T12        | IO164NDB4V1      | V12        | GND              |

| P13        | IO155NPB4V0      | T13        | IO156NDB4V0      | V13        | IO162NDB4V1      |

| P14        | VCCPLD           | T14        | VMV4             | V14        | IO160NDB4V0      |

| P15        | VJTAG            | T15        | TDI              | V15        | IO160PDB4V0      |

| P16        | GDC0/IO151NDB3V4 | T16        | GNDQ             | V16        | IO158NDB4V0      |

| P17        | GDC1/IO151PDB3V4 | T17        | TDO              | V17        | IO158PDB4V0      |

| P18        | IO142PDB3V3      | T18        | IO146PDB3V4      | V18        | GND              |

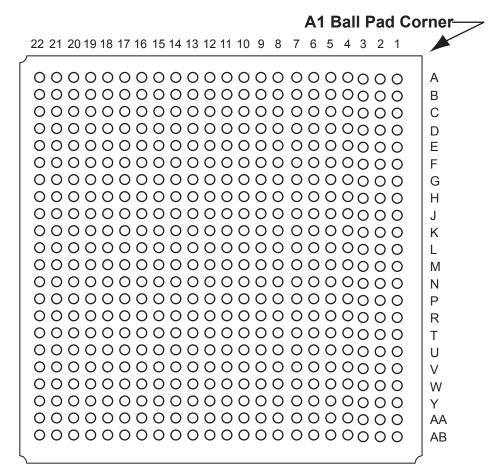

## FG484

Note: This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

Datasheet Information

| Revision                                                          | Changes                                                                                                                                                                                                                        | Page |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 3 (Apr 2008)<br>Packaging v1.2                           | The following pins had duplicates and the extra pins were deleted from the "PQ208" A3PE3000 table:                                                                                                                             | 4-2  |

|                                                                   | 36, 62, 171                                                                                                                                                                                                                    |      |

|                                                                   | Note: There were no pin function changes in this update.                                                                                                                                                                       |      |

|                                                                   | The following pins had duplicates and the extra pins were deleted from the "FG324" table:                                                                                                                                      | 4-12 |

|                                                                   | E2, E3, E16, E17, P2, P3, T16, U17                                                                                                                                                                                             |      |

|                                                                   | Note: There were no pin function changes in this update.                                                                                                                                                                       |      |

|                                                                   | The "FG256" pin table was updated for the A3PE600 device because the old PAT were based on the IFX die, and this is the final UMC die version.                                                                                 | 4-9  |

|                                                                   | The "FG484" was updated for the A3PE600 device because the old PAT were based on the IFX die, and this is the final UMC die version.                                                                                           | 4-22 |

|                                                                   | The following pins had duplicates and the extra pins were deleted from the "FG896" table:                                                                                                                                      | 4-41 |

|                                                                   | AD6, AE5, AE28, AF29, F5, F26, G6, G25                                                                                                                                                                                         |      |

|                                                                   | Note: There were no pin function changes in this update.                                                                                                                                                                       |      |

| Revision 2 (Mar 2008)<br>Product Brief rev. 1                     | B) The FG324 package was added to the "ProASIC3E Product Family" table, the<br>"I/Os Per Package1" table, and the "Temperature Grade Offerings" table for<br>A3PE3000.                                                         |      |

| Revision 1 (Feb 2008)<br>DC and Switching<br>Characteristics v1.1 | In Table 2-3 • Flash Programming Limits – Retention, Storage and Operating Temperature 1, Maximum Operating Junction Temperature was changed from 110°C to 100°C for both commercial and industrial grades.                    | 2    |

|                                                                   | The "PLL Behavior at Brownout Condition" section is new.                                                                                                                                                                       | 2-4  |

|                                                                   | In the "PLL Contribution—PPLL" section, the following was deleted:<br>FCLKIN is the input clock frequency.                                                                                                                     | 2-10 |

|                                                                   | In Table 2-14 • Summary of Maximum and Minimum DC Input Levels, the note was incorrect. It previously said $T_J$ and it was corrected and changed to $T_A$ .                                                                   | 2-17 |

|                                                                   | In Table 2-98 • ProASIC3E CCC/PLL Specification, the SCLK parameter and note 1 are new.                                                                                                                                        | 2-70 |

|                                                                   | Table 2-103 • JTAG 1532 was populated with the parameter data, which was not in the previous version of the document.                                                                                                          | 2-83 |

| Revision 1 (cont'd)                                               | The "PQ208" pin table for A3PE3000 was updated.                                                                                                                                                                                | 4-2  |

| Packaging v1.1                                                    | The "FG324" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-13 |

|                                                                   | The "FG484" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-17 |

|                                                                   | The "FG896" pin table for A3PE3000 is new.                                                                                                                                                                                     | 4-41 |

| Revision 0 (Jan 2008)                                             | This document was previously in datasheet v2.1. As a result of moving to the handbook format, Actel has restarted the version numbers. The new version number is 51700098-001-0.                                               |      |

| v2.1<br>(July 2007)                                               | CoreMP7 information was removed from the "Features and Benefits" section.                                                                                                                                                      | 1-I  |

|                                                                   | The M1 device part numbers have been updated in ProASIC3E Product Family,<br>"Packaging Tables", "Temperature Grade Offerings", "Speed Grade and<br>Temperature Grade Matrix", and "Speed Grade and Temperature Grade Matrix". | 1-1  |