Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                       |

|--------------------------------|------------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 516096                                                                       |

| Number of I/O                  | 620                                                                          |

| Number of Gates                | 300000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

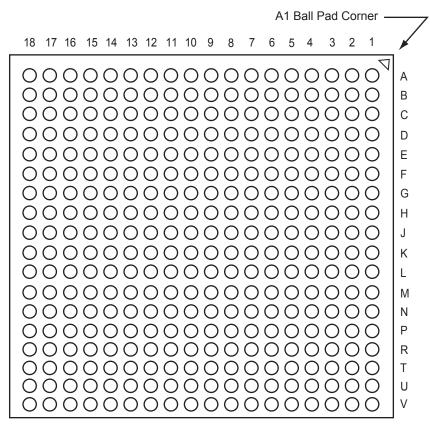

| Package / Case                 | 896-BGA                                                                      |

| Supplier Device Package        | 896-FBGA (31x31)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1a3pe3000-fgg896i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ProASIC3E Device Family Overview

### Single Chip

Flash-based FPGAs store their configuration information in on-chip flash cells. Once programmed, the configuration data is an inherent part of the FPGA structure, and no external configuration data needs to be loaded at system power-up (unlike SRAM-based FPGAs). Therefore, flash-based ProASIC3E FPGAs do not require system configuration components such as EEPROMs or microcontrollers to load device configuration data. This reduces bill-of-materials costs and PCB area, and increases security and system reliability.

### Instant On

Flash-based ProASIC3E devices support Level 0 of the Instant On classification standard. This feature helps in system component initialization, execution of critical tasks before the processor wakes up, setup and configuration of memory blocks, clock generation, and bus activity management. The Instant On feature of flash-based ProASIC3E devices greatly simplifies total system design and reduces total system cost, often eliminating the need for CPLDs and clock generation PLLs that are used for these purposes in a system. In addition, glitches and brownouts in system power will not corrupt the ProASIC3E device's flash configuration, and unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables the reduction or complete removal of the configuration PROM, expensive voltage monitor, brownout detection, and clock generator devices from the PCB design. Flash-based ProASIC3E devices simplify total system design and reduce cost and design risk while increasing system reliability and improving system initialization time.

### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of ProASIC3E flash-based FPGAs. Once it is programmed, the flash cell configuration element of ProASIC3E FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

### Low Power

Flash-based ProASIC3E devices exhibit power characteristics similar to an ASIC, making them an ideal choice for power-sensitive applications. ProASIC3E devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

ProASIC3E devices also have low dynamic power consumption to further maximize power savings.

# **Advanced Flash Technology**

The ProASIC3E family offers many benefits, including nonvolatility and reprogrammability through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

ProASIC3E DC and Switching Characteristics

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

### Table 2-7 • Quiescent Supply Current Characteristics

|                      | A3PE600 | A3PE1500 | A3PE3000 |

|----------------------|---------|----------|----------|

| Typical (25°C)       | 5 mA    | 12 mA    | 25 mA    |

| Maximum (Commercial) | 30 mA   | 70 mA    | 150 mA   |

| Maximum (Industrial) | 45 mA   | 105 mA   | 225 mA   |

Notes:

1. IDD Includes VCC, VPUMP, VCCI, and VMV currents. Values do not include I/O static contribution, which is shown in Table 2-8 and Table 2-9 on page 2-7.

2. -F speed grade devices may experience higher standby IDD of up to five times the standard IDD and higher I/O leakage.

# **Power per I/O Pin**

### Table 2-8 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings

|                                                              | VMV<br>(V) | Static Power<br>PDC2 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|--------------------------------------------------------------|------------|----------------------------------------|---------------------------------------------|

| Single-Ended                                                 |            |                                        |                                             |

| 3.3 V LVTTL/LVCMOS                                           | 3.3        | -                                      | 17.39                                       |

| 3.3 V LVTTL/LVCMOS – Schmitt trigger                         | 3.3        | -                                      | 25.51                                       |

| 3.3 V LVTTL/LVCMOS Wide Range <sup>3</sup>                   | 3.3        | -                                      | 16.34                                       |

| 3.3 V LVTTL/LVCMOS Wide Range – Schmitt trigger <sup>3</sup> | 3.3        | -                                      | 24.49                                       |

| 2.5 V LVCMOS                                                 | 2.5        | -                                      | 5.76                                        |

| 2.5 V LVCMOS – Schmitt trigger                               | 2.5        | _                                      | 7.16                                        |

| 1.8 V LVCMOS                                                 | 1.8        | -                                      | 2.72                                        |

| 1.8 V LVCMOS – Schmitt trigger                               | 1.8        | _                                      | 2.80                                        |

| 1.5 V LVCMOS (JESD8-11)                                      | 1.5        | -                                      | 2.08                                        |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger                    | 1.5        | _                                      | 2.00                                        |

| 3.3 V PCI                                                    | 3.3        | -                                      | 18.82                                       |

| 3.3 V PCI – Schmitt trigger                                  | 3.3        | _                                      | 20.12                                       |

| 3.3 V PCI-X                                                  | 3.3        | -                                      | 18.82                                       |

| 3.3 V PCI-X – Schmitt trigger                                | 3.3        | -                                      | 20.12                                       |

| Voltage-Referenced                                           |            | •                                      |                                             |

| 3.3 V GTL                                                    | 3.3        | 2.90                                   | 8.23                                        |

| 2.5 V GTL                                                    | 2.5        | 2.13                                   | 4.78                                        |

| 3.3 V GTL+                                                   | 3.3        | 2.81                                   | 4.14                                        |

| 2.5 V GTL+                                                   | 2.5        | 2.57                                   | 3.71                                        |

Notes:

1. PDC2 is the static power (where applicable) measured on VMV.

2. PAC9 is the total dynamic power measured on VCC and VMV.

3. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD8b specification.

# static Microsemi.

ProASIC3E DC and Switching Characteristics

# **Single-Ended I/O Characteristics**

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. The 3.3 V LVCMOS standard is supported as part of the 3.3 V LVTTL support.

| 3.3 V LVTTL /<br>3.3 V LVCMOS | VIL       |           | VIH        |           | VOL       | vон       | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.,<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 12  | 12 | 109                     | 103                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 16  | 16 | 127                     | 132                     | 10               | 10               |

| 24 mA                         | -0.3      | 0.8       | 2          | 3.6       | 0.4       | 2.4       | 24  | 24 | 181                     | 268                     | 10               | 10               |

### Table 2-25 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V< VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

### Figure 2-6 • AC Loading

#### Table 2-26 • 3.3 V LVTTL / 3.3 V LVCMOS AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | -               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

# static Microsemi.

ProASIC3E DC and Switching Characteristics

### 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

| 1.5 V<br>LVCMOS   | VIL       |             | VIH        |           | VOL VOH     |             | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-------------|------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V  | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.30 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 16                      | 13                      | 10               | 10               |

| 4 mA              | -0.3      | 0.30 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 33                      | 25                      | 10               | 10               |

| 6 mA              | -0.3      | 0.30 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 6   | 6  | 39                      | 32                      | 10               | 10               |

| 8 mA              | -0.3      | 0.30 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 8   | 8  | 55                      | 66                      | 10               | 10               |

| 12 mA             | -0.3      | 0.30 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12  | 12 | 55                      | 66                      | 10               | 10               |

### Table 2-41 • Minimum and Maximum DC Input and Output Levels

#### Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V< VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

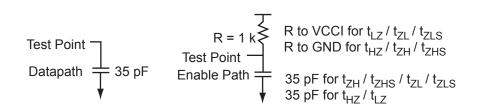

Test Point

Datapath

$$\downarrow$$

35 pF

$$R = 1 k$$

Test Point

Enable Path  $\downarrow$

$$R to VCCI for t_{LZ} / t_{ZL} / t_{ZLS}$$

$$R to GND for t_{HZ} / t_{ZH} / t_{ZHS} / t_{ZL} / t_{ZLS}$$

$$35 pF for t_{ZH} / t_{ZHS} / t_{ZL} / t_{ZLS}$$

### Figure 2-10 • AC Loading

#### Table 2-42 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 1.5            | 0.75                 | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

# **Microsemi**.

ProASIC3E DC and Switching Characteristics

### 3.3 V PCI, 3.3 V PCI-X

Peripheral Component Interface for 3.3 V standard specifies support for 33 MHz and 66 MHz PCI Bus applications.

#### Table 2-45 • Minimum and Maximum DC Input and Output Levels

| 3.3 V PCI/PCI-X       | VIL       |                | VIH       |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-----------------------|-----------|----------------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-----------------|------------------|

| Drive Strength        | Min.<br>V | Max.<br>V      | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| Per PCI specification |           | Per PCI curves |           |           |           |           |     |     |                         |                         |                 | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V< VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN< VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

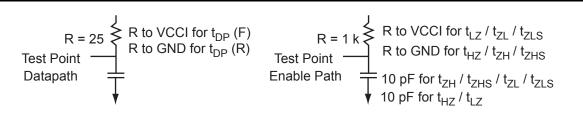

AC loadings are defined per the PCI/PCI-X specifications for the datapath; Microsemi loadings for enable path characterization are described in Figure 2-11.

### Figure 2-11 • AC Loading

AC loadings are defined per PCI/PCI-X specifications for the datapath; Microsemi loading for tristate is described in Table 2-46.

### Table 2-46 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V)                                         | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|--------------------------------------------------------------|-----------------|------------------------|

| 0             | 3.3            | 0.285 * VCCI for $t_{DP(R)}$<br>0.615 * VCCI for $t_{DP(F)}$ | -               | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

#### Table 2-47 • 3.3 V PCI/PCI-X

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.81            | 0.04             | 1.05            | 1.67             | 0.43              | 2.86            | 2.00            | 3.28            | 3.61            | 5.09             | 4.23             | ns    |

| –1             | 0.56              | 2.39            | 0.04             | 0.89            | 1.42             | 0.36              | 2.43            | 1.70            | 2.79            | 3.07            | 4.33             | 3.60             | ns    |

| -2             | 0.49              | 2.09            | 0.03             | 0.78            | 1.25             | 0.32              | 2.13            | 1.49            | 2.45            | 2.70            | 3.80             | 3.16             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

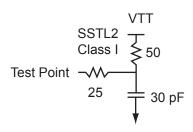

### SSTL2 Class I

Stub-Speed Terminated Logic for 2.5 V memory bus standard (JESD8-9). ProASIC3E devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| SSTL2 Class I     | VIL       |            | VIH        |           | VOL       | VOH         | IOL | IOH | IOSL                    | IOSH                    | IIL | IIH |

|-------------------|-----------|------------|------------|-----------|-----------|-------------|-----|-----|-------------------------|-------------------------|-----|-----|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V   | mA  | mA  | Max.<br>mA <sup>1</sup> | Max.<br>mA <sup>1</sup> | μA² | μA² |

| 15 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.54      | VCCI – 0.62 | 15  | 15  | 87                      | 83                      | 10  | 10  |

Notes:

1. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

2. Currents are measured at 85°C junction temperature.

### Figure 2-18 • AC Loading

| Input Low (V) | Input High (V) | Measuring<br>Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|-------------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.25                    | 1.25            | 1.25           | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

### **Timing Characteristics**

Table 2-68 • SSTL 2 Class I

```

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 2.3 V, VREF = 1.25 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 1.33            | 0.43              | 2.17            | 1.85            |                 |                 | 4.40             | 4.08             | ns    |

| –1             | 0.56              | 1.81            | 0.04             | 1.14            | 0.36              | 1.84            | 1.57            |                 |                 | 3.74             | 3.47             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.00            | 0.32              | 1.62            | 1.38            |                 |                 | 3.29             | 3.05             | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

# **Microsemi**

ProASIC3E DC and Switching Characteristics

| DC Parameter     | Description                             | Min.  | Тур.  | Max.  | Units |

|------------------|-----------------------------------------|-------|-------|-------|-------|

| VCCI             | Supply Voltage                          | 2.375 | 2.5   | 2.625 | V     |

| VOL              | Output Low Voltage                      | 0.9   | 1.075 | 1.25  | V     |

| VOH              | Output High Voltage                     | 1.25  | 1.425 | 1.6   | V     |

| IOL <sup>1</sup> | Output Lower Current                    | 0.65  | 0.91  | 1.16  | mA    |

| IOH <sup>1</sup> | Output High Current                     | 0.65  | 0.91  | 1.16  | mA    |

| VI               | Input Voltage                           | 0     |       | 2.925 | V     |

| IIH <sup>2</sup> | Input High Leakage Current              |       |       | 10    | μA    |

| IIL <sup>2</sup> | Input Low Leakage Current               |       |       | 10    | μA    |

| VODIFF           | Differential Output Voltage             | 250   | 350   | 450   | mV    |

| VOCM             | Output Common Mode Voltage              | 1.125 | 1.25  | 1.375 | V     |

| VICM             | Input Common Mode Voltage               | 0.05  | 1.25  | 2.35  | V     |

| VIDIFF           | Input Differential Voltage <sup>2</sup> | 100   | 350   |       | mV    |

### Table 2-78 • LVDS Minimum and Maximum DC Input and Output Levels

Notes:

1. IOL/IOH defined by VODIFF/(Resistor Network).

2. Currents are measured at 85°C junction temperature.

### Table 2-79 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | -               |

*Note:* \*Measuring point = Vtrip. See Table 2-15 on page 2-18 for a complete table of trip points.

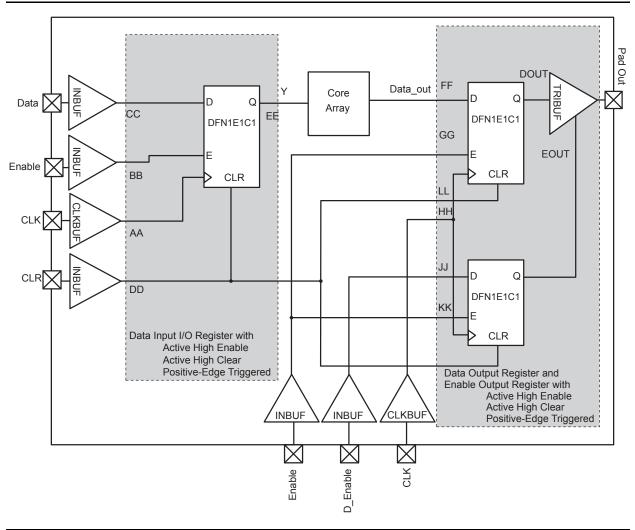

# Fully Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

Figure 2-26 • Timing Model of the Registered I/O Buffers with Synchronous Enable and Asynchronous Clear

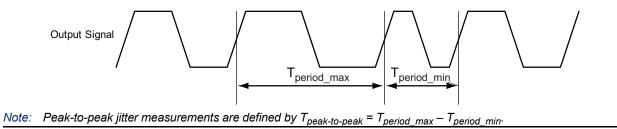

Figure 2-39 • Peak-to-Peak Jitter Definition

**Wicrosemi**. ProASIC3E DC and Switching Characteristics

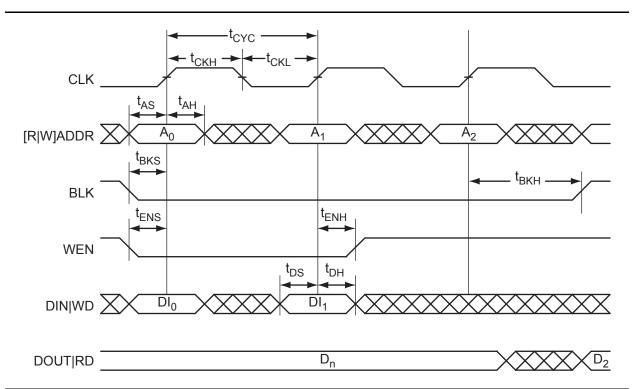

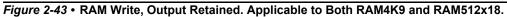

Figure 2-44 • RAM Write, Output as Write Data. Applicable to RAM4K9 Only.

# 🌜 Microsemi.

ProASIC3E DC and Switching Characteristics

# **Timing Characteristics**

### Table 2-99 • RAM4K9

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -2   | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.14 | 0.16 | 0.19 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 0.23 | 0.27 | 0.31 | ns    |

| t <sub>BKH</sub>      | BLK hold time                                                                                                       | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 1.79 | 2.03 | 2.39 | ns    |

|                       | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>C2CWWL</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Closing Edge        | 0.33 | 0.28 | 0.25 | ns    |

| t <sub>C2CWWH</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Rising Edge         | 0.30 | 0.26 | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.45 | 0.38 | 0.34 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.49 | 0.42 | 0.37 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on DO (flow-through)                                                                      | 0.92 | 1.05 | 1.23 | ns    |

|                       | RESET Low to Data Out Low on DO (pipelined)                                                                         | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-5 for derating values.

|            | PQ208             |            | PQ208             |

|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| 118        | IO134NDB3V2       | 157        | VMV1              |

| 119        | IO134PDB3V2       | 158        | GNDQ              |

| 120        | IO132NDB3V2       | 159        | GBA1/IO81PDB1V4   |

| 121        | IO132PDB3V2       | 160        | GBA0/IO81NDB1V4   |

| 122        | GND               | 161        | GBB1/IO80PDB1V4   |

| 123        | VCCIB3            | 162        | GND               |

| 124        | GCC2/IO117PSB3V0  | 163        | GBB0/IO80NDB1V4   |

| 125        | GCB2/IO116PSB3V0  | 164        | GBC1/IO79PDB1V4   |

| 126        | NC                | 165        | GBC0/IO79NDB1V4   |

| 127        | IO115NDB3V0       | 166        | IO74PDB1V4        |

| 128        | GCA2/IO115PDB3V0  | 167        | IO74NDB1V4        |

| 129        | GCA1/IO114PPB3V0  | 168        | IO70PDB1V3        |

| 130        | GND               | 169        | IO70NDB1V3        |

| 131        | VCCPLC            | 170        | VCCIB1            |

| 132        | GCA0/IO114NPB3V0  | 171        | VCC               |

| 133        | VCOMPLC           | 172        | IO56PSB1V1        |

| 134        | GCB0/IO113NDB2V3  | 173        | IO55PDB1V1        |

| 135        | GCB1/IO113PDB2V3  | 174        | IO55NDB1V1        |

| 136        | GCC1/IO112PSB2V3  | 175        | IO54PDB1V1        |

| 137        | IO110NDB2V3       | 176        | IO54NDB1V1        |

| 138        | IO110PDB2V3       | 177        | IO40PDB0V4        |

| 139        | IO106PSB2V3       | 178        | GND               |

| 140        | VCCIB2            | 179        | IO40NDB0V4        |

| 141        | GND               | 180        | IO37PDB0V4        |

| 142        | VCC               | 181        | IO37NDB0V4        |

| 143        | IO99NDB2V2        | 182        | IO35PDB0V4        |

| 144        | IO99PDB2V2        | 183        | IO35NDB0V4        |

| 145        | IO96NDB2V1        | 184        | IO32PDB0V3        |

| 146        | IO96PDB2V1        | 185        | IO32NDB0V3        |

| 147        | IO91NDB2V1        | 186        | VCCIB0            |

| 148        | IO91PDB2V1        | 187        | VCC               |

| 149        | IO88NDB2V0        | 188        | IO28PDB0V3        |

| 150        | IO88PDB2V0        | 189        | IO28NDB0V3        |

| 151        | GBC2/IO84PSB2V0   | 190        | IO24PDB0V2        |

| 152        | GBA2/IO82PSB2V0   | 191        | IO24NDB0V2        |

| 153        | GBB2/IO83PSB2V0   | 192        | IO21PSB0V2        |

| 154        | VMV2              | 193        | IO16PDB0V1        |

| 155        | GNDQ              | 194        | IO16NDB0V1        |

| 156        | GND               | 195        | GND               |

|            |                   | -          |                   |

| PQ208      |                   |  |  |  |  |

|------------|-------------------|--|--|--|--|

| Pin Number | A3PE3000 Function |  |  |  |  |

| 196        | IO11PDB0V1        |  |  |  |  |

| 197        | IO11NDB0V1        |  |  |  |  |

| 198        | IO08PDB0V0        |  |  |  |  |

| 199        | IO08NDB0V0        |  |  |  |  |

| 200        | VCCIB0            |  |  |  |  |

| 201        | GAC1/IO02PDB0V0   |  |  |  |  |

| 202        | GAC0/IO02NDB0V0   |  |  |  |  |

| 203        | GAB1/IO01PDB0V0   |  |  |  |  |

| 204        | GAB0/IO01NDB0V0   |  |  |  |  |

| 205        | GAA1/IO00PDB0V0   |  |  |  |  |

| 206        | GAA0/IO00NDB0V0   |  |  |  |  |

| 207        | GNDQ              |  |  |  |  |

| 208        | VMV0              |  |  |  |  |

# FG324

Note: This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

|            | FG324            |            | FG324            |            | FG324           |

|------------|------------------|------------|------------------|------------|-----------------|

| Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA    | Pin Number | A3PE3000 FBGA   |

| A1         | GND              | C1         | IO305NDB7V3      | E1         | IO303NDB7V3     |

| A2         | IO08NDB0V0       | C2         | IO308NDB7V4      | E2         | GNDQ            |

| A3         | IO08PDB0V0       | C3         | GAA2/IO309PPB7V4 | E3         | VMV7            |

| A4         | IO10NDB0V1       | C4         | GAA1/IO00PPB0V0  | E4         | IO307NPB7V4     |

| A5         | IO10PDB0V1       | C5         | VMV0             | E5         | VCCPLA          |

| A6         | IO12PDB0V1       | C6         | IO14NDB0V1       | E6         | GAB0/IO01NPB0V0 |

| A7         | GND              | C7         | IO18PDB0V2       | E7         | VCCIB0          |

| A8         | IO32NDB0V3       | C8         | IO40NDB0V4       | E8         | GND             |

| A9         | IO32PDB0V3       | C9         | IO40PDB0V4       | E9         | IO28NDB0V3      |

| A10        | IO42PPB1V0       | C10        | IO44PDB1V0       | E10        | IO48PDB1V0      |

| A11        | IO52NPB1V1       | C11        | IO56NDB1V1       | E11        | GND             |

| A12        | GND              | C12        | IO64NDB1V2       | E12        | VCCIB1          |

| A13        | IO66NDB1V3       | C13        | IO64PDB1V2       | E13        | IO60NPB1V2      |

| A14        | IO72NDB1V3       | C14        | VMV1             | E14        | VCCPLB          |

| A15        | IO72PDB1V3       | C15        | GBC0/IO79NDB1V4  | E15        | IO82NDB2V0      |

| A16        | IO74NDB1V4       | C16        | GBC1/IO79PDB1V4  | E16        | VMV2            |

| A17        | IO74PDB1V4       | C17        | GBB2/IO83PPB2V0  | E17        | GNDQ            |

| A18        | GND              | C18        | IO88NDB2V0       | E18        | IO90NDB2V1      |

| B1         | IO305PDB7V3      | D1         | IO303PDB7V3      | F1         | IO299NDB7V3     |

| B2         | GAB2/IO308PDB7V4 | D2         | VCCIB7           | F2         | IO299PDB7V3     |

| B3         | GAA0/IO00NPB0V0  | D3         | GAC2/IO307PPB7V4 | F3         | IO295PDB7V2     |

| B4         | VCCIB0           | D4         | IO309NPB7V4      | F4         | IO295NDB7V2     |

| B5         | GNDQ             | D5         | GAB1/IO01PPB0V0  | F5         | VCOMPLA         |

| B6         | IO12NDB0V1       | D6         | IO14PDB0V1       | F6         | IO291PPB7V2     |

| B7         | IO18NDB0V2       | D7         | IO24NDB0V2       | F7         | GAC0/IO02NDB0V0 |

| B8         | VCCIB0           | D8         | IO24PDB0V2       | F8         | GAC1/IO02PDB0V0 |

| B9         | IO42NPB1V0       | D9         | IO28PDB0V3       | F9         | IO26PDB0V3      |

| B10        | IO44NDB1V0       | D10        | IO48NDB1V0       | F10        | IO34PDB0V4      |

| B11        | VCCIB1           | D11        | IO56PDB1V1       | F11        | IO58NDB1V2      |

| B12        | IO52PPB1V1       | D12        | IO60PPB1V2       | F12        | IO58PDB1V2      |

| B13        | IO66PDB1V3       | D13        | GBB0/IO80NDB1V4  | F13        | IO94PPB2V1      |

| B14        | GNDQ             | D14        | GBB1/IO80PDB1V4  | F14        | VCOMPLB         |

| B15        | VCCIB1           | D15        | GBA2/IO82PDB2V0  | F15        | GBC2/IO84PDB2V0 |

| B16        | GBA0/IO81NDB1V4  | D16        | IO83NPB2V0       | F16        | IO84NDB2V0      |

| B17        | GBA1/IO81PDB1V4  | D17        | VCCIB2           | F17        | IO92NDB2V1      |

| B18        | IO88PDB2V0       | D18        | IO90PDB2V1       | F18        | IO92PDB2V1      |

# 🌜 Microsemi.

Package Pin Assignments

| FG484      |                   |            | FG484             |            | FG484             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function | Pin Number | A3PE1500 Function |

| A1         | GND               | AA15       | NC                | B7         | IO10PDB0V1        |

| A2         | GND               | AA16       | IO117NDB4V0       | B8         | IO15NDB0V1        |

| A3         | VCCIB0            | AA17       | IO117PDB4V0       | B9         | IO17NDB0V2        |

| A4         | IO05NDB0V0        | AA18       | IO115NDB4V0       | B10        | IO20PDB0V2        |

| A5         | IO05PDB0V0        | AA19       | IO115PDB4V0       | B11        | IO29PDB0V3        |

| A6         | IO11NDB0V1        | AA20       | NC                | B12        | IO32NDB1V0        |

| A7         | IO11PDB0V1        | AA21       | VCCIB3            | B13        | IO43NDB1V1        |

| A8         | IO15PDB0V1        | AA22       | GND               | B14        | NC                |

| A9         | IO17PDB0V2        | AB1        | GND               | B15        | NC                |

| A10        | IO27NDB0V3        | AB2        | GND               | B16        | IO53NDB1V2        |

| A11        | IO27PDB0V3        | AB3        | VCCIB5            | B17        | IO53PDB1V2        |

| A12        | IO32PDB1V0        | AB4        | IO159NDB5V3       | B18        | IO54PDB1V3        |

| A13        | IO43PDB1V1        | AB5        | IO159PDB5V3       | B19        | NC                |

| A14        | IO47NDB1V1        | AB6        | IO149NDB5V1       | B20        | NC                |

| A15        | IO47PDB1V1        | AB7        | IO149PDB5V1       | B21        | VCCIB2            |

| A16        | IO51NDB1V2        | AB8        | IO138NDB5V0       | B22        | GND               |

| A17        | IO51PDB1V2        | AB9        | IO138PDB5V0       | C1         | VCCIB7            |

| A18        | IO54NDB1V3        | AB10       | NC                | C2         | NC                |

| A19        | NC                | AB11       | NC                | C3         | NC                |

| A20        | VCCIB1            | AB12       | IO127NDB4V2       | C4         | NC                |

| A21        | GND               | AB13       | IO127PDB4V2       | C5         | GND               |

| A22        | GND               | AB14       | IO125NDB4V1       | C6         | IO07NDB0V0        |

| AA1        | GND               | AB15       | IO125PDB4V1       | C7         | IO07PDB0V0        |

| AA2        | VCCIB6            | AB16       | IO122NDB4V1       | C8         | VCC               |

| AA3        | NC                | AB17       | IO122PDB4V1       | C9         | VCC               |

| AA4        | IO161PDB5V3       | AB18       | NC                | C10        | IO20NDB0V2        |

| AA5        | IO155NDB5V2       | AB19       | NC                | C11        | IO29NDB0V3        |

| AA6        | IO155PDB5V2       | AB20       | VCCIB4            | C12        | NC                |

| AA7        | IO154NDB5V2       | AB21       | GND               | C13        | NC                |

| AA8        | IO154PDB5V2       | AB22       | GND               | C14        | VCC               |

| AA9        | IO143PDB5V1       | B1         | GND               | C15        | VCC               |

| AA10       | IO143NDB5V1       | B2         | VCCIB7            | C16        | NC                |

| AA11       | IO131PPB4V2       | B3         | NC                | C17        | NC                |

| AA12       | IO129NDB4V2       | B4         | IO03NDB0V0        | C18        | GND               |

| AA13       | IO129PDB4V2       | B5         | IO03PDB0V0        | C19        | NC                |

| AA14       | NC                | B6         | IO10NDB0V1        | C20        | NC                |

| FG484      |                   |            | FG484             |            | FG484             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| H19        | IO100PDB2V2       | K11        | GND               | M3         | IO272NDB6V4       |

| H20        | VCC               | K12        | GND               | M4         | GFA2/IO272PDB6V4  |

| H21        | VMV2              | K13        | GND               | M5         | GFA1/IO273PDB6V4  |

| H22        | IO105PDB2V2       | K14        | VCC               | M6         | VCCPLF            |

| J1         | IO285NDB7V1       | K15        | VCCIB2            | M7         | IO271NDB6V4       |

| J2         | IO285PDB7V1       | K16        | GCC1/IO112PPB2V3  | M8         | GFB2/IO271PDB6V4  |

| J3         | VMV7              | K17        | IO108NDB2V3       | M9         | VCC               |

| J4         | IO279PDB7V0       | K18        | IO108PDB2V3       | M10        | GND               |

| J5         | IO283PDB7V1       | K19        | IO110NPB2V3       | M11        | GND               |

| J6         | IO281PDB7V0       | K20        | IO106NPB2V3       | M12        | GND               |

| J7         | IO287NDB7V1       | K21        | IO109NDB2V3       | M13        | GND               |

| J8         | VCCIB7            | K22        | IO107NDB2V3       | M14        | VCC               |

| J9         | GND               | L1         | IO257PSB6V2       | M15        | GCB2/IO116PPB3V0  |

| J10        | VCC               | L2         | IO276PDB7V0       | M16        | GCA1/IO114PPB3V0  |

| J11        | VCC               | L3         | IO276NDB7V0       | M17        | GCC2/IO117PPB3V0  |

| J12        | VCC               | L4         | GFB0/IO274NPB7V0  | M18        | VCCPLC            |

| J13        | VCC               | L5         | GFA0/IO273NDB6V4  | M19        | GCA2/IO115PDB3V0  |

| J14        | GND               | L6         | GFB1/IO274PPB7V0  | M20        | IO115NDB3V0       |

| J15        | VCCIB2            | L7         | VCOMPLF           | M21        | IO126PDB3V1       |

| J16        | IO84NDB2V0        | L8         | GFC0/IO275NPB7V0  | M22        | IO124PSB3V1       |

| J17        | IO104NDB2V2       | L9         | VCC               | N1         | IO255PPB6V2       |

| J18        | IO104PDB2V2       | L10        | GND               | N2         | IO253NDB6V2       |

| J19        | IO106PPB2V3       | L11        | GND               | N3         | VMV6              |

| J20        | GNDQ              | L12        | GND               | N4         | GFC2/IO270PPB6V4  |

| J21        | IO109PDB2V3       | L13        | GND               | N5         | IO261PPB6V3       |

| J22        | IO107PDB2V3       | L14        | VCC               | N6         | IO263PDB6V3       |

| K1         | IO277NDB7V0       | L15        | GCC0/IO112NPB2V3  | N7         | IO263NDB6V3       |

| K2         | IO277PDB7V0       | L16        | GCB1/IO113PPB2V3  | N8         | VCCIB6            |

| K3         | GNDQ              | L17        | GCA0/IO114NPB3V0  | N9         | VCC               |

| K4         | IO279NDB7V0       | L18        | VCOMPLC           | N10        | GND               |

| K5         | IO283NDB7V1       | L19        | GCB0/IO113NPB2V3  | N11        | GND               |

| K6         | IO281NDB7V0       | L20        | IO110PPB2V3       | N12        | GND               |

| K7         | GFC1/IO275PPB7V0  | L21        | IO111NDB2V3       | N13        | GND               |

| K8         | VCCIB7            | L22        | IO111PDB2V3       | N14        | VCC               |

| K9         | VCC               | M1         | GNDQ              | N15        | VCCIB3            |

| K10        | GND               | M2         | IO255NPB6V2       | N16        | IO116NPB3V0       |

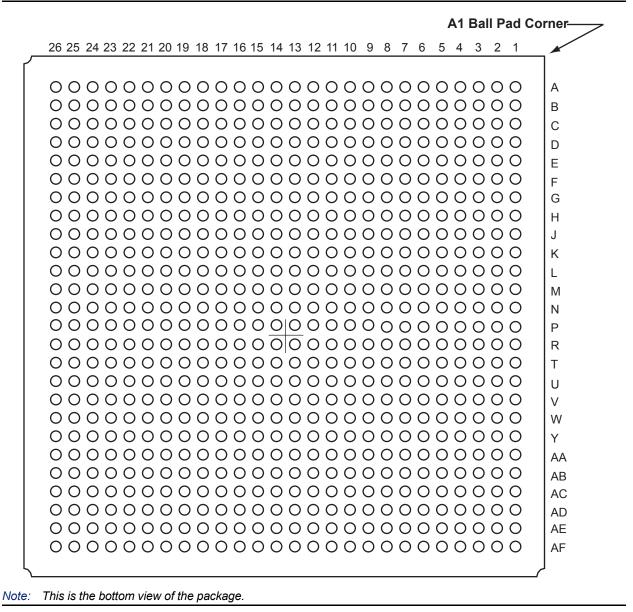

# FG676

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at *http://www.microsemi.com/products/fpga-soc/solutions*.

| FG896      |                   |            | FG896             |            | FG896             |

|------------|-------------------|------------|-------------------|------------|-------------------|

| Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function | Pin Number | A3PE3000 Function |

| A2         | GND               | AA9        | GEB1/IO235PPB6V0  | AB15       | IO198PDB5V0       |

| A3         | GND               | AA10       | VCC               | AB16       | IO192NDB4V4       |

| A4         | IO14NPB0V1        | AA11       | IO226PPB5V4       | AB17       | IO192PDB4V4       |

| A5         | GND               | AA12       | VCCIB5            | AB18       | IO178NDB4V3       |

| A6         | IO07NPB0V0        | AA13       | VCCIB5            | AB19       | IO178PDB4V3       |

| A7         | GND               | AA14       | VCCIB5            | AB20       | IO174NDB4V2       |

| A8         | IO09NDB0V1        | AA15       | VCCIB5            | AB21       | IO162NPB4V1       |

| A9         | IO17NDB0V2        | AA16       | VCCIB4            | AB22       | VCC               |

| A10        | IO17PDB0V2        | AA17       | VCCIB4            | AB23       | VCCPLD            |

| A11        | IO21NDB0V2        | AA18       | VCCIB4            | AB24       | VCCIB3            |

| A12        | IO21PDB0V2        | AA19       | VCCIB4            | AB25       | IO150PDB3V4       |

| A13        | IO33NDB0V4        | AA20       | IO174PDB4V2       | AB26       | IO148PDB3V4       |

| A14        | IO33PDB0V4        | AA21       | VCC               | AB27       | IO147NDB3V4       |

| A15        | IO35NDB0V4        | AA22       | IO142NPB3V3       | AB28       | IO145PDB3V3       |

| A16        | IO35PDB0V4        | AA23       | IO144NDB3V3       | AB29       | IO143PDB3V3       |

| A17        | IO41NDB1V0        | AA24       | IO144PDB3V3       | AB30       | IO137PDB3V2       |

| A18        | IO43NDB1V0        | AA25       | IO146NDB3V4       | AC1        | IO254PDB6V2       |

| A19        | IO43PDB1V0        | AA26       | IO146PDB3V4       | AC2        | IO254NDB6V2       |

| A20        | IO45NDB1V0        | AA27       | IO147PDB3V4       | AC3        | IO240PDB6V0       |

| A21        | IO45PDB1V0        | AA28       | IO139NDB3V3       | AC4        | GEC1/IO236PDB6V0  |

| A22        | IO57NDB1V2        | AA29       | IO139PDB3V3       | AC5        | IO237PDB6V0       |

| A23        | IO57PDB1V2        | AA30       | IO133NDB3V2       | AC6        | IO237NDB6V0       |

| A24        | GND               | AB1        | IO256NDB6V2       | AC7        | VCOMPLE           |

| A25        | IO69PPB1V3        | AB2        | IO244PDB6V1       | AC8        | GND               |

| A26        | GND               | AB3        | IO244NDB6V1       | AC9        | IO226NPB5V4       |

| A27        | GBC1/IO79PPB1V4   | AB4        | IO241PDB6V0       | AC10       | IO222NDB5V3       |

| A28        | GND               | AB5        | IO241NDB6V0       | AC11       | IO216NPB5V2       |

| A29        | GND               | AB6        | IO243NPB6V1       | AC12       | IO210NPB5V2       |

| AA1        | IO256PDB6V2       | AB7        | VCCIB6            | AC13       | IO204NDB5V1       |

| AA2        | IO248PDB6V1       | AB8        | VCCPLE            | AC14       | IO204PDB5V1       |

| AA3        | IO248NDB6V1       | AB9        | VCC               | AC15       | IO194NDB5V0       |

| AA4        | IO246NDB6V1       | AB10       | IO222PDB5V3       | AC16       | IO188NDB4V4       |

| AA5        | GEA1/IO234PDB6V0  | AB11       | IO218PPB5V3       | AC17       | IO188PDB4V4       |

| AA6        | GEA0/IO234NDB6V0  | AB12       | IO206NDB5V1       | AC18       | IO182PPB4V3       |

| AA7        | IO243PPB6V1       | AB13       | IO206PDB5V1       | AC19       | IO170NPB4V2       |

| AA8        | IO245NDB6V1       | AB14       | IO198NDB5V0       | AC20       | IO164NDB4V1       |

Datasheet Information

| Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Revision 11<br>(August 2012) | Added a Note stating "VMV pins must be connected to the corresponding VCCI pins.<br>See the "VMVx I/O Supply Voltage (quiet)" section on page 3-1 for further<br>information." to Table 2-1 • Absolute Maximum Ratings and Table 2-2<br>• Recommended Operating Conditions <sup>1</sup> (SAR 38322).                                                                                                                                                                                                                | 2-1<br>3-1<br>2-1            |

|                              | The drive strength, IOL, and IOH value for 3.3 V GTL and 2.5 V GTL was changed from 25 mA to 20 mA in the following tables (SAR 31924):<br>"Summary of Maximum and Minimum DC Input and Output Levels" table<br>"Summary of I/O Timing Characteristics—Software Default Settings" table<br>"I/O Output Buffer Maximum Resistances <sup>1</sup> " table<br>"Minimum and Maximum DC Input and Output Levels" table)                                                                                                   | 2-16<br>2-19<br>2-20<br>2-39 |

|                              | "Minimum and Maximum DC Input and Output Levels" table<br>Also added note stating "Output drive strength is below JEDEC specification" for<br>Tables 2-17 and 2-19.<br>Additionally, the IOL and IOH values for 3.3 V GTL+ and 2.5 V GTL+ were<br>corrected from 51 to 35 (for 3.3 V GTL+) and from 40 to 33 (for 2.5 V GTL+) in<br>table Table 2-13 (SAR 39714).                                                                                                                                                   | 2-40                         |

|                              | "Duration of Short Circuit Event Before Failure" table was revised to change the maximum temperature from 110°C to 100°C, with an example of six months instead of three months (SAR 37934).                                                                                                                                                                                                                                                                                                                        | 2-22                         |

|                              | The following sentence was deleted from the "2.5 V LVCMOS" section (SAR 34796):<br>"It uses a 5 V-tolerant input buffer and push-pull output buffer." This change was<br>made in revision 10 and omitted from the change table in error.                                                                                                                                                                                                                                                                            | 2-30                         |

| Revision 11<br>(continued)   | Figure 2-11 was updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34889).                                                                                                                                                                                                                                                                                                                                                                         | 2-38                         |

|                              | In Table 2-81 VIL and VIH were revised so that the maximum is 3.6 V for all listed values of VCCI (SAR 37222).                                                                                                                                                                                                                                                                                                                                                                                                      | 2-52                         |

|                              | Figure 2-47 and Figure 2-48 are new (SAR 34848).                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-79                         |

|                              | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions and Packaging" chapter: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38322). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1                          |

| Revision                    | Changes                                                                                                                                                                              | Page |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Advance v0.5<br>(continued) | The "RESET" section was updated.                                                                                                                                                     | 2-25 |

|                             | The "RESET" section was updated.                                                                                                                                                     | 2-27 |

|                             | The "Introduction" of the "Introduction" section was updated.                                                                                                                        | 2-28 |

|                             | PCI-X 3.3 V was added to the Compatible Standards for 3.3 V in Table 2-<br>11 • VCCI Voltages and Compatible Standards                                                               | 2-29 |

|                             | Table 2-35 • ProASIC3E I/O Features was updated.                                                                                                                                     | 2-54 |

|                             | The "Double Data Rate (DDR) Support" section was updated to include information concerning implementation of the feature.                                                            | 2-32 |

|                             | The "Electrostatic Discharge (ESD) Protection" section was updated to include testing information.                                                                                   | 2-35 |

|                             | Level 3 and 4 descriptions were updated in Table 2-43 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3 Devices.                                                       | 2-64 |

|                             | The notes in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices were updated.                                                                       | 2-64 |

|                             | The "Simultaneous Switching Outputs (SSOs) and Printed Circuit Board Layout" section is new.                                                                                         | 2-41 |

|                             | A footnote was added to Table 2-37 • Maximum I/O Frequency for Single-Ended and Differential I/Os in All Banks in ProASIC3E Devices (maximum drive strength and high slew selected). | 2-55 |

|                             | Table 2-48 • ProASIC3E I/O Attributes vs. I/O Standard Applications                                                                                                                  | 2-81 |

|                             | Table 2-55 • ProASIC3 I/O Standards—SLEW and Output Drive (OUT_DRIVE) Settings                                                                                                       | 2-85 |

|                             | The "x" was updated in the "Pin Descriptions" section.                                                                                                                               | 2-50 |

|                             | The "VCC Core Supply Voltage" pin description was updated.                                                                                                                           | 2-50 |

|                             | The "VMVx I/O Supply Voltage (quiet)" pin description was updated to include information concerning leaving the pin unconnected.                                                     | 2-50 |

|                             | EXTFB was removed from Figure 2-24 • ProASIC3E CCC Options.                                                                                                                          | 2-24 |

|                             | The CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> was updated in Table 2-13 • ProASIC3E CCC/PLL Specification.                                                          | 2-30 |

|                             | EXTFB was removed from Figure 2-27 • CCC/PLL Macro.                                                                                                                                  | 2-28 |

|                             | The LVPECL specification in Table 2-45 • I/O Hot-Swap and 5 V Input Tolerance Capabilities in ProASIC3E Devices was updated.                                                         | 2-64 |

|                             | Table 2-15 • Levels of Hot-Swap Support was updated.                                                                                                                                 | 2-34 |

|                             | The "Cold-Sparing Support" section was updated.                                                                                                                                      | 2-34 |

|                             | "Electrostatic Discharge (ESD) Protection" section was updated.                                                                                                                      | 2-35 |

|                             | The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions" section.                                                                                                   | 2-50 |

|                             | The "VJTAG JTAG Supply Voltage" pin description was updated.                                                                                                                         | 2-50 |

|                             | The "VPUMP Programming Supply Voltage" pin description was updated to include information on what happens when the pin is tied to ground.                                            | 2-50 |