Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                         |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), UART/USART                                 |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b                                                       |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 10-VFDFN Exposed Pad                                           |

| Supplier Device Package    | 11-QFN (3x3)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f300-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.4.Using the SMBus                                   | 115 |

|--------------------------------------------------------|-----|

| 13.4.1.SMBus Configuration Register                    |     |

| 13.4.2.SMB0CN Control Register                         |     |

| 13.4.3.Data Register                                   |     |

| 13.5.SMBus Transfer Modes                              |     |

| 13.5.1.Master Transmitter Mode                         |     |

| 13.5.2.Master Receiver Mode                            |     |

| 13.5.3.Slave Receiver Mode                             |     |

| 13.5.4.Slave Transmitter Mode                          |     |

|                                                        |     |

| 13.6.SMBus Status Decoding                             |     |

| 14.1.Enhanced Baud Rate Generation                     |     |

|                                                        |     |

| 14.2.Operational Modes                                 |     |

| 14.2.1.8-Bit UART                                      |     |

| 14.2.2.9-Bit UART                                      |     |

| 14.3.Multiprocessor Communications                     |     |

| 15. Timers                                             |     |

| 15.1.Timer 0 and Timer 1                               |     |

| 15.1.1.Mode 0: 13-bit Counter/Timer                    |     |

| 15.1.2.Mode 1: 16-bit Counter/Timer                    |     |

| 15.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 15.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

| 15.2.Timer 2                                           |     |

| 15.2.1.16-bit Timer with Auto-Reload                   |     |

| 15.2.2.8-bit Timers with Auto-Reload                   |     |

| 16. Programmable Counter Array                         |     |

| 16.1.PCA Counter/Timer                                 |     |

| 16.2.Capture/Compare Modules                           |     |

| 16.2.1.Edge-triggered Capture Mode                     |     |

| 16.2.2.Software Timer (Compare) Mode                   | 159 |

| 16.2.3.High Speed Output Mode                          | 160 |

| 16.2.4. Frequency Output Mode                          | 161 |

| 16.2.5.8-Bit Pulse Width Modulator Mode                | 162 |

| 16.2.6.16-Bit Pulse Width Modulator Mode               | 163 |

| 16.3.Watchdog Timer Mode                               | 164 |

| 16.3.1.Watchdog Timer Operation                        |     |

| 16.3.2.Watchdog Timer Usage                            | 165 |

| 16.4.Register Descriptions for PCA                     |     |

| 17.C2 Interface                                        |     |

| 17.1.C2 Interface Registers                            |     |

| 17.2.C2 Pin Sharing                                    |     |

| Document Change List                                   |     |

| Contact Information                                    |     |

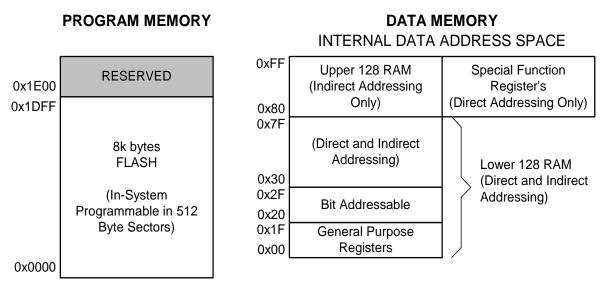

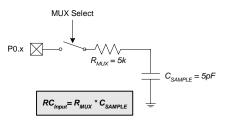

## 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

The C8051F300/1/2/3 includes 8k bytes of Flash program memory (the C8051F304 includes 4k bytes; the C8051F305 includes 2k bytes). This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.5 for the C8051F300/1/2/3 system memory map.

Figure 1.5. On-chip Memory Map (C8051F300/1/2/3 Shown)

## Table 3.1. Global Electrical Characteristics (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                       | Conditions                                                  | Min | Тур   | Max | Units  |

|-------------------------------------------------|-------------------------------------------------------------|-----|-------|-----|--------|

| I <sub>DD</sub> Supply Sensitivity (Note 3)     | F = 25 MHz                                                  | _   | 47    | _   | %/V    |

|                                                 | F = 1 MHz                                                   | —   | 59    | —   | %/V    |

| I <sub>DD</sub> Frequency Sensitivity           | V <sub>DD</sub> = 3.0 V, F <= 1 MHz, T = 25 °C              | _   | 0.27  |     | mA/MHz |

| (Note 3, Note 5)                                | V <sub>DD</sub> = 3.0 V, F > 1 MHz, T = 25 °C               | _   | 0.10  | _   | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F <= 1 MHz, T = 25 ℃               | —   | 0.35  | —   | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F > 1 MHz, T = 25 °C               | —   | 0.12  | _   | mA/MHz |

| Digital Supply Current<br>(Stop Mode, shutdown) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled | —   | < 0.1 | —   | μA     |

### Notes:

- 1. Given in Table 9.2 on page 86.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data; Not production tested.

- 4. Normal IDD can be estimated for frequencies <= 15 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for >15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 3.0 V; F = 20 MHz,  $I_{DD}$  = 6.6 mA – (25 MHz – 20 MHz) x 0.16 mA/MHz = 5.8 mA.

5. Idle IDD can be estimated for frequencies <= 1 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for >1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 3.3 mA – (25 MHz – 5 MHz) x 0.10 mA/MHz = 1.3 mA.

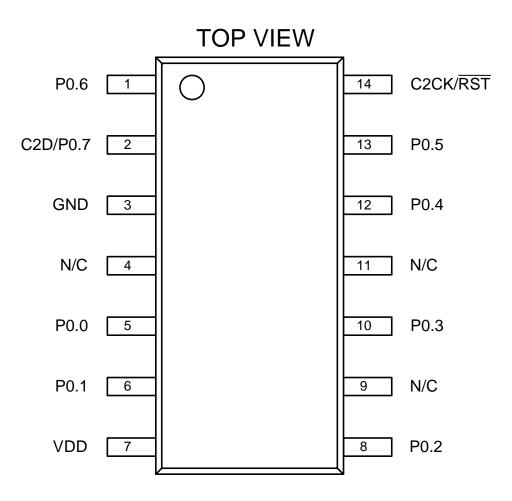

Figure 4.5. SOIC-14 Pinout Diagram (Top View)

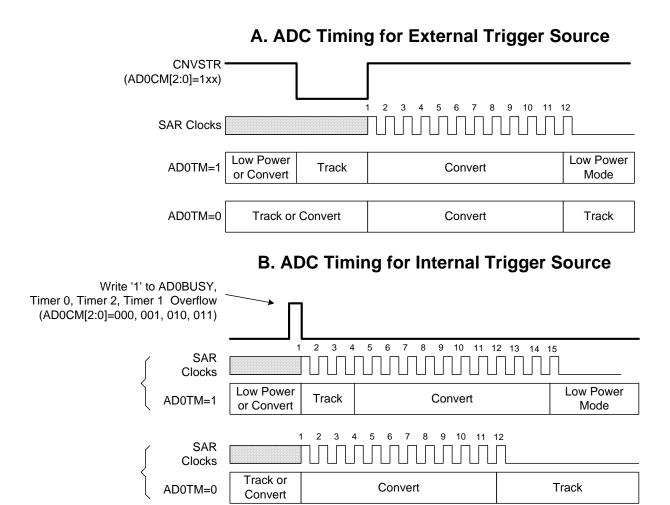

### 5.3.2. Tracking Modes

According to Table 5.1 on page 47, each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate. The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked except when a conversion is in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 5.4). Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX or PGA settings are frequently changed, due to the settling time requirements described in **Section "5.3.3. Settling Time Requirements" on page 41**.

Figure 5.4. 8-Bit ADC Track and Conversion Example Timing

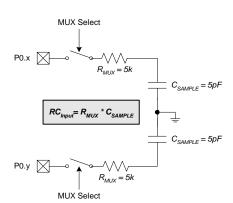

### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 or PGA selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

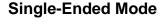

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time (track/hold time) requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

## Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (8).

**Differential Mode**

Note: When the PGA gain is set to 0.5,  $C_{SAMPLE} = 3pF$

## Figure 5.5. ADC0 Equivalent Input Circuits

Comparator0 interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see **Section "8.3. Interrupt Handler" on page 72**). The CP0FIF flag is set to logic 1 upon a Comparator0 falling-edge interrupt, and the CP0RIF flag is set to logic 1 upon the Comparator0 rising-edge interrupt. Once set, these bits remain set until cleared by software. The output state of Comparator0 can be obtained at any time by reading the CP0OUT bit. Comparator0 is enabled by setting the CP0EN bit to logic 1, and is disabled by clearing this bit to logic 0.

| R/W       | R                                                                                             | R/W                               | R/W        | R/W       | R/W     | R/W           | R/W          | Reset Value  |

|-----------|-----------------------------------------------------------------------------------------------|-----------------------------------|------------|-----------|---------|---------------|--------------|--------------|

| CP0EN     | CP0OUT                                                                                        | <b>CP0RIF</b>                     | CP0FIF     | CP0HYP1   | CP0HYP0 | CP0HYN1       | CP0HYN0      | 00000000     |

| Bit7      | Bit6                                                                                          | Bit5                              | Bit4       | Bit3      | Bit2    | Bit1          | Bit0         | SFR Address: |

|           |                                                                                               |                                   |            |           |         | (bit          | addressable) | 0xF8         |

|           |                                                                                               |                                   |            |           |         | ,             | ,            |              |

| Bit7:     | CP0EN: Cor                                                                                    | nparator0 E                       | nable Bit. |           |         |               |              |              |

|           | 0: Comparat                                                                                   | or0 Disable                       | d.         |           |         |               |              |              |

|           | 1: Comparat                                                                                   | or0 Enable                        | d.         |           |         |               |              |              |

| Bit6:     | CP0OUT: Co                                                                                    | omparator0                        | Output Sta | ite Flag. |         |               |              |              |

|           | 0: Voltage or                                                                                 | ר CP0+ < C                        | P0–.       |           |         |               |              |              |

|           | 1: Voltage or                                                                                 | ר CP0+ > C                        | P0–.       |           |         |               |              |              |

| Bit5:     | CP0RIF: Co                                                                                    |                                   |            |           |         |               |              |              |

|           | 0: No Compa                                                                                   |                                   |            |           |         | nce this flag | was last cl  | eared.       |

|           | 1: Comparat                                                                                   | -                                 | -          | •         |         |               |              |              |

| Bit4:     | CP0FIF: Cor                                                                                   |                                   |            |           |         |               |              |              |

|           | 0: No Compa                                                                                   |                                   |            |           |         | nce this flag | g was last c | leared.      |

|           | 1: Comparat                                                                                   | -                                 | -          | •         |         |               |              |              |

| Bits3–2:  | CP0HYP1–0: Comparator0 Positive Hysteresis Control Bits.                                      |                                   |            |           |         |               |              |              |

|           |                                                                                               | 00: Positive Hysteresis Disabled. |            |           |         |               |              |              |

|           | 01: Positive Hysteresis = 5 mV.                                                               |                                   |            |           |         |               |              |              |

|           | 10: Positive Hysteresis = 10 mV.                                                              |                                   |            |           |         |               |              |              |

| Bits1–0:  | 11: Positive Hysteresis = 20 mV.                                                              |                                   |            |           |         |               |              |              |

| Dits I=0. | CP0HYN1–0: Comparator0 Negative Hysteresis Control Bits.<br>00: Negative Hysteresis Disabled. |                                   |            |           |         |               |              |              |

|           | 01: Negative Hysteresis Disabled.<br>01: Negative Hysteresis = 5 mV.                          |                                   |            |           |         |               |              |              |

|           | 10: Negative Hysteresis = 5 mV.                                                               |                                   |            |           |         |               |              |              |

|           | 11: Negative Hysteresis = 20 mV.                                                              |                                   |            |           |         |               |              |              |

|           | ·····togativo                                                                                 |                                   | 20         |           |         |               |              |              |

|           |                                                                                               |                                   |            |           |         |               |              |              |

## SFR Definition 7.1. CPT0CN: Comparator0 Control

## 8.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 8.2 and Figure 8.3.

### 8.2.1. Program Memory

The CIP-51 core has a 64k-byte program memory space. The C8051F300/1/2/3 implements 8192 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Note: 512 bytes (0x1E00 - 0x1FFF) of this memory are reserved for factory use and are not available for user program storage. The C8051F304 implements 4096 bytes of reprogrammable Flash program memory space; the C8051F305 implements 2048 bytes of reprogrammable Flash program memory space. Figure 8.2 shows the program memory maps for C8051F300/1/2/3/4/5 devices.

Figure 8.2. Program Memory Maps

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 89** for further details.

| R/W      | R/W                                                                                                      | R/W                    | R/W          | R/W          | R/W          | R/W  | R/W  | Reset Value  |  |

|----------|----------------------------------------------------------------------------------------------------------|------------------------|--------------|--------------|--------------|------|------|--------------|--|

| _        | —                                                                                                        | PT2                    | PS0          | PT1          | PX1          | PT0  | PX0  | 11000000     |  |

| Bit7     | Bit6                                                                                                     | Bit5                   | Bit4         | Bit3         | Bit2         | Bit1 | Bit0 | SFR Address: |  |

|          |                                                                                                          | (bit addressable) 0xB8 |              |              |              |      |      |              |  |

|          |                                                                                                          |                        |              |              |              |      |      |              |  |

| Bits7–6: | UNUSED. F                                                                                                | Read = 11b             | , Write = do | n't care.    |              |      |      |              |  |

| Bit5:    | PT2: Timer                                                                                               | 2 Interrupt            | Priority Cor | ntrol.       |              |      |      |              |  |

|          | This bit sets                                                                                            | the priority           | / of the Tim | er 2 interru | pt.          |      |      |              |  |

|          | 0: Timer 2 ir                                                                                            |                        |              |              |              |      |      |              |  |

|          | 1: Timer 2 ir                                                                                            |                        |              |              |              |      |      |              |  |

| Bit4:    | PS0: UART                                                                                                |                        |              |              |              |      |      |              |  |

|          | This bit sets                                                                                            |                        |              |              | ot.          |      |      |              |  |

|          | 0: UART0 ir                                                                                              | •                      |              | •            |              |      |      |              |  |

|          | 1: UART0 in                                                                                              | •                      | • •          |              |              |      |      |              |  |

| Bit3:    | PT1: Timer                                                                                               |                        |              |              |              |      |      |              |  |

|          | This bit sets                                                                                            |                        |              |              | pt.          |      |      |              |  |

|          | 0: Timer 1 ir                                                                                            |                        |              |              |              |      |      |              |  |

| D:+0.    | 1: Timer 1 ir                                                                                            |                        |              |              |              |      |      |              |  |

| Bit2:    | PX1: Extern                                                                                              |                        |              |              | unt diato mu |      |      |              |  |

|          | This bit sets                                                                                            |                        |              |              | •            | ipt. |      |              |  |

|          | 0: External I<br>1: External I                                                                           |                        |              |              |              |      |      |              |  |

| Bit1:    | PT0: Timer                                                                                               |                        |              |              | 1.           |      |      |              |  |

| DILT.    |                                                                                                          |                        |              |              | nt           |      |      |              |  |

|          | This bit sets the priority of the Timer 0 interrupt.<br>0: Timer 0 interrupts set to low priority level. |                        |              |              |              |      |      |              |  |

|          | 1: Timer 0 interrupts set to high priority level.                                                        |                        |              |              |              |      |      |              |  |

| Bit0:    | PX0: External Interrupt 0 Priority Control.                                                              |                        |              |              |              |      |      |              |  |

| 2.00.    | This bit sets the priority of the External Interrupt 0 interrupt.                                        |                        |              |              |              |      |      |              |  |

|          | 0: External Interrupt 0 set to low priority level.                                                       |                        |              |              |              |      |      |              |  |

|          | 1: External I                                                                                            |                        |              |              |              |      |      |              |  |

|          |                                                                                                          |                        | 3.1          |              |              |      |      |              |  |

|          |                                                                                                          |                        |              |              |              |      |      |              |  |

## SFR Definition 8.8. IP: Interrupt Priority

# C8051F300/1/2/3/4/5

NOTES:

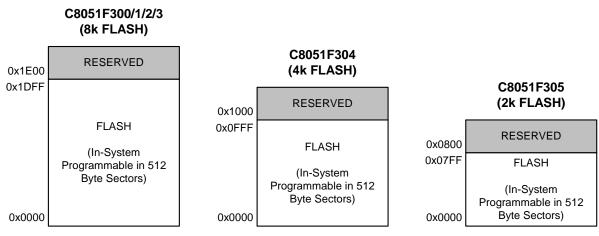

# 13. SMBus

The SMBus I/O interface is a two-wire bidirectional serial bus. The SMBus is compliant with the System Management Bus Specification, version 1.1, and compatible with the I<sup>2</sup>C serial bus. Reads and writes to the interface by the system controller are byte oriented with the SMBus interface autonomously controlling the serial transfer of the data. Data can be transferred at up to 1/20th of the system clock operating as master or slave (this can be faster than allowed by the SMBus specification, depending on the system clock used). A method of extending the clock-low duration is available to accommodate devices with different speed capabilities on the same bus.

The SMBus interface may operate as a master and/or slave, and may function on a bus with multiple masters. The SMBus provides control of SDA (serial data), SCL (serial clock) generation and synchronization, arbitration logic, and START/STOP control and generation. Three SFRs are associated with the SMBus: SMB0CF configures the SMBus; SMB0CN controls the status of the SMBus; and SMB0DAT is the data register, used for both transmitting and receiving SMBus data and slave addresses.

Figure 13.1. SMBus Block Diagram

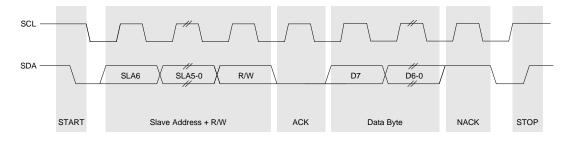

The direction bit (R/W) occupies the least significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 13.3 illustrates a typical SMBus transaction.

Figure 13.3. SMBus Transaction

### 13.3.1. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see **Section "13.3.4. SCL High (SMBus Free) Timeout" on page 114**). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

### 13.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

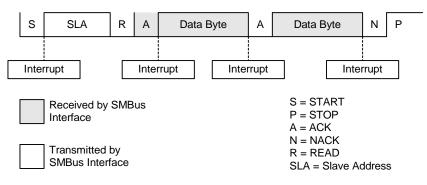

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "13.5. SMBus Transfer Modes" on page 123** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "13.4.2. SMB0CN Control Register" on page 119**; Table 13.4 provides a quick SMB0CN decoding reference.

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in **Section "13.4.1. SMBus Configura**tion Register" on page 116.

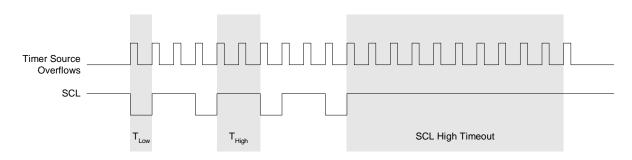

## Figure 13.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 13.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |

|---------|-------------------------------------------------------------------------------------|-----------------------|

| 0       | T <sub>low</sub> – 4 system clocks<br>OR<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |

| 1       | 11 system clocks                                                                    | 12 system clocks      |

Table 13.2. Minimum SDA Setup and Hold Times

\*Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. The s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero.

With the SMBTOE bit set, Timer 2 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see **Section "13.3.3. SCL Low Timeout" on page 114**). The SMBus interface will force Timer 2 to reload while SCL is high, and allow Timer 2 to count when SCL is low. The Timer 2 interrupt service routine should be used to reset SMBus communication by disabling and reenabling the SMBus. Timer 2 configuration is described in **Section "15.2. Timer 2" on page 151**.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 13.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

### 13.5.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. After each byte is received, ACKRQ is set to '1' and an interrupt is generated. Software must write the ACK bit (SMB0CN.1) to define the outgoing acknowledge value (Note: writing a '1' to the ACK bit generates an ACK; writing a '0' generates a NACK). Software should write a '0' to the ACK bit after the last byte is received, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. Note that the interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 13.6 shows a typical Master Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 13.6. Typical Master Receiver Sequence

124

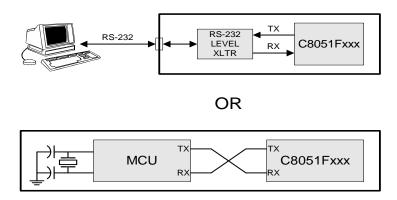

## 14.2. Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 14.3. UART Interconnect Diagram

### 14.2.1. 8-Bit UART

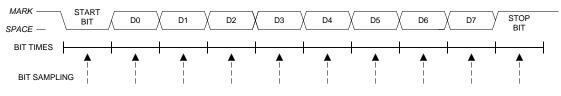

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX pin and received at the RX pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 14.4. 8-Bit UART Timing Diagram

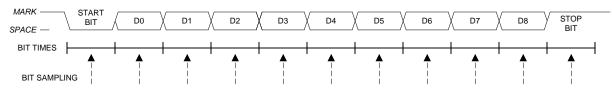

### 14.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to '1'. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to '1'.

Figure 14.5. 9-Bit UART Timing Diagram

# C8051F300/1/2/3/4/5

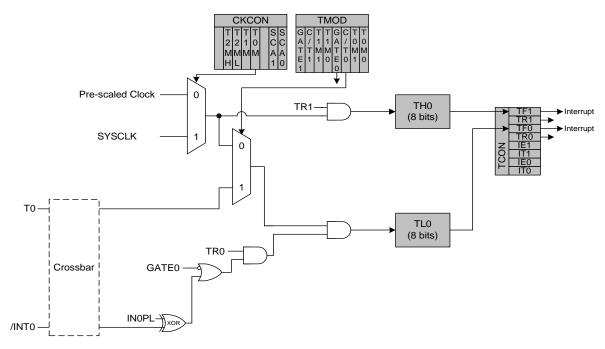

### 15.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 15.3. T0 Mode 3 Block Diagram

# 16. Programmable Counter Array

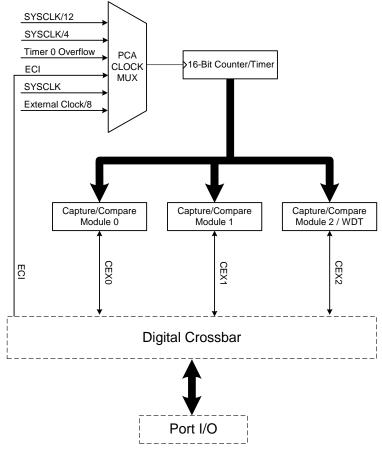

The Programmable Counter Array (PCA0) provides enhanced timer functionality while requiring less CPU intervention than the standard 8051 counter/timers. The PCA consists of a dedicated 16-bit counter/timer and three 16-bit capture/compare modules. Each capture/compare module has its own associated I/O line (CEXn) which is routed through the Crossbar to Port I/O when enabled (See Section "12.1. Priority Crossbar Decoder" on page 104 for details on configuring the Crossbar). The counter/timer is driven by a programmable timebase that can select between six sources: system clock, system clock divided by four, system clock divided by twelve, the external oscillator clock source divided by 8, Timer 0 overflow, or an external clock signal on the ECI input pin. Each capture/compare module may be configured to operate independently in one of six modes: Edge-Triggered Capture, Software Timer, High-Speed Output, Frequency Output, 8-Bit PWM, or 16-Bit PWM (each mode is described in Section "16.2. Capture/Compare Modules" on page 157). The external oscillator clock option is ideal for real-time clock (RTC) functionality, allowing the PCA to be clocked by a precision external oscillator while the internal oscillator drives the system clock. The PCA is configured and controlled through the system controller's Special Function Registers. The basic PCA block diagram is shown in Figure 16.1.

**Important Note:** The PCA Module 2 may be used as a watchdog timer (WDT), and is enabled in this mode following a system reset. Access to certain PCA registers is restricted while WDT mode is enabled. See **Section 16.3** for details.

Figure 16.1. PCA Block Diagram

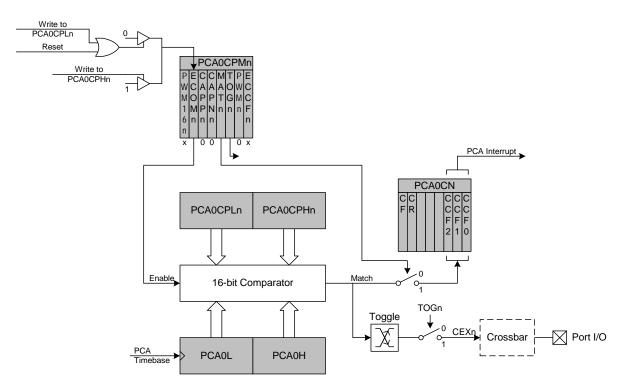

### 16.2.3. High Speed Output Mode

In High Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn) Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 16.6. PCA High Speed Output Mode Diagram