Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                  |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 14-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f301-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

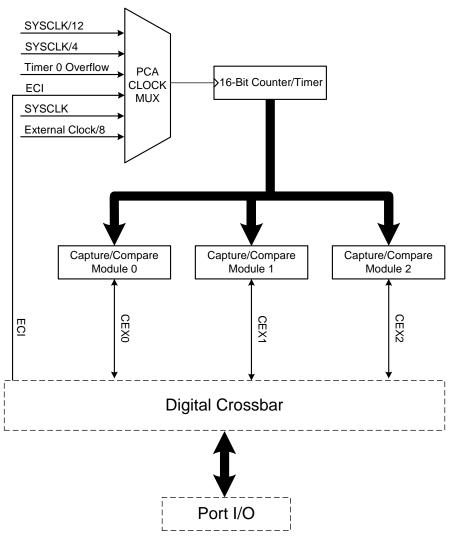

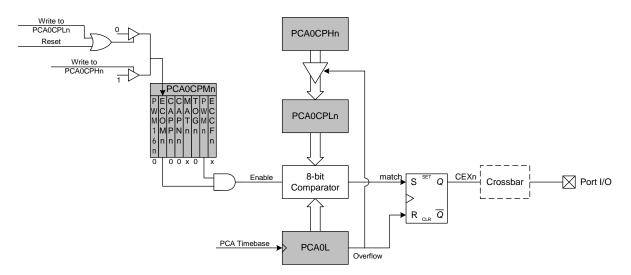

#### **1.6.** Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the three 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or the external oscillator clock source divided by 8. The external clock source selection is useful for real-time clock functionality, where the PCA is clocked by an external source while the internal oscillator drives the system clock.

Each capture/compare module can be configured to operate in one of six modes: Edge-Triggered Capture, Software Timer, High Speed Output, 8- or 16-bit Pulse Width Modulator, or Frequency Output. Additionally, Capture/Compare Module 2 offers watchdog timer (WDT) capabilities. Following a system reset, Module 2 is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input may be routed to Port I/O via the Digital Crossbar.

Figure 1.9. PCA Block Diagram

## 1.7. 8-Bit Analog to Digital Converter (C8051F300/2 Only)

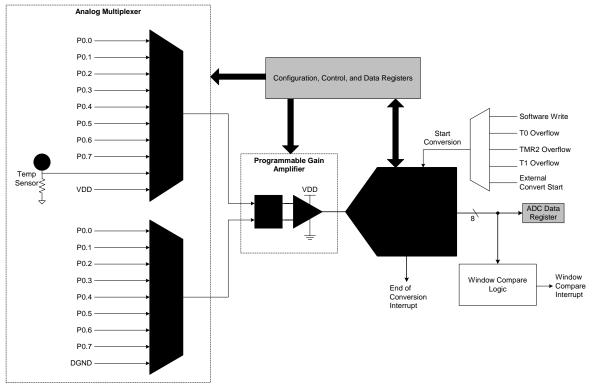

The C8051F300/2 includes an on-chip 8-bit SAR ADC with a 10-channel differential input multiplexer and programmable gain amplifier. With a maximum throughput of 500 ksps, the ADC offers true 8-bit accuracy with an INL of  $\pm$ 1LSB. The ADC system includes a configurable analog multiplexer that selects both positive and negative ADC inputs. Each Port pin is available as an ADC input; additionally, the on-chip Temperature Sensor output and the power supply voltage (V<sub>DD</sub>) are available as ADC inputs. User firmware may shut down the ADC to save power.

The integrated programmable gain amplifier (PGA) amplifies the ADC input by 0.5, 1, 2, or 4 as defined by user software. The gain stage is especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset.

Conversions can be started in five ways: a software command, an overflow of Timer 0, 1, or 2, or an external convert start signal. This flexibility allows the start of conversion to be triggered by software events, a periodic signal (timer overflows), or external HW signals. Conversion completions are indicated by a status bit and an interrupt (if enabled). The resulting 8-bit data word is latched into an SFR upon completion of a conversion.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is either within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within/outside the specified range.

# C8051F300/1/2/3/4/5

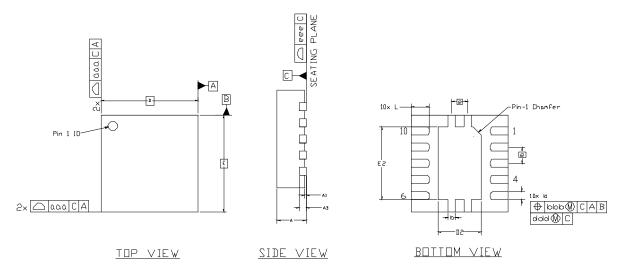

Figure 4.2. QFN-11 Package Drawing

| Dimension | Min  | Nom       | Мах  | Dimension | Min       | Nom  |  |

|-----------|------|-----------|------|-----------|-----------|------|--|

| А         | 0.80 | 0.90      | 1.00 | E         | 3.00 BSC. |      |  |

| A1        | 0.03 | 0.07      | 0.11 | E2        | 2.20      | 2.25 |  |

| A3        |      | 0.25 REF  |      | L         | .45       | .55  |  |

| b         | 0.18 | 0.25      | 0.30 | aaa       |           |      |  |

| D         |      | 3.00 BSC. |      | bbb       |           |      |  |

| D2        | 1.30 | 1.35      | 1.40 | ddd       |           |      |  |

| е         |      | 0.50 BSC. |      | eee       |           |      |  |

#### Table 4.2. QFN-11 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

**3.** This drawing conforms to JEDEC outline MO-243, variation VEED except for custom features D2, E2, and L which are toleranced per supplier designation.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

# 5. ADC0 (8-Bit ADC, C8051F300/2)

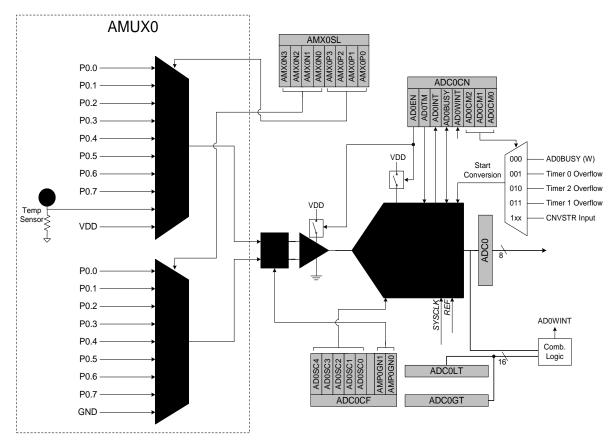

The ADC0 subsystem for the C8051F300/2 consists of two analog multiplexers (referred to collectively as AMUX0) with 11 total input selections, a differential programmable gain amplifier (PGA), and a 500 ksps, 8-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector (see block diagram in Figure 5.1). The AMUX0, PGA, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure any Port pin, the Temperature Sensor output, or  $V_{DD}$  with respect to any Port pin or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 5.1. ADC0 Functional Block Diagram

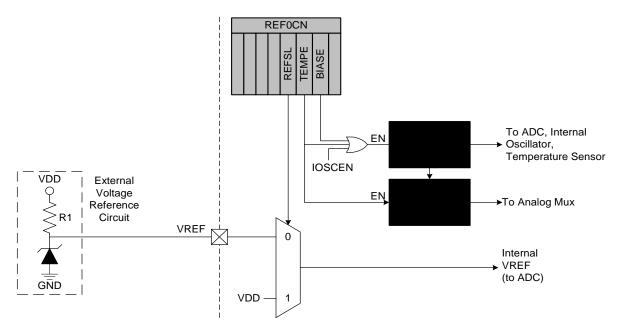

# 6. Voltage Reference (C8051F300/2)

The voltage reference MUX on C8051F300/2 devices is configurable to use an externally connected voltage reference or the power supply voltage,  $V_{DD}$  (see Figure 6.1). The REFSL bit in the Reference Control register (REF0CN) selects the reference source. For an external source, REFSL should be set to '0'; For  $V_{DD}$  as the reference source, REFSL should be set to '1'.

The BIASE bit enables the internal voltage bias generator, which is used by the ADC, Temperature Sensor, and Internal Oscillator. This bit is forced to logic 1 when any of the aforementioned peripherals is enabled. The bias generator may be enabled manually by writing a '1' to the BIASE bit in register REF0CN; see SFR Definition 6.1 for REF0CN register details. The electrical specifications for the voltage reference circuit are given in Table 6.1.

**Important Note About the VREF Input:** Port pin P0.0 is used as the external VREF input. When using an external voltage reference, P0.0 should be configured as analog input and skipped by the Digital Crossbar. To configure P0.0 as analog input, set to '1' Bit0 in register P0MDIN. To configure the Crossbar to skip P0.0, set to '1' Bit0 in register XBR0. Refer to **Section "12. Port Input/Output" on page 103** for complete Port I/O configuration details. The external reference voltage must be within the range  $0 \le VREF \le V_{DD}$ .

On C8051F300/2 devices, the temperature sensor connects to the highest order input of the ADC0 positive input multiplexer (see **Section "5.1. Analog Multiplexer and PGA" on page 36** for details). The TEMPE bit in register REF0CN enables/disables the temperature sensor. While disabled, the temperature sensor defaults to a high impedance state and any ADC0 measurements performed on the sensor result in meaningless data.

Figure 6.1. Voltage Reference Functional Block Diagram

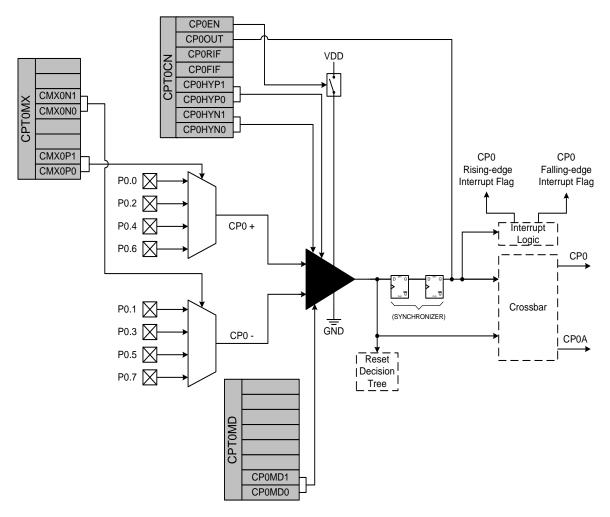

# 7. Comparator0

C8051F300/1/2/3/4/5 devices include an on-chip programmable voltage comparator, which is shown in Figure 7.1. Comparator0 offers programmable response time and hysteresis, an analog input multiplexer, and two outputs that are optionally available at the Port pins: a synchronous "latched" output (CP0), or an asynchronous "raw" output (CP0A). The asynchronous CP0A signal is available even when the system clock is not active. This allows Comparator0 to operate and generate an output with the device in STOP mode. When assigned to a Port pin, the Comparator0 output may be configured as open drain or push-pull (see Section "12.2. Port I/O Initialization" on page 106). Comparator0 may also be used as a reset source (see Section "9.5. Comparator0 Reset" on page 85).

The inputs for Comparator0 are selected in the CPT0MX register (SFR Definition 7.2). The CMX0P1-CMX-0P0 bits select the Comparator0 positive input; the CMX0N1-CMX0N0 bits select the Comparator0 negative input.

**Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see **Section "12.3. General Purpose Port I/O" on page 108**).

### SFR Definition 8.9. EIE1: Extended Interrupt Enable 1

| R/W      | R/W                           | R/W                                                     | R/W   | R/W         | R/W          | R/W           | R/W   | Reset Value |  |

|----------|-------------------------------|---------------------------------------------------------|-------|-------------|--------------|---------------|-------|-------------|--|

|          | _                             | ECP0R                                                   | ECP0F | EPCA0       | EADC0C       | EWADC0        | ESMB0 | 00000000    |  |

| Bit7     | Bit6                          | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address:<br>0xE6 |       |             |              |               |       |             |  |

| Bits7–6: | UNUSED. F                     |                                                         |       |             |              |               |       |             |  |

| Bit5:    | ECP0R: En                     |                                                         | •     | , 0         | • •          |               |       |             |  |

|          | This bit sets<br>0: Disable C |                                                         | •     | •           | age interrup | ot.           |       |             |  |

|          | 1: Enable in                  | •                                                       | •     | •           |              | a             |       |             |  |

| Bit4:    | ECP0F: Ena                    |                                                         | •     |             |              | •             |       |             |  |

|          | This bit sets                 |                                                         | · ·   | , 0         | •            |               |       |             |  |

|          | 0: Disable C                  | •                                                       | •     |             |              |               |       |             |  |

| Dite     | 1: Enable in                  |                                                         | •     |             |              | •             |       |             |  |

| Bit3:    | EPCA0: Ena<br>This bit sets   | •                                                       |       |             | , , ,        | terrupt.      |       |             |  |

|          | 0: Disable a                  |                                                         | •     |             | 515.         |               |       |             |  |

|          | 1: Enable in                  |                                                         | •     | ated by PC  | A0.          |               |       |             |  |

| Bit2:    | EADC0C: E                     |                                                         |       |             | •            |               |       |             |  |

|          | This bit sets                 |                                                         | •     |             |              | lete interrup | ot.   |             |  |

|          | 0: Disable A                  |                                                         |       | •           | •            | ~             |       |             |  |

| Bit1:    | 1: Enable in<br>EWADC0: E     |                                                         | •     | •           |              | ig.           |       |             |  |

| Ditt.    | This bit sets                 |                                                         |       |             |              | nterrupt.     |       |             |  |

|          | 0: Disable A                  |                                                         | •     |             |              | •             |       |             |  |

|          | 1: Enable in                  |                                                         | •     | ated by AD  | C0 Window    | Compare f     | lag.  |             |  |

| Bit0:    | ESMB0: En                     |                                                         |       | <b>ID</b>   |              |               |       |             |  |

|          | This bit sets<br>0: Disable a |                                                         | •     | IBUS INTERN | upt.         |               |       |             |  |

|          | 1: Enable in                  |                                                         |       | ated by the | SI flag.     |               |       |             |  |

|          |                               |                                                         |       |             |              |               |       |             |  |

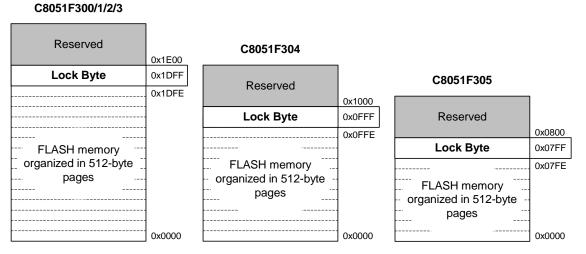

#### 9.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to '1' and a MOVX operation is attempted above the user code space address limit.

- A Flash read is attempted above user code space. This occurs when a MOVC operation is attempted above the user code space address limit.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the user code space address limit.

| Device          | User Code Space Address Limit |

|-----------------|-------------------------------|

| C8051F300/1/2/3 | 0x1DFF                        |

| C8051F304       | 0x0FFF                        |

| C8051F305       | 0x07FF                        |

Table 9.1. User Code Space Address Limits

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 9.8. Software Reset

Software may force a reset by writing a '1' to the SWRSF bit (RSTSRC.4). The SWRSF bit will read '1' following a software forced reset. The state of the RST pin is unaffected by this reset.

#### Table 9.2. Reset Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter                                          | Conditions                                                                            | Min                         | Тур  | Max                 | Units |

|----------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|------|---------------------|-------|

| RST Output Low Voltage                             | $I_{OL} = 8.5 \text{ mA}, V_{DD} = 2.7 \text{ V to}$<br>3.6 V                         | —                           | _    | 0.6                 | V     |

| RST Input High Voltage                             |                                                                                       | $0.7 	ext{ x V}_{	ext{DD}}$ |      | _                   | V     |

| RST Input Low Voltage                              |                                                                                       | _                           |      | $0.3 \times V_{DD}$ |       |

| RST Input Leakage Current                          | RST = 0.0 V                                                                           | —                           | 25   | 40                  | μA    |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )           |                                                                                       | 2.40                        | 2.55 | 2.70                | V     |

| Missing Clock Detector Timeout                     | Time from last system clock ris-<br>ing edge to reset initiation                      | 100                         | 220  | 500                 | μs    |

| Reset Time Delay                                   | Delay between release of any<br>reset source and code execution<br>at location 0x0000 | 5.0                         |      | _                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset |                                                                                       | 15                          | _    | —                   | μs    |

| V <sub>DD</sub> Ramp Time                          | $V_{DD} = 0$ to $V_{RST}$                                                             |                             |      | 1                   | ms    |

| Bits | Description                                                                                                                                               |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4  | Write Lock: Clearing any of these bits to logic 0 prevents all Flash memory from being written or page-erased across the C2 interface                     |

| 3–0  | <b>Read/Write Lock:</b> Clearing any of these bits to logic 0 prevents all Flash memory from being read, written, or page-erased across the C2 interface. |

#### Table 10.2. Security Byte Decoding

The lock bits can always be read and cleared to logic 0 regardless of the security settings.

Important note: The only means of removing a lock (write or read/write) once set is to erase the entire program memory space via a C2 Device Erase command.

#### Figure 10.1. Flash Program Memory Map

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages.

#### Accessing Flash from the C2 debug interface:

- 1. Any unlocked page may be read, written, or erased.

- 2. Locked pages cannot be read, written, or erased.

- 3. The page containing the Lock Byte may be read, written, or erased if it is unlocked.

- 4. Reading the contents of the Lock Byte is always permitted only if no pages are locked.

- 5. Locking additional pages (changing '1's to '0's in the Lock Byte) is not permitted.

- Unlocking Flash pages (changing '0's to '1's in the Lock Byte) requires the C2 Device Erase command, which erases all Flash pages including the page containing the Lock Byte and the Lock Byte itself.

- 7. The Reserved Area cannot be read, written, or erased.

viced in priority order after the Flash operation has been completed and interrupts have been re-enabled by software.

- 10. Make certain that the Flash write and erase pointer variables are not located in XRAM. See your compiler documentation for instructions regarding how to explicitly locate variables in different memory areas.

- 11. Add address bounds checking to the routines that write or erase Flash memory to ensure that a routine called with an illegal address does not result in modification of the Flash.

#### 10.4.3. System Clock

- 12. If operating from an external crystal, be advised that crystal performance is susceptible to electrical interference and is sensitive to layout and to changes in temperature. If the system is operating in an electrically noisy environment, use the internal oscillator or use an external CMOS clock.

- 13. If operating from the external oscillator, switch to the internal oscillator during Flash write or erase operations. The external oscillator can continue to run, and the CPU can switch back to the external oscillator after the Flash operation has completed.

Additional Flash recommendations and example code can be found in *AN201, "Writing to Flash from Firm-ware"*, available from the Silicon Laboratories web site.

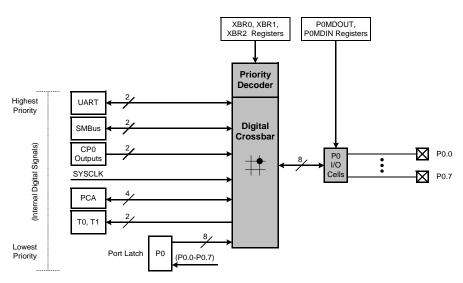

# 12. Port Input/Output

Digital and analog resources are available through a byte-wide digital I/O Port, Port0. Each of the Port pins can be defined as general-purpose I/O (GPIO), analog input, or assigned to one of the internal digital resources as shown in Figure 12.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

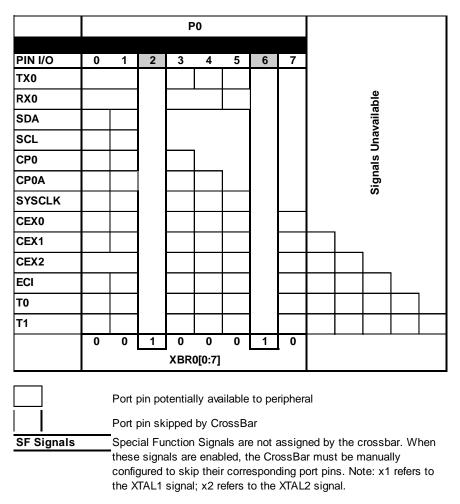

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 12.3 and Figure 12.4). The registers XBR0, XBR1, and XBR2, defined in SFR Definition 12.1, SFR Definition 12.2, and SFR Definition 12.3 are used to select internal digital functions.

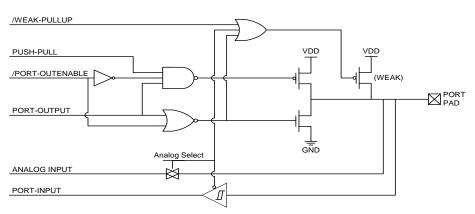

All Port I/Os are 5 V tolerant (refer to Figure 12.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port0 Output Mode register (P0MDOUT). Complete Electrical Specifications for Port I/O are given in Table 12.1 on page 110.

Figure 12.1. Port I/O Functional Block Diagram

Figure 12.2. Port I/O Cell Block Diagram

### Figure 12.4. Crossbar Priority Decoder with XBR0 = 0x44

Registers XBR1 and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL). Either or both of the UART signals may be selected by the Crossbar. UART0 pin assignments are fixed for bootloading purposes: when UART TX0 is selected, it is always assigned to P0.4; when UART RX0 is selected, it is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned. For example, if assigned functions that take the first 3 Port I/O (P0.[2:0]), 5 Port I/O are left for analog or GPIO use.

### SFR Definition 12.4. P0: Port0 Register

| R/W<br>P0.7 | R/W<br>P0.6                                  | R/W<br>P0.5                                                             | R/W<br>P0.4                                   | R/W<br>P0.3            | R/W<br>P0.2 | R/W<br>P0.1  | R/W<br>P0.0         | Reset Value             |

|-------------|----------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------|------------------------|-------------|--------------|---------------------|-------------------------|

| Bit7        | Bit6                                         | Bit5                                                                    | Bit4                                          | Bit3                   | Bit2        | Bit1<br>(bit | Bit0<br>addressable | SFR Address:<br>e) 0x80 |

| Bits7–0:    | Write - Outp<br>0: Logic Low<br>1: Logic Hig | v Output.<br>h Output (o<br>lys reads '1<br>nfigured as<br>s logic low. | pen-drain if<br>' if selected<br>digital inpu | correspon<br>as analog | ding P0MD   | OUT.n bit =  | 0)                  | ly reads Port           |

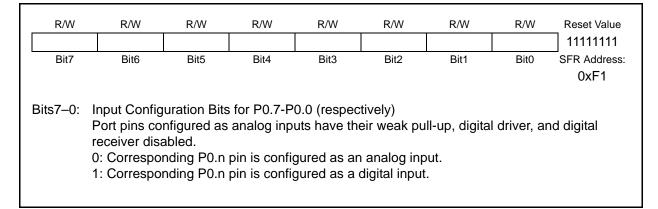

#### SFR Definition 12.5. P0MDIN: Port0 Input Mode

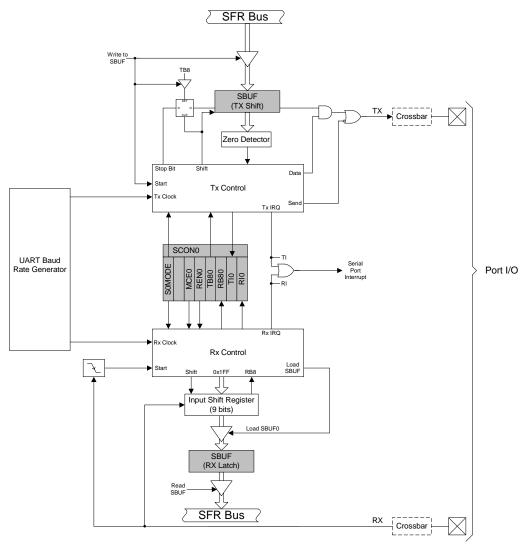

## 14. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in **Section "14.1. Enhanced Baud Rate Generation" on page 132**). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UARTO has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Reading SBUF0 accesses the buffered Receive register; writing SBUF0 accesses the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

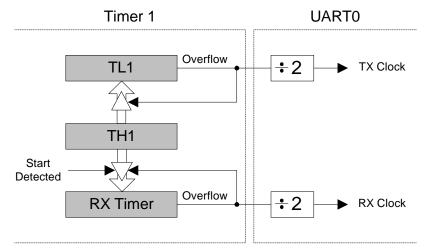

#### 14.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 14.2), which is not user accessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see **Section "15.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 145**). The Timer 1 reload value should be set so that over-flows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of five sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, or the external oscillator clock / 8. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 14.1.

$$UartBaudRate = \frac{T1_{CLK}}{(256 - T1H)} \times \frac{1}{2}$$

#### Equation 14.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in **Section "15.2. Timer 2" on page 151**. A quick reference for typical baud rates and system clock frequencies is given in Tables 14.1 through 14.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1 (see **Section "15.1. Timer 0 and Timer 1" on page 143** for more details).

# C8051F300/1/2/3/4/5

#### 16.2.5. 8-Bit Pulse Width Modulator Mode

Each module can be used independently to generate a pulse width modulated (PWM) output on its associated CEXn pin. The frequency of the output is dependent on the timebase for the PCA counter/timer. The duty cycle of the PWM output signal is varied using the module's PCA0CPLn capture/compare register. When the value in the low byte of the PCA counter/timer (PCA0L) is equal to the value in PCA0CPLn, the output on the CEXn pin will be set to '1'. When the count value in PCA0L overflows, the CEXn output will be set to '0' (see Figure 16.8). Also, when the counter/timer low byte (PCA0L) overflows from 0xFF to 0x00, PCA0CPLn is reloaded automatically with the value stored in the module's capture/compare high byte (PCA0CPHn) without software intervention. Setting the ECOMn and PWMn bits in the PCA0CPMn register enables 8-bit Pulse Width Modulator mode. The duty cycle for 8-bit PWM Mode is given by Equation 16.2.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

$$DutyCycle = \frac{(256 - PCA0CPHn)}{256}$$

#### Equation 16.2. 8-Bit PWM Duty Cycle

Using Equation 16.2, the largest duty cycle is 100% (PCA0CPHn = 0), and the smallest duty cycle is 0.39% (PCA0CPHn = 0xFF). A 0% duty cycle may be generated by clearing the ECOMn bit to '0'.

Figure 16.8. PCA 8-Bit PWM Mode Diagram

#### 16.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

| SFR Definition 16.1. PC | A0CN: PCA Control |

|-------------------------|-------------------|

|-------------------------|-------------------|

| R/W               | R/W                                                                                       | R/W                                                                                                  | R/W                                                                                           | R/W                                                   | R/W                                         | R/W                        | R/W                      | Reset Value                                |

|-------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|----------------------------|--------------------------|--------------------------------------------|

| CF                | CR                                                                                        | _                                                                                                    | _                                                                                             | —                                                     | CCF2                                        | CCF1                       | CCF0                     | 00000000                                   |

| Bit7              | Bit6                                                                                      | Bit5                                                                                                 | Bit4                                                                                          | Bit3                                                  | Bit2                                        | Bit1                       | Bit0                     | SFR Address:                               |

|                   |                                                                                           |                                                                                                      |                                                                                               |                                                       |                                             | (bit                       | addressable              | e) 0xD8                                    |

| Bit7:<br>Bit6:    | Counter/Tim<br>to the PCA i<br>must be clea<br>CR: PCA Co<br>This bit enal<br>0: PCA Cou  | vare when<br>er Overflow<br>nterrupt se<br>ared by soft<br>punter/Time<br>ples/disable<br>nter/Timer | the PCA Co<br>v (CF) inter<br>rvice routin<br>ware.<br>er Run Cont<br>es the PCA<br>disabled. | ounter/Time<br>rupt is enat<br>e. This bit is<br>rol. | oled, setting<br>s not autom                | this bit cau               | uses the C               | 00. When the<br>PU to vector<br>rdware and |

| Bits5–3:<br>Bit2: | 1: PCA Cour<br>UNUSED. R<br>CCF2: PCA<br>This bit is se<br>enabled, set<br>bit is not aut | ead = 000<br>Module 2 (<br>et by hardw<br>ting this bit                                              | o, Write = d<br>Capture/Co<br>are when a<br>causes the                                        | mpare Flag<br>match or c<br>CPU to ve                 | ector to the                                | PCA interru                | upt service              | nterrupt is<br>routine. This               |

| Bit1:             | CCF1: PCA<br>This bit is se<br>enabled, set<br>bit is not aut                             | Module 1 (<br>et by hardw<br>ting this bit<br>omatically                                             | Capture/Co<br>are when a<br>causes the<br>cleared by                                          | mpare Flag<br>match or c<br>CPU to ve<br>hardware a   | apture occu<br>ector to the l<br>nd must be | urs. When t<br>PCA interru | he CCF1 i<br>ıpt service | nterrupt is<br>routine. This               |

| Bit0:             | CCF0: PCA<br>This bit is se<br>enabled, set<br>bit is not aut                             | et by hardw<br>ting this bit                                                                         | are when a causes the                                                                         | match or c<br>CPU to ve                               | ector to the                                | PCA interru                | upt service              | nterrupt is<br>routine. This               |

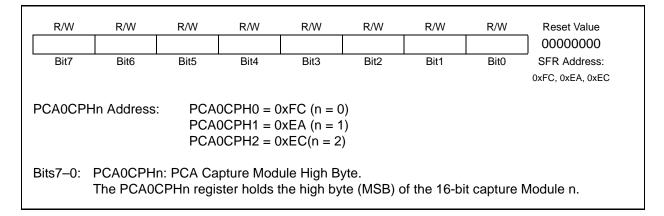

### SFR Definition 16.6. PCA0CPLn: PCA Capture Module Low Byte

| R/W                                                                                                                               | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000          |  |

|-----------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|----------------------------------|--|

| Bit7                                                                                                                              | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xFB, 0xE9, 0xEB |  |

| PCA0CPLn Address:PCA0CPL0 = $0xFB (n = 0)$<br>PCA0CPL1 = $0xE9 (n = 1)$<br>PCA0CPL2 = $0xEB (n = 2)$                              |      |      |      |      |      |      |      |                                  |  |

| Bits7–0: PCA0CPLn: PCA Capture Module Low Byte.<br>The PCA0CPLn register holds the low byte (LSB) of the 16-bit capture Module n. |      |      |      |      |      |      |      |                                  |  |

### SFR Definition 16.7. PCA0CPHn: PCA Capture Module High Byte

# 17. C2 Interface

C8051F300/1/2/3/4/5 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D) and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

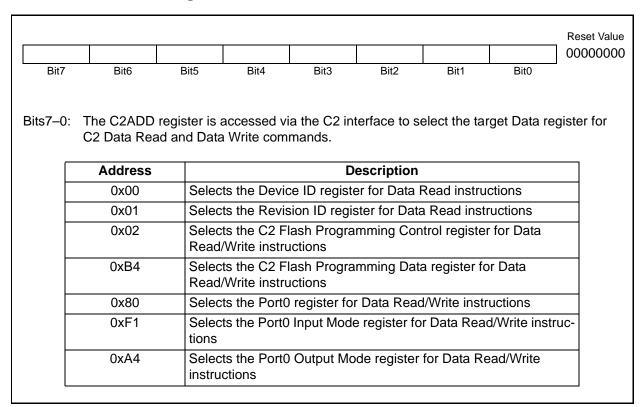

#### 17.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

### C2 Register Definition 17.1. C2ADD: C2 Address

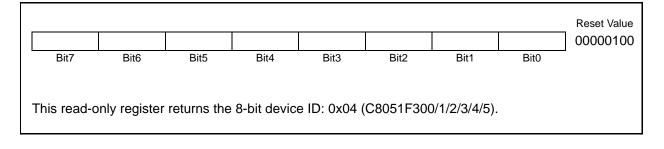

## C2 Register Definition 17.2. DEVICEID: C2 Device ID

# C8051F300/1/2/3/4/5

# NOTES: