Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2012.10                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Last Time Buy                                                   |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I²C), UART/USART                                  |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 14-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f301-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F300/1/2/3/4/5

NOTES:

# List of Registers

| SFR Definition 5.1. AMX0SL: AMUX0 Channel Select (C8051F300/2)        | 42  |

|-----------------------------------------------------------------------|-----|

| SFR Definition 5.2. ADC0CF: ADC0 Configuration (C8051F300/2)          | 43  |

| SFR Definition 5.3. ADC0: ADC0 Data Word (C8051F300/2)                | 43  |

| SFR Definition 5.4. ADC0CN: ADC0 Control (C8051F300/2)                | 44  |

| SFR Definition 5.5. ADC0GT: ADC0 Greater-Than Data Byte (C8051F300/2) | 46  |

| SFR Definition 5.6. ADC0LT: ADC0 Less-Than Data Byte (C8051F300/2)    | 46  |

| SFR Definition 6.1. REF0CN: Reference Control Register                | 50  |

| SFR Definition 7.1. CPT0CN: Comparator0 Control                       |     |

| SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection                 | 54  |

| SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection                | 54  |

| SFR Definition 8.1. DPL: Data Pointer Low Byte                        |     |

| SFR Definition 8.2. DPH: Data Pointer High Byte                       | 69  |

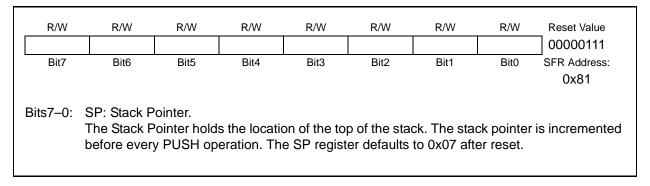

| SFR Definition 8.3. SP: Stack Pointer                                 | 69  |

| SFR Definition 8.4. PSW: Program Status Word                          | 70  |

| SFR Definition 8.5. ACC: Accumulator                                  | 71  |

| SFR Definition 8.6. B: B Register                                     | 71  |

| SFR Definition 8.7. IE: Interrupt Enable                              | 75  |

| SFR Definition 8.8. IP: Interrupt Priority                            | 76  |

| SFR Definition 8.9. EIE1: Extended Interrupt Enable 1                 | 77  |

| SFR Definition 8.10. EIP1: Extended Interrupt Priority 1              | 78  |

| SFR Definition 8.11. IT01CF: INT0/INT1 Configuration                  |     |

| SFR Definition 8.12. PCON: Power Control                              |     |

| SFR Definition 9.1. RSTSRC: Reset Source                              | 87  |

| SFR Definition 10.1. PSCTL: Program Store R/W Control                 | 92  |

| SFR Definition 10.2. FLKEY: Flash Lock and Key                        |     |

| SFR Definition 10.3. FLSCL: Flash Scale                               |     |

| SFR Definition 11.1. OSCICL: Internal Oscillator Calibration          | 98  |

| SFR Definition 11.2. OSCICN: Internal Oscillator Control              |     |

| SFR Definition 11.3. OSCXCN: External Oscillator Control              | 100 |

| SFR Definition 12.1. XBR0: Port I/O Crossbar Register 0               |     |

| SFR Definition 12.2. XBR1: Port I/O Crossbar Register 1               |     |

| SFR Definition 12.3. XBR2: Port I/O Crossbar Register 2               | 108 |

| SFR Definition 12.4. P0: Port0 Register                               |     |

| SFR Definition 12.5. P0MDIN: Port0 Input Mode                         |     |

| SFR Definition 12.6. P0MDOUT: Port0 Output Mode                       |     |

| SFR Definition 13.1. SMB0CF: SMBus Clock/Configuration                | 118 |

| SFR Definition 13.2. SMB0CN: SMBus Control                            |     |

| SFR Definition 13.3. SMB0DAT: SMBus Data                              |     |

| SFR Definition 14.1. SCON0: Serial Port 0 Control                     |     |

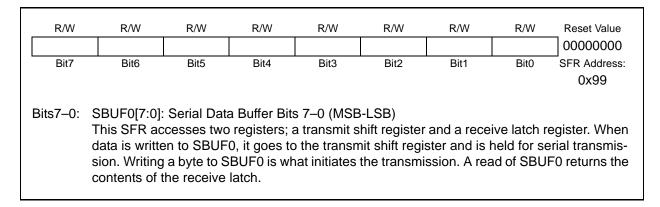

| SFR Definition 14.2. SBUF0: Serial (UART0) Port Data Buffer           |     |

| SFR Definition 15.1. TCON: Timer Control                              |     |

| SFR Definition 15.2. TMOD: Timer Mode                                 |     |

| SFR Definition 15.3. CKCON: Clock Control                             | 149 |

# C8051F300/1/2/3/4/5

| Ordering Part Number | MIPS (Peak) | Flash Memory | RAM | Calibrated Internal Oscillator | SMBus/I <sup>2</sup> C | UART         | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | 8-bit 500ksps ADC | Temperature Sensor | Analog Comparators | Lead-free (RoHS compliant) | Package |

|----------------------|-------------|--------------|-----|--------------------------------|------------------------|--------------|-----------------|----------------------------|-------------------|-------------------|--------------------|--------------------|----------------------------|---------|

| C8051F300-GM         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | QFN-11  |

| C8051F300-GS         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | ~                 | $\checkmark$       | 1                  | ~                          | SOIC-14 |

| C8051F301-GM         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | $\checkmark$               | 8                 | —                 |                    | 1                  | $\checkmark$               | QFN-11  |

| C8051F301-GS         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | SOIC-14 |

| C8051F302-GM         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | QFN-11  |

| C8051F302-GS         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | SOIC-14 |

| C8051F303-GM         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | QFN-11  |

| C8051F303-GS         | 25          | 8 k          | 256 |                                | ~                      | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | SOIC-14 |

| C8051F304-GM         | 25          | 4 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | —                 |                    | 1                  | ~                          | QFN-11  |

| C8051F304-GS         | 25          | 4 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | —                 | _                  | 1                  | ~                          | SOIC-14 |

| C8051F305-GM         | 25          | 2 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | QFN-11  |

| C8051F305-GS         | 25          | 2 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | $\checkmark$               | 8                 |                   |                    | 1                  | $\checkmark$               | SOIC-14 |

Table 1.1. Product Selection Guide

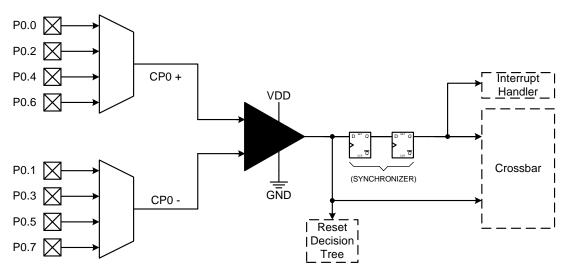

### 1.8. Comparator

C8051F300/1/2/3/4/5 devices include an on-chip voltage comparator that is enabled/disabled and configured via user software. All Port I/O pins may be configurated as comparator inputs. Two comparator outputs may be routed to a Port pin if desired: a latched output and/or an unlatched (asynchronous) output. Comparator response time is programmable, allowing the user to select between high-speed and lowpower modes. Positive and negative hysteresis is also configurable.

Comparator interrupts may be generated on rising, falling, or both edges. When in IDLE mode, these interrupts may be used as a "wake-up" source. The comparator may also be configured as a reset source.

Figure 1.11. Comparator Block Diagram

# C8051F300/1/2/3/4/5

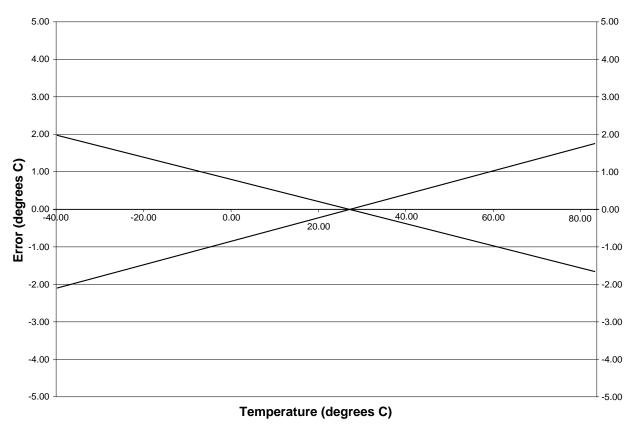

Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V)

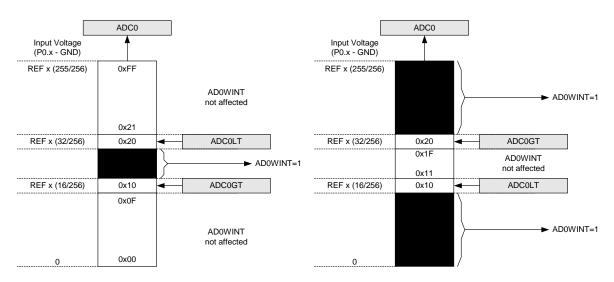

## 5.4. Programmable Window Detector

The ADC Programmable Window Detector continuously compares the ADC0 output to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GT) and Less-Than (ADC0LT) registers hold the comparison values. Example comparisons for Single-ended and Differential modes are shown in Figure 5.6 and Figure 5.7, respectively. Notice that the window detector flag can be programmed to indicate when measured data is inside or out-side of the user-programmed limits depending on the contents of the ADC0LT and ADC0GT registers.

#### 5.4.1. Window Detector In Single-Ended Mode

Figure 5.6 shows two example window comparisons for Single-ended mode, with ADC0LT = 0x20 and ADC0GT = 0x10. Notice that in Single-ended mode, the codes vary from 0 to VREF x (255/256) and are represented as 8-bit unsigned integers. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0) is within the range defined by ADC0GT and ADC0LT (if 0x10 < ADC0 < 0x20). In the right example, and AD0WINT interrupt will be generated if ADC0 is outside of the range defined by ADC0GT and ADC0LT (if ADC0 < 0x10 or ADC0 > 0x20).

Figure 5.6. ADC Window Compare Examples, Single-Ended Mode

| R/W                  | R/W                   | R/W                      | R/W                                             | R/W                      | R/W  | R/W    | R/W        | Reset Value          |

|----------------------|-----------------------|--------------------------|-------------------------------------------------|--------------------------|------|--------|------------|----------------------|

| —                    | —                     | CMX0N1                   | CMX0N0                                          | _                        | —    | CMX0P1 | CMX0P0     | 00000000             |

| Bit7                 | Bit6                  | Bit5                     | Bit4                                            | Bit3                     | Bit2 | Bit1   | Bit0       | SFR Address:<br>0x9F |

| Bits7–6:<br>Bits6–4: | CMX0N1-               | CMX0N0: C                | o, Write = doi<br>Comparator0<br>ch Port pin is | Negative                 |      |        | ive input. |                      |

|                      | CMX0N1                | CMX0N0                   | Negative I                                      | nput                     |      |        |            |                      |

|                      | 0                     | 0                        | P0.1                                            |                          |      |        |            |                      |

|                      | 0                     | 1                        | P0.3                                            |                          |      |        |            |                      |

|                      | 1                     | 0                        | P0.5                                            |                          |      |        |            |                      |

|                      | 1                     | 1                        | P0.7                                            |                          |      |        |            |                      |

| Bits3–2:<br>Bits1–0: | CMX0P1–<br>These bits | CMX0P0: C<br>select whic | o, Write = doi<br>Comparator0<br>ch Port pin is | Positive II<br>used as t |      |        | ve input.  |                      |

|                      | CMX0P1                | CMX0P0                   | Positive Ir                                     | nput                     |      |        |            |                      |

|                      | 0                     | 0                        | P0.0                                            |                          |      |        |            |                      |

|                      | 0                     |                          | DO 0                                            |                          |      |        |            |                      |

|                      | 0                     | 1                        | P0.2                                            |                          |      |        |            |                      |

|                      |                       | 1<br>0                   | P0.2<br>P0.4                                    |                          |      |        |            |                      |

# SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection

# SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection

| R/W      | R/W                   | R/W                     | R/W                     | R/W                 | R/W                   | R/W      | R/W    | Reset Value  |

|----------|-----------------------|-------------------------|-------------------------|---------------------|-----------------------|----------|--------|--------------|

| —        |                       | _                       | —                       | —                   | _                     | CP0MD1   | CP0MD0 | 00000010     |

| Bit7     | Bit6                  | Bit5                    | Bit4                    | Bit3                | Bit2                  | Bit1     | Bit0   | SFR Address: |

|          |                       |                         |                         |                     |                       |          |        | 0x9D         |

| Bits1–0: | CP0MD1-C              |                         |                         |                     |                       |          |        |              |

|          | These bits s          | select the re           | esponse time            | e for Compa         | arator0.<br>ponse Tim | ie (TYP) |        |              |

|          |                       |                         |                         | CP0 Res             |                       | . ,      |        |              |

|          | Mode                  | CP0MD1                  | CP0MD0                  | CP0 Res             | ponse Tim             | . ,      |        |              |

|          | Mode                  | <b>CP0MD1</b>           | CP0MD0                  | CP0 Res             | ponse Tim             | . ,      |        |              |

|          | <b>Mode</b><br>0<br>1 | <b>CP0MD1</b><br>0<br>0 | <b>CP0MD0</b><br>0<br>1 | CP0 Resp<br>Fastest | ponse Tim             | e Time   |        |              |

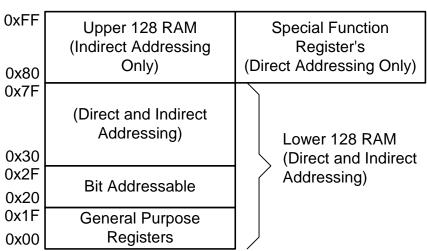

### 8.2.2. Data Memory

The CIP-51 includes 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory organization of the CIP-51.

# INTERNAL DATA ADDRESS SPACE

## Figure 8.3. Data Memory Map

#### 8.2.3. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 8.4). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

# SFR Definition 8.2. DPH: Data Pointer High Byte

| R/W     | R/W                                    | R/W            | R/W         | R/W         | R/W         | R/W         | R/W        | Reset Value   |

|---------|----------------------------------------|----------------|-------------|-------------|-------------|-------------|------------|---------------|

|         |                                        |                |             |             |             |             |            | 0000000       |

| Bit7    | Bit6                                   | Bit5           | Bit4        | Bit3        | Bit2        | Bit1        | Bit0       | SFR Address:  |

|         |                                        |                |             |             |             |             |            | 0x83          |

| Bits7–0 | : DPH: Data<br>The DPH re<br>addressed | egister is the | e high byte | of the 16-b | it DPTR. DI | PTR is used | d to acces | ss indirectly |

# SFR Definition 8.3. SP: Stack Pointer

| R/W          | R/W         | R/W         | R/W                 | R/W        | R/W           | R/W          | R              | Reset Value      |

|--------------|-------------|-------------|---------------------|------------|---------------|--------------|----------------|------------------|

| CY           | AC          | F0          | RS1                 | RS0        | OV            | F1           | PARITY         | 0000000          |

| Bit7         | Bit6        | Bit5        | Bit4                | Bit3       | Bit2          | Bit1         | Bit0           | SFR Address:     |

|              |             |             |                     |            |               | (bi          | t addressable) | 0xD0             |

|              |             |             |                     |            |               |              |                |                  |

| Bit7:        | CY: Carry   | •           |                     |            |               |              |                |                  |

|              |             |             | he last arithmet    |            |               |              |                | or a borrow      |

| <b>B</b> 146 |             |             | eared to logic 0 l  | by all oth | ner arithme   | tic operatio | ns.            |                  |

| Bit6:        | AC: Auxilia |             |                     |            |               |              |                |                  |

|              |             |             | he last arithmetic  |            |               |              |                |                  |

|              | tions.      | raction) th | e high order nib    |            |               |              |                | nmetic opera-    |

| Bit5:        | F0: User F  | lag 0       |                     |            |               |              |                |                  |

| Dito.        |             | 0           | able, general pu    | irpose fl  | ad for use i  | under softw  | are control    |                  |

| Bits4–3:     |             |             | Bank Select.        |            |               |              |                |                  |

|              |             |             | ich register ban    | k is used  | d during reg  | gister acces | sses.          |                  |

|              |             |             | C C                 |            |               |              |                |                  |

|              | RS1         | RS0         | Register Bank       | Ad         | dress         |              |                |                  |

|              | 0           | 0           | 0                   | 0x0        | 0–0x07        |              |                |                  |

|              | 0           | 1           | 1                   | 0x0        | 8–0x0F        |              |                |                  |

|              | 1           | 0           | 2                   | 0x1        | 0–0x17        |              |                |                  |

|              | 1           | 1           | 3                   | 0x1        | 8–0x1F        |              |                |                  |

| D:40         | O(k) O(k)   |             |                     |            |               |              |                |                  |

| Bit2:        | OV: Overf   | •           | der the followin    |            | etancoc:      |              |                |                  |

|              |             |             | or SUBB instruct    |            |               | change ove   | rflow          |                  |

|              |             |             | results in an ov    |            | •             | •            |                |                  |

|              |             |             | causes a divide-    |            |               |              |                |                  |

|              |             |             | d to 0 by the AD    |            |               | /IUL, and D  | IV instruction | ons in all other |

|              | cases.      |             | -                   |            | ,             | ·            |                |                  |

| Bit1:        | F1: User F  | •           |                     |            |               |              |                |                  |

|              |             |             | able, general pu    | irpose fl  | ag for use ι  | under softw  | are control    |                  |

| Bit0:        | PARITY: F   |             |                     |            |               |              |                |                  |

|              |             | -           | : 1 if the sum of t | he eight   | bits in the a | accumulato   | or is odd an   | d cleared if the |

|              | sum is eve  | en.         |                     |            |               |              |                |                  |

|              |             |             |                     |            |               |              |                |                  |

# SFR Definition 8.4. PSW: Program Status Word

### 10.1.3. Flash Write Procedure

Flash bytes are programmed by software with the following sequence:

- Step 1. Disable interrupts (recommended).

- Step 2. Erase the 512-byte Flash page containing the target location, as described in **Section 10.1.2**.

- Step 3. Set the PSWE bit in PSCTL.

- Step 4. Clear the PSEE bit in PSCTL.

- Step 5. Write the first key code to FLKEY: 0xA5.

- Step 6. Write the second key code to FLKEY: 0xF1.

- Step 7. Using the MOVX instruction, write a single data byte to the desired location within the 512byte sector.

Steps 5–7 must be repeated for each byte to be written. After Flash writes are complete, PSWE should be cleared so that MOVX instructions do not target program memory. Writing to and erasing the Reserved area of Flash should be avoided.

| Parameter                                             | Conditions          | Min   | Тур  | Max | Units       |

|-------------------------------------------------------|---------------------|-------|------|-----|-------------|

|                                                       | C8051F300/1/2/3     | 8192* |      |     | bytes       |

| Flash Size                                            | C8051F304           | 4096  |      |     | bytes       |

|                                                       | C8051F305           | 2048  |      |     | bytes       |

| Endurance                                             |                     | 20k   | 100k |     | Erase/Write |

| Erase Cycle Time                                      | 25 MHz System Clock | 10    | 15   | 20  | ms          |

| Write Cycle Time                                      | 25 MHz System Clock | 40    | 55   | 70  | μs          |

| SYSCLK Frequency (Flash writes from application code) |                     | 100   |      |     | kHz         |

Table 10.1. Flash Electrical Characteristics

\*Note: 512 bytes at location 0x1E00 to 0x1FFF are reserved.

#### 10.2. Non-Volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX instruction and read using the MOVC instruction.

### 10.3. Security Options

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the Flash memory from accidental modification by software. PSWE must be explicitly set to '1' before software can modify the Flash memory; both PSWE and PSEE must be set to '1' before software can erase Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A security lock byte stored at the last byte of Flash user space protects the Flash program memory from being read or altered across the C2 interface. See Table 10.2 for the security byte description; see Figure 10.1 for a program memory map and the security byte locations for each device.

# SFR Definition 12.1. XBR0: Port I/O Crossbar Register 0

| R/W               | R/W<br>XSKP6 | R/W<br>XSKP5                                                         | R/W<br>XSKP4                                                              | R/W<br>XSKP3                                                        | R/W<br>XSKP2                               | R/W<br>XSKP1           | R/W<br>XSKP0 | Reset Value 0000000                     |

|-------------------|--------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|------------------------|--------------|-----------------------------------------|

| Bit7              | Bit6         | Bit5                                                                 | Bit4                                                                      | Bit3                                                                | Bit2                                       | Bit1                   | Bit0         | SFR Address:                            |

| Bit7:<br>Bits6–0: |              | Crossbar S<br>elect Port p<br>or ADC or C<br>CNVSTR in<br>nding P0.n | kip Enable<br>bins to be sl<br>Comparator<br>nput) should<br>pin is not s | Bits<br>kipped by th<br>) or used as<br>d be skippe<br>kipped by tl | s special fur<br>d by the Cr<br>he Crossba | nctions (VR<br>ossbar. |              | 0xE1<br>Ised as ana-<br>external oscil- |

## SFR Definition 12.2. XBR1: Port I/O Crossbar Register 1

| R/W      | R/W         | R/W                                                                        | R/W         | R/W        | R/W       | R/W  | R/W    | Reset Value  |  |  |

|----------|-------------|----------------------------------------------------------------------------|-------------|------------|-----------|------|--------|--------------|--|--|

| -        | AOME        | CP0AOEN                                                                    | CPOOEN      | SYSCKE     |           | -    | UTX0EN | 7            |  |  |

| Bit7     | Bit6        | Bit5                                                                       | Bit4        | Bit3       | Bit2      | Bit1 | Bit0   | SFR Address: |  |  |

| Ditt     | Dito        | Dito                                                                       | Ditt        | Dito       | DIE       | Ditt | Dito   | 0xE2         |  |  |

|          |             |                                                                            |             |            |           |      |        | UNEZ         |  |  |

| Bits7–6: | PCA0ME: P   | CA Module                                                                  | /0 Enable   | Bits       |           |      |        |              |  |  |

|          | 00: All PCA | I/O unavaila                                                               | ble at Port | pins.      |           |      |        |              |  |  |

|          | 01: CEX0 rc |                                                                            |             | •          |           |      |        |              |  |  |

|          | 10: CEX0, C | EX1 routed                                                                 | to Port pin | s.         |           |      |        |              |  |  |

|          | 11: CEX0, C | EX1, CEX2                                                                  | routed to F | Port pins. |           |      |        |              |  |  |

| Bit5:    |             | Comparator                                                                 |             |            | ut Enable |      |        |              |  |  |

|          | 0: Asynchro |                                                                            |             |            |           |      |        |              |  |  |

|          |             | nous CP0 ro                                                                |             |            |           |      |        |              |  |  |

| Bit4:    |             | omparator0                                                                 | •           | able       |           |      |        |              |  |  |

|          |             | ailable at Po                                                              |             |            |           |      |        |              |  |  |

| Dito     |             | ed to Port pi                                                              |             |            |           |      |        |              |  |  |

| Bit3:    |             | SYSCLK Out                                                                 |             |            |           |      |        |              |  |  |

|          | 0: /SYSCLK  |                                                                            | •           |            |           |      |        |              |  |  |

| Bit2:    |             | output route<br>SMBus I/O                                                  | •           | nn.        |           |      |        |              |  |  |

| DILZ.    | 0: SMBus I/ |                                                                            |             | inc        |           |      |        |              |  |  |

|          |             | L routed to F                                                              |             |            |           |      |        |              |  |  |

| Bit1:    | ,           |                                                                            | •           |            |           |      |        |              |  |  |

| Ditt.    |             | JRX0EN: UART RX Enable<br>): UART RX0 unavailable at Port pin.             |             |            |           |      |        |              |  |  |

|          |             | UART RX0 unavailable at Port pin.<br>UART RX0 routed to Port pin P0.5.     |             |            |           |      |        |              |  |  |

| Bit0:    |             | ART TX Out                                                                 | •           |            |           |      |        |              |  |  |

|          |             |                                                                            |             |            |           |      |        |              |  |  |

|          |             | : UART TX0 unavailable at Port pin.<br>: UART TX0 routed to Port pin P0.4. |             |            |           |      |        |              |  |  |

|          |             |                                                                            |             |            |           |      |        |              |  |  |

|                | Valu             | ies   | Read    | b   | Current SMbus State                                                                 | Typical Response Options                                                                                                                                                |     | /alue<br>Vritte |     |

|----------------|------------------|-------|---------|-----|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|

| Mode           | Status<br>Vector | ACKRQ | ARBLOST | ACK |                                                                                     |                                                                                                                                                                         | STA | STO             | ACK |

|                | 0010             | 1     | 0       | X   | A slave address was received;<br>ACK requested.                                     | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0   | 0               | 1   |

|                |                  |       |         |     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0   |

|                |                  |       |         |     |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0   | 0               | 1   |

|                |                  | 1     | 1       | Х   | Lost arbitration as master; slave<br>address received; ACK<br>requested.            | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0   | 0               | 1   |

|                |                  |       |         |     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0   |

| SLAVE RECEIVER |                  |       |         |     |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0   | 0               | 1   |

| SL/            |                  |       |         |     |                                                                                     | Reschedule failed transfer;<br>do not acknowledge received<br>address                                                                                                   | 1   | 0               | 0   |

|                | 0010             | 0     | 1       | Х   | Lost arbitration while attempting a                                                 | Abort failed transfer.                                                                                                                                                  | 0   | 0               | Х   |

|                | 0001             |       |         | V   | repeated START.                                                                     | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X   |

|                | 0001             | 1     | 1       |     | Lost arbitration while attempting a STOP.                                           | complete/aborted).                                                                                                                                                      | 0   | 0               | 0   |

|                |                  | 0     | 0       |     | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver. | Clear STO.                                                                                                                                                              | 0   | 0               | X   |

|                |                  | 0     | 1       | Х   |                                                                                     | Abort transfer.                                                                                                                                                         | 0   | 0               | Х   |

|                |                  |       |         |     | STOP.                                                                               | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X   |

|                | 0000             | 1     | 0       | X   | A slave byte was received; ACK requested.                                           | Acknowledge received byte;<br>Read SMB0DAT.                                                                                                                             | 0   | 0               | 1   |

|                |                  |       |         |     |                                                                                     | Do not acknowledge received byte.                                                                                                                                       | 0   | 0               | 0   |

|                |                  | 1     | 1       | х   | Lost arbitration while transmitting                                                 | Abort failed transfer.                                                                                                                                                  | 0   | 0               | 0   |

|                |                  |       |         |     | a data byte as master.                                                              | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | 0   |

# Table 13.4. SMBus Status Decoding (Continued)

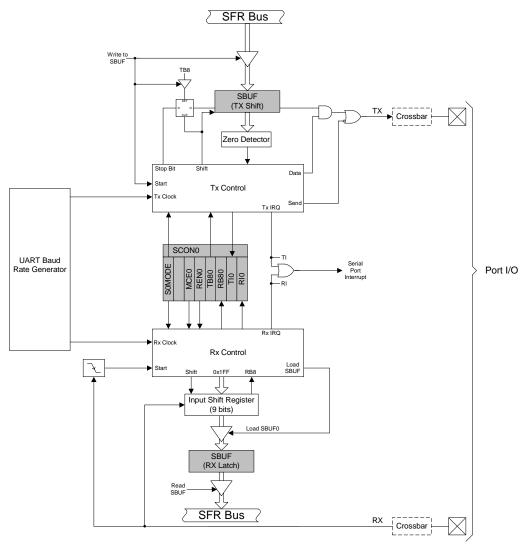

# 14. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in **Section "14.1. Enhanced Baud Rate Generation" on page 132**). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

UARTO has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Reading SBUF0 accesses the buffered Receive register; writing SBUF0 accesses the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

# SFR Definition 14.2. SBUF0: Serial (UART0) Port Data Buffer

#### 15.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 15.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see **Section "8.3.2. External Interrupts" on page 73** for details on the external input signals /INT0 and /INT1).

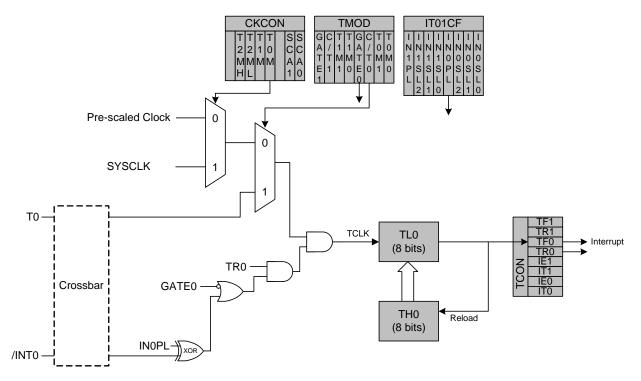

Figure 15.2. T0 Mode 2 Block Diagram

## 16.1. PCA Counter/Timer

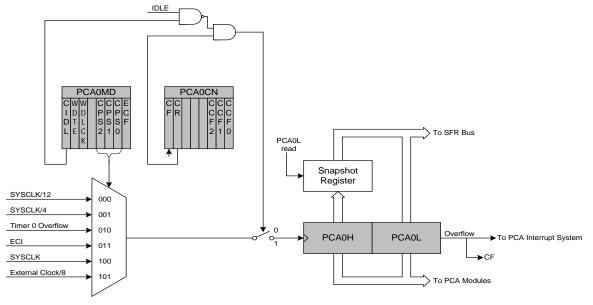

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter**. Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2-CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 16.1. **Note that in 'External oscillator source divided by 8' mode, the external oscillator source is synchronized with the system clock, and must have a frequency less than or equal to the system clock.**

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software (Note: PCA0 interrupts must be globally enabled before CF interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1). Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2 | CPS1 | CPS0 | Timebase                                                              |

|------|------|------|-----------------------------------------------------------------------|

| 0    | 0    | 0    | System clock divided by 12                                            |

| 0    | 0    | 1    | System clock divided by 4                                             |

| 0    | 1    | 0    | Timer 0 overflow                                                      |

| 0    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

| 1    | 0    | 0    | System clock                                                          |

| 1    | 0    | 1    | External oscillator source divided by 8 <sup>*</sup>                  |

| Table 16.1. PCA Timebase Input Options | Table | 16.1. | PCA | Timebase | Input | Options |

|----------------------------------------|-------|-------|-----|----------|-------|---------|

|----------------------------------------|-------|-------|-----|----------|-------|---------|

\*Note: External oscillator source divided by 8 is synchronized with the system clock.

# C8051F300/1/2/3/4/5

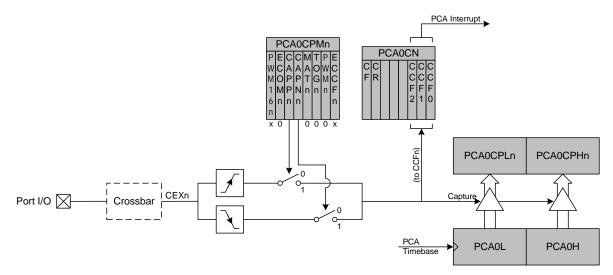

### 16.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/ timer and copy it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 16.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

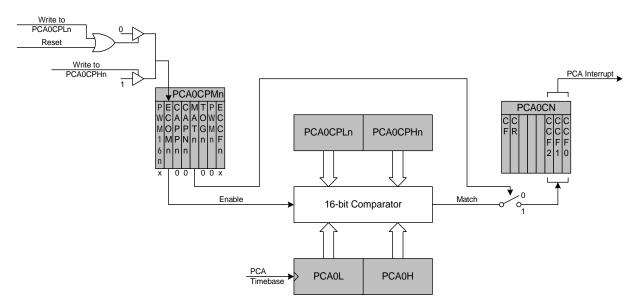

### 16.2.2. Software Timer (Compare) Mode

In Software Timer mode, the PCA counter/timer value is compared to the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn). When a match occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. Setting the ECOMn and MATn bits in the PCA0CPMn register enables Software Timer mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 16.5. PCA Software Timer Mode Diagram

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

http://www.silabs.com