Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Last Time Buy                                                  |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 8x8b                                                       |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 14-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f302-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 14.3. Timer Settings for Standard Baud Rates                        |

|---------------------------------------------------------------------------|

| Using an External 22.1184 MHz Oscillator 139                              |

| Table 14.4. Timer Settings for Standard Baud Rates                        |

| Using an External 18.432 MHz Oscillator 140                               |

| Table 14.5. Timer Settings for Standard Baud Rates                        |

| Using an External 11.0592 MHz Oscillator 141                              |

| Table 14.6. Timer Settings for Standard Baud Rates                        |

| Using an External 3.6864 MHZ Oscillator 142                               |

| 15. Timers                                                                |

| 16. Programmable Counter Array                                            |

| Table 16.1. PCA Timebase Input Options 156                                |

| Table 16.2. PCA0CPM Register Settings for PCA Capture/Compare Modules 157 |

| Table 16.3. Watchdog Timer Timeout Intervals 166                          |

| 17.C2 Interface                                                           |

## List of Registers

| SFR Definition 5.1. AMX0SL: AMUX0 Channel Select (C8051F300/2)        | 42  |

|-----------------------------------------------------------------------|-----|

| SFR Definition 5.2. ADC0CF: ADC0 Configuration (C8051F300/2)          | 43  |

| SFR Definition 5.3. ADC0: ADC0 Data Word (C8051F300/2)                | 43  |

| SFR Definition 5.4. ADC0CN: ADC0 Control (C8051F300/2)                | 44  |

| SFR Definition 5.5. ADC0GT: ADC0 Greater-Than Data Byte (C8051F300/2) | 46  |

| SFR Definition 5.6. ADC0LT: ADC0 Less-Than Data Byte (C8051F300/2)    | 46  |

| SFR Definition 6.1. REF0CN: Reference Control Register                | 50  |

| SFR Definition 7.1. CPT0CN: Comparator0 Control                       |     |

| SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection                 | 54  |

| SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection                | 54  |

| SFR Definition 8.1. DPL: Data Pointer Low Byte                        |     |

| SFR Definition 8.2. DPH: Data Pointer High Byte                       | 69  |

| SFR Definition 8.3. SP: Stack Pointer                                 | 69  |

| SFR Definition 8.4. PSW: Program Status Word                          | 70  |

| SFR Definition 8.5. ACC: Accumulator                                  | 71  |

| SFR Definition 8.6. B: B Register                                     | 71  |

| SFR Definition 8.7. IE: Interrupt Enable                              | 75  |

| SFR Definition 8.8. IP: Interrupt Priority                            | 76  |

| SFR Definition 8.9. EIE1: Extended Interrupt Enable 1                 | 77  |

| SFR Definition 8.10. EIP1: Extended Interrupt Priority 1              | 78  |

| SFR Definition 8.11. IT01CF: INT0/INT1 Configuration                  |     |

| SFR Definition 8.12. PCON: Power Control                              |     |

| SFR Definition 9.1. RSTSRC: Reset Source                              | 87  |

| SFR Definition 10.1. PSCTL: Program Store R/W Control                 | 92  |

| SFR Definition 10.2. FLKEY: Flash Lock and Key                        |     |

| SFR Definition 10.3. FLSCL: Flash Scale                               |     |

| SFR Definition 11.1. OSCICL: Internal Oscillator Calibration          | 98  |

| SFR Definition 11.2. OSCICN: Internal Oscillator Control              |     |

| SFR Definition 11.3. OSCXCN: External Oscillator Control              | 100 |

| SFR Definition 12.1. XBR0: Port I/O Crossbar Register 0               |     |

| SFR Definition 12.2. XBR1: Port I/O Crossbar Register 1               |     |

| SFR Definition 12.3. XBR2: Port I/O Crossbar Register 2               | 108 |

| SFR Definition 12.4. P0: Port0 Register                               |     |

| SFR Definition 12.5. P0MDIN: Port0 Input Mode                         |     |

| SFR Definition 12.6. P0MDOUT: Port0 Output Mode                       |     |

| SFR Definition 13.1. SMB0CF: SMBus Clock/Configuration                | 118 |

| SFR Definition 13.2. SMB0CN: SMBus Control                            |     |

| SFR Definition 13.3. SMB0DAT: SMBus Data                              |     |

| SFR Definition 14.1. SCON0: Serial Port 0 Control                     |     |

| SFR Definition 14.2. SBUF0: Serial (UART0) Port Data Buffer           |     |

| SFR Definition 15.1. TCON: Timer Control                              |     |

| SFR Definition 15.2. TMOD: Timer Mode                                 |     |

| SFR Definition 15.3. CKCON: Clock Control                             | 149 |

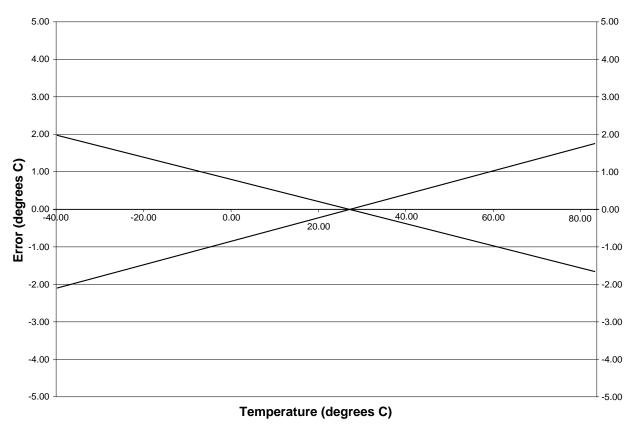

Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V)

### Table 5.1. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                                                                                                              | Conditions                         | Min  | Тур    | Мах  | Units   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------|--------|------|---------|--|--|--|--|

| DC Accuracy                                                                                                                                            |                                    |      |        |      |         |  |  |  |  |

| Resolution                                                                                                                                             |                                    |      | 8      |      | bits    |  |  |  |  |

| Integral Nonlinearity                                                                                                                                  |                                    | —    | ±0.5   | ±1   | LSB     |  |  |  |  |

| Differential Nonlinearity                                                                                                                              | Guaranteed Monotonic               | —    | ±0.5   | ±1   | LSB     |  |  |  |  |

| Offset Error                                                                                                                                           |                                    | -5.0 | 0.5    | 5.0  | LSB     |  |  |  |  |

| Full Scale Error                                                                                                                                       | Differential mode                  | -5.0 | -1     | 5.0  | LSB     |  |  |  |  |

| Dynamic Performance (10 kHz Sine-wave Differential Input, 1 dB below Full Scale, 500 ksps)                                                             |                                    |      |        |      |         |  |  |  |  |

| Signal-to-Noise Plus Distortion                                                                                                                        |                                    | 45   | 48     | —    | dB      |  |  |  |  |

| Total Harmonic Distortion                                                                                                                              | Up to the 5 <sup>th</sup> harmonic |      | -56    | —    | dB      |  |  |  |  |

| Spurious-Free Dynamic Range                                                                                                                            |                                    |      | 58     | —    | dB      |  |  |  |  |

| Conversion Rate                                                                                                                                        |                                    |      |        |      |         |  |  |  |  |

| SAR Conversion Clock                                                                                                                                   |                                    | —    |        | 6    | MHz     |  |  |  |  |

| Conversion Time in SAR Clocks                                                                                                                          |                                    | 11   | _      | —    | clocks  |  |  |  |  |

| Track/Hold Acquisition Time                                                                                                                            |                                    | 300  | _      | —    | ns      |  |  |  |  |

| Throughput Rate                                                                                                                                        |                                    | —    | —      | 500  | ksps    |  |  |  |  |

| Analog Inputs                                                                                                                                          |                                    |      | 1      |      |         |  |  |  |  |

| Input Voltage Range                                                                                                                                    |                                    | 0    | —      | VREF | V       |  |  |  |  |

| Input Capacitance                                                                                                                                      |                                    | —    | 5      | —    | pF      |  |  |  |  |

| Temperature Sensor                                                                                                                                     |                                    | —    | _      | —    |         |  |  |  |  |

| Linearity <sup>1,2,3</sup>                                                                                                                             |                                    | —    | ±0.5   | —    | °C      |  |  |  |  |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    | —    | 3350   | —    | μV / °C |  |  |  |  |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    |      | ±110   |      |         |  |  |  |  |

| Offset <sup>1,2,3</sup>                                                                                                                                | (Temp = 0 °C)                      |      | 897±31 | —    | mV      |  |  |  |  |

| Power Specifications                                                                                                                                   |                                    |      |        |      |         |  |  |  |  |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0)                                                                                             | Operating Mode, 500 ksps           | —    | 400    | 900  | μA      |  |  |  |  |

| Power Supply Rejection                                                                                                                                 |                                    | —    | ±0.3   | —    | mV/V    |  |  |  |  |

| <ul> <li>Notes:</li> <li>1. Represents one standard devi</li> <li>2. Measured with PGA Gain = 2.</li> <li>3. Includes ADC offset, gain, and</li> </ul> |                                    |      |        |      |         |  |  |  |  |

The output of Comparator0 can be polled in software, used as an interrupt source, and/or routed to a Port pin. When routed to a Port pin, the Comparator0 output is available asynchronous or synchronous to the system clock; the asynchronous output is available even in STOP mode (with no system clock active). When disabled, the Comparator0 output (if assigned to a Port I/O pin via the Crossbar) defaults to the logic low state, and its supply current falls to less than 100 nA. See **Section "12.1. Priority Crossbar Decoder" on page 104** for details on configuring the Comparator0 output via the digital Crossbar. Comparator0 inputs can be externally driven from -0.25 to (V<sub>DD</sub>) + 0.25 V without damage or upset. The complete electrical specifications for Comparator0 are given in Table 7.1.

The Comparator0 response time may be configured in software via the CP0MD1-0 bits in register CPT0MD (see SFR Definition 7.3). Selecting a longer response time reduces the amount of power consumed by Comparator0. See Table 7.1 for complete timing and power consumption specifications.

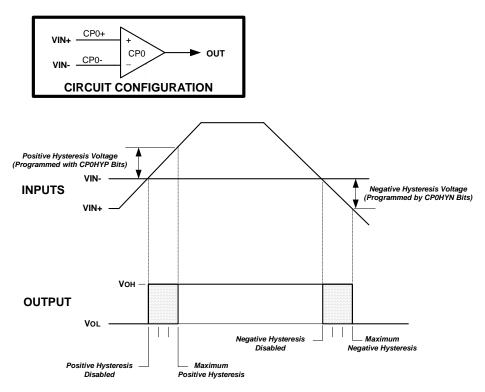

The hysteresis of Comparator0 is software-programmable via its Comparator0 Control register (CPT0CN). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator0 hysteresis is programmed using Bits3–0 in the Comparator0 Control Register CPT0CN (shown in SFR Definition 7.1). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 7.2, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

| Mnemonic      | Description                                | Bytes | Clock<br>Cycles |

|---------------|--------------------------------------------|-------|-----------------|

| MOVC A, @A+PC | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri   | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A   | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct   | Push direct byte onto stack                | 2     | 2               |

| POP direct    | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn     | Exchange Register with A                   | 1     | 1               |

| XCH A, direct | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri    | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri   | Exchange low nibble of indirect RAM with A | 1     | 2               |

|               | Boolean Manipulation                       | ŀ     |                 |

| CLR C         | Clear Carry                                | 1     | 1               |

| CLR bit       | Clear direct bit                           | 2     | 2               |

| SETB C        | Set Carry                                  | 1     | 1               |

| SETB bit      | Set direct bit                             | 2     | 2               |

| CPL C         | Complement Carry                           | 1     | 1               |

| CPL bit       | Complement direct bit                      | 2     | 2               |

| ANL C, bit    | AND direct bit to Carry                    | 2     | 2               |

| ANL C, /bit   | AND complement of direct bit to Carry      | 2     | 2               |

| ORL C, bit    | OR direct bit to carry                     | 2     | 2               |

| ORL C, /bit   | OR complement of direct bit to Carry       | 2     | 2               |

| MOV C, bit    | Move direct bit to Carry                   | 2     | 2               |

| MOV bit, C    | Move Carry to direct bit                   | 2     | 2               |

| JC rel        | Jump if Carry is set                       | 2     | 2/3             |

| JNC rel       | Jump if Carry is not set                   | 2     | 2/3             |

| JB bit, rel   | Jump if direct bit is set                  | 3     | 3/4             |

| JNB bit, rel  | Jump if direct bit is not set              | 3     | 3/4             |

| JBC bit, rel  | Jump if direct bit is set and clear bit    | 3     | 3/4             |

|               | Program Branching                          |       |                 |

| ACALL addr11  | Absolute subroutine call                   | 2     | 3               |

| LCALL addr16  | Long subroutine call                       | 3     | 4               |

| RET           | Return from subroutine                     | 1     | 5               |

| RETI          | Return from interrupt                      | 1     | 5               |

| AJMP addr11   | Absolute jump                              | 2     | 3               |

| LJMP addr16   | Long jump                                  | 3     | 4               |

| SJMP rel      | Short jump (relative address)              | 2     | 3               |

| JMP @A+DPTR   | Jump indirect relative to DPTR             | 1     | 3               |

| JZ rel        | Jump if A equals zero                      | 2     | 2/3             |

### Table 8.1. CIP-51 Instruction Set Summary (Continued)

| Register      | Address            | Description                                              | Page<br>No. |

|---------------|--------------------|----------------------------------------------------------|-------------|

| FLSCL         | 0xB6               | Flash Scale                                              | 93          |

| IE            | 0xA8               | Interrupt Enable                                         | 75          |

| IP            | 0xB8               | Interrupt Priority                                       | 76          |

| IT01CF        | 0xE4               | INT0/INT1 Configuration Register                         | 79          |

| OSCICL        | 0xB3               | Internal Oscillator Calibration                          | 98          |

| OSCICN        | 0xB2               | Internal Oscillator Control                              | 98          |

| OSCXCN        | 0xB1               | External Oscillator Control                              | 100         |

| P0            | 0x80               | Port 0 Latch                                             | 109         |

| POMDIN        | 0xF1               | Port 0 Input Mode Configuration                          | 109         |

| POMDOUT       | 0xA4               | Port 0 Output Mode Configuration                         | 110         |

| PCA0CN        | 0xD8               | PCA Control                                              | 167         |

| PCA0MD        | 0xD9               | PCA Mode                                                 | 168         |

| PCA0CPH0      | 0xFC               | PCA Capture 0 High                                       | 171         |

| PCA0CPH1      | 0xEA               | PCA Capture 1 High                                       | 171         |

| PCA0CPH2      | 0xEC               | PCA Capture 2 High                                       | 171         |

| PCA0CPL0      | 0xFB               | PCA Capture 0 Low                                        | 171         |

| PCA0CPL1      | 0xE9               | PCA Capture 1 Low                                        | 171         |

| PCA0CPL2      | 0xEB               | PCA Capture 2 Low                                        | 171         |

| PCA0CPM0      | 0xDA               | PCA Module 0 Mode Register                               | 169         |

| PCA0CPM1      | 0xDB               | PCA Module 1 Mode Register                               | 169         |

| PCA0CPM2      | 0xDC               | PCA Module 2 Mode Register                               | 169         |

| PCA0H         | 0xFA               | PCA Counter High                                         | 170         |

| PCA0L         | 0xF9               | PCA Counter Low                                          | 170         |

| PCON          | 0x87               | Power Control                                            | 81          |

| PSCTL         | 0x8F               | Program Store R/W Control                                | 92          |

| PSW           | 0xD0               | Program Status Word                                      | 70          |

| REF0CN        | 0xD1               | Voltage Reference Control                                | 49          |

| RSTSRC        | 0xEF               | Reset Source Configuration/Status                        | 87          |

| SBUF0         | 0x99               | UART 0 Data Buffer                                       | 137         |

| SCON0         | 0x98               | UART 0 Control                                           | 136         |

| SMB0CF        | 0xC1               | SMBus Configuration                                      | 118         |

| SMB0CN        | 0xC0               | SMBus Control                                            | 120         |

| SMB0DAT       | 0xC2               | SMBus Data                                               | 122         |

| SP            | 0x81               | Stack Pointer                                            | 69          |

| TMR2CN        | 0xC8               | Timer/Counter 2 Control                                  | 154         |

| TCON          | 0x88               | Timer/Counter Control                                    | 147         |

| TH0           | 0x8C               | Timer/Counter 0 High                                     | 150         |

| *Note: SFRs a | re listed in aloha | abetical order. All undefined SFR locations are reserved | I           |

### Table 8.3. Special Function Registers\* (Continued)

| R/W         | R/W         | R/W         | R/W                | R/W       | R/W           | R/W          | R              | Reset Value      |

|-------------|-------------|-------------|--------------------|-----------|---------------|--------------|----------------|------------------|

| CY          | AC          | F0          | RS1                | RS0       | OV            | F1           | PARITY         | 0000000          |

| Bit7        | Bit6        | Bit5        | Bit4               | Bit3 Bit2 |               | Bit1         | Bit0           | SFR Address:     |

|             |             |             |                    |           |               | (bi          | t addressable) | 0xD0             |

|             |             |             |                    |           |               |              |                |                  |

| Bit7:       | CY: Carry   | •           |                    |           |               |              |                |                  |

|             |             |             | he last arithmet   |           |               |              |                | or a borrow      |

| <b>B</b> HA |             |             | eared to logic 0 t | by all ot | ner arithme   | tic operatio | ns.            |                  |

| Bit6:       | AC: Auxilia |             |                    |           |               |              |                |                  |

|             |             |             | he last arithmetic |           |               |              |                |                  |

|             | tions.      | raction) th | e high order nib   |           |               |              |                | nmetic opera-    |

| Bit5:       | F0: User F  | lag 0       |                    |           |               |              |                |                  |

| Dito.       |             | 0           | able, general pu   | irpose fl | ad for use i  | under softw  | are control    | _                |

| Bits4–3:    |             |             | Bank Select.       |           |               |              |                |                  |

|             |             |             | ich register ban   | k is use  | d during reg  | gister acces | sses.          |                  |

|             |             |             | 0                  |           |               |              |                |                  |

|             | RS1         | RS0         | Register Bank      | Ad        | dress         |              |                |                  |

|             | 0           | 0           | 0                  | 0x0       | 0–0x07        |              |                |                  |

|             | 0           | 1           | 1                  | 0x0       | 8–0x0F        |              |                |                  |

|             | 1           | 0           | 2                  | 0x1       | 0–0x17        |              |                |                  |

|             | 1           | 1           | 3                  | 0x1       | 8–0x1F        |              |                |                  |

| D:40        | O(k) O(k)   |             |                    |           |               |              |                |                  |

| Bit2:       | OV: Overf   | •           | der the following  |           | etancoc:      |              |                |                  |

|             |             |             | or SUBB instruct   |           |               | change ove   | rflow          |                  |

|             |             |             | results in an ov   |           | •             | •            |                |                  |

|             |             |             | causes a divide-   |           |               |              |                |                  |

|             |             |             | d to 0 by the AD   |           |               | /IUL, and D  | IV instruction | ons in all other |

|             | cases.      |             | 2                  |           | . ,           |              |                |                  |

| Bit1:       | F1: User F  | lag 1.      |                    |           |               |              |                |                  |

|             |             |             | able, general pu   | irpose fl | ag for use ι  | under softw  | are control    |                  |

| Bit0:       | PARITY: F   |             |                    |           |               |              |                |                  |

|             |             | -           | 1 if the sum of t  | he eight  | bits in the a | accumulato   | or is odd an   | d cleared if the |

|             | sum is eve  | en.         |                    |           |               |              |                |                  |

|             |             |             |                    |           |               |              |                |                  |

### SFR Definition 8.4. PSW: Program Status Word

#### 8.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 12 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interruptpending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regard-less of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE1). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

# Note: Any instruction that clears the EA bit should be immediately followed by an instruction that has two or more opcode bytes. For example:

// in 'C': EA = 0; // clear EA bit EA = 0; // ... followed by another 2-byte opcode ; in assembly: CLR EA ; clear EA bit CLR EA ; ... followed by another 2-byte opcode

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction which clears the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. However, a read of the EA bit will return a '0' inside the interrupt service routine. When the "CLR EA" opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will reenter the ISR after the completion of the next instruction.

#### 8.3.1. MCU Interrupt Sources and Vectors

The MCUs support 12 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 8.4 on page 74. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

| Parameter                                                     | Conditions                           | Min  | Тур  | Max | Units |  |  |  |  |

|---------------------------------------------------------------|--------------------------------------|------|------|-----|-------|--|--|--|--|

| Calibrated Internal Oscillator                                | C8051F300/1 devices<br>-40 to +85 °C | 24   | 24.5 | 25  | MHz   |  |  |  |  |

| Frequency                                                     | C8051F300/1 devices<br>0 to +70 °C   | 24.3 | 24.7 | 25  | MHz   |  |  |  |  |

| Uncalibrated Internal Oscillator<br>Frequency                 | C8051F302/3/4/5 devices              | 16   | 20   | 24  | MHz   |  |  |  |  |

| Internal Oscillator Supply Current<br>(from V <sub>DD</sub> ) | OSCICN.2 = 1                         |      | 450  |     | μA    |  |  |  |  |

#### Table 11.1. Internal Oscillator Electrical Characteristics

#### 11.2. External Oscillator Drive Circuit

-40 to +85 °C unless otherwise specified

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 11.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 11.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 11.3).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are occupied as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is occupied as XTAL2. The Port I/O Crossbar should be configured to skip the occupied Port pins; see **Section "12.1. Priority Crossbar Decoder" on page 104** for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See **Section "12.2. Port I/O Initialization" on page 106** for details on Port input mode selection.

#### 11.3. System Clock Selection

The CLKSL bit in register OSCICN selects which oscillator is used as the system clock. CLKSL must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no start-up time.

#### SFR Definition 11.3. OSCXCN: External Oscillator Control

|          | <b>D</b> 444     | 5 444                    | 544                                 | -          | <b>5</b> 4 4     | 5 4 4        | 5 ***        | 5                    |

|----------|------------------|--------------------------|-------------------------------------|------------|------------------|--------------|--------------|----------------------|

|          |                  | R/W<br>XOSCMD1           |                                     | R          | R/W<br>XFCN2     | R/W<br>XFCN1 | R/W<br>XFCN0 | Reset Value          |

| Bit7     | Bit6             | Bit5                     | Bit4                                |            | Bit2             |              | Bit0         | 00000000             |

| BIT      | BIto             | BItS                     | BIt4                                | Bit3       | BItZ             | Bit1         | Bitu         | SFR Address:<br>0xB1 |

|          |                  |                          |                                     |            |                  |              |              | UXDI                 |

| Bit7:    |                  | ustal Oscillat           | or Valid Flag.                      |            |                  |              |              |                      |

| Ditr.    | (Read only w     |                          |                                     |            |                  |              |              |                      |

|          | · ·              |                          | used or not ye                      | t stable.  |                  |              |              |                      |

|          | •                |                          | nning and stab                      |            |                  |              |              |                      |

| Bits6-4: | XOSCMD2-0        | 0: External C            | scillator Mode                      | Bits.      |                  |              |              |                      |

|          | 00x: Externa     | l Oscillator c           | ircuit off.                         |            |                  |              |              |                      |

|          | 010: Externa     |                          |                                     |            |                  |              |              |                      |

|          |                  |                          | ck Mode with o                      | •          | -                |              |              |                      |

|          |                  |                          | with divide by                      | -          |                  |              |              |                      |

|          | •                |                          | Mode with div                       | ide by 2   | stage.           |              |              |                      |

|          | 110: Crystal     |                          |                                     | by 2 of    |                  |              |              |                      |

| Bit3:    | •                |                          | ode with divide<br>Vrite = don't ca | •          | ige.             |              |              |                      |

| Bits2–0: |                  |                          | ator Frequenc                       |            | l Rits           |              |              |                      |

| B102 0.  | 000-111: See     |                          | •                                   |            |                  |              |              |                      |

|          | XFCN             | Crystal (XC              | OSCMD = 11x)                        | RC ()      | (OSCMD =         | 10x) C       | (XOSCMD      | = 10x)               |

|          | 000              | f ≤ 3                    | 32 kHz                              |            | f≤25 kHz         |              | K Factor =   | 0.87                 |

|          | 001              | 32 kHz <                 | < f ≤ 84 kHz                        | 25 k       | Hz < f ≤ 50      | kHz          | K Factor =   | = 2.6                |

|          | 010              | 84 kHz <                 | f ≤ 225 kHz                         | 50 kł      | Hz < f ≤ 100     | kHz          | K Factor =   | = 7.7                |

|          | 011              | 225 kHz «                | < f ≤ 590 kHz                       | 100 k      | $Hz < f \le 200$ | ) kHz        | K Factor =   | = 22                 |

|          | 100              | 590 kHz <                | < f ≤ 1.5 MHz                       | 200 k      | $Hz < f \le 400$ | ) kHz        | K Factor =   | = 65                 |

|          | 101              | 1.5 MHz                  | $< f \le 4 MHz$                     | 400 k      | $Hz < f \le 800$ | ) kHz        | K Factor =   | 180                  |

|          | 110              | 4 MHz <                  | $f \le 10 \text{ MHz}$              | 800 k      | Hz < f ≤ 1.6     | MHz          | K Factor =   | 664                  |

|          | 111              | 10 MHz «                 | < f ≤ 30 MHz                        | 1.6 M      | Hz < f ≤ 3.2     | MHz          | K Factor =   | 1590                 |

| CRYSTA   |                  | cuit from Fig            | ure 11.1, Optio                     | n 1· XO    | SCMD - 11        | x)           |              |                      |

| GRIGIA   |                  |                          | natch crystal fr                    |            |                  | ~)           |              |                      |

|          |                  |                          |                                     | - 40.0110) |                  |              |              |                      |

| RC MOD   | E (Circuit fror  | n Figure 11.1            | , Option 2; XC                      | SCMD       | = 10x)           |              |              |                      |

|          |                  |                          | natch frequend                      |            |                  |              |              |                      |

|          | $f = 1.23(10^3)$ | )/(R x C), w             | here                                |            |                  |              |              |                      |

|          | f = frequency    |                          |                                     |            |                  |              |              |                      |

|          | C = capacito     | or value in pF           |                                     |            |                  |              |              |                      |

|          | R = Pull-up i    | esistor value            | e in kΩ                             |            |                  |              |              |                      |

| C MODE   | (Circuit from    | Figure 11.1,             | Option 3; XOS                       | SCMD =     | 10x)             |              |              |                      |

|          | •                | •                        | the oscillation                     |            | ,                | :            |              |                      |

|          | f = KF / (C x    | V <sub>DD</sub> ), where | )                                   |            | -                |              |              |                      |

|          | f = frequency    | y of oscillatio          | n in MHz                            |            |                  |              |              |                      |

|          |                  |                          | TAL2 pin in pl                      | =          |                  |              |              |                      |

|          | $V_{DD} = Powe$  | r Supply on I            | MCU in volts                        |            |                  |              |              |                      |

|          |                  |                          |                                     |            |                  |              |              |                      |

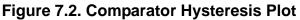

### Figure 12.4. Crossbar Priority Decoder with XBR0 = 0x44

Registers XBR1 and XBR2 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL). Either or both of the UART signals may be selected by the Crossbar. UART0 pin assignments are fixed for bootloading purposes: when UART TX0 is selected, it is always assigned to P0.4; when UART RX0 is selected, it is always assigned to P0.5. Standard Port I/Os appear contiguously after the prioritized functions have been assigned. For example, if assigned functions that take the first 3 Port I/O (P0.[2:0]), 5 Port I/O are left for analog or GPIO use.

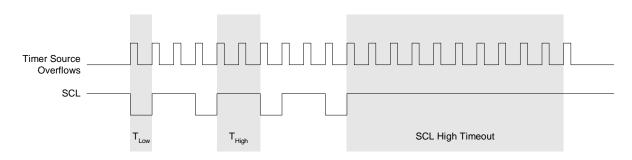

#### Figure 13.4. Typical SMBus SCL Generation

Setting the EXTHOLD bit extends the minimum setup and hold times for the SDA line. The minimum SDA setup time defines the absolute minimum time that SDA is stable before SCL transitions from low-to-high. The minimum SDA hold time defines the absolute minimum time that the current SDA value remains stable after SCL transitions from high-to-low. EXTHOLD should be set so that the minimum setup and hold times meet the SMBus Specification requirements of 250 ns and 300 ns, respectively. Table 13.2 shows the minimum setup and hold times for the two EXTHOLD settings. Setup and hold time extensions are typically necessary when SYSCLK is above 10 MHz.

| EXTHOLD | Minimum SDA Setup Time                                                              | Minimum SDA Hold Time |

|---------|-------------------------------------------------------------------------------------|-----------------------|

| 0       | T <sub>low</sub> – 4 system clocks<br>OR<br>1 system clock + s/w delay <sup>*</sup> | 3 system clocks       |

| 1       | 11 system clocks                                                                    | 12 system clocks      |

Table 13.2. Minimum SDA Setup and Hold Times

\*Note: Setup Time for ACK bit transmissions and the MSB of all data transfers. The s/w delay occurs between the time SMB0DAT or ACK is written and when SI is cleared. Note that if SI is cleared in the same write that defines the outgoing ACK value, s/w delay is zero.

With the SMBTOE bit set, Timer 2 should be configured to overflow after 25 ms in order to detect SCL low timeouts (see **Section "13.3.3. SCL Low Timeout" on page 114**). The SMBus interface will force Timer 2 to reload while SCL is high, and allow Timer 2 to count when SCL is low. The Timer 2 interrupt service routine should be used to reset SMBus communication by disabling and reenabling the SMBus. Timer 2 configuration is described in **Section "15.2. Timer 2" on page 151**.

SMBus Free Timeout detection can be enabled by setting the SMBFTE bit. When this bit is set, the bus will be considered free if SDA and SCL remain high for more than 10 SMBus clock source periods (see Figure 13.4). When a Free Timeout is detected, the interface will respond as if a STOP was detected (an interrupt will be generated, and STO will be set).

|                | Valu                                                                          | ies                                                                                                              | Read                                                                                  | b   | Current SMbus State                                                                                                                                                     | Typical Response Options                                                                                                                                                |     | /alue<br>Vritte |     |

|----------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|

| Mode           | Status<br>Vector                                                              | ACKRQ                                                                                                            | ARBLOST                                                                               | ACK |                                                                                                                                                                         |                                                                                                                                                                         | STA | STO             | ACK |

|                | 0010                                                                          | 0010 1 0 X A slave address was received; Acknowledge received address (received slav address match, R/W b READ). |                                                                                       |     |                                                                                                                                                                         |                                                                                                                                                                         | 0   | 0               | 1   |

|                | Don                                                                           |                                                                                                                  |                                                                                       |     |                                                                                                                                                                         | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0   |

|                |                                                                               |                                                                                                                  |                                                                                       |     |                                                                                                                                                                         | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0   | 0               | 1   |

|                | 1 1 X Lost arbitration as master; slav<br>address received; ACK<br>requested. |                                                                                                                  | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ). | 0   | 0                                                                                                                                                                       | 1                                                                                                                                                                       |     |                 |     |

|                |                                                                               |                                                                                                                  |                                                                                       |     |                                                                                                                                                                         | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0   |

| SLAVE RECEIVER |                                                                               |                                                                                                                  |                                                                                       |     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0                                                                                                                                                                       | 0   | 1               |     |

| SL/            |                                                                               |                                                                                                                  |                                                                                       |     |                                                                                                                                                                         | Reschedule failed transfer;<br>do not acknowledge received<br>address                                                                                                   | 1   | 0               | 0   |

|                | 0010                                                                          | 0                                                                                                                | 1                                                                                     | Х   | Lost arbitration while attempting a                                                                                                                                     | Abort failed transfer.                                                                                                                                                  | 0   | 0               | Х   |

|                | 0001                                                                          |                                                                                                                  |                                                                                       | V   | repeated START.                                                                                                                                                         | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X   |

|                | 0001                                                                          | 1                                                                                                                | 1                                                                                     |     | Lost arbitration while attempting a STOP.                                                                                                                               | complete/aborted).                                                                                                                                                      | 0   | 0               | 0   |

|                |                                                                               | 0                                                                                                                | 0                                                                                     |     | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver.                                                                                     | Clear STO.                                                                                                                                                              | 0   | 0               | X   |

|                |                                                                               | 0                                                                                                                | 1                                                                                     | Х   |                                                                                                                                                                         | Abort transfer.                                                                                                                                                         | 0   | 0               | Х   |

|                |                                                                               |                                                                                                                  |                                                                                       |     | STOP.                                                                                                                                                                   | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X   |

|                | 0000                                                                          | 1                                                                                                                | 0                                                                                     | X   | A slave byte was received; ACK requested.                                                                                                                               | Acknowledge received byte;<br>Read SMB0DAT.                                                                                                                             | 0   | 0               | 1   |

|                |                                                                               |                                                                                                                  |                                                                                       |     |                                                                                                                                                                         | Do not acknowledge received byte.                                                                                                                                       | 0   | 0               | 0   |

|                |                                                                               | 1                                                                                                                | 1                                                                                     | х   | Lost arbitration while transmitting                                                                                                                                     | Abort failed transfer.                                                                                                                                                  | 0   | 0               | 0   |

|                |                                                                               |                                                                                                                  |                                                                                       |     | a data byte as master.                                                                                                                                                  | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | 0   |

#### Table 13.4. SMBus Status Decoding (Continued)

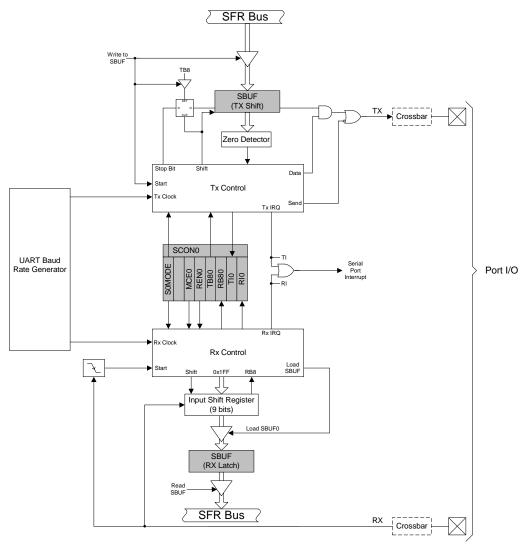

### 14. UART0

UART0 is an asynchronous, full duplex serial port offering modes 1 and 3 of the standard 8051 UART. Enhanced baud rate support allows a wide range of clock sources to generate standard baud rates (details in **Section "14.1. Enhanced Baud Rate Generation" on page 132**). Received data buffering allows UART0 to start reception of a second incoming data byte before software has finished reading the previous data byte.

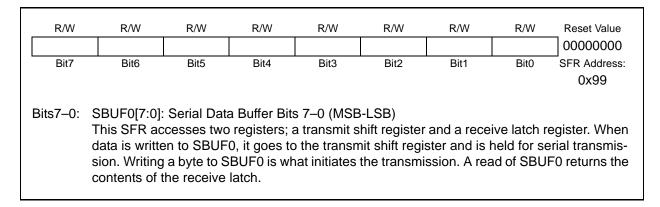

UARTO has two associated SFRs: Serial Control Register 0 (SCON0) and Serial Data Buffer 0 (SBUF0). The single SBUF0 location provides access to both transmit and receive registers. Reading SBUF0 accesses the buffered Receive register; writing SBUF0 accesses the Transmit register.

With UART0 interrupts enabled, an interrupt is generated each time a transmit is completed (TI0 is set in SCON0), or a data byte has been received (RI0 is set in SCON0). The UART0 interrupt flags are not cleared by hardware when the CPU vectors to the interrupt service routine. They must be cleared manually by software, allowing software to determine the cause of the UART0 interrupt (transmit complete or receive complete).

### SFR Definition 14.2. SBUF0: Serial (UART0) Port Data Buffer

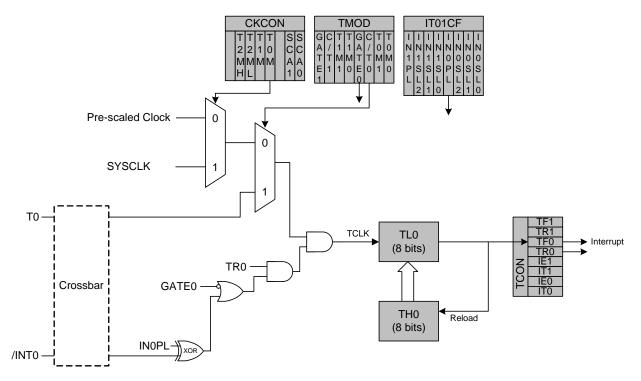

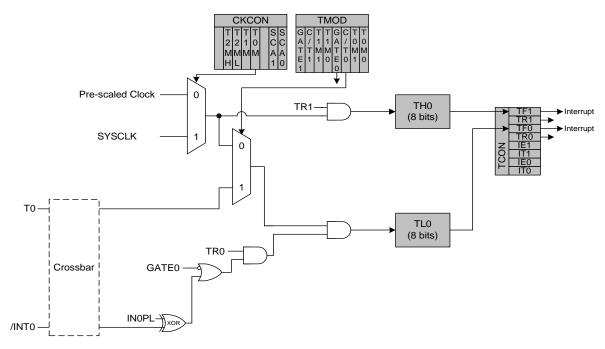

#### 15.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

#### 15.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see **Section "8.3.2. External Interrupts" on page 73** for details on the external input signals /INT0 and /INT1).

Figure 15.2. T0 Mode 2 Block Diagram

#### 15.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 15.3. T0 Mode 3 Block Diagram

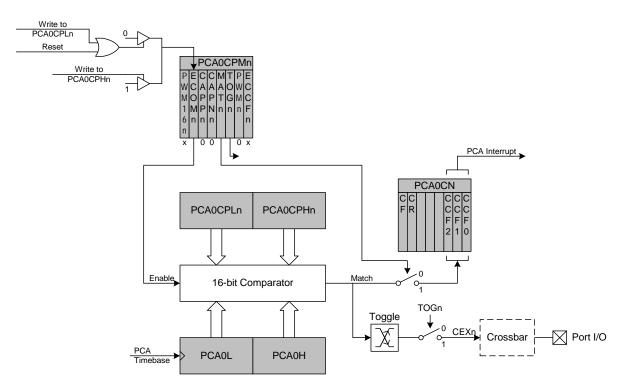

#### 16.2.3. High Speed Output Mode

In High Speed Output mode, a module's associated CEXn pin is toggled each time a match occurs between the PCA Counter and the module's 16-bit capture/compare register (PCA0CPHn and PCA0CPLn) Setting the TOGn, MATn, and ECOMn bits in the PCA0CPMn register enables the High-Speed Output mode.

**Important Note About Capture/Compare Registers**: When writing a 16-bit value to the PCA0 Capture/ Compare registers, the low byte should always be written first. Writing to PCA0CPLn clears the ECOMn bit to '0'; writing to PCA0CPHn sets ECOMn to '1'.

Figure 16.6. PCA High Speed Output Mode Diagram

## NOTES: