Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                   |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                     |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 8                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 8x8b                                                        |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                  |

| Supplier Device Package    | 14-SOIC                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f302-gsr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.4.Using the SMBus                                   | 115 |

|--------------------------------------------------------|-----|

| 13.4.1.SMBus Configuration Register                    |     |

| 13.4.2.SMB0CN Control Register                         |     |

| 13.4.3.Data Register                                   |     |

| 13.5.SMBus Transfer Modes                              |     |

| 13.5.1.Master Transmitter Mode                         |     |

| 13.5.2.Master Receiver Mode                            |     |

| 13.5.3.Slave Receiver Mode                             |     |

| 13.5.4.Slave Transmitter Mode                          |     |

|                                                        |     |

| 13.6.SMBus Status Decoding                             |     |

| 14.1.Enhanced Baud Rate Generation                     |     |

|                                                        |     |

| 14.2.Operational Modes<br>14.2.1.8-Bit UART            |     |

| 14.2.1.о-ын UART<br>14.2.2.9-Bit UART                  |     |

| 14.2.2.9-Bit OART                                      |     |

| •                                                      |     |

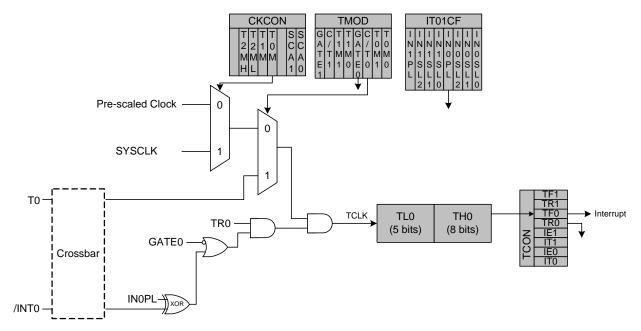

| 15.1.Timer 0 and Timer 1                               |     |

| 15.1.1.Mode 0: 13-bit Counter/Timer                    |     |

|                                                        |     |

| 15.1.2.Mode 1: 16-bit Counter/Timer                    |     |

| 15.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 15.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

| 15.2.Timer 2<br>15.2.1.16-bit Timer with Auto-Reload   |     |

|                                                        |     |

| 15.2.2.8-bit Timers with Auto-Reload                   |     |

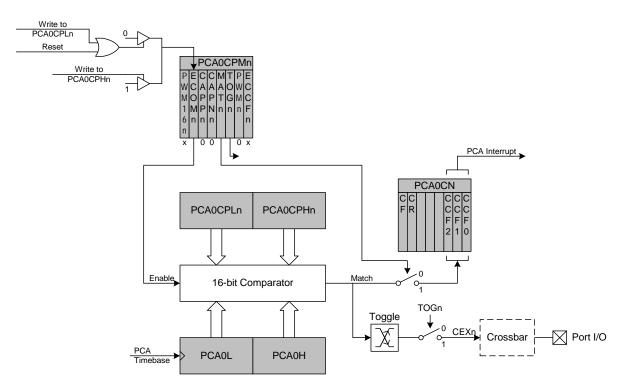

| 16. Programmable Counter Array                         |     |

| 16.1.PCA Counter/Timer                                 |     |

| 16.2.Capture/Compare Modules                           |     |

| 16.2.1.Edge-triggered Capture Mode                     |     |

| 16.2.2.Software Timer (Compare) Mode                   |     |

| 16.2.3. High Speed Output Mode                         |     |

| 16.2.4. Frequency Output Mode                          | 101 |

| 16.2.5.8-Bit Pulse Width Modulator Mode                |     |

| 16.2.6.16-Bit Pulse Width Modulator Mode               |     |

| 16.3.Watchdog Timer Mode                               |     |

| 16.3.1.Watchdog Timer Operation                        |     |

| 16.3.2.Watchdog Timer Usage                            |     |

| 16.4.Register Descriptions for PCA                     |     |

| 17.C2 Interface                                        |     |

| 17.1.C2 Interface Registers                            |     |

| 17.2.C2 Pin Sharing                                    |     |

| Document Change List                                   |     |

| Contact Information                                    | 178 |

| Table 14.3. Timer Settings for Standard Baud Rates                        |

|---------------------------------------------------------------------------|

| Using an External 22.1184 MHz Oscillator 139                              |

| Table 14.4. Timer Settings for Standard Baud Rates                        |

| Using an External 18.432 MHz Oscillator 140                               |

| Table 14.5. Timer Settings for Standard Baud Rates                        |

| Using an External 11.0592 MHz Oscillator 141                              |

| Table 14.6. Timer Settings for Standard Baud Rates                        |

| Using an External 3.6864 MHZ Oscillator 142                               |

| 15. Timers                                                                |

| 16. Programmable Counter Array                                            |

| Table 16.1. PCA Timebase Input Options 156                                |

| Table 16.2. PCA0CPM Register Settings for PCA Capture/Compare Modules 157 |

| Table 16.3. Watchdog Timer Timeout Intervals 166                          |

| 17.C2 Interface                                                           |

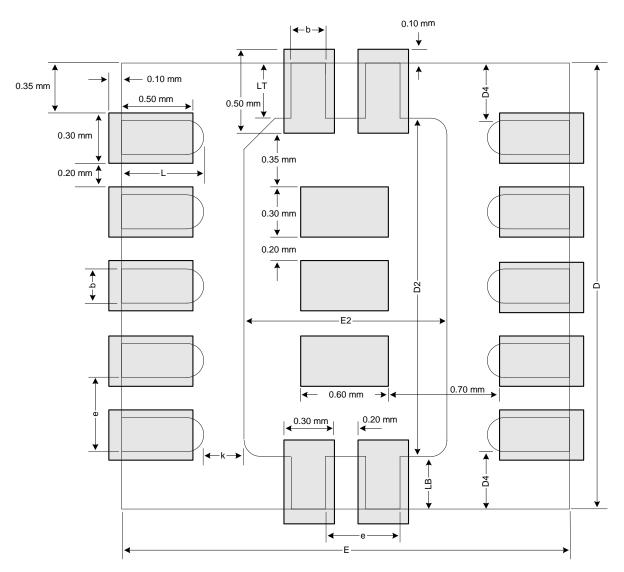

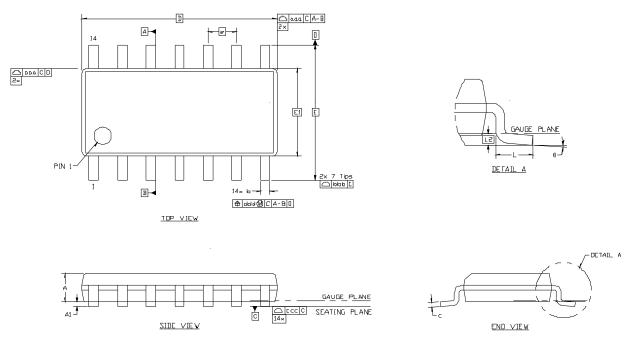

Figure 4.3. Typical QFN-11 Solder Paste Mask

Figure 4.6. SOIC-14 Package Drawing

| Dimension | Min       | Max  | Dimension | Min        | Max        |

|-----------|-----------|------|-----------|------------|------------|

| А         |           | 1.75 | L         | 0.40       | 1.27       |

| A1        | 0.10 0.25 |      | L2        | 0.25       | BSC        |

| b         | 0.33      | 0.51 | Q         | <b>0</b> ° | <b>8</b> ° |

| С         | 0.17 0.25 |      | aaa       | 0.10       |            |

| D         | 8.65 BSC  |      | bbb       | 0.:        | 20         |

| E         | 6.00 BSC  |      | CCC       | 0.         | 10         |

| E1        | 3.90 BSC  |      | ddd       | 0.:        | 25         |

| е         | 1.27      | BSC  | LL        |            |            |

| lotes:    |           |      |           |            |            |

Table 4.4. SOIC-14 Package Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS012, variation AB.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

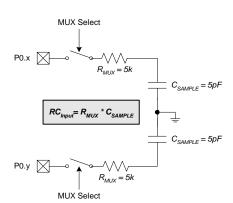

#### 5.3.3. Settling Time Requirements

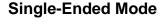

When the ADC0 input configuration is changed (i.e., a different AMUX0 or PGA selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time (track/hold time) requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

#### Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (8).

**Differential Mode**

Note: When the PGA gain is set to 0.5,  $C_{SAMPLE} = 3pF$

#### Figure 5.5. ADC0 Equivalent Input Circuits

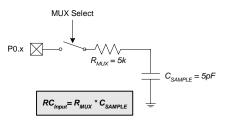

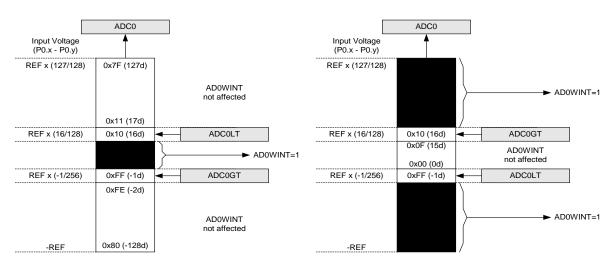

#### 5.4.2. Window Detector In Differential Mode

Figure 5.7 shows two example window comparisons for differential mode, with ADC0LT = 0x10 (+16d) and ADC0GT = 0xFF (-1d). Notice that in Differential mode, the codes vary from –VREF to VREF x (127/128) and are represented as 8-bit 2's complement signed integers. In the left example, an AD0WINT interrupt will be generated if the ADC0 conversion word (ADC0L) is within the range defined by ADC0GT and ADC0LT (if 0xFF (-1d) < ADC0 < 0x10 (16d)). In the right example, an AD0WINT interrupt will be generated if ADC0 is outside of the range defined by ADC0GT and ADC0LT (if ADC0 < 0xFF (-1d) or ADC0 > 0x10 (+16d)).

Figure 5.7. ADC Window Compare Examples, Differential Mode

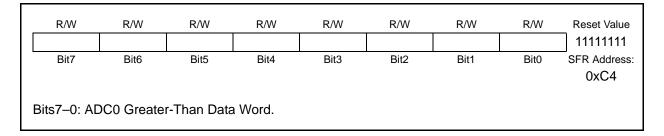

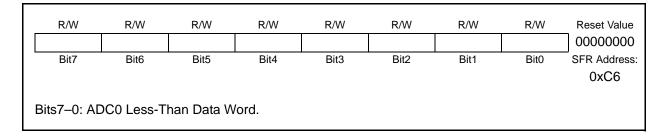

#### SFR Definition 5.5. ADC0GT: ADC0 Greater-Than Data Byte (C8051F300/2)

#### SFR Definition 5.6. ADC0LT: ADC0 Less-Than Data Byte (C8051F300/2)

# Table 7.1. Comparator0 Electrical Characteristics $V_{DD}$ = 3.0 V, -40 to +85 °C unless otherwise specified.

| Parameter                                         | Conditions                 | Min      | Тур   | Max                       | Units |

|---------------------------------------------------|----------------------------|----------|-------|---------------------------|-------|

| Response Time:                                    | CP0+ - CP0- = 100 mV       |          | 100   | —                         | ns    |

| Mode 0, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV      |          | 250   | —                         | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV       | _        | 175   | —                         | ns    |

| Mode 1, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV      | _        | 500   | —                         | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV       | _        | 320   | —                         | ns    |

| Mode 2, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV      |          | 1100  | —                         | ns    |

| Response Time:                                    | CP0+ - CP0- = 100 mV       |          | 1050  | —                         | ns    |

| Mode 3, Vcm* = 1.5 V                              | CP0+ - CP0- = -100 mV      |          | 5200  | —                         | ns    |

| Common-Mode Rejection<br>Ratio                    |                            | —        | 1.5   | 4                         | mV/V  |

| Positive Hysteresis 1                             | CP0HYP1-0 = 00             | _        | 0     | 1                         | mV    |

| Positive Hysteresis 2                             | CP0HYP1-0 = 01             | 3        | 5     | 7                         | mV    |

| Positive Hysteresis 3                             | CP0HYP1-0 = 10             | 7        | 10    | 15                        | mV    |

| Positive Hysteresis 4                             | CP0HYP1-0 = 11             | 15       | 20    | 25                        | mV    |

| Negative Hysteresis 1                             | CP0HYN1-0 = 00             |          | 0     | 1                         | mV    |

| Negative Hysteresis 2                             | CP0HYN1-0 = 01             | 3        | 5     | 7                         | mV    |

| Negative Hysteresis 3                             | CP0HYN1-0 = 10             | 7        | 10    | 15                        | mV    |

| Negative Hysteresis 4                             | CP0HYN1–0 = 11             | 15       | 20    | 25                        | mV    |

| Inverting or Non-Inverting<br>Input Voltage Range |                            | -0.25    |       | V <sub>DD</sub> +<br>0.25 | V     |

| Input Capacitance                                 |                            | —        | 7     | —                         | pF    |

| Input Bias Current                                |                            | -5       | 0.001 | +5                        | nA    |

| Input Offset Voltage                              |                            | -5       | —     | +5                        | mV    |

|                                                   | Power Supply               | <b>I</b> |       |                           |       |

| Power Supply Rejection                            |                            |          | 0.1   | 1                         | mV/V  |

| Power-up Time                                     |                            | —        | 10    | —                         | μs    |

|                                                   | Mode 0                     | —        | 7.6   | —                         | μA    |

| Supply Current at DC                              | Mode 1                     | —        | 3.2   | —                         | μA    |

|                                                   | Mode 2                     | —        | 1.3   | —                         | μA    |

|                                                   | Mode 3                     | —        | 0.4   | —                         | μA    |

| *Note: Vcm is the common-mo                       | de voltage on CP0+ and CP0 | 1        |       |                           |       |

NOTES:

| Mnemonic            | Description                                         | Bytes | Clock<br>Cycles |

|---------------------|-----------------------------------------------------|-------|-----------------|

| JNZ rel             | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel  | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel | Compare immediate to Register and jump if not equal | 3     | 3/4             |

Compare immediate to indirect and jump if not

Decrement Register and jump if not zero

Decrement direct byte and jump if not zero

3

2

3

1

4/5

2/3

3/4

1

#### Table 8.1. CIP-51 Instruction Set Summary (Continued)

Notes on Registers, Operands and Addressing Modes:

equal

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

No operation

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

CJNE @Ri, #data, rel

DJNZ Rn, rel

NOP

DJNZ direct, rel

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

#### 8.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 8.2 and Figure 8.3.

#### 8.2.1. Program Memory

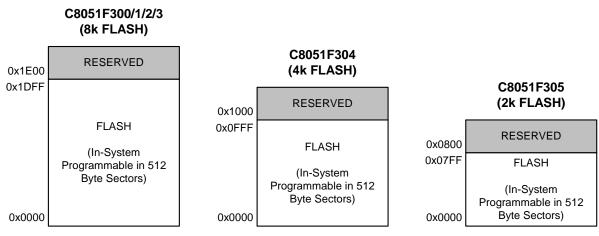

The CIP-51 core has a 64k-byte program memory space. The C8051F300/1/2/3 implements 8192 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Note: 512 bytes (0x1E00 - 0x1FFF) of this memory are reserved for factory use and are not available for user program storage. The C8051F304 implements 4096 bytes of reprogrammable Flash program memory space; the C8051F305 implements 2048 bytes of reprogrammable Flash program memory space. Figure 8.2 shows the program memory maps for C8051F300/1/2/3/4/5 devices.

Figure 8.2. Program Memory Maps

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 89** for further details.

| Register Address                                                       |                            | Address Description                                     |     |  |  |  |

|------------------------------------------------------------------------|----------------------------|---------------------------------------------------------|-----|--|--|--|

| TH1                                                                    | 0x8D                       | Timer/Counter 1 High                                    | 150 |  |  |  |

| TL0                                                                    | 0x8A                       | Timer/Counter 0 Low                                     | 150 |  |  |  |

| TL1                                                                    | 0x8B                       | Timer/Counter 1 Low                                     | 150 |  |  |  |

| TMOD                                                                   | 0x89                       | Timer/Counter Mode                                      | 148 |  |  |  |

| TMR2RLH                                                                | 0xCB                       | Timer/Counter 2 Reload High                             | 154 |  |  |  |

| TMR2RLL                                                                | 0xCA                       | Timer/Counter 2 Reload Low                              | 154 |  |  |  |

| TMR2H                                                                  | 0xCD                       | Timer/Counter 2 High                                    | 154 |  |  |  |

| TMR2L                                                                  | 0xCC                       | Timer/Counter 2 Low                                     | 154 |  |  |  |

| XBR0                                                                   | 0xE1                       | Port I/O Crossbar Control 0                             | 107 |  |  |  |

| XBR1                                                                   | 0xE2                       | Port I/O Crossbar Control 1                             | 107 |  |  |  |

| XBR2                                                                   | 0xE3                       | Port I/O Crossbar Control 2                             | 108 |  |  |  |

| 0x97, 0xAE, (<br>0xB6, 0xBF, (<br>0xD3, 0xD4, (<br>0xD7, 0xDD,<br>0xF5 | 0xCE, 0xD2,<br>0xD5, 0xD6, | Reserved                                                |     |  |  |  |

| *Note: SFRs a                                                          | are listed in alpha        | betical order. All undefined SFR locations are reserved |     |  |  |  |

#### 8.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

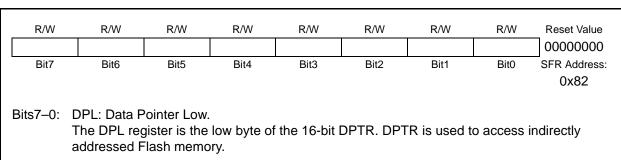

#### SFR Definition 8.1. DPL: Data Pointer Low Byte

|       |            |       | Definition  | 10.5. AO     | O. Accu    | Indiator |             |              |

|-------|------------|-------|-------------|--------------|------------|----------|-------------|--------------|

| R/W   | R/W        | R/W   | R/W         | R/W          | R/W        | R/W      | R/W         | Reset Value  |

| ACC.7 | ACC.6      | ACC.5 | ACC.4       | ACC.3        | ACC.2      | ACC.1    | ACC.0       | 00000000     |

| Bit7  | Bit6       | Bit5  | Bit4        | Bit3         | Bit2       | Bit1     | Bit0        | SFR Address: |

|       |            |       |             |              |            | (bit     | addressable | e) 0xE0      |

|       | ACC: Accur |       | umulator fo | r arithmetic | operations |          |             |              |

### SFR Definition 8.5. ACC: Accumulator

### SFR Definition 8.6. B: B Register

|    | R/W    | R/W                           | R/W  | R/W        | R/W        | R/W           | R/W          | R/W            | Reset Value  |

|----|--------|-------------------------------|------|------------|------------|---------------|--------------|----------------|--------------|

|    | B.7    | B.6                           | B.5  | B.4        | B.3        | B.2           | B.1          | B.0            | 0000000      |

|    | Bit7   | Bit6                          | Bit5 | Bit4       | Bit3       | Bit2          | Bit1         | Bit0           | SFR Address: |

|    |        |                               |      |            |            |               | (bi          | t addressable) | 0xF0         |

| Bi | ts7–0: | B: B Registe<br>This register |      | a second a | ccumulator | for certain a | arithmetic o | operations.    |              |

#### 8.3.5. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

| R/W   | R/W                                                                                                | R/W                                                                                                                 | R/W      | R/W            | R/W         | R/W      | R/W           | Reset Value  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------|----------------|-------------|----------|---------------|--------------|--|--|--|

| EA    | IEGF0                                                                                              | ET2                                                                                                                 | ES0      | ET1            | EX1         | ET0      | EX0           | 00000000     |  |  |  |

| Bit7  | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Addre                                                       |                                                                                                                     |          |                |             |          |               | SFR Address: |  |  |  |

|       |                                                                                                    |                                                                                                                     |          |                |             | (bi      | t addressable | e) 0xA8      |  |  |  |

|       |                                                                                                    |                                                                                                                     |          |                |             |          |               |              |  |  |  |

| Bit7: | EA: Enable All Interrupts.                                                                         |                                                                                                                     |          |                |             |          |               |              |  |  |  |

|       | This bit globally enables/disables all interrupts. It overrides the individual interrupt mask set- |                                                                                                                     |          |                |             |          |               |              |  |  |  |

|       | tings.                                                                                             |                                                                                                                     |          |                |             |          |               |              |  |  |  |

|       | 0: Disable a                                                                                       |                                                                                                                     |          | 1. 10. 1. P. 1 |             |          |               |              |  |  |  |

| D'10  | 1: Enable ea                                                                                       |                                                                                                                     |          | to its indivi  | dual mask   | setting. |               |              |  |  |  |

| Bit6: | IEGF0: Gen                                                                                         | •                                                                                                                   | •        |                | -           | 440      |               |              |  |  |  |

| Bit5: | This is a ger<br>ET2: Enable                                                                       |                                                                                                                     |          | use under s    | onware con  | III OI.  |               |              |  |  |  |

| DIG.  | This bit sets                                                                                      |                                                                                                                     |          | mor 2 interr   | unt         |          |               |              |  |  |  |

|       | 0: Disable T                                                                                       |                                                                                                                     |          |                | սբւ.        |          |               |              |  |  |  |

|       | 1: Enable in                                                                                       |                                                                                                                     |          | ated by the    | TE2L or TE  | 2H flags |               |              |  |  |  |

| Bit4: | ES0: Enable                                                                                        |                                                                                                                     | •        |                |             | Linago   |               |              |  |  |  |

| 2     | This bit sets                                                                                      |                                                                                                                     |          | ART0 interro   | upt.        |          |               |              |  |  |  |

|       | 0: Disable U                                                                                       |                                                                                                                     | •        |                |             |          |               |              |  |  |  |

|       | 1: Enable U                                                                                        |                                                                                                                     | •        |                |             |          |               |              |  |  |  |

| Bit3: | ET1: Enable                                                                                        | Timer 1 In                                                                                                          | terrupt. |                |             |          |               |              |  |  |  |

|       | This bit sets                                                                                      |                                                                                                                     |          | ner 1 interr   | upt.        |          |               |              |  |  |  |

|       | 0: Disable a                                                                                       |                                                                                                                     |          |                |             |          |               |              |  |  |  |

|       | 1: Enable in                                                                                       |                                                                                                                     | •        | ated by the    | TF1 flag.   |          |               |              |  |  |  |

| Bit2: | EX1: Enable                                                                                        |                                                                                                                     | •        |                |             |          |               |              |  |  |  |

|       | This bit sets                                                                                      |                                                                                                                     |          | al interrupt   | 1.          |          |               |              |  |  |  |

|       | 0: Disable e                                                                                       |                                                                                                                     |          |                |             |          |               |              |  |  |  |

| Bit1: | 1: Enable in                                                                                       |                                                                                                                     |          | ated by the    |             | [.       |               |              |  |  |  |

| DILI. | ET0: Enable<br>This bit sets                                                                       |                                                                                                                     | •        | nor () intorr  | unt         |          |               |              |  |  |  |

|       |                                                                                                    |                                                                                                                     |          |                | սբւ.        |          |               |              |  |  |  |

|       |                                                                                                    | <ul><li>0: Disable all Timer 0 interrupt.</li><li>1: Enable interrupt requests generated by the TF0 flag.</li></ul> |          |                |             |          |               |              |  |  |  |

| Bit0: | EX0: Enable                                                                                        |                                                                                                                     | •        |                | n o nag.    |          |               |              |  |  |  |

| 2.101 | This bit sets                                                                                      |                                                                                                                     | •        | al interrupt   | 0.          |          |               |              |  |  |  |

|       | 0: Disable e                                                                                       |                                                                                                                     | •        |                |             |          |               |              |  |  |  |

|       | 1: Enable in                                                                                       |                                                                                                                     |          | ated by the    | /INT0 input | t.       |               |              |  |  |  |

|       |                                                                                                    |                                                                                                                     |          |                |             |          |               |              |  |  |  |

|       |                                                                                                    |                                                                                                                     |          |                |             |          |               |              |  |  |  |

#### SFR Definition 8.7. IE: Interrupt Enable

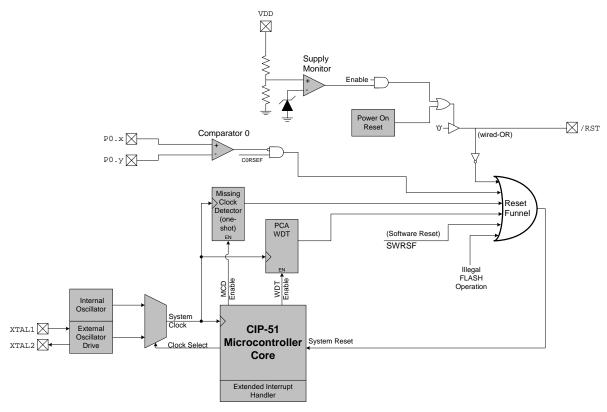

#### 9. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to **Section "11. Oscillators" on page 97** for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (**Section "16.3. Watchdog Timer Mode" on page 164** details the use of the Watchdog Timer). Once the system clock source is stable, program execution begins at location 0x0000.

Figure 9.1. Reset Sources

#### 9.7. Flash Error Reset

If a Flash read/write/erase or program read targets an illegal address, a system reset is generated. This may occur due to any of the following:

- A Flash write or erase is attempted above user code space. This occurs when PSWE is set to '1' and a MOVX operation is attempted above the user code space address limit.

- A Flash read is attempted above user code space. This occurs when a MOVC operation is attempted above the user code space address limit.

- A Program read is attempted above user code space. This occurs when user code attempts to branch to an address above the user code space address limit.

| Device          | User Code Space Address Limit |

|-----------------|-------------------------------|

| C8051F300/1/2/3 | 0x1DFF                        |

| C8051F304       | 0x0FFF                        |

| C8051F305       | 0x07FF                        |

Table 9.1. User Code Space Address Limits

The FERROR bit (RSTSRC.6) is set following a Flash error reset. The state of the  $\overline{RST}$  pin is unaffected by this reset.

#### 9.8. Software Reset

Software may force a reset by writing a '1' to the SWRSF bit (RSTSRC.4). The SWRSF bit will read '1' following a software forced reset. The state of the RST pin is unaffected by this reset.

#### Table 9.2. Reset Electrical Characteristics

-40 to +85 °C unless otherwise specified.

| Parameter                                          | Conditions                                                                            | Min                         | Тур  | Max                 | Units |

|----------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|------|---------------------|-------|

| RST Output Low Voltage                             | $I_{OL} = 8.5 \text{ mA}, V_{DD} = 2.7 \text{ V to}$<br>3.6 V                         | —                           | _    | 0.6                 | V     |

| RST Input High Voltage                             |                                                                                       | $0.7 	ext{ x V}_{	ext{DD}}$ |      | _                   | V     |

| RST Input Low Voltage                              |                                                                                       | _                           |      | $0.3 \times V_{DD}$ |       |

| RST Input Leakage Current                          | RST = 0.0 V                                                                           | —                           | 25   | 40                  | μA    |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )           |                                                                                       | 2.40                        | 2.55 | 2.70                | V     |

| Missing Clock Detector Timeout                     | Time from last system clock ris-<br>ing edge to reset initiation                      | 100                         | 220  | 500                 | μs    |

| Reset Time Delay                                   | Delay between release of any<br>reset source and code execution<br>at location 0x0000 | 5.0                         | _    | _                   | μs    |

| Minimum RST Low Time to<br>Generate a System Reset |                                                                                       | 15                          | _    | —                   | μs    |

| V <sub>DD</sub> Ramp Time                          | $V_{DD} = 0$ to $V_{RST}$                                                             |                             |      | 1                   | ms    |

#### 13.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification Version 1.1, SBS Implementers Forum.

#### **13.2. SMBus Configuration**

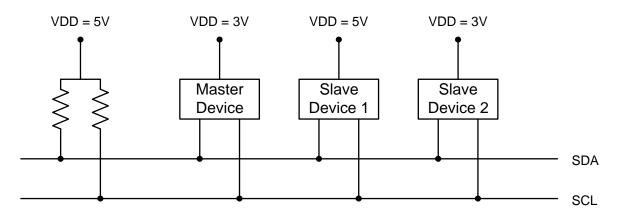

Figure 13.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 and 5.0 V; different devices on the bus may operate at different voltage levels. The bidirectional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

#### Figure 13.2. Typical SMBus Configuration

#### 13.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device that transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 13.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

#### 13.4. Using the SMBus

The SMBus can operate in both Master and Slave modes. The interface provides timing and shifting control for serial transfers; higher level protocol is determined by user software. The SMBus interface provides the following application-independent features:

- Byte-wise serial data transfers

- Clock signal generation on SCL (Master Mode only) and SDA data synchronization

- Timeout/bus error recognition, as defined by the SMB0CF configuration register

- START/STOP timing, detection, and generation

- Bus arbitration

- Interrupt generation

- Status information

SMBus interrupts are generated for each data byte or slave address that is transferred. When transmitting, this interrupt is generated after the ACK cycle so that software may read the received ACK value; when receiving data, this interrupt is generated before the ACK cycle so that software may define the outgoing ACK value. See **Section "13.5. SMBus Transfer Modes" on page 123** for more details on transmission sequences.

Interrupts are also generated to indicate the beginning of a transfer when a master (START generated), or the end of a transfer when a slave (STOP detected). Software should read the SMB0CN (SMBus Control register) to find the cause of the SMBus interrupt. The SMB0CN register is described in **Section "13.4.2. SMB0CN Control Register" on page 119**; Table 13.4 provides a quick SMB0CN decoding reference.

SMBus configuration options include:

- Timeout detection (SCL Low Timeout and/or Bus Free Timeout)

- SDA setup and hold time extensions

- Slave event enable/disable

- Clock source selection

These options are selected in the SMB0CF register, as described in **Section "13.4.1. SMBus Configura**tion Register" on page 116.

| Frequency: 11.0592 MHz       |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                   |                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error                                                                                                                                                                                                                                                                                                                      | Oscillator<br>Divide<br>Factor                                                                                                                    | Timer Clock<br>Source                                                                                                                                                                                                         | SCA1-SCA0<br>(pre-scale<br>select) <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T1M <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Timer 1<br>Reload<br>Value (hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 230400                       | 0.00%                                                                                                                                                                                                                                                                                                                                     | 48                                                                                                                                                | SYSCLK                                                                                                                                                                                                                        | XX <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0xE8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 115200                       | 0.00%                                                                                                                                                                                                                                                                                                                                     | 96                                                                                                                                                | SYSCLK                                                                                                                                                                                                                        | XX <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0xD0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 57600                        | 0.00%                                                                                                                                                                                                                                                                                                                                     | 192                                                                                                                                               | SYSCLK                                                                                                                                                                                                                        | XX <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0xA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28800                        | 0.00%                                                                                                                                                                                                                                                                                                                                     | 384                                                                                                                                               | SYSCLK                                                                                                                                                                                                                        | XX <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 14400                        | 0.00%                                                                                                                                                                                                                                                                                                                                     | 768                                                                                                                                               | SYSCLK / 12                                                                                                                                                                                                                   | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0xE0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |