Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 4KB (4K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 10-VFDFN Exposed Pad                                           |

| Supplier Device Package    | 11-QFN (3x3)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f304-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 13.4.Using the SMBus                                   | 115 |

|--------------------------------------------------------|-----|

| 13.4.1.SMBus Configuration Register                    |     |

| 13.4.2.SMB0CN Control Register                         |     |

| 13.4.3.Data Register                                   |     |

| 13.5.SMBus Transfer Modes                              |     |

| 13.5.1.Master Transmitter Mode                         |     |

| 13.5.2.Master Receiver Mode                            |     |

| 13.5.3.Slave Receiver Mode                             |     |

| 13.5.4.Slave Transmitter Mode                          |     |

|                                                        |     |

| 13.6.SMBus Status Decoding                             |     |

| 14.1.Enhanced Baud Rate Generation                     |     |

|                                                        |     |

| 14.2.Operational Modes<br>14.2.1.8-Bit UART            |     |

| 14.2.1.о-ын UART<br>14.2.2.9-Bit UART                  |     |

| 14.2.2.9-Bit OART                                      |     |

| •                                                      |     |

| 15.1.Timer 0 and Timer 1                               |     |

| 15.1.1.Mode 0: 13-bit Counter/Timer                    |     |

|                                                        |     |

| 15.1.2.Mode 1: 16-bit Counter/Timer                    |     |

| 15.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 15.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

| 15.2.Timer 2<br>15.2.1.16-bit Timer with Auto-Reload   |     |

|                                                        |     |

| 15.2.2.8-bit Timers with Auto-Reload                   |     |

| 16. Programmable Counter Array                         |     |

| 16.1.PCA Counter/Timer                                 |     |

| 16.2.Capture/Compare Modules                           |     |

| 16.2.1.Edge-triggered Capture Mode                     |     |

| 16.2.2.Software Timer (Compare) Mode                   |     |

| 16.2.3. High Speed Output Mode                         |     |

| 16.2.4. Frequency Output Mode                          | 101 |

| 16.2.5.8-Bit Pulse Width Modulator Mode                |     |

| 16.2.6.16-Bit Pulse Width Modulator Mode               |     |

| 16.3.Watchdog Timer Mode                               |     |

| 16.3.1.Watchdog Timer Operation                        |     |

| 16.3.2.Watchdog Timer Usage                            |     |

| 16.4.Register Descriptions for PCA                     |     |

| 17.C2 Interface                                        |     |

| 17.1.C2 Interface Registers                            |     |

| 17.2.C2 Pin Sharing                                    |     |

| Document Change List                                   |     |

| Contact Information                                    | 178 |

## List of Figures

| 1. | System Overview                                                               |            |

|----|-------------------------------------------------------------------------------|------------|

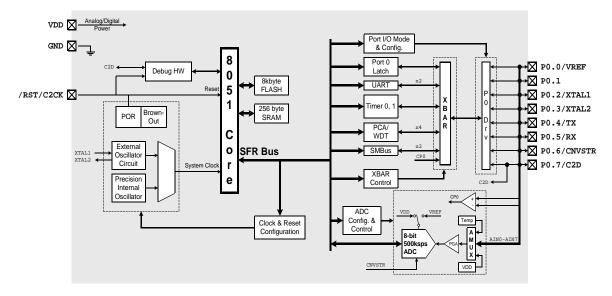

|    | Figure 1.1. C8051F300/2 Block Diagram                                         | 15         |

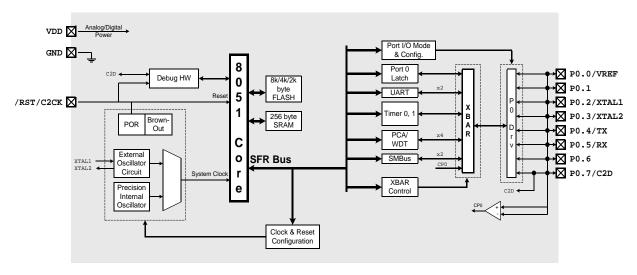

|    | Figure 1.2. C8051F301/3/4/5 Block Diagram                                     | 15         |

|    | Figure 1.3. Comparison of Peak MCU Execution Speeds                           | 16         |

|    | Figure 1.4. On-Chip Clock and Reset                                           | 17         |

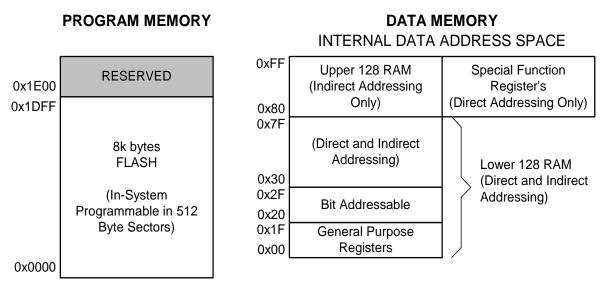

|    | Figure 1.5. On-chip Memory Map (C8051F300/1/2/3 Shown)                        | 18         |

|    | Figure 1.6. Development/In-System Debug Diagram                               | 19         |

|    | Figure 1.7. Digital Crossbar Diagram                                          | 20         |

|    | Figure 1.8. PCA Block Diagram                                                 | 21         |

|    | Figure 1.9. PCA Block Diagram                                                 |            |

|    | Figure 1.10. 8-Bit ADC Block Diagram                                          |            |

|    | Figure 1.11. Comparator Block Diagram                                         | 23         |

| 2. | Absolute Maximum Ratings                                                      |            |

|    | Global Electrical Characteristics                                             |            |

| 4. | Pinout and Package Definitions                                                |            |

|    | Figure 4.1. QFN-11 Pinout Diagram (Top View)                                  |            |

|    | Figure 4.2. QFN-11 Package Drawing                                            |            |

|    | Figure 4.3. Typical QFN-11 Solder Paste Mask                                  |            |

|    | Figure 4.4. Typical QFN-11 Landing Diagram                                    | 31         |

|    | Figure 4.5. SOIC-14 Pinout Diagram (Top View)                                 |            |

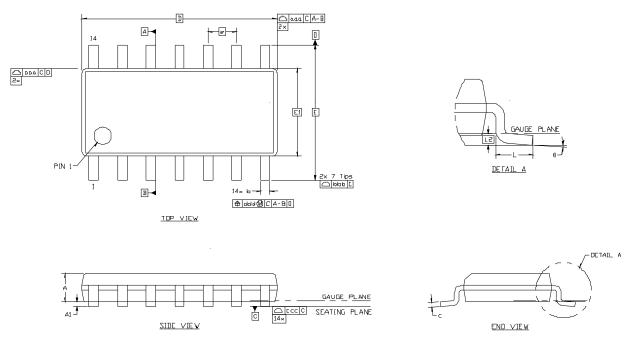

|    | Figure 4.6. SOIC-14 Package Drawing                                           |            |

| _  | Figure 4.7. SOIC-14 PCB Land Pattern                                          | 34         |

| 5. | ADC0 (8-Bit ADC, C8051F300/2)                                                 |            |

|    | Figure 5.1. ADC0 Functional Block Diagram                                     |            |

|    | Figure 5.2. Typical Temperature Sensor Transfer Function                      |            |

|    | Figure 5.3. Temperature Sensor Error with 1-Point Calibration (VREF = 2.40 V) |            |

|    | Figure 5.4. 8-Bit ADC Track and Conversion Example Timing                     |            |

|    | Figure 5.5. ADC0 Equivalent Input Circuits                                    |            |

|    | Figure 5.6. ADC Window Compare Examples, Single-Ended Mode                    |            |

| ~  | Figure 5.7. ADC Window Compare Examples, Differential Mode                    | 46         |

| 6. | Voltage Reference (C8051F300/2)                                               | 40         |

| -  | Figure 6.1. Voltage Reference Functional Block Diagram                        | 49         |

| 1. | Comparator0                                                                   | <b>Г</b> 4 |

|    | Figure 7.1. Comparator0 Functional Block Diagram                              |            |

| •  | Figure 7.2. Comparator Hysteresis Plot                                        | 52         |

| 8. | CIP-51 Microcontroller                                                        | 57         |

|    | Figure 8.1. CIP-51 Block Diagram                                              |            |

|    | Figure 8.2. Program Memory Maps                                               |            |

| •  | Figure 8.3. Data Memory Map                                                   | 04         |

| 9. | Reset Sources                                                                 | റ          |

|    | Figure 9.1. Reset Sources                                                     |            |

|    | Figure 9.2. Power-On and VDD Monitor Reset Timing                             | 04         |

## C8051F300/1/2/3/4/5

| Ordering Part Number | MIPS (Peak) | Flash Memory | RAM | Calibrated Internal Oscillator | SMBus/I <sup>2</sup> C | UART         | Timers (16-bit) | Programmable Counter Array | Digital Port I/Os | 8-bit 500ksps ADC | Temperature Sensor | Analog Comparators | Lead-free (RoHS compliant) | Package |

|----------------------|-------------|--------------|-----|--------------------------------|------------------------|--------------|-----------------|----------------------------|-------------------|-------------------|--------------------|--------------------|----------------------------|---------|

| C8051F300-GM         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | QFN-11  |

| C8051F300-GS         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | ~                 | $\checkmark$       | 1                  | ~                          | SOIC-14 |

| C8051F301-GM         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | $\checkmark$               | 8                 | —                 |                    | 1                  | $\checkmark$               | QFN-11  |

| C8051F301-GS         | 25          | 8 k          | 256 | $\checkmark$                   | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | SOIC-14 |

| C8051F302-GM         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | QFN-11  |

| C8051F302-GS         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | $\checkmark$      | $\checkmark$       | 1                  | ~                          | SOIC-14 |

| C8051F303-GM         | 25          | 8 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | QFN-11  |

| C8051F303-GS         | 25          | 8 k          | 256 |                                | ~                      | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | SOIC-14 |

| C8051F304-GM         | 25          | 4 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | —                 |                    | 1                  | ~                          | QFN-11  |

| C8051F304-GS         | 25          | 4 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 | —                 | _                  | 1                  | ~                          | SOIC-14 |

| C8051F305-GM         | 25          | 2 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | ~                          | 8                 |                   |                    | 1                  | ~                          | QFN-11  |

| C8051F305-GS         | 25          | 2 k          | 256 |                                | $\checkmark$           | $\checkmark$ | 3               | $\checkmark$               | 8                 |                   |                    | 1                  | $\checkmark$               | SOIC-14 |

Table 1.1. Product Selection Guide

## C8051F300/1/2/3/4/5

Figure 1.1. C8051F300/2 Block Diagram

Figure 1.2. C8051F301/3/4/5 Block Diagram

### 1.2. On-Chip Memory

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

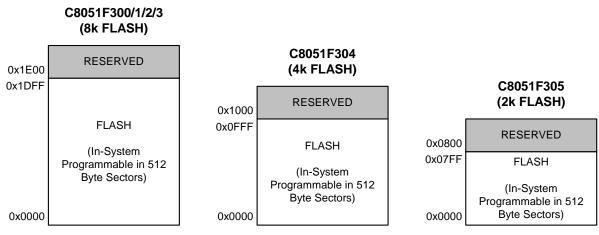

The C8051F300/1/2/3 includes 8k bytes of Flash program memory (the C8051F304 includes 4k bytes; the C8051F305 includes 2k bytes). This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.5 for the C8051F300/1/2/3 system memory map.

Figure 1.5. On-chip Memory Map (C8051F300/1/2/3 Shown)

### Table 3.1. Global Electrical Characteristics (Continued)

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                       | Conditions                                                  | Min | Тур   | Max | Units  |

|-------------------------------------------------|-------------------------------------------------------------|-----|-------|-----|--------|

| I <sub>DD</sub> Supply Sensitivity (Note 3)     | F = 25 MHz                                                  | _   | 47    | _   | %/V    |

|                                                 | F = 1 MHz                                                   | —   | 59    | —   | %/V    |

| I <sub>DD</sub> Frequency Sensitivity           | V <sub>DD</sub> = 3.0 V, F <= 1 MHz, T = 25 °C              | _   | 0.27  |     | mA/MHz |

| (Note 3, Note 5)                                | V <sub>DD</sub> = 3.0 V, F > 1 MHz, T = 25 °C               | _   | 0.10  | _   | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F <= 1 MHz, T = 25 ℃               | —   | 0.35  | —   | mA/MHz |

|                                                 | V <sub>DD</sub> = 3.6 V, F > 1 MHz, T = 25 °C               | —   | 0.12  | _   | mA/MHz |

| Digital Supply Current<br>(Stop Mode, shutdown) | Oscillator not running,<br>V <sub>DD</sub> Monitor Disabled | —   | < 0.1 | —   | μA     |

### Notes:

- 1. Given in Table 9.2 on page 86.

- 2. SYSCLK must be at least 32 kHz to enable debugging.

- 3. Based on device characterization data; Not production tested.

- 4. Normal IDD can be estimated for frequencies <= 15 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate I<sub>DD</sub> for >15 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 3.0 V; F = 20 MHz,  $I_{DD}$  = 6.6 mA – (25 MHz – 20 MHz) x 0.16 mA/MHz = 5.8 mA.

5. Idle IDD can be estimated for frequencies <= 1 MHz by simply multiplying the frequency of interest by the frequency sensitivity number for that range. When using these numbers to estimate Idle I<sub>DD</sub> for >1 MHz, the estimate should be the current at 25 MHz minus the difference in current indicated by the frequency sensitivity number.

For example:  $V_{DD}$  = 3.0 V; F = 5 MHz, Idle I<sub>DD</sub> = 3.3 mA – (25 MHz – 5 MHz) x 0.10 mA/MHz = 1.3 mA.

## C8051F300/1/2/3/4/5

Figure 4.6. SOIC-14 Package Drawing

| Dimension | Min  | Max  | Dimension | Min        | Max        |  |

|-----------|------|------|-----------|------------|------------|--|

| А         |      | 1.75 | L         | 0.40       | 1.27       |  |

| A1        | 0.10 | 0.25 | L2        | 0.25       | BSC        |  |

| b         | 0.33 | 0.51 | Q         | <b>0</b> ° | <b>8</b> ° |  |

| С         | 0.17 | 0.25 | aaa       | 0.         | 10         |  |

| D         | 8.65 | BSC  | bbb       | 0.20       |            |  |

| E         | 6.00 | BSC  | CCC       | 0.10       |            |  |

| E1        | 3.90 | BSC  | ddd       | 0.25       |            |  |

| е         | 1.27 | BSC  | LL        |            |            |  |

| lotes:    |      |      |           |            |            |  |

Table 4.4. SOIC-14 Package Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS012, variation AB.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

### 5. ADC0 (8-Bit ADC, C8051F300/2)

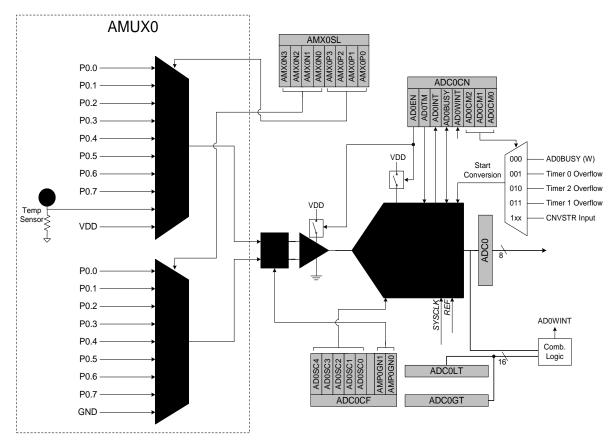

The ADC0 subsystem for the C8051F300/2 consists of two analog multiplexers (referred to collectively as AMUX0) with 11 total input selections, a differential programmable gain amplifier (PGA), and a 500 ksps, 8-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector (see block diagram in Figure 5.1). The AMUX0, PGA, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure any Port pin, the Temperature Sensor output, or  $V_{DD}$  with respect to any Port pin or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

Figure 5.1. ADC0 Functional Block Diagram

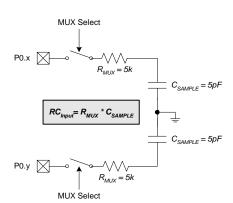

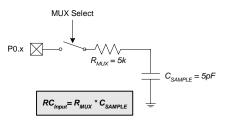

### 5.3.3. Settling Time Requirements

When the ADC0 input configuration is changed (i.e., a different AMUX0 or PGA selection is made), a minimum tracking time is required before an accurate conversion can be performed. This tracking time is determined by the AMUX0 resistance, the ADC0 sampling capacitance, any external source resistance, and the accuracy required for the conversion. Note that in low-power tracking mode, three SAR clocks are used for tracking at the start of every conversion. For most applications, these three SAR clocks will meet the minimum tracking time requirements.

Figure 5.5 shows the equivalent ADC0 input circuits for both Differential and Single-ended modes. Notice that the equivalent time constant for both input circuits is the same. The required ADC0 settling time for a given settling accuracy (SA) may be approximated by Equation 5.1. When measuring the Temperature Sensor output or  $V_{DD}$  with respect to GND,  $R_{TOTAL}$  reduces to  $R_{MUX}$ . See Table 5.1 for ADC0 minimum settling time (track/hold time) requirements.

$$t = \ln\left(\frac{2^n}{SA}\right) \times R_{TOTAL} C_{SAMPLE}$$

### Equation 5.1. ADC0 Settling Time Requirements

Where:

SA is the settling accuracy, given as a fraction of an LSB (for example, 0.25 to settle within 1/4 LSB) *t* is the required settling time in seconds

$R_{TOTAL}$  is the sum of the AMUX0 resistance and any external source resistance.

*n* is the ADC resolution in bits (8).

**Differential Mode**

Note: When the PGA gain is set to 0.5,  $C_{SAMPLE} = 3pF$

### Figure 5.5. ADC0 Equivalent Input Circuits

### Table 5.1. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                                                                                                              | Conditions                         | Min     | Тур       | Мах      | Units   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|-----------|----------|---------|

| DC Accuracy                                                                                                                                            |                                    |         |           |          |         |

| Resolution                                                                                                                                             |                                    |         | 8         |          | bits    |

| Integral Nonlinearity                                                                                                                                  |                                    | —       | ±0.5      | ±1       | LSB     |

| Differential Nonlinearity                                                                                                                              | Guaranteed Monotonic               | —       | ±0.5      | ±1       | LSB     |

| Offset Error                                                                                                                                           |                                    | -5.0    | 0.5       | 5.0      | LSB     |

| Full Scale Error                                                                                                                                       | Differential mode                  | -5.0    | -1        | 5.0      | LSB     |

| Dynamic Performance (10 kHz                                                                                                                            | Sine-wave Differential Input, 1    | dB belo | w Full Sc | ale, 500 | ksps)   |

| Signal-to-Noise Plus Distortion                                                                                                                        |                                    | 45      | 48        | —        | dB      |

| Total Harmonic Distortion                                                                                                                              | Up to the 5 <sup>th</sup> harmonic |         | -56       | —        | dB      |

| Spurious-Free Dynamic Range                                                                                                                            |                                    |         | 58        | —        | dB      |

| Conversion Rate                                                                                                                                        |                                    |         |           |          |         |

| SAR Conversion Clock                                                                                                                                   |                                    | —       |           | 6        | MHz     |

| Conversion Time in SAR Clocks                                                                                                                          |                                    | 11      |           | —        | clocks  |

| Track/Hold Acquisition Time                                                                                                                            |                                    | 300     |           | —        | ns      |

| Throughput Rate                                                                                                                                        |                                    | —       | —         | 500      | ksps    |

| Analog Inputs                                                                                                                                          |                                    |         | 1         |          |         |

| Input Voltage Range                                                                                                                                    |                                    | 0       | —         | VREF     | V       |

| Input Capacitance                                                                                                                                      |                                    | —       | 5         | —        | pF      |

| Temperature Sensor                                                                                                                                     |                                    | —       | _         | —        |         |

| Linearity <sup>1,2,3</sup>                                                                                                                             |                                    | —       | ±0.5      | —        | °C      |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    | —       | 3350      | —        | μV / °C |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    |         | ±110      |          |         |

| Offset <sup>1,2,3</sup>                                                                                                                                | (Temp = 0 °C)                      |         | 897±31    | —        | mV      |

| Power Specifications                                                                                                                                   |                                    |         |           |          |         |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0)                                                                                             | Operating Mode, 500 ksps           | —       | 400       | 900      | μA      |

| Power Supply Rejection                                                                                                                                 |                                    | —       | ±0.3      | —        | mV/V    |

| <ul> <li>Notes:</li> <li>1. Represents one standard devi</li> <li>2. Measured with PGA Gain = 2.</li> <li>3. Includes ADC offset, gain, and</li> </ul> |                                    |         |           |          |         |

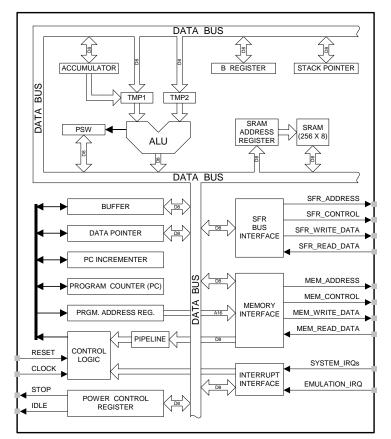

### 8. CIP-51 Microcontroller

The MCU system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The MCU family has a superset of all the peripherals included with a standard 8051. Included are three 16-bit counter/timers (see description in **Section 15**), an enhanced full-duplex UART (see description in **Section 14**), 256 bytes of internal RAM, 128 byte Special Function Register (SFR) address space (**Section 8.2.6**), and one byte-wide I/O Port (see description in **Section 12**). The CIP-51 also includes on-chip debug hardware (see description in **Section 17**), and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 Microcontroller core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 8.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 25 MIPS Peak Throughput with 25 MHz Clock

- 0 to 25 MHz Clock Frequency

- 256 Bytes of Internal RAM

- Byte-Wide I/O Port

- Extended Interrupt Handler

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

Figure 8.1. CIP-51 Block Diagram

### 8.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The CIP-51 memory organization is shown in Figure 8.2 and Figure 8.3.

### 8.2.1. Program Memory

The CIP-51 core has a 64k-byte program memory space. The C8051F300/1/2/3 implements 8192 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Note: 512 bytes (0x1E00 - 0x1FFF) of this memory are reserved for factory use and are not available for user program storage. The C8051F304 implements 4096 bytes of reprogrammable Flash program memory space; the C8051F305 implements 2048 bytes of reprogrammable Flash program memory space. Figure 8.2 shows the program memory maps for C8051F300/1/2/3/4/5 devices.

Figure 8.2. Program Memory Maps

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 89** for further details.

### 8.3.2. External Interrupts

The /INT0 and /INT1 external interrupt sources are configurable as active high or low, edge or level sensitive. The IN0PL (/INT0 Polarity) and IN1PL (/INT1 Polarity) bits in the IT01CF register select active high or active low; the IT0 and IT1 bits in TCON (**Section "15.1. Timer 0 and Timer 1" on page 143**) select level or edge sensitive. The table below lists the possible configurations.

| IT0 | IN0PL | /INT0 Interrupt              |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

/INT0 and /INT1 are assigned to Port pins as defined in the IT01CF register (see SFR Definition 8.11). Note that /INT0 and /INT0 Port pin assignments are independent of any Crossbar assignments. /INT0 and /INT1 will monitor their assigned Port pins without disturbing the peripheral that was assigned the Port pin via the Crossbar. To assign a Port pin only to /INT0 and/or /INT1, configure the Crossbar to skip the selected pin(s). This is accomplished by setting the associated bit in register XBR0 (see **Section** "**12.1. Priority Crossbar Decoder**" on page **104** for complete details on configuring the Crossbar).

IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flags for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag remains logic 1 while the input is active as defined by the corresponding polarity bit (IN0PL or IN1PL); the flag remains logic 0 while the input is inactive. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

### 8.3.3. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP or EIP1) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate, given in Table 8.4.

### 8.3.4. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                             | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|-------------------------------|---------------------|-------------------|------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                         | 0x0000              | Тор               | None                                     | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (/INT0)  | 0x0003              | 0                 | IE0 (TCON.1)                             | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                             | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (/INT1)  | 0x0013              | 2                 | IE1 (TCON.3)                             | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                             | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                         | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)           | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H<br>(TMR2CN.7)<br>TF2L<br>(TMR2CN.6) | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SMBus Interface               | 0x0033              | 6                 | SI (SMB0CN.0)                            | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Compare           | 0x003B              | 7                 | AD0WINT<br>(ADC0CN.3)                    | Y                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion Com-<br>plete | 0x0043              | 8                 | AD0INT<br>(ADC0CN.5)                     | Y                | N              | EADC0C<br>(EIE1.2) | PADC0C<br>(EIP1.2)  |

| Programmable Counter<br>Array | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn<br>(PCA0CN.n)      | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0 Falling Edge      | 0x0053              | 10                | CP0FIF<br>(CPT0CN.4)                     | N                | N              | ECP0F<br>(EIE1.4)  | PCP0F<br>(EIP1.4)   |

| Comparator0 Rising Edge       | 0x005B              | 11                | CP0RIF<br>(CPT0CN.5)                     | N                | N              | ECP0R<br>(EIE1.5)  | PCP0R<br>(EIP1.5)   |

Table 8.4. Interrupt Summary

### SFR Definition 9.1. RSTSRC: Reset Source

| R        | R                                                                                                 | R/W           | R/W           | R             | R/W                      | R/W          | R            | Reset Value  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------|---------------|---------------|---------------|--------------------------|--------------|--------------|--------------|--|--|--|--|--|

|          | FERROR                                                                                            | CORSEF        | SWRSF         | WDTRSF        | MCDRSF                   | PORSF        | PINRSF       | Variable     |  |  |  |  |  |

| Bit7     | Bit6                                                                                              | Bit5          | Bit4          | Bit3          | Bit2                     | Bit1         | Bit0         | SFR Address: |  |  |  |  |  |

|          |                                                                                                   |               |               |               |                          |              |              | 0xEF         |  |  |  |  |  |

| (Nata: D | a natura raa                                                                                      | l modify yr   | ita anaratio  |               | NIL ) on this            | ragiotar)    |              |              |  |  |  |  |  |

| (Note: D | o not use read                                                                                    | a-modily-wr   | ite operatio  | ons (ORL, A   | INL) ON this             | register)    |              |              |  |  |  |  |  |

| Bit7:    | UNUSED. R                                                                                         | ead = 0. W    | rite = don't  | care.         |                          |              |              |              |  |  |  |  |  |

| Bit6:    | FERROR: Flash Error Indicator.<br>0: Source of last reset was not a Flash read/write/erase error. |               |               |               |                          |              |              |              |  |  |  |  |  |

|          |                                                                                                   |               |               |               |                          |              |              |              |  |  |  |  |  |

| D        | 1: Source of                                                                                      |               |               |               |                          |              |              |              |  |  |  |  |  |

| Bit5:    | CORSEF: Co<br>Write                                                                               | omparatoru    | Reset Ena     | able and Fla  | ıg.                      |              |              |              |  |  |  |  |  |

|          | 0: Comparat                                                                                       | or0 is not a  | reset sou     | rce           |                          |              |              |              |  |  |  |  |  |

|          | 1: Comparat                                                                                       |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | Read                                                                                              |               |               | ( )           |                          |              |              |              |  |  |  |  |  |

|          | 0: Source of                                                                                      |               |               | •             |                          |              |              |              |  |  |  |  |  |

| 5.4      | 1: Source of                                                                                      |               |               |               |                          |              |              |              |  |  |  |  |  |

| Bit4:    | SWRSF: So                                                                                         | ftware Rese   | et Force ar   | nd Flag.      |                          |              |              |              |  |  |  |  |  |

|          | Write<br>0: No Effect.                                                                            |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 1: Forces a                                                                                       |               | et.           |               |                          |              |              |              |  |  |  |  |  |

|          | Read                                                                                              |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 0: Source of                                                                                      |               |               |               |                          |              |              |              |  |  |  |  |  |

| Dire     | 1: Source of                                                                                      |               |               |               | it.                      |              |              |              |  |  |  |  |  |

| Bit3:    | WDTRSF: W<br>0: Source of                                                                         | -             |               | -             | +                        |              |              |              |  |  |  |  |  |

|          | 1: Source of                                                                                      |               |               |               | ι.                       |              |              |              |  |  |  |  |  |

| Bit2:    | MCDRSF: M                                                                                         |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | Write:                                                                                            | 0             |               | 0             |                          |              |              |              |  |  |  |  |  |

|          | 0: Missing C                                                                                      |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 1: Missing C                                                                                      | lock Detect   | or enabled    | l; triggers a | reset if a mi            | ssing clock  | condition i  | s detected.  |  |  |  |  |  |

|          | Read:                                                                                             | lost react y  | vaa nat a N   | liaging Clas  | k Dotootor t             | imaaut       |              |              |  |  |  |  |  |

|          | 0: Source of<br>1: Source of                                                                      |               |               |               |                          |              |              |              |  |  |  |  |  |

| Bit1:    | PORSF: Pov                                                                                        |               |               | -             |                          | 000.         |              |              |  |  |  |  |  |

|          | This bit is se                                                                                    |               |               | •             | s. This may              | be due to a  | a true power | -on reset or |  |  |  |  |  |

|          | a V <sub>DD</sub> monit                                                                           | or reset. In  | either case   | e, data men   | nory should l            | be conside   | red indeterr | ninate fol-  |  |  |  |  |  |

|          | lowing the re                                                                                     | eset. Writing | g this bit er | nables/disab  | oles the V <sub>DD</sub> | monitor.     |              |              |  |  |  |  |  |

|          | Write:                                                                                            |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 0: V <sub>DD</sub> moni                                                                           |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 1: V <sub>DD</sub> moni                                                                           | tor enabled   | •             |               |                          |              |              |              |  |  |  |  |  |

|          | Read:                                                                                             |               |               |               | 10                       |              |              |              |  |  |  |  |  |

|          | 0: Last reset                                                                                     |               | -             |               |                          | an 1000 ( 1) | ب ا د ا د ا  | in at-       |  |  |  |  |  |

| D:40-    | 1: Last reset                                                                                     | -             |               | DD monitor    | reset; all oth           | er reset fla | igs indetern | imate.       |  |  |  |  |  |

| Bit0:    | PINRSF: HV<br>0: Source of                                                                        |               |               |               |                          |              |              |              |  |  |  |  |  |

|          | 1: Source of                                                                                      |               |               | •             |                          |              |              |              |  |  |  |  |  |

|          | 1: Source of                                                                                      | iast reset v  | vas KST p     | in.           |                          |              |              |              |  |  |  |  |  |

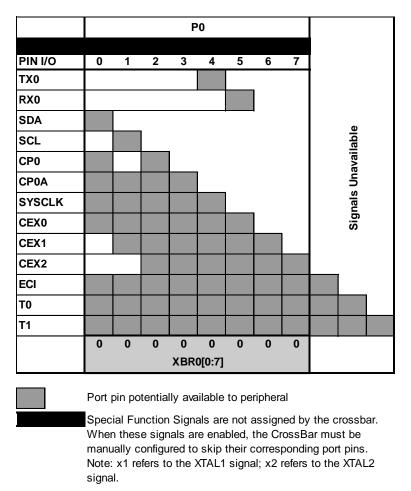

### 12.1. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 12.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least significant unassigned Port pin is assigned to that resource (excluding UART0, which is always at pins 4 and 5). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the XBR0 register are set. The XBR0 register allows software to skip Port pins that are to be used for analog input or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding XBR0 bit should be set. This applies to P0.0 if VREF is enabled, P0.3 and/or P0.2 if the external oscillator circuit is enabled, P0.6 if the ADC is configured to use the external conversion start signal (CNVSTR), and any selected ADC or Comparator inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 12.3 shows the Crossbar Decoder priority with no Port pins skipped (XBR0 = 0x00); Figure 12.4 shows the Crossbar Decoder priority with pins 6 and 2 skipped (XBR0 = 0x44).

Figure 12.3. Crossbar Priority Decoder with XBR0 = 0x00

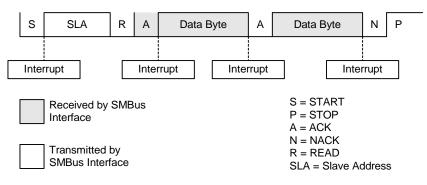

### 13.5.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. After each byte is received, ACKRQ is set to '1' and an interrupt is generated. Software must write the ACK bit (SMB0CN.1) to define the outgoing acknowledge value (Note: writing a '1' to the ACK bit generates an ACK; writing a '0' generates a NACK). Software should write a '0' to the ACK bit after the last byte is received, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. Note that the interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 13.6 shows a typical Master Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 13.6. Typical Master Receiver Sequence

124

### 13.6. SMBus Status Decoding

The current SMBus status can be easily decoded using the SMB0CN register. In the table below, STATUS VECTOR refers to the four upper bits of SMB0CN: MASTER, TXMODE, STA, and STO. Note that the shown response options are only the typical responses; application-specific procedures are allowed as long as they conform with the SMBus specification. Highlighted responses are allowed but do not conform to the SMBus specification.

|                    | Values Read      |       | k       | Current SMbus State | Typical Response Options                                     | Values<br>Written                                                                      |     |     |     |

|--------------------|------------------|-------|---------|---------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|

| Mode               | Status<br>Vector | ACKRQ | ARBLOST | ACK                 |                                                              |                                                                                        | STA | STO | ACK |

|                    | 1110             | 0     | 0       | Х                   | A master START was generated.                                | Load slave address + R/W into SMB0DAT.                                                 | 0   | 0   | Х   |

|                    | 1100             | 0     | 0       | 0                   | A master data or address byte                                | Set STA to restart transfer.                                                           | 1   | 0   | Х   |

| ter                |                  |       |         |                     | was transmitted; NACK received.                              | Abort transfer.                                                                        | 0   | 1   | Х   |

| nsmit              |                  | 0     | 0       | 1                   | A master data or address byte was transmitted; ACK received. | Load next data byte into<br>SMB0DAT                                                    | 0   | 0   | Х   |

| Irai               |                  |       |         |                     |                                                              | End transfer with STOP                                                                 | 0   | 1   | Х   |

| Master Transmitter |                  |       |         |                     |                                                              | End transfer with STOP and start another transfer.                                     | 1   | 1   | Х   |

| Ř                  |                  |       |         |                     |                                                              | Send repeated START                                                                    | 1   | 0   | Х   |

|                    |                  |       |         |                     |                                                              | Switch to Master Receiver<br>Mode (clear SI without writ-<br>ing new data to SMB0DAT). | 0   | 0   | X   |

### Table 13.4. SMBus Status Decoding

| R/W    | R/W                                                                                               | R/W           | R/W             | R/W           | R/W           | R/W           | R/W          | Reset Value     |  |  |  |

|--------|---------------------------------------------------------------------------------------------------|---------------|-----------------|---------------|---------------|---------------|--------------|-----------------|--|--|--|

| SOMODE |                                                                                                   | MCE0          | REN0            | TB80          | RB80          | TI0           | RI0          | 01000000        |  |  |  |

| Bit7   | Bit6                                                                                              | Bit5          | Bit4            | Bit3          | Bit2          | Bit1          | Bit0         | SFR Address:    |  |  |  |

|        |                                                                                                   |               |                 |               |               | (bit          | addressable  | e) 0x98         |  |  |  |

|        |                                                                                                   |               |                 |               |               |               |              |                 |  |  |  |

|        | SOMODE: S                                                                                         |               |                 |               |               |               |              |                 |  |  |  |

|        | This bit sele                                                                                     |               |                 |               | 1             |               |              |                 |  |  |  |

|        | 0: Mode 0: 8                                                                                      |               |                 |               |               |               |              |                 |  |  |  |

| D:40.  | 1: Mode 1: 9                                                                                      |               |                 |               | te            |               |              |                 |  |  |  |

|        | UNUSED. R                                                                                         |               |                 |               | _             |               |              |                 |  |  |  |

|        | MCE0: Mult                                                                                        |               |                 |               |               | Onaration N   | lada         |                 |  |  |  |

|        | The functior<br>Mode 0: Ch                                                                        |               |                 | nt on the Se  | enal Port 0   | Operation     | vioue.       |                 |  |  |  |

|        |                                                                                                   |               | of stop bit is  | ignored       |               |               |              |                 |  |  |  |

|        |                                                                                                   |               | be activate     |               | is logic low  | ol 1          |              |                 |  |  |  |

|        | Mode 1: Mu                                                                                        |               |                 |               | •             |               |              |                 |  |  |  |

|        |                                                                                                   |               | of ninth bit is |               |               |               |              |                 |  |  |  |

|        |                                                                                                   |               | id an interru   |               | ated only w   | hen the nin   | th hit is lo | aic 1           |  |  |  |

| Bit4:  | REN0: Rece                                                                                        |               |                 | ipt is gener  |               |               |              | gio i.          |  |  |  |

| Dit i. |                                                                                                   |               |                 | T receiver    |               |               |              |                 |  |  |  |

|        | This bit enables/disables the UART receiver.<br>0: UART0 reception disabled.                      |               |                 |               |               |               |              |                 |  |  |  |

|        | 1: UARTO reception enabled.                                                                       |               |                 |               |               |               |              |                 |  |  |  |

| Bit3:  | TB80: Ninth Transmission Bit.                                                                     |               |                 |               |               |               |              |                 |  |  |  |

|        | The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode. It |               |                 |               |               |               |              |                 |  |  |  |

|        | is not used i                                                                                     |               |                 | •             |               |               |              |                 |  |  |  |

|        | RB80: Ninth                                                                                       |               |                 |               | ,             |               |              |                 |  |  |  |

|        | RB80 is ass                                                                                       | igned the v   | alue of the     | STOP bit ir   | Mode 0; it    | is assigned   | d the value  | e of the 9th    |  |  |  |

|        | data bit in N                                                                                     | •             |                 |               |               | Ũ             |              |                 |  |  |  |

| Bit1:  | TI0: Transm                                                                                       | it Interrupt  | Flag.           |               |               |               |              |                 |  |  |  |

|        | Set by hard                                                                                       | ware when     | a byte of da    | ata has bee   | n transmitte  | ed by UART    | Γ0 (after th | ne 8th bit in 8 |  |  |  |

|        | bit UART M                                                                                        | ode, or at th | ne beginning    | g of the ST   | OP bit in 9-l | bit UART M    | ode). Whe    | en the UART     |  |  |  |

|        | interrupt is e                                                                                    | enabled, se   | tting this bit  | causes the    | CPU to ve     | ctor to the l | JART0 int    | errupt servic   |  |  |  |

|        | routine. This                                                                                     | s bit must b  | e cleared m     | nanually by   | software      |               |              |                 |  |  |  |

| Bit0:  | RI0: Receiv                                                                                       | e Interrupt   | Flag.           |               |               |               |              |                 |  |  |  |

|        |                                                                                                   |               |                 |               |               |               |              | t the STOP b    |  |  |  |

|        |                                                                                                   |               |                 |               |               |               |              | uses the CP     |  |  |  |

|        | to vector to                                                                                      | the UART0     | interrupt se    | ervice routir | ne. This bit  | must be cle   | eared man    | ually by soft-  |  |  |  |

|        | ware.                                                                                             |               |                 |               |               |               |              |                 |  |  |  |

|        |                                                                                                   |               |                 |               |               |               |              |                 |  |  |  |

### SFR Definition 14.1. SCON0: Serial Port 0 Control

## Table 14.1. Timer Settings for Standard Baud Rates Using The Internal 24.5 MHzOscillator

|                                                                                                        | Frequency: 24.5 MHz          |                      |                                |                       |                                                 |                  |                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|

|                                                                                                        | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |

| SYSCLK from<br>Internal Osc.                                                                           | 230400                       | -0.32%               | 106                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCB                             |  |  |  |

|                                                                                                        | 115200                       | -0.32%               | 212                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x96                             |  |  |  |

|                                                                                                        | 57600                        | 0.15%                | 426                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x2B                             |  |  |  |

|                                                                                                        | 28800                        | -0.32%               | 848                            | SYSCLK / 4            | 01                                              | 0                | 0x96                             |  |  |  |

|                                                                                                        | 14400                        | 0.15%                | 1704                           | SYSCLK / 12           | 00                                              | 0                | 0xB9                             |  |  |  |

|                                                                                                        | 9600                         | -0.32%               | 2544                           | SYSCLK / 12           | 00                                              | 0                | 0x96                             |  |  |  |

|                                                                                                        | 2400                         | -0.32%               | 10176                          | SYSCLK / 48           | 10                                              | 0                | 0x96                             |  |  |  |

|                                                                                                        | 1200                         | 0.15%                | 20448                          | SYSCLK / 48           | 10                                              | 0                | 0x2B                             |  |  |  |

| <ul> <li>Notes:</li> <li>1. SCA1-SCA0 and T1M bit definitions can be found in Section 15.1.</li> </ul> |                              |                      |                                |                       |                                                 |                  |                                  |  |  |  |

**2.** X = Don't care.

# Table 14.2. Timer Settings for Standard Baud Rates Using an External 25 MHzOscillator

|                              | Frequency: 25.0 MHz          |                      |                                |                       |                                                 |                  |                                  |  |  |  |

|------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |

| SYSCLK from<br>External Osc. | 230400                       | -0.47%               | 108                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xCA                             |  |  |  |

|                              | 115200                       | 0.45%                | 218                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x93                             |  |  |  |

|                              | 57600                        | -0.01%               | 434                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x27                             |  |  |  |

|                              | 28800                        | 0.45%                | 872                            | SYSCLK / 4            | 01                                              | 0                | 0x93                             |  |  |  |

|                              | 14400                        | -0.01%               | 1736                           | SYSCLK / 4            | 01                                              | 0                | 0x27                             |  |  |  |

|                              | 9600                         | 0.15%                | 2608                           | EXTCLK / 8            | 11                                              | 0                | 0x5D                             |  |  |  |

|                              | 2400                         | 0.45%                | 10464                          | SYSCLK / 48           | 10                                              | 0                | 0x93                             |  |  |  |

|                              | 1200                         | -0.01%               | 20832                          | SYSCLK / 48           | 10                                              | 0                | 0x27                             |  |  |  |

| SYSCLK from<br>Internal Osc. | 57600                        | -0.47%               | 432                            | EXTCLK / 8            | 11                                              | 0                | 0xE5                             |  |  |  |

|                              | 28800                        | -0.47%               | 864                            | EXTCLK / 8            | 11                                              | 0                | 0xCA                             |  |  |  |

|                              | 14400                        | 0.45%                | 1744                           | EXTCLK / 8            | 11                                              | 0                | 0x93                             |  |  |  |

|                              | 9600                         | 0.15%                | 2608                           | EXTCLK / 8            | 11                                              | 0                | 0x5D                             |  |  |  |

Notes:

1. SCA1–SCA0 and T1M bit definitions can be found in **Section 15.1**.

2. X = Don't care