Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                 |

| Peripherals                | POR, PWM, WDT                                               |

| Number of I/O              | 8                                                           |

| Program Memory Size        | 4KB (4K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 256 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | -                                                           |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 10-VFDFN Exposed Pad                                        |

| Supplier Device Package    | 11-QFN (3x3)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f304 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. | System Overview                                           | 13 |

|----|-----------------------------------------------------------|----|

|    | 1.1. CIP-51 <sup>™</sup> Microcontroller Core             | 16 |

|    | 1.1.1. Fully 8051 Compatible                              |    |

|    | 1.1.2. Improved Throughput                                | 16 |

|    | 1.1.3. Additional Features                                |    |

|    | 1.2. On-Chip Memory                                       | 18 |

|    | 1.3. On-Chip Debug Circuitry                              | 19 |

|    | 1.4. Programmable Digital I/O and Crossbar                | 19 |

|    | 1.5. Serial Ports                                         |    |

|    | 1.6. Programmable Counter Array                           | 21 |

|    | 1.7. 8-Bit Analog to Digital Converter (C8051F300/2 Only) | 22 |

|    | 1.8. Comparator                                           | 23 |

| 2. | Absolute Maximum Ratings                                  |    |

| 3. | Global Electrical Characteristics                         | 25 |

| 4. | Pinout and Package Definitions                            | 27 |

| 5. | ADC0 (8-Bit ADC, C8051F300/2)                             | 35 |

|    | 5.1. Analog Multiplexer and PGA                           | 36 |

|    | 5.2. Temperature Sensor                                   | 36 |

|    | 5.3. Modes of Operation                                   | 39 |

|    | 5.3.1. Starting a Conversion                              | 39 |

|    | 5.3.2. Tracking Modes                                     | 40 |

|    | 5.3.3. Settling Time Requirements                         | 41 |

|    | 5.4. Programmable Window Detector                         | 45 |

|    | 5.4.1. Window Detector In Single-Ended Mode               | 45 |

|    | 5.4.2. Window Detector In Differential Mode               |    |

| 6. | Voltage Reference (C8051F300/2)                           | 49 |

| 7. |                                                           |    |

| 8. | •••••••••••••••••••••••••••••••••••••••                   |    |

|    | 8.1. Instruction Set                                      |    |

|    | 8.1.1. Instruction and CPU Timing                         |    |

|    | 8.1.2. MOVX Instruction and Program Memory                |    |

|    | 8.2. Memory Organization                                  |    |

|    | 8.2.1. Program Memory                                     |    |

|    | 8.2.2. Data Memory                                        | 64 |

|    | 8.2.3. General Purpose Registers                          |    |

|    | 8.2.4. Bit Addressable Locations                          |    |

|    | 8.2.5. Stack                                              |    |

|    | 8.2.6. Special Function Registers                         |    |

|    | 8.2.7. Register Descriptions                              | 68 |

|    | 8.3. Interrupt Handler                                    |    |

|    | 8.3.1. MCU Interrupt Sources and Vectors                  |    |

|    | 8.3.2. External Interrupts                                |    |

|    | 8.3.3. Interrupt Priorities                               | 73 |

### Table 5.1. ADC0 Electrical Characteristics

$V_{DD}$  = 3.0 V, VREF = 2.40 V (REFSL = 0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                                                                                                              | Conditions                         | Min     | Тур       | Мах      | Units   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|-----------|----------|---------|

| DC Accuracy                                                                                                                                            |                                    |         |           |          |         |

| Resolution                                                                                                                                             |                                    |         | 8         |          | bits    |

| Integral Nonlinearity                                                                                                                                  |                                    | —       | ±0.5      | ±1       | LSB     |

| Differential Nonlinearity                                                                                                                              | Guaranteed Monotonic               | —       | ±0.5      | ±1       | LSB     |

| Offset Error                                                                                                                                           |                                    | -5.0    | 0.5       | 5.0      | LSB     |

| Full Scale Error                                                                                                                                       | Differential mode                  | -5.0    | -1        | 5.0      | LSB     |

| Dynamic Performance (10 kHz                                                                                                                            | Sine-wave Differential Input, 1    | dB belo | w Full Sc | ale, 500 | ksps)   |

| Signal-to-Noise Plus Distortion                                                                                                                        |                                    | 45      | 48        | —        | dB      |

| Total Harmonic Distortion                                                                                                                              | Up to the 5 <sup>th</sup> harmonic |         | -56       | —        | dB      |

| Spurious-Free Dynamic Range                                                                                                                            |                                    |         | 58        | —        | dB      |

| Conversion Rate                                                                                                                                        |                                    |         |           |          |         |

| SAR Conversion Clock                                                                                                                                   |                                    | —       |           | 6        | MHz     |

| Conversion Time in SAR Clocks                                                                                                                          |                                    | 11      |           | —        | clocks  |

| Track/Hold Acquisition Time                                                                                                                            |                                    | 300     |           | —        | ns      |

| Throughput Rate                                                                                                                                        |                                    | —       | —         | 500      | ksps    |

| Analog Inputs                                                                                                                                          |                                    |         | 1         |          |         |

| Input Voltage Range                                                                                                                                    |                                    | 0       | —         | VREF     | V       |

| Input Capacitance                                                                                                                                      |                                    | —       | 5         | —        | pF      |

| Temperature Sensor                                                                                                                                     |                                    | —       | _         | —        |         |

| Linearity <sup>1,2,3</sup>                                                                                                                             |                                    | —       | ±0.5      | —        | °C      |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    | —       | 3350      | —        | μV / °C |

| Gain <sup>1,2,3</sup>                                                                                                                                  |                                    |         | ±110      |          |         |

| Offset <sup>1,2,3</sup>                                                                                                                                | (Temp = 0 °C)                      |         | 897±31    | —        | mV      |

| Power Specifications                                                                                                                                   |                                    |         |           |          |         |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC0)                                                                                             | Operating Mode, 500 ksps           | —       | 400       | 900      | μA      |

| Power Supply Rejection                                                                                                                                 |                                    | —       | ±0.3      | —        | mV/V    |

| <ul> <li>Notes:</li> <li>1. Represents one standard devi</li> <li>2. Measured with PGA Gain = 2.</li> <li>3. Includes ADC offset, gain, and</li> </ul> |                                    |         |           |          |         |

NOTES:

| Mnemonic            | Description                                         | Bytes | Clock<br>Cycles |

|---------------------|-----------------------------------------------------|-------|-----------------|

| JNZ rel             | Jump if A does not equal zero                       | 2     | 2/3             |

| CJNE A, direct, rel | Compare direct byte to A and jump if not equal      | 3     | 3/4             |

| CJNE A, #data, rel  | Compare immediate to A and jump if not equal        | 3     | 3/4             |

| CJNE Rn, #data, rel | Compare immediate to Register and jump if not equal | 3     | 3/4             |

Compare immediate to indirect and jump if not

Decrement Register and jump if not zero

Decrement direct byte and jump if not zero

3

2

3

1

4/5

2/3

3/4

1

#### Table 8.1. CIP-51 Instruction Set Summary (Continued)

Notes on Registers, Operands and Addressing Modes:

equal

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through R0 or R1.

No operation

**rel** - 8-bit, signed (two's complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00-0x7F) or an SFR (0x80-0xFF).

#data - 8-bit constant

CJNE @Ri, #data, rel

DJNZ Rn, rel

NOP

DJNZ direct, rel

#data16 - 16-bit constant

bit - Direct-accessed bit in Data RAM or SFR

**addr11** - 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2K-byte page of program memory as the first byte of the following instruction.

**addr16** - 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8K-byte program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| R/W         | R/W         | R/W         | R/W                 | R/W        | R/W           | R/W          | R              | Reset Value      |

|-------------|-------------|-------------|---------------------|------------|---------------|--------------|----------------|------------------|

| CY          | AC          | F0          | RS1                 | RS0        | OV            | F1           | PARITY         | 0000000          |

| Bit7        | Bit6        | Bit5        | Bit4                | Bit3       | Bit2          | Bit1         | Bit0           | SFR Address:     |

|             |             |             |                     |            |               | (bi          | t addressable) | 0xD0             |

|             |             |             |                     |            |               |              |                |                  |

| Bit7:       | CY: Carry   | •           |                     |            |               |              |                |                  |

|             |             |             | he last arithmet    |            |               |              |                | or a borrow      |

| <b>B</b> HA |             |             | eared to logic 0 l  | by all oth | ner arithme   | tic operatio | ns.            |                  |

| Bit6:       | AC: Auxilia |             |                     |            |               |              |                |                  |

|             |             |             | he last arithmetic  |            |               |              |                |                  |

|             | tions.      | raction) th | e high order nib    |            |               |              |                | nmetic opera-    |

| Bit5:       | F0: User F  | lag 0       |                     |            |               |              |                |                  |

| Dito.       |             | 0           | able, general pu    | irpose fl  | ad for use i  | under softw  | are control    |                  |

| Bits4–3:    |             |             | Bank Select.        |            |               |              |                |                  |

|             |             |             | ich register ban    | k is used  | d during reg  | gister acces | sses.          |                  |

|             |             |             | C C                 |            |               |              |                |                  |

|             | RS1         | RS0         | Register Bank       | Ad         | dress         |              |                |                  |

|             | 0           | 0           | 0                   | 0x0        | 0–0x07        |              |                |                  |

|             | 0           | 1           | 1                   | 0x0        | 8–0x0F        |              |                |                  |

|             | 1           | 0           | 2                   | 0x1        | 0–0x17        |              |                |                  |

|             | 1           | 1           | 3                   | 0x1        | 8–0x1F        |              |                |                  |

| D:40        | O(k) O(k)   |             |                     |            |               |              |                |                  |

| Bit2:       | OV: Overf   | •           | der the followin    |            | etancoc:      |              |                |                  |

|             |             |             | or SUBB instruct    |            |               | change ove   | rflow          |                  |

|             |             |             | results in an ov    |            | •             | •            |                |                  |

|             |             |             | causes a divide-    |            |               |              |                |                  |

|             |             |             | d to 0 by the AD    |            |               | /IUL, and D  | IV instruction | ons in all other |

|             | cases.      |             | -                   |            | ,             | ·            |                |                  |

| Bit1:       | F1: User F  | •           |                     |            |               |              |                |                  |

|             |             |             | able, general pu    | irpose fl  | ag for use ι  | under softw  | are control    |                  |

| Bit0:       | PARITY: F   |             |                     |            |               |              |                |                  |

|             |             | -           | : 1 if the sum of t | he eight   | bits in the a | accumulato   | or is odd an   | d cleared if the |

|             | sum is eve  | en.         |                     |            |               |              |                |                  |

|             |             |             |                     |            |               |              |                |                  |

## SFR Definition 8.4. PSW: Program Status Word

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                             | Bit addressable? | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|-------------------------------|---------------------|-------------------|------------------------------------------|------------------|----------------|--------------------|---------------------|

| Reset                         | 0x0000              | Тор               | None                                     | N/A              | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (/INT0)  | 0x0003              | 0                 | IE0 (TCON.1)                             | Y                | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                             | Y                | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (/INT1)  | 0x0013              | 2                 | IE1 (TCON.3)                             | Y                | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                             | Y                | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                         | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)           | Y                | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H<br>(TMR2CN.7)<br>TF2L<br>(TMR2CN.6) | Y                | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SMBus Interface               | 0x0033              | 6                 | SI (SMB0CN.0)                            | Y                | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Compare           | 0x003B              | 7                 | AD0WINT<br>(ADC0CN.3)                    | Y                | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion Com-<br>plete | 0x0043              | 8                 | AD0INT<br>(ADC0CN.5)                     | Y                | N              | EADC0C<br>(EIE1.2) | PADC0C<br>(EIP1.2)  |

| Programmable Counter<br>Array | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn<br>(PCA0CN.n)      | Y                | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0 Falling Edge      | 0x0053              | 10                | CP0FIF<br>(CPT0CN.4)                     | N                | N              | ECP0F<br>(EIE1.4)  | PCP0F<br>(EIP1.4)   |

| Comparator0 Rising Edge       | 0x005B              | 11                | CP0RIF<br>(CPT0CN.5)                     | N                | N              | ECP0R<br>(EIE1.5)  | PCP0R<br>(EIP1.5)   |

Table 8.4. Interrupt Summary

#### 8.4.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes execution. In Stop mode the internal oscillator, CPU, and all digital peripherals are stopped; the state of the external oscillator circuit is not affected. Each analog peripheral (including the external oscillator circuit) may be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to in STOP mode for longer than the MCD timeout of 100  $\mu$ sec.

| R/W                                                                                                             | R/W                                                                                     | R/W           | R/W         | R/W          | R/W         | R/W            | R/W       | Reset Value  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------|-------------|--------------|-------------|----------------|-----------|--------------|--|--|--|--|

| GF5                                                                                                             | GF4                                                                                     | GF3           | GF2         | GF1          | GF0         | STOP           | IDLE      | 0000000      |  |  |  |  |

| Bit7                                                                                                            | Bit6                                                                                    | Bit5          | Bit4        | Bit3         | Bit2        | Bit1           | Bit0      | SFR Address: |  |  |  |  |

|                                                                                                                 |                                                                                         |               |             |              |             |                |           | 0x87         |  |  |  |  |

| Bits7–2: GF5–GF0: General Purpose Flags 5-0.<br>These are general purpose flags for use under software control. |                                                                                         |               |             |              |             |                |           |              |  |  |  |  |

| Bit1:                                                                                                           | STOP: Stop                                                                              |               | •           | or use unde  | er sontware | control.       |           |              |  |  |  |  |

| Ditt.                                                                                                           | Setting this                                                                            |               |             | 1 in Stop m  | ode. This b | oit will alway | s be read | as 0.        |  |  |  |  |

|                                                                                                                 | 1: CPU goes                                                                             |               |             |              |             |                |           |              |  |  |  |  |

| Bit0:                                                                                                           | IDLE: Idle M                                                                            | ode Select    |             |              |             |                |           |              |  |  |  |  |

|                                                                                                                 | Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0. |               |             |              |             |                |           |              |  |  |  |  |

|                                                                                                                 | •                                                                                       | •             |             |              |             |                |           |              |  |  |  |  |

|                                                                                                                 | 1: CPU goes<br>Ports, and A                                                             | s into Idle n | node (shuts | off clock to | CPU, but    |                |           |              |  |  |  |  |

### SFR Definition 8.12. PCON: Power Control

# 12. Port Input/Output

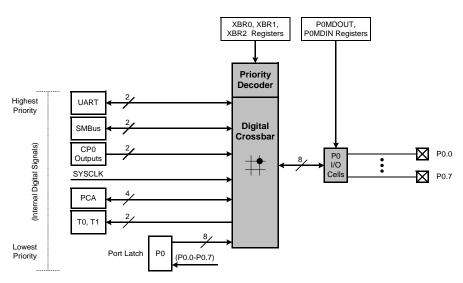

Digital and analog resources are available through a byte-wide digital I/O Port, Port0. Each of the Port pins can be defined as general-purpose I/O (GPIO), analog input, or assigned to one of the internal digital resources as shown in Figure 12.3. The designer has complete control over which functions are assigned, limited only by the number of physical I/O pins. This resource assignment flexibility is achieved through the use of a Priority Crossbar Decoder. Note that the state of a Port I/O pin can always be read in the corresponding Port latch, regardless of the Crossbar settings.

The Crossbar assigns the selected internal digital resources to the I/O pins based on the Priority Decoder (Figure 12.3 and Figure 12.4). The registers XBR0, XBR1, and XBR2, defined in SFR Definition 12.1, SFR Definition 12.2, and SFR Definition 12.3 are used to select internal digital functions.

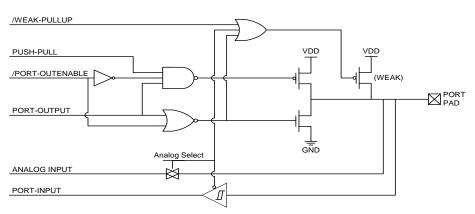

All Port I/Os are 5 V tolerant (refer to Figure 12.2 for the Port cell circuit). The Port I/O cells are configured as either push-pull or open-drain in the Port0 Output Mode register (P0MDOUT). Complete Electrical Specifications for Port I/O are given in Table 12.1 on page 110.

Figure 12.1. Port I/O Functional Block Diagram

Figure 12.2. Port I/O Cell Block Diagram

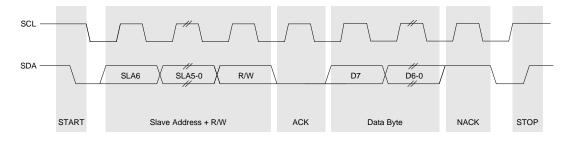

The direction bit (R/W) occupies the least significant bit position of the address byte. The direction bit is set to logic 1 to indicate a "READ" operation and cleared to logic 0 to indicate a "WRITE" operation.

All transactions are initiated by a master, with one or more addressed slave devices as the target. The master generates the START condition and then transmits the slave address and direction bit. If the transaction is a WRITE operation from the master to the slave, the master transmits the data a byte at a time waiting for an ACK from the slave at the end of each byte. For READ operations, the slave transmits the data waiting for an ACK from the master at the end of each byte. At the end of the data transfer, the master generates a STOP condition to terminate the transaction and free the bus. Figure 13.3 illustrates a typical SMBus transaction.

Figure 13.3. SMBus Transaction

#### 13.3.1. Arbitration

A master may start a transfer only if the bus is free. The bus is free after a STOP condition or after the SCL and SDA lines remain high for a specified time (see **Section "13.3.4. SCL High (SMBus Free) Timeout" on page 114**). In the event that two or more devices attempt to begin a transfer at the same time, an arbitration scheme is employed to force one master to give up the bus. The master devices continue transmitting until one attempts a HIGH while the other transmits a LOW. Since the bus is open-drain, the bus will be pulled LOW. The master attempting the HIGH will detect a LOW SDA and lose the arbitration. The winning master continues its transmission without interruption; the losing master becomes a slave and receives the rest of the transfer if addressed. This arbitration scheme is non-destructive: one device always wins, and no data is lost.

| SFR Definition 13.1. SMB0CF: SMBus | Clock/Configuration |

|------------------------------------|---------------------|

|------------------------------------|---------------------|

| R/W      | R/W                                            | R               | R/W           | R/W                       | R/W           | R/W          | R/W          | Reset Value  |  |  |  |

|----------|------------------------------------------------|-----------------|---------------|---------------------------|---------------|--------------|--------------|--------------|--|--|--|

| ENSMB    | INH                                            | BUSY            | EXTHOLD       | SMBTOE                    | SMBFTE        | SMBCS1       | SMBCS0       | 0000000      |  |  |  |

| Bit7     | Bit6                                           | Bit5            | Bit4          | Bit3                      | Bit2          | Bit1         | Bit0         | SFR Addres   |  |  |  |

|          |                                                |                 |               |                           |               |              |              | 0xC1         |  |  |  |

| Bit7:    | ENSMB: SM                                      | IBus Enabl      | ۵             |                           |               |              |              |              |  |  |  |

|          | This bit enal                                  |                 | -             | is interface.             | When ena      | bled, the in | terface con  | stantly mo   |  |  |  |

|          | itors the SD                                   |                 |               |                           |               |              |              | otantiy mo   |  |  |  |

|          | 0: SMBus in                                    |                 | -             |                           |               |              |              |              |  |  |  |

|          | 1: SMBus in                                    |                 |               |                           |               |              |              |              |  |  |  |

| Bit6:    | INH: SMBus                                     |                 |               |                           |               |              |              |              |  |  |  |

|          | When this b                                    | it is set to lo | ogic 1, the S | MBus does                 | s not genera  | ate an inter | rupt when s  | lave even    |  |  |  |

|          | occur. This e                                  |                 |               |                           |               |              |              |              |  |  |  |

|          | not affected                                   | •               |               |                           |               |              |              | •            |  |  |  |

|          | 0: SMBus S                                     | lave Mode       | enabled.      |                           |               |              |              |              |  |  |  |

|          | 1: SMBus S                                     | lave Mode       | inhibited.    |                           |               |              |              |              |  |  |  |

| Bit5:    | BUSY: SMB                                      | us Busy In      | dicator.      |                           |               |              |              |              |  |  |  |

|          | This bit is se                                 | et to logic 1   | by hardwar    | e when a tr               | ansfer is in  | progress. I  | t is cleared | to logic 0   |  |  |  |

|          | when a STC                                     | P or free ti    | meout is sei  | nsed.                     |               |              |              |              |  |  |  |

| Bit4:    | EXTHOLD:                                       | SMBus Set       | up and Hold   | d Time Exte               | nsion Enab    | ole.         |              |              |  |  |  |

|          | This bit cont                                  |                 | •             |                           | -             | to Table 13  | 3.2.         |              |  |  |  |

|          | 0: SDA Extended Setup and Hold Times disabled. |                 |               |                           |               |              |              |              |  |  |  |

|          | 1: SDA Exte                                    |                 |               |                           |               |              |              |              |  |  |  |

| Bit3:    | SMBTOE: S                                      |                 |               |                           |               |              |              |              |  |  |  |

|          | This bit enal                                  |                 |               |                           |               |              |              |              |  |  |  |

|          | reload while                                   |                 |               |                           |               |              |              |              |  |  |  |

|          | figured in sp                                  | •               |               |                           |               |              |              |              |  |  |  |

|          | SCL is high.                                   |                 |               |                           |               |              | t 25 ms, an  | d the Time   |  |  |  |

|          | 2 interrupt s                                  |                 |               |                           |               | ation.       |              |              |  |  |  |

| Bit2:    | SMBFTE: S                                      |                 |               |                           |               |              |              |              |  |  |  |

|          | When this b                                    |                 |               |                           | onsidered fro | ee if SCL a  | nd SDA ren   | hain high fo |  |  |  |

|          | more than 1                                    |                 |               |                           |               |              |              |              |  |  |  |

| Bits1–0: | SMBCS1-SI                                      |                 |               |                           |               |              |              |              |  |  |  |

|          | These two b                                    |                 |               |                           |               | •            |              | VIBUS bit    |  |  |  |

|          | rate. The se                                   | lected devi     | ce snould be  | e configure               | a according   | to Equatio   | n 13.1.      |              |  |  |  |

|          | SMBCS1                                         | SMBCS0          | SM            | Bus Clock                 | Source        |              |              |              |  |  |  |

|          | 0                                              | 0               |               | Fimer 0 Ove               |               |              |              |              |  |  |  |

|          | 0                                              | 4               |               | Fimer 1 Ove               | rflow         |              |              |              |  |  |  |

|          | ů,                                             | 1               |               |                           |               |              |              |              |  |  |  |

|          | 1                                              | 1<br>0          | Timer         | 2 High Byte<br>2 Low Byte | e Overflow    |              |              |              |  |  |  |

|                | Values Read                                         |   |   |   | Current SMbus State                                                                 | Typical Response Options                                                                                                                                                |     | /alue<br>Vritte |   |

|----------------|-----------------------------------------------------|---|---|---|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|---|

| Mode           | Mode<br>Status<br>Vector<br>ACKRQ<br>ARBLOST<br>ACK |   |   |   | STA                                                                                 | STO                                                                                                                                                                     | ACK |                 |   |

|                | 0010                                                | 1 | 0 | X | A slave address was received;<br>ACK requested.                                     | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0   | 0               | 1 |

|                |                                                     |   |   |   |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0 |

|                |                                                     |   |   |   |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0   | 0               | 1 |

|                |                                                     | 1 | 1 | X | Lost arbitration as master; slave<br>address received; ACK<br>requested.            | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0   | 0               | 1 |

|                |                                                     |   |   |   |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0   | 0               | 0 |

| SLAVE RECEIVER |                                                     |   |   |   |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0   | 0               | 1 |

| SL/            |                                                     |   |   |   |                                                                                     | Reschedule failed transfer;<br>do not acknowledge received<br>address                                                                                                   | 1   | 0               | 0 |

|                | 0010                                                | 0 | 1 | Х | Lost arbitration while attempting a                                                 | Abort failed transfer.                                                                                                                                                  | 0   | 0               | Х |

|                | 0001                                                |   |   | V | repeated START.                                                                     | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X |

|                | 0001                                                | 1 | 1 |   | Lost arbitration while attempting a STOP.                                           | complete/aborted).                                                                                                                                                      | 0   | 0               | 0 |

|                |                                                     | 0 | 0 |   | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver. | Clear STO.                                                                                                                                                              | 0   | 0               | X |

|                |                                                     | 0 | 1 | Х |                                                                                     | Abort transfer.                                                                                                                                                         | 0   | 0               | Х |

|                |                                                     |   |   |   | STOP.                                                                               | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | X |

|                | 0000                                                | 1 | 0 | X | A slave byte was received; ACK requested.                                           | Acknowledge received byte;<br>Read SMB0DAT.                                                                                                                             | 0   | 0               | 1 |

|                |                                                     |   |   |   |                                                                                     | Do not acknowledge received byte.                                                                                                                                       | 0   | 0               | 0 |

|                |                                                     | 1 | 1 | х | Lost arbitration while transmitting                                                 | Abort failed transfer.                                                                                                                                                  | 0   | 0               | 0 |

|                |                                                     |   |   |   | a data byte as master.                                                              | Reschedule failed transfer.                                                                                                                                             | 1   | 0               | 0 |

### Table 13.4. SMBus Status Decoding (Continued)

NOTES:

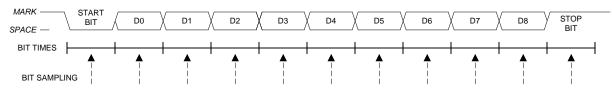

#### 14.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to '1'. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to '1'.

Figure 14.5. 9-Bit UART Timing Diagram

| Table 14.6. Timer Settings for Standard Baud Rates Using an External 3.6864 MHZ |

|---------------------------------------------------------------------------------|

| Oscillator                                                                      |

|                              |                              |                      | Frequ                          | iency: 3.6864 M       | ЛНz                                             |                  |                                  |

|------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|                              | 230400                       | 0.00%                | 16                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xF8                             |

|                              | 115200                       | 0.00%                | 32                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xF0                             |

| from<br>Osc.                 | 57600                        | 0.00%                | 64                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xE0                             |

| SYSCLK from<br>External Osc. | 28800                        | 0.00%                | 128                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xC0                             |

| SYSCLK<br>External           | 14400                        | 0.00%                | 256                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x80                             |

| SY:<br>Ext                   | 9600                         | 0.00%                | 384                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x40                             |

|                              | 2400                         | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |

|                              | 1200                         | 0.00%                | 3072                           | SYSCLK / 12           | 00                                              | 0                | 0x80                             |

|                              | 230400                       | 0.00%                | 16                             | EXTCLK / 8            | 11                                              | 0                | 0xFF                             |

| from<br>Osc.                 | 115200                       | 0.00%                | 32                             | EXTCLK / 8            | 11                                              | 0                | 0xFE                             |

| K fr<br>al O                 | 57600                        | 0.00%                | 64                             | EXTCLK / 8            | 11                                              | 0                | 0xFC                             |

| SYSCLK from<br>Internal Osc. | 28800                        | 0.00%                | 128                            | EXTCLK / 8            | 11                                              | 0                | 0xF8                             |

| SY:<br>Inte                  | 14400                        | 0.00%                | 256                            | EXTCLK / 8            | 11                                              | 0                | 0xF0                             |

|                              | 9600                         | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |

Notes:

1. SCA1–SCA0 and T1M bit definitions can be found in **Section 15.1**.

2. X = Don't care

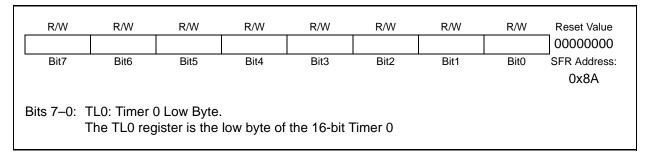

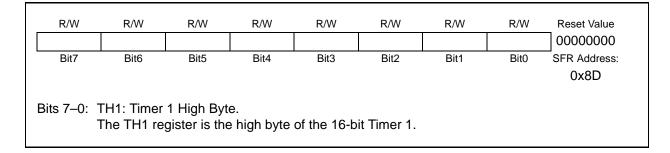

### SFR Definition 15.5. TL1: Timer 1 Low Byte

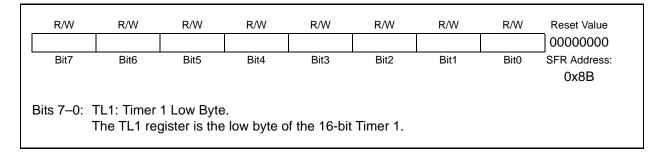

#### SFR Definition 15.6. TH0: Timer 0 High Byte

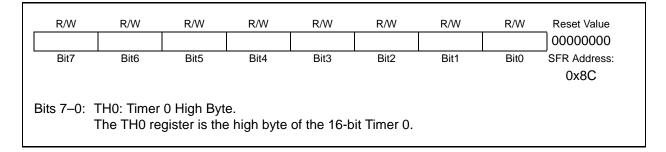

### SFR Definition 15.7. TH1: Timer 1 High Byte

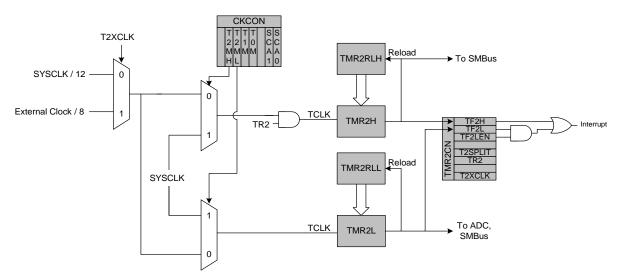

#### 15.2.2. 8-bit Timers with Auto-Reload

When T2SPLIT is set, Timer 2 operates as two 8-bit timers (TMR2H and TMR2L). Both 8-bit timers operate in auto-reload mode as shown in Figure 15.5. TMR2RLL holds the reload value for TMR2L; TMR2RLH holds the reload value for TMR2H. The TR2 bit in TMR2CN handles the run control for TMR2H. TMR2L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 2 Clock Select bits (T2MH and T2ML in CKCON) select either SYSCLK or the clock defined by the Timer 2 External Clock Select bit (T2XCLK in TMR2CN), as follows:

| T2MH | T2XCLK | TMR2H Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

| T2ML | T2XCLK | TMR2L Clock Source |

|------|--------|--------------------|

| 0    | 0      | SYSCLK / 12        |

| 0    | 1      | External Clock / 8 |

| 1    | Х      | SYSCLK             |

Note: External clock divided by 8 is synchronized with the system clock, and the external clock must be less than or equal to the system clock to operate in this mode.

The TF2H bit is set when TMR2H overflows from 0xFF to 0x00; the TF2L bit is set when TMR2L overflows from 0xFF to 0x00. When Timer 2 interrupts are enabled (IE.5), an interrupt is generated each time TMR2H overflows. If Timer 2 interrupts are enabled and TF2LEN (TMR2CN.5) is set, an interrupt is generated each time either TMR2L or TMR2H overflows. When TF2LEN is enabled, software must check the TF2H and TF2L flags to determine the source of the Timer 2 interrupt. The TF2H and TF2L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 15.5. Timer 2 8-Bit Mode Block Diagram

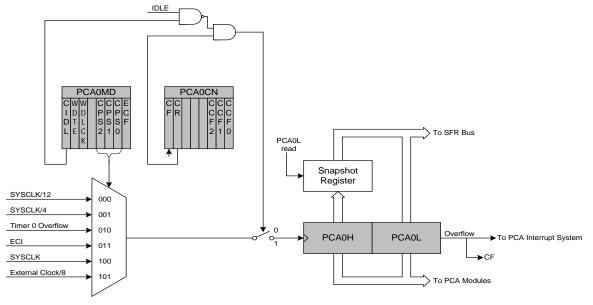

#### 16.1. PCA Counter/Timer

The 16-bit PCA counter/timer consists of two 8-bit SFRs: PCA0L and PCA0H. PCA0H is the high byte (MSB) of the 16-bit counter/timer and PCA0L is the low byte (LSB). Reading PCA0L automatically latches the value of PCA0H into a "snapshot" register; the following PCA0H read accesses this "snapshot" register. **Reading the PCA0L Register first guarantees an accurate reading of the entire 16-bit PCA0 counter**. Reading PCA0H or PCA0L does not disturb the counter operation. The CPS2-CPS0 bits in the PCA0MD register select the timebase for the counter/timer as shown in Table 16.1. **Note that in 'External oscillator source divided by 8' mode, the external oscillator source is synchronized with the system clock, and must have a frequency less than or equal to the system clock.**

When the counter/timer overflows from 0xFFFF to 0x0000, the Counter Overflow Flag (CF) in PCA0MD is set to logic 1 and an interrupt request is generated if CF interrupts are enabled. Setting the ECF bit in PCA0MD to logic 1 enables the CF flag to generate an interrupt request. The CF bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software (Note: PCA0 interrupts must be globally enabled before CF interrupts are recognized. PCA0 interrupts are globally enabled by setting the EA bit and the EPCA0 bit to logic 1). Clearing the CIDL bit in the PCA0MD register allows the PCA to continue normal operation while the CPU is in Idle mode.

| CPS2 | CPS1 | CPS0 | Timebase                                                              |

|------|------|------|-----------------------------------------------------------------------|

| 0    | 0    | 0    | System clock divided by 12                                            |

| 0    | 0    | 1    | System clock divided by 4                                             |

| 0    | 1    | 0    | Timer 0 overflow                                                      |

| 0    | 1    | 1    | High-to-low transitions on ECI (max rate = system clock divided by 4) |

| 1    | 0    | 0    | System clock                                                          |

| 1    | 0    | 1    | External oscillator source divided by 8 <sup>*</sup>                  |

| Table 16.1. PCA Timebase Input Options | Table | 16.1. | PCA | Timebase | Input | Options |

|----------------------------------------|-------|-------|-----|----------|-------|---------|

|----------------------------------------|-------|-------|-----|----------|-------|---------|

\*Note: External oscillator source divided by 8 is synchronized with the system clock.

#### 16.4. Register Descriptions for PCA

Following are detailed descriptions of the special function registers related to the operation of the PCA.

| SFR Definition 16.1. PC | A0CN: PCA Control |

|-------------------------|-------------------|

|-------------------------|-------------------|

| R/W               | R/W                                                                                       | R/W                                                                                                  | R/W                                                                                           | R/W                                                   | R/W                                         | R/W                        | R/W                      | Reset Value                                |

|-------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------|----------------------------|--------------------------|--------------------------------------------|

| CF                | CR                                                                                        | _                                                                                                    | _                                                                                             | —                                                     | CCF2                                        | CCF1                       | CCF0                     | 00000000                                   |

| Bit7              | Bit6                                                                                      | Bit5                                                                                                 | Bit4                                                                                          | Bit3                                                  | Bit2                                        | Bit1                       | Bit0                     | SFR Address:                               |

|                   |                                                                                           |                                                                                                      |                                                                                               |                                                       |                                             | (bit                       | addressable              | e) 0xD8                                    |

| Bit7:<br>Bit6:    | Counter/Tim<br>to the PCA i<br>must be clea<br>CR: PCA Co<br>This bit enal<br>0: PCA Cou  | vare when<br>er Overflow<br>nterrupt se<br>ared by soft<br>punter/Time<br>ples/disable<br>nter/Timer | the PCA Co<br>v (CF) inter<br>rvice routin<br>ware.<br>er Run Cont<br>es the PCA<br>disabled. | ounter/Time<br>rupt is enat<br>e. This bit is<br>rol. | oled, setting<br>s not autom                | this bit cau               | uses the C               | 00. When the<br>PU to vector<br>rdware and |

| Bits5–3:<br>Bit2: | 1: PCA Cour<br>UNUSED. R<br>CCF2: PCA<br>This bit is se<br>enabled, set<br>bit is not aut | ead = 000<br>Module 2 (<br>et by hardw<br>ting this bit                                              | o, Write = d<br>Capture/Co<br>are when a<br>causes the                                        | mpare Flag<br>match or c<br>CPU to ve                 | ector to the                                | PCA interru                | upt service              | nterrupt is<br>routine. This               |

| Bit1:             | CCF1: PCA<br>This bit is se<br>enabled, set<br>bit is not aut                             | Module 1 (<br>et by hardw<br>ting this bit<br>omatically                                             | Capture/Co<br>are when a<br>causes the<br>cleared by                                          | mpare Flag<br>match or c<br>CPU to ve<br>hardware a   | apture occu<br>ector to the l<br>nd must be | urs. When t<br>PCA interru | he CCF1 i<br>ıpt service | nterrupt is<br>routine. This               |

| Bit0:             | CCF0: PCA<br>This bit is se<br>enabled, set<br>bit is not aut                             | et by hardw<br>ting this bit                                                                         | are when a causes the                                                                         | match or c<br>CPU to ve                               | ector to the                                | PCA interru                | upt service              | nterrupt is<br>routine. This               |

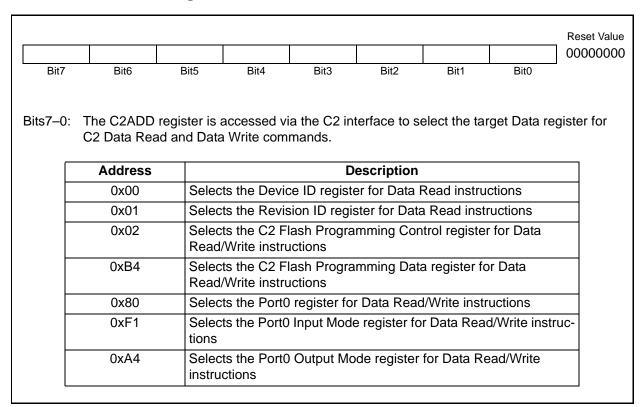

# 17. C2 Interface

C8051F300/1/2/3/4/5 devices include an on-chip Silicon Labs 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface operates using only two pins: a bi-directional data signal (C2D) and a clock input (C2CK). See the C2 Interface Specification for details on the C2 protocol.

#### 17.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

### C2 Register Definition 17.1. C2ADD: C2 Address

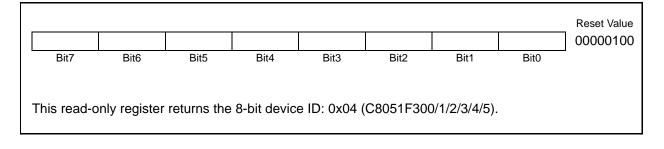

## C2 Register Definition 17.2. DEVICEID: C2 Device ID

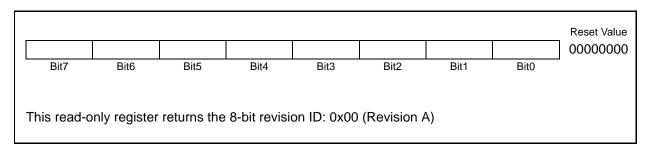

## C2 Register Definition 17.3. REVID: C2 Revision ID

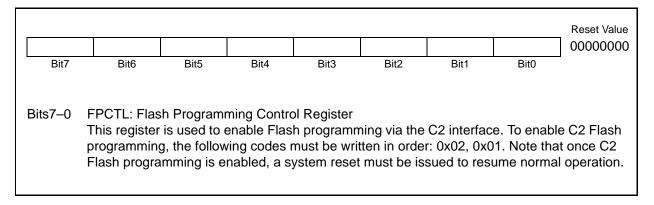

# C2 Register Definition 17.4. FPCTL: C2 Flash Programming Control

## C2 Register Definition 17.5. FPDAT: C2 Flash Programming Data

|          |                            |      |                                                    |                                 |           |             |             | Reset Value |

|----------|----------------------------|------|----------------------------------------------------|---------------------------------|-----------|-------------|-------------|-------------|

| Bit7     | Bit6                       | Bit5 | Bit4                                               | Bit3                            | Bit2      | Bit1        | Bit0        | <b>_</b>    |

| Bits7–0: | FPDAT: C2 F                |      |                                                    |                                 |           |             |             |             |

|          | This register accesses. Va |      |                                                    |                                 | addresses | , and data  | during C2 I | Flash       |

|          | -                          |      | nds are list                                       |                                 | addresses | s, and data | during C2 I | Flash       |

|          | accesses. Va               |      | nds are list<br>Com                                | ed below.                       | addresses | s, and data | during C2 I | Flash       |

|          | accesses. Va               |      | nds are list<br><b>Com</b><br>Flash Bl             | ed below.<br>mand               | addresses | and data    | during C2 I | -lash       |

|          | accesses. Va               |      | nds are list<br><b>Com</b><br>Flash Bl<br>Flash Bl | ed below.<br>Imand<br>lock Read | addresses | and data    | during C2 I | Flash       |