#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 25MHz                                                        |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                  |

| Peripherals                | POR, PWM, WDT                                                |

| Number of I/O              | 8                                                            |

| Program Memory Size        | 4KB (4K x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 256 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | -                                                            |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 10-VFDFN Exposed Pad                                         |

| Supplier Device Package    | 11-QFN (3x3)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f304r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

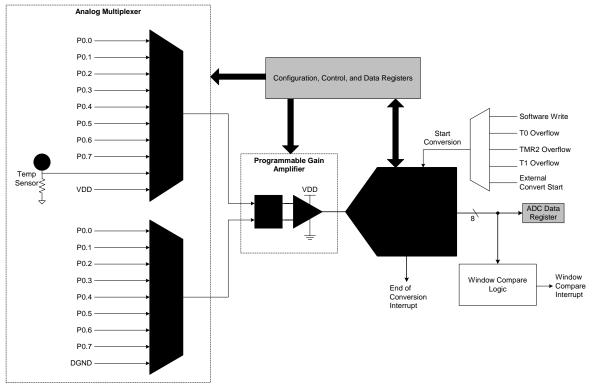

#### 1.7. 8-Bit Analog to Digital Converter (C8051F300/2 Only)

The C8051F300/2 includes an on-chip 8-bit SAR ADC with a 10-channel differential input multiplexer and programmable gain amplifier. With a maximum throughput of 500 ksps, the ADC offers true 8-bit accuracy with an INL of  $\pm$ 1LSB. The ADC system includes a configurable analog multiplexer that selects both positive and negative ADC inputs. Each Port pin is available as an ADC input; additionally, the on-chip Temperature Sensor output and the power supply voltage (V<sub>DD</sub>) are available as ADC inputs. User firmware may shut down the ADC to save power.

The integrated programmable gain amplifier (PGA) amplifies the ADC input by 0.5, 1, 2, or 4 as defined by user software. The gain stage is especially useful when different ADC input channels have widely varied input voltage signals, or when it is necessary to "zoom in" on a signal with a large DC offset.

Conversions can be started in five ways: a software command, an overflow of Timer 0, 1, or 2, or an external convert start signal. This flexibility allows the start of conversion to be triggered by software events, a periodic signal (timer overflows), or external HW signals. Conversion completions are indicated by a status bit and an interrupt (if enabled). The resulting 8-bit data word is latched into an SFR upon completion of a conversion.

Window compare registers for the ADC data can be configured to interrupt the controller when ADC data is either within or outside of a specified range. The ADC can monitor a key voltage continuously in background mode, but not interrupt the controller unless the converted data is within/outside the specified range.

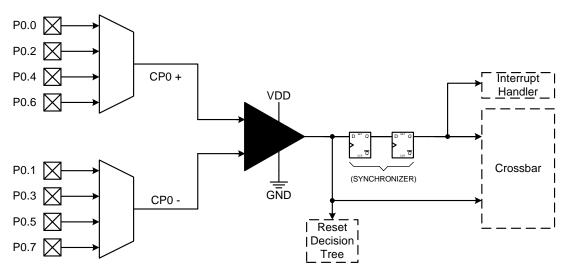

#### 1.8. Comparator

C8051F300/1/2/3/4/5 devices include an on-chip voltage comparator that is enabled/disabled and configured via user software. All Port I/O pins may be configurated as comparator inputs. Two comparator outputs may be routed to a Port pin if desired: a latched output and/or an unlatched (asynchronous) output. Comparator response time is programmable, allowing the user to select between high-speed and lowpower modes. Positive and negative hysteresis is also configurable.

Comparator interrupts may be generated on rising, falling, or both edges. When in IDLE mode, these interrupts may be used as a "wake-up" source. The comparator may also be configured as a reset source.

Figure 1.11. Comparator Block Diagram

### 2. Absolute Maximum Ratings

#### Table 2.1. Absolute Maximum Ratings\*

| Parameter                                                                  | Conditions     | Min        | Тур       | Max        | Units    |

|----------------------------------------------------------------------------|----------------|------------|-----------|------------|----------|

| Ambient temperature under bias                                             |                | -55        |           | 125        | °C       |

| Storage Temperature                                                        |                | -65        | _         | 150        | °C       |

| Voltage on any Port I/O Pin or $\overline{\text{RST}}$ with respect to GND |                | -0.3       | _         | 5.8        | V        |

| Voltage on V <sub>DD</sub> with respect to GND                             |                | -0.3       | _         | 4.2        | V        |

| Maximum Total current through $V_{DD}$ and GND                             |                | _          | _         | 500        | mA       |

| Maximum output current sunk by RST or any Port pin                         |                | _          | _         | 100        | mA       |

| *Note: Stresses above those listed under "Absolute Maximu                  | m Ratings" may | cause perr | manent da | mage to th | e device |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 3. Global Electrical Characteristics

#### Table 3.1. Global Electrical Characteristics

-40 to +85 °C, 25 MHz system clock unless otherwise specified.

| Parameter                                    | Conditions                                      | Min           | Тур     | Мах   | Units  |

|----------------------------------------------|-------------------------------------------------|---------------|---------|-------|--------|

| Digital Supply Voltage                       |                                                 | $V_{RST}^{1}$ | 3.0     | 3.6   | V      |

| Digital Supply RAM Data<br>Retention Voltage |                                                 | —             | 1.5     |       | V      |

| SYSCLK (System Clock)<br>(Note 2)            |                                                 | 0             | _       | 25    | MHz    |

| T <sub>SYSH</sub> (SYSCLK High Time)         |                                                 | 18            | _       | _     | ns     |

| T <sub>SYSL</sub> (SYSCLK Low Time)          |                                                 | 18            | _       | _     | ns     |

| Specified Operating<br>Temperature Range     |                                                 | -40           |         | +85   | °C     |

| Digital Supply Current—CPU                   | Active (Normal Mode, fetching instru            | ctions f      | rom Fla | sh)   |        |

| I <sub>DD</sub> (Note 3)                     | V <sub>DD</sub> = 3.6 V, F = 25 MHz             |               | 9.4     | 10.2  | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 25 MHz             | —             | 6.6     | 7.2   | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 1 MHz              | _             | 0.45    | _     | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 80 kHz             | _             | 36      | _     | μA     |

| I <sub>DD</sub> Supply Sensitivity (Note 3)  | F = 25 MHz                                      | —             | 69      |       | %/V    |

|                                              | F = 1 MHz                                       | _             | 51      | _     | %/V    |

| I <sub>DD</sub> Frequency Sensitivity        | V <sub>DD</sub> = 3.0 V, F <= 15 MHz, T = 25 °C | —             | 0.45    |       | mA/MHz |

| (Note 3, Note 4)                             | V <sub>DD</sub> = 3.0 V, F > 15 MHz, T = 25 °C  | —             | 0.16    | —     | mA/MHz |

|                                              | V <sub>DD</sub> = 3.6 V, F <= 15 MHz, T = 25 °C | —             | 0.69    | —     | mA/MHz |

|                                              | V <sub>DD</sub> = 3.6 V, F > 15 MHz, T = 25 °C  | —             | 0.20    | _     | mA/MHz |

| Digital Supply Current—CPU                   | Inactive (Idle Mode, not fetching instr         | uctions       | from F  | lash) |        |

| I <sub>DD</sub> (Note 3)                     | V <sub>DD</sub> = 3.6 V, F = 25 MHz             | —             | 3.3     | 4.0   | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 25 MHz             | —             | 2.5     | 3.2   | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 1 MHz              | —             | 0.10    | _     | mA     |

|                                              | V <sub>DD</sub> = 3.0 V, F = 80 kHz             | _             | 8       | —     | μA     |

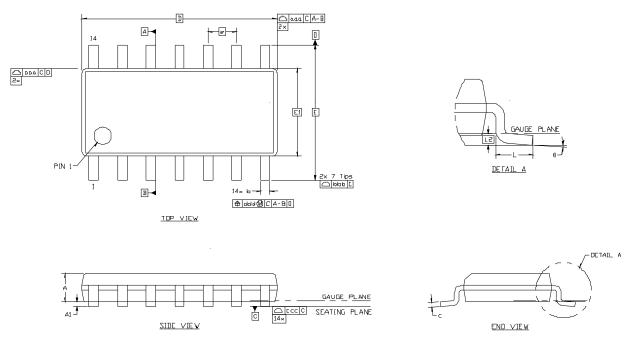

Figure 4.6. SOIC-14 Package Drawing

| Dimension | Min  | Max  | Dimension | Min        | Max        |  |

|-----------|------|------|-----------|------------|------------|--|

| А         |      | 1.75 | L         | 0.40       | 1.27       |  |

| A1        | 0.10 | 0.25 | L2        | 0.25       | BSC        |  |

| b         | 0.33 | 0.51 | Q         | <b>0</b> ° | <b>8</b> ° |  |

| С         | 0.17 | 0.25 | aaa       | 0.10       |            |  |

| D         | 8.65 | BSC  | bbb       | 0.20       |            |  |

| E         | 6.00 | BSC  | CCC       | 0.10       |            |  |

| E1        | 3.90 | BSC  | ddd       | 0.25       |            |  |

| е         | 1.27 | BSC  | LL        |            |            |  |

| lotes:    |      |      |           |            |            |  |

Table 4.4. SOIC-14 Package Dimensions

1. All dimensions shown are in millimeters (mm).

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. This drawing conforms to JEDEC outline MS012, variation AB.

4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

#### 5.3. Modes of Operation

ADC0 has a maximum conversion speed of 500 ksps. The ADC0 conversion clock is a divided version of the system clock, determined by the AD0SC bits in the ADC0CF register (system clock divided by (AD0SC + 1) for  $0 \le AD0SC \le 31$ ).

#### 5.3.1. Starting a Conversion

A conversion can be initiated in one of five ways, depending on the programmed states of the ADC0 Start of Conversion Mode bits (AD0CM2–0) in register ADC0CN. Conversions may be initiated by one of the following:

- 1. Writing a '1' to the AD0BUSY bit of register ADC0CN

- 2. A Timer 0 overflow (i.e. timed continuous conversions)

- 3. A Timer 2 overflow

- 4. A Timer 1 overflow

- 5. A rising edge on the CNVSTR input signal (pin P0.6)

Writing a '1' to AD0BUSY provides software control of ADC0 whereby conversions are performed "ondemand". During conversion, the AD0BUSY bit is set to logic 1 and reset to logic 0 when the conversion is complete. The falling edge of AD0BUSY triggers an interrupt (when enabled) and sets the ADC0 interrupt flag (AD0INT). Note: When polling for ADC conversion completions, the ADC0 interrupt flag (AD0INT) should be used. Converted data is available in the ADC0 data register, ADC0, when bit AD0INT is logic 1. Note that when Timer 2 overflows are used as the conversion source, Timer 2 Low Byte overflows are used if Timer 2 is in 8-bit mode; Timer 2 High byte overflows are used if Timer 2 is in 16-bit mode. See **Section "15. Timers" on page 143** for timer configuration.

**Important Note About Using CNVSTR:** The CNVSTR input pin also functions as Port pin P0.6. When the CNVSTR input is used as the ADC0 conversion source, Port pin P0.6 should be skipped by the Digital Crossbar. To configure the Crossbar to skip P0.6, set to '1' Bit6 in register XBR0. See **Section "12. Port Input/Output" on page 103** for details on Port I/O configuration.

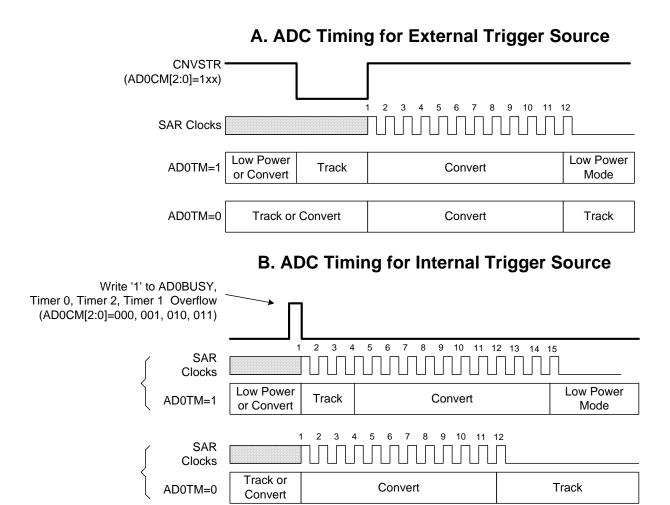

#### 5.3.2. Tracking Modes

According to Table 5.1 on page 47, each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate. The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked except when a conversion is in progress. When the AD0TM bit is logic 1, ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 5.4). Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX or PGA settings are frequently changed, due to the settling time requirements described in **Section "5.3.3. Settling Time Requirements" on page 41**.

Figure 5.4. 8-Bit ADC Track and Conversion Example Timing

| R/W                                                                                                                                                                                                                                                               | R/W                                                                                                                                                | R/W         | R/W          | R/W     | R/W   | R/W   | R/W  | Reset Value  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------|-------|-------|------|--------------|--|--|--|--|

|                                                                                                                                                                                                                                                                   | —                                                                                                                                                  | _           |              | REFSL   | TEMPE | BIASE | _    | 00000000     |  |  |  |  |

| Bit7                                                                                                                                                                                                                                                              | Bit6                                                                                                                                               | Bit5        | Bit4         | Bit3    | Bit2  | Bit1  | Bit0 | SFR Address: |  |  |  |  |

|                                                                                                                                                                                                                                                                   |                                                                                                                                                    |             |              |         |       |       |      | 0xD1         |  |  |  |  |

| Bits7–3: UNUSED. Read = 00000b; Write = don't care.<br>Bit3: REFSL: Voltage Reference Select.<br>This bit selects the source for the internal voltage reference.<br>0: VREF input pin used as voltage reference.<br>1: V <sub>DD</sub> used as voltage reference. |                                                                                                                                                    |             |              |         |       |       |      |              |  |  |  |  |

| Bit2:                                                                                                                                                                                                                                                             | TEMPE: Ten<br>0: Internal Te<br>1: Internal Te                                                                                                     | emperature  | Sensor off.  |         |       |       |      |              |  |  |  |  |

| Bit1:                                                                                                                                                                                                                                                             | BIASE: Internal Analog Bias Generator Enable Bit. (Must be '1' if using ADC).<br>0: Internal Bias Generator off.<br>1: Internal Bias Generator on. |             |              |         |       |       |      |              |  |  |  |  |

| Bit0:                                                                                                                                                                                                                                                             | UNUSED. R                                                                                                                                          | ead = 0b. \ | Vrite = don' | t care. |       |       |      |              |  |  |  |  |

#### SFR Definition 6.1. REF0CN: Reference Control Register

# Table 6.1. External Voltage Reference Circuit Electrical Characteristics $V_{DD} = 3.0 \text{ V}$ ; -40 to +85°C unless otherwise specified.

| Parameter           | Conditions                              | Min | Тур | Max             | Units |

|---------------------|-----------------------------------------|-----|-----|-----------------|-------|

| Input Voltage Range |                                         | 0   | —   | V <sub>DD</sub> | V     |

| Input Current       | Sample Rate = 500 ksps;<br>VREF = 3.0 V | —   | 12  |                 | μA    |

#### 8.2.4. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit 7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination operands as opposed to a byte source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 8.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 8.2.6. Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). The SFRs provide control and data exchange with the CIP-51's resources and peripherals. The CIP-51 duplicates the SFRs found in a typical 8051 implementation as well as implementing additional SFRs used to configure and access the subsystems unique to the MCU. This allows the addition of new functionality while retaining compatibility with the MCS-51<sup>™</sup> instruction set. Table 8.2 lists the SFRs implemented in the CIP-51 System Controller.

The SFR registers are accessed anytime the direct addressing mode is used to access memory locations from 0x80 to 0xFF. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, SCON0, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only. Unoccupied addresses in the SFR space are reserved for future use. Accessing these areas will have an indeterminate effect and should be avoided. Refer to the corresponding pages of the datasheet, as indicated in Table 8.3, for a detailed description of each register.

#### SFR Definition 9.1. RSTSRC: Reset Source

| R        | R                                                                                                                                                         | R/W           | R/W           | R             | R/W                      | R/W          | R            | Reset Value  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|--------------------------|--------------|--------------|--------------|--|--|

|          | FERROR                                                                                                                                                    | CORSEF        | SWRSF         | WDTRSF        | MCDRSF                   | PORSF        | PINRSF       | Variable     |  |  |

| Bit7     | Bit6                                                                                                                                                      | Bit5          | Bit4          | Bit3          | Bit2                     | Bit1         | Bit0         | SFR Address: |  |  |

|          |                                                                                                                                                           |               |               |               |                          |              |              | 0xEF         |  |  |

| (Nata: D | a natura raa                                                                                                                                              | lmodify       | ita anaratio  |               | NIL ) on this            | ragiotar)    |              |              |  |  |

| (Note: D | o not use read                                                                                                                                            | a-modily-wr   | ite operatio  | ons (ORL, A   | INL) ON this             | register)    |              |              |  |  |

| Bit7:    | UNUSED. R                                                                                                                                                 | ead = 0. W    | rite = don't  | care.         |                          |              |              |              |  |  |

| Bit6:    | FERROR: F                                                                                                                                                 | lash Error I  | ndicator.     |               |                          |              |              |              |  |  |

|          | 0: Source of                                                                                                                                              |               |               |               |                          |              |              |              |  |  |

| D        | 1: Source of                                                                                                                                              |               |               |               |                          |              |              |              |  |  |

| Bit5:    | CORSEF: Co<br>Write                                                                                                                                       | omparatoru    | Reset Ena     | able and Fla  | ıg.                      |              |              |              |  |  |

|          | 0: Comparat                                                                                                                                               | or0 is not a  | reset sou     | rce           |                          |              |              |              |  |  |

|          | 1: Comparat                                                                                                                                               |               |               |               |                          |              |              |              |  |  |

|          | Read                                                                                                                                                      |               |               | ( )           |                          |              |              |              |  |  |

|          | 0: Source of                                                                                                                                              |               |               | •             |                          |              |              |              |  |  |

| 5.4      | 1: Source of                                                                                                                                              |               |               |               |                          |              |              |              |  |  |

| Bit4:    | SWRSF: So                                                                                                                                                 | ftware Rese   | et Force ar   | nd Flag.      |                          |              |              |              |  |  |

|          | Write<br>0: No Effect.                                                                                                                                    |               |               |               |                          |              |              |              |  |  |

|          | 1: Forces a                                                                                                                                               |               | et.           |               |                          |              |              |              |  |  |

|          | Read                                                                                                                                                      | ,             |               |               |                          |              |              |              |  |  |

|          | 0: Source of                                                                                                                                              |               |               |               |                          |              |              |              |  |  |

| Dire     | 1: Source of                                                                                                                                              |               |               |               | it.                      |              |              |              |  |  |

| Bit3:    | WDTRSF: W<br>0: Source of                                                                                                                                 | -             |               | -             | +                        |              |              |              |  |  |

|          | 1: Source of                                                                                                                                              |               |               |               | ι.                       |              |              |              |  |  |

| Bit2:    | MCDRSF: M                                                                                                                                                 |               |               |               |                          |              |              |              |  |  |

|          | Write:                                                                                                                                                    | 0             |               | 0             |                          |              |              |              |  |  |

|          | 0: Missing C                                                                                                                                              |               |               |               |                          |              |              |              |  |  |

|          | 1: Missing C                                                                                                                                              | lock Detect   | or enabled    | l; triggers a | reset if a mi            | ssing clock  | condition i  | s detected.  |  |  |

|          | Read:                                                                                                                                                     | lost react y  | vaa nat a N   | liaging Clas  | k Dotootor t             | imaaut       |              |              |  |  |

|          | <ul><li>0: Source of last reset was not a Missing Clock Detector timeout.</li><li>1: Source of last reset was a Missing Clock Detector timeout.</li></ul> |               |               |               |                          |              |              |              |  |  |

| Bit1:    | PORSF: Pov                                                                                                                                                |               |               | -             |                          | 001.         |              |              |  |  |

|          | This bit is se                                                                                                                                            |               |               | •             | s. This may              | be due to a  | a true power | -on reset or |  |  |

|          | a V <sub>DD</sub> monit                                                                                                                                   | or reset. In  | either case   | e, data men   | nory should l            | be conside   | red indeterr | ninate fol-  |  |  |

|          | lowing the re                                                                                                                                             | eset. Writing | g this bit er | nables/disab  | oles the V <sub>DD</sub> | monitor.     |              |              |  |  |

|          | Write:                                                                                                                                                    |               |               |               |                          |              |              |              |  |  |

|          | 0: V <sub>DD</sub> moni                                                                                                                                   |               |               |               |                          |              |              |              |  |  |

|          | 1: V <sub>DD</sub> moni                                                                                                                                   | tor enabled   | •             |               |                          |              |              |              |  |  |

|          | Read:                                                                                                                                                     |               |               |               | 10                       |              |              |              |  |  |

|          | 0: Last reset                                                                                                                                             |               | -             |               |                          | an 1000 ( 1) | ب ا د ا د ا  | in at-       |  |  |

| D:40-    | 1: Last reset                                                                                                                                             | -             |               | DD monitor    | reset; all oth           | er reset fla | igs indetern | imate.       |  |  |

| Bit0:    | PINRSF: HV<br>0: Source of                                                                                                                                |               |               |               |                          |              |              |              |  |  |

|          | 1: Source of                                                                                                                                              |               |               | •             |                          |              |              |              |  |  |

|          | 1: Source of                                                                                                                                              | iast reset v  | vas KST p     | in.           |                          |              |              |              |  |  |

| -40 to +65 °C unless otherwise specified                      |                                      |      |      |     |       |  |  |  |  |  |  |

|---------------------------------------------------------------|--------------------------------------|------|------|-----|-------|--|--|--|--|--|--|

| Parameter                                                     | Conditions                           | Min  | Тур  | Max | Units |  |  |  |  |  |  |

| Calibrated Internal Oscillator                                | C8051F300/1 devices<br>-40 to +85 °C | 24   | 24.5 | 25  | MHz   |  |  |  |  |  |  |

| Frequency                                                     | C8051F300/1 devices<br>0 to +70 °C   | 24.3 | 24.7 | 25  | MHz   |  |  |  |  |  |  |

| Uncalibrated Internal Oscillator<br>Frequency                 | C8051F302/3/4/5 devices              | 16   | 20   | 24  | MHz   |  |  |  |  |  |  |

| Internal Oscillator Supply Current<br>(from V <sub>DD</sub> ) | OSCICN.2 = 1                         |      | 450  |     | μA    |  |  |  |  |  |  |

#### Table 11.1. Internal Oscillator Electrical Characteristics

#### 11.2. External Oscillator Drive Circuit

-40 to +85 °C unless otherwise specified

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 11.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 11.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 11.3).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are occupied as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is occupied as XTAL2. The Port I/O Crossbar should be configured to skip the occupied Port pins; see **Section "12.1. Priority Crossbar Decoder" on page 104** for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See **Section "12.2. Port I/O Initialization" on page 106** for details on Port input mode selection.

#### 11.3. System Clock Selection

The CLKSL bit in register OSCICN selects which oscillator is used as the system clock. CLKSL must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no start-up time.

#### 11.5. External RC Example

If an RC network is used as an external oscillator source for the MCU, the circuit should be configured as shown in Figure 11.1, Option 2. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 k $\Omega$  and C = 50 pF:

$f = 1.23(10^3) / RC = 1.23(10^3) / [246 \times 50] = 0.1 MHz = 100 kHz$

Referring to the table in SFR Definition 11.3, the required XFCN setting is 010b.

#### 11.6. External Capacitor Example

If a capacitor is used as an external oscillator for the MCU, the circuit should be configured as shown in Figure 11.1, Option 3. The capacitor should be no greater than 100 pF; however for very small capacitors, the total capacitance may be dominated by parasitic capacitance in the PCB layout. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume  $V_{DD} = 3.0$  V and f = 150 kHz:

$f = KF / (C \times VDD)$

0.150 MHz = KF / (C x 3.0)

Since the frequency of roughly 150 kHz is desired, select the K Factor from the table in SFR Definition 11.3 as KF = 22:

0.150 MHz = 22 / (C x 3.0)

C x 3.0 = 22 / 0.150 MHz

C = 146.6 / 3.0 pF = 48.8 pF

Therefore, the XFCN value to use in this example is 011b and C = 50 pF.

| SFR Definition 1 | 13.2. \$ | SMB0CN: | SMBus | Control |

|------------------|----------|---------|-------|---------|

|------------------|----------|---------|-------|---------|

| R     | R                                                                                             | R/W         | R/W         | R              | R               | R/W           | R/W         | Reset Value     |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------|-------------|-------------|----------------|-----------------|---------------|-------------|-----------------|--|--|--|--|

| MASTE | R TXMODE                                                                                      | STA         | STO         | ACKRQ          | ARBLOST         | ACK           | SI          | 00000000        |  |  |  |  |

| Bit7  | Bit6                                                                                          | Bit5        | Bit4        | Bit3           | Bit2            | Bit1          | Bit0        | SFR Address:    |  |  |  |  |

|       |                                                                                               |             |             |                |                 | (bit          | addressable | e) 0xC0         |  |  |  |  |

| D:/-7 |                                                                                               |             | ( )0        |                |                 |               |             |                 |  |  |  |  |

| Bit7: | MASTER: SI                                                                                    |             |             |                |                 |               |             |                 |  |  |  |  |

|       |                                                                                               | •           |             |                | s is operating  | as a masi     | er.         |                 |  |  |  |  |

|       | 0: SMBus op<br>1: SMBus op                                                                    | -           |             |                |                 |               |             |                 |  |  |  |  |

| Bit6: | TXMODE: S                                                                                     | •           |             |                |                 |               |             |                 |  |  |  |  |

| Dito. |                                                                                               |             |             |                | s is operating  | as a trans    | mitter      |                 |  |  |  |  |

|       | 0: SMBus in                                                                                   | •           |             |                | o operating     |               |             |                 |  |  |  |  |

|       | 1: SMBus in                                                                                   |             |             |                |                 |               |             |                 |  |  |  |  |

| Bit5: | STA: SMBus                                                                                    |             |             |                |                 |               |             |                 |  |  |  |  |

|       | Write:                                                                                        |             | •           |                |                 |               |             |                 |  |  |  |  |

|       | 0: No Start g                                                                                 | enerated.   |             |                |                 |               |             |                 |  |  |  |  |

|       | 1: When ope                                                                                   | rating as a | a master, a | START co       | ndition is tran | smitted if t  | he bus is   | free (If the bu |  |  |  |  |

|       |                                                                                               |             |             |                |                 |               |             | ut is detected) |  |  |  |  |

|       | If STA is set by software as an active Master, a repeated START will be generated after the   |             |             |                |                 |               |             |                 |  |  |  |  |

|       | next ACK cy                                                                                   | cle.        |             |                |                 |               |             |                 |  |  |  |  |

|       | Read:<br>0: No Start or repeated Start detected.                                              |             |             |                |                 |               |             |                 |  |  |  |  |

|       |                                                                                               | •           |             |                |                 |               |             |                 |  |  |  |  |

| Bit4: | 1: Start or re                                                                                | •           |             | α.             |                 |               |             |                 |  |  |  |  |

| DIL4. | STO: SMBus<br>Write:                                                                          | S Slop Flag | y.          |                |                 |               |             |                 |  |  |  |  |

|       | As a master, setting this bit to '1' causes a STOP condition to be transmitted after the next |             |             |                |                 |               |             |                 |  |  |  |  |

|       | ACK cycle. STO is cleared to '0' by hardware when the STOP is generated.                      |             |             |                |                 |               |             |                 |  |  |  |  |

|       | •                                                                                             |             |             | •              |                 | -             |             | Slave Trans-    |  |  |  |  |

|       | mitter mode.                                                                                  |             | -           |                | -               |               |             |                 |  |  |  |  |

|       | Read:                                                                                         |             |             |                |                 |               |             |                 |  |  |  |  |

|       | 0: No Stop c                                                                                  | ondition de | etected.    |                |                 |               |             |                 |  |  |  |  |

|       |                                                                                               |             |             |                | or pending (    | if in Maste   | r Mode).    |                 |  |  |  |  |

| Bit3: | ACKRQ: SM                                                                                     |             | -           |                |                 |               |             |                 |  |  |  |  |

|       |                                                                                               |             |             |                |                 | eceived a b   | byte and r  | needs the AC    |  |  |  |  |

|       | bit to be writt                                                                               |             |             | •              |                 |               |             |                 |  |  |  |  |

| Bit2: | ARBLOST: S                                                                                    |             |             |                |                 | o ub itration | سيام م      | arating on a    |  |  |  |  |

|       |                                                                                               | •           | -           |                | SMBus loses     |               | •           | erating as a    |  |  |  |  |

| Bit1: | ACK: SMBus                                                                                    |             |             |                | uicales a bus   |               | ulion.      |                 |  |  |  |  |

| DILT. |                                                                                               |             |             |                | records incor   |               | lovels It a | should be writ  |  |  |  |  |

|       |                                                                                               |             |             |                |                 | -             |             | s transmitted.  |  |  |  |  |

|       |                                                                                               |             |             |                |                 |               |             | transmitted (   |  |  |  |  |

|       | in Receiver M                                                                                 |             |             |                |                 |               |             | (               |  |  |  |  |

|       |                                                                                               | ,           | as been re  | eceived (if ir | n Transmitter   | Mode) OR      | will be tr  | ansmitted (if i |  |  |  |  |

|       | Receiver Mo                                                                                   | -           |             | Ň              |                 | ,             |             | ,               |  |  |  |  |

| Bit0: | SI: SMBus Ir                                                                                  | nterrupt Fl | ag.         |                |                 |               |             |                 |  |  |  |  |

|       |                                                                                               |             |             | the conditi    | ons listed in T | Table 13.3.   | SI must l   | be cleared by   |  |  |  |  |

|       | software. Wh                                                                                  |             |             |                |                 |               |             |                 |  |  |  |  |

|                   | Values Read      |       |         | k   | Current SMbus State                                                                   | Typical Response Options                                                                        |     | /alue<br>Vritte | -   |

|-------------------|------------------|-------|---------|-----|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|-----------------|-----|

| Mode              | Status<br>Vector | ACKRQ | ARBLOST | ACK |                                                                                       |                                                                                                 | STA | STO             | ACK |

|                   | 1000             | 1     | 0       | Х   | A master data byte was received;<br>ACK requested.                                    | Acknowledge received byte;<br>Read SMB0DAT.                                                     | 0   | 0               | 1   |

|                   |                  |       |         |     |                                                                                       | Send NACK to indicate last byte, and send STOP.                                                 | 0   | 1               | 0   |

| ĸ                 |                  |       |         |     |                                                                                       | Send NACK to indicate last<br>byte, and send STOP fol-<br>lowed by START.                       | 1   | 1               | 0   |

| CEIVE             |                  |       |         |     |                                                                                       | Send ACK followed by<br>repeated START.                                                         | 1   | 0               | 1   |

| MASTER RECEIVER   |                  |       |         |     |                                                                                       | Send NACK to indicate last<br>byte, and send repeated<br>START.                                 | 1   | 0               | 0   |

| MAS               |                  |       |         |     |                                                                                       | Send ACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI).  | 0   | 0               | 1   |

|                   |                  |       |         |     |                                                                                       | Send NACK and switch to<br>Master Transmitter Mode<br>(write to SMB0DAT before<br>clearing SI). | 0   | 0               | 0   |

| TER               | 0100             | 0     | 0       | 0   | A slave byte was transmitted;<br>NACK received.                                       | No action required (expect-<br>ing STOP condition).                                             | 0   | 0               | Х   |

| ISMIT             |                  | 0     | 0       | 1   | A slave byte was transmitted;<br>ACK received.                                        | Load SMB0DAT with next data byte to transmit.                                                   | 0   | 0               | Х   |

| TRAN              |                  | 0     | 1       | Х   | A Slave byte was transmitted;<br>error detected.                                      | No action required (expect-<br>ing Master to end transfer).                                     | 0   | 0               | Х   |

| SLAVE TRANSMITTER | 0101             | 0     | Х       | Х   | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | Clear STO.                                                                                      | 0   | 0               | X   |

#### Table 13.4. SMBus Status Decoding (Continued)

|                | Values Read                                                |                                                                                                                                                                         | k                                                                                     | Current SMbus State | Typical Response Options                                                            |                                                                                                                                                                         | /alue<br>Vritte |     |     |

|----------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|

| Mode           | Status<br>Vector                                           | ACKRQ                                                                                                                                                                   | ARBLOST                                                                               | ACK                 |                                                                                     |                                                                                                                                                                         | STA             | STO | ACK |

|                | 0010 1 0 X A slave address was received;<br>ACK requested. |                                                                                                                                                                         | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ). | 0                   | 0                                                                                   | 1                                                                                                                                                                       |                 |     |     |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0               | 0   | 0   |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0               | 0   | 1   |

|                |                                                            | 1                                                                                                                                                                       | 1                                                                                     | X                   | Lost arbitration as master; slave<br>address received; ACK<br>requested.            | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0               | 0   | 1   |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0               | 0   | 0   |

| SLAVE RECEIVER |                                                            | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0                                                                                     | 0                   | 1                                                                                   |                                                                                                                                                                         |                 |     |     |

| SL/            |                                                            |                                                                                                                                                                         |                                                                                       |                     |                                                                                     | Reschedule failed transfer;<br>do not acknowledge received<br>address                                                                                                   | 1               | 0   | 0   |

|                | 0010                                                       | 0                                                                                                                                                                       | 1                                                                                     | Х                   | Lost arbitration while attempting a                                                 | Abort failed transfer.                                                                                                                                                  | 0               | 0   | Х   |

|                | 0001                                                       |                                                                                                                                                                         |                                                                                       | V                   | repeated START.                                                                     | Reschedule failed transfer.                                                                                                                                             | 1               | 0   | X   |

|                | 0001                                                       | 1                                                                                                                                                                       | 1                                                                                     |                     | Lost arbitration while attempting a STOP.                                           | complete/aborted).                                                                                                                                                      | 0               | 0   | 0   |

|                |                                                            | 0                                                                                                                                                                       | 0                                                                                     |                     | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver. | Clear STO.                                                                                                                                                              | 0               | 0   | X   |

|                |                                                            | 0                                                                                                                                                                       | 1                                                                                     | Х                   |                                                                                     | Abort transfer.                                                                                                                                                         | 0               | 0   | Х   |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     | STOP.                                                                               | Reschedule failed transfer.                                                                                                                                             | 1               | 0   | X   |

|                | 0000                                                       | 1                                                                                                                                                                       | 0                                                                                     | X                   | A slave byte was received; ACK requested.                                           | Acknowledge received byte;<br>Read SMB0DAT.                                                                                                                             | 0               | 0   | 1   |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     |                                                                                     | Do not acknowledge received byte.                                                                                                                                       | 0               | 0   | 0   |

|                |                                                            | 1                                                                                                                                                                       | 1                                                                                     | х                   | Lost arbitration while transmitting                                                 | Abort failed transfer.                                                                                                                                                  | 0               | 0   | 0   |

|                |                                                            |                                                                                                                                                                         |                                                                                       |                     | a data byte as master.                                                              | Reschedule failed transfer.                                                                                                                                             | 1               | 0   | 0   |

#### Table 13.4. SMBus Status Decoding (Continued)

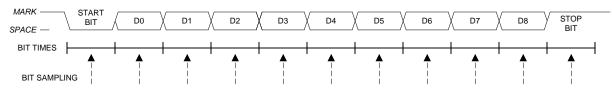

#### 14.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic 0, and (2) if MCE0 is logic 1, the 9th bit must be logic 1 (when MCE0 is logic 0, the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to '1'. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to '1'.

Figure 14.5. 9-Bit UART Timing Diagram

| Table 14.6. Timer Settings for Standard Baud Rates Using an External 3.6864 MHZ |

|---------------------------------------------------------------------------------|

| Oscillator                                                                      |

|                              | Frequency: 3.6864 MHz        |                      |                                |                       |                                                 |                  |                                  |  |  |  |  |

|------------------------------|------------------------------|----------------------|--------------------------------|-----------------------|-------------------------------------------------|------------------|----------------------------------|--|--|--|--|

|                              | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscillator<br>Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale<br>select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |

| SYSCLK from<br>External Osc. | 230400                       | 0.00%                | 16                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xF8                             |  |  |  |  |

|                              | 115200                       | 0.00%                | 32                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xF0                             |  |  |  |  |

|                              | 57600                        | 0.00%                | 64                             | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xE0                             |  |  |  |  |

|                              | 28800                        | 0.00%                | 128                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0xC0                             |  |  |  |  |

|                              | 14400                        | 0.00%                | 256                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x80                             |  |  |  |  |

|                              | 9600                         | 0.00%                | 384                            | SYSCLK                | XX <sup>2</sup>                                 | 1                | 0x40                             |  |  |  |  |

|                              | 2400                         | 0.00%                | 1536                           | SYSCLK / 12           | 00                                              | 0                | 0xC0                             |  |  |  |  |

|                              | 1200                         | 0.00%                | 3072                           | SYSCLK / 12           | 00                                              | 0                | 0x80                             |  |  |  |  |

| SYSCLK from<br>Internal Osc. | 230400                       | 0.00%                | 16                             | EXTCLK / 8            | 11                                              | 0                | 0xFF                             |  |  |  |  |

|                              | 115200                       | 0.00%                | 32                             | EXTCLK / 8            | 11                                              | 0                | 0xFE                             |  |  |  |  |

|                              | 57600                        | 0.00%                | 64                             | EXTCLK / 8            | 11                                              | 0                | 0xFC                             |  |  |  |  |

|                              | 28800                        | 0.00%                | 128                            | EXTCLK / 8            | 11                                              | 0                | 0xF8                             |  |  |  |  |

|                              | 14400                        | 0.00%                | 256                            | EXTCLK / 8            | 11                                              | 0                | 0xF0                             |  |  |  |  |

|                              | 9600                         | 0.00%                | 384                            | EXTCLK / 8            | 11                                              | 0                | 0xE8                             |  |  |  |  |

Notes:

1. SCA1–SCA0 and T1M bit definitions can be found in **Section 15.1**.

2. X = Don't care

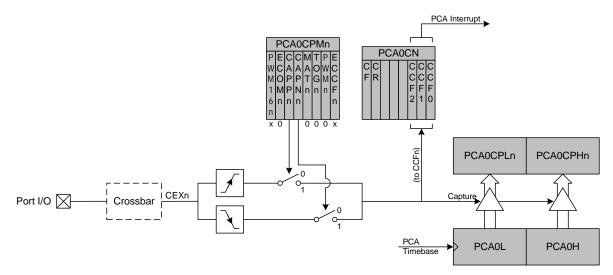

#### 16.2.1. Edge-triggered Capture Mode

In this mode, a valid transition on the CEXn pin causes the PCA to capture the value of the PCA counter/ timer and copy it into the corresponding module's 16-bit capture/compare register (PCA0CPLn and PCA0CPHn). The CAPPn and CAPNn bits in the PCA0CPMn register are used to select the type of transition that triggers the capture: low-to-high transition (positive edge), high-to-low transition (negative edge), or either transition (positive or negative edge). When a capture occurs, the Capture/Compare Flag (CCFn) in PCA0CN is set to logic 1 and an interrupt request is generated if CCF interrupts are enabled. The CCFn bit is not automatically cleared by hardware when the CPU vectors to the interrupt service routine, and must be cleared by software. If both CAPPn and CAPNn bits are set to logic 1, then the state of the Port pin associated with CEXn can be read directly to determine whether a rising-edge or falling-edge caused the capture.

Figure 16.4. PCA Capture Mode Diagram

Note: The CEXn input signal must remain high or low for at least 2 system clock cycles to be recognized by the hardware.

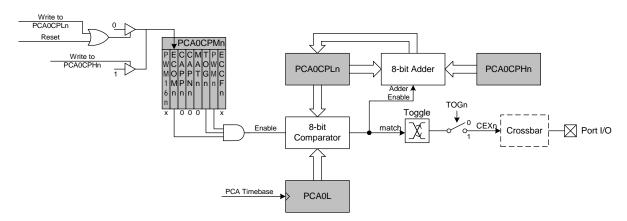

#### 16.2.4. Frequency Output Mode

Frequency Output Mode produces a programmable-frequency square wave on the module's associated CEXn pin. The capture/compare module high byte holds the number of PCA clocks to count before the output is toggled. The frequency of the square wave is then defined by Equation 16.1.

$$F_{CEXn} = \frac{F_{PCA}}{2 \times PCA0CPHn}$$

#### **Equation 16.1. Square Wave Frequency Output**

Where  $F_{PCA}$  is the frequency of the clock selected by the CPS2–0 bits in the PCA mode register, PCA0MD. The lower byte of the capture/compare module is compared to the PCA counter low byte; on a match, CEXn is toggled and the offset held in the high byte is added to the matched value in PCA0CPLn. Frequency Output Mode is enabled by setting the ECOMn, TOGn, and PWMn bits in the PCA0CPMn register.

Figure 16.7. PCA Frequency Output Mode

#### SFR Definition 16.3. PCA0CPMn: PCA Capture/Compare Mode

| R/W                                                                                 | R/W                                                                                                                                                                                    | R/W           | R/W          | R/W         | R/W           | R/W         | R/W         | Reset Value      |  |  |  |  |

|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|-------------|---------------|-------------|-------------|------------------|--|--|--|--|

| PWM16                                                                               |                                                                                                                                                                                        | CAPPn         | CAPNn        | MATn        | TOGn          | PWMn        | ECCFn       | 00000000         |  |  |  |  |