Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Last Time Buy                                                  |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), UART/USART                    |

| Peripherals                | POR, PWM, WDT                                                  |

| Number of I/O              | 8                                                              |

| Program Memory Size        | 2KB (2K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                 |

| Supplier Device Package    | 14-SOIC                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f305-gs |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Registers

| SFR Definition 5.1. AMX0SL: AMUX0 Channel Select (C8051F300/2)        | 42  |

|-----------------------------------------------------------------------|-----|

| SFR Definition 5.2. ADC0CF: ADC0 Configuration (C8051F300/2)          | 43  |

| SFR Definition 5.3. ADC0: ADC0 Data Word (C8051F300/2)                | 43  |

| SFR Definition 5.4. ADC0CN: ADC0 Control (C8051F300/2)                | 44  |

| SFR Definition 5.5. ADC0GT: ADC0 Greater-Than Data Byte (C8051F300/2) | 46  |

| SFR Definition 5.6. ADC0LT: ADC0 Less-Than Data Byte (C8051F300/2)    | 46  |

| SFR Definition 6.1. REF0CN: Reference Control Register                | 50  |

| SFR Definition 7.1. CPT0CN: Comparator0 Control                       |     |

| SFR Definition 7.2. CPT0MX: Comparator0 MUX Selection                 | 54  |

| SFR Definition 7.3. CPT0MD: Comparator0 Mode Selection                | 54  |

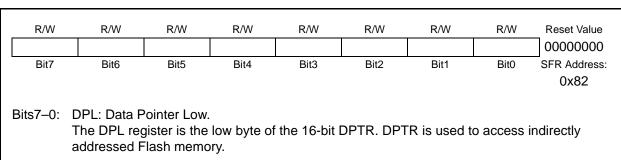

| SFR Definition 8.1. DPL: Data Pointer Low Byte                        |     |

| SFR Definition 8.2. DPH: Data Pointer High Byte                       | 69  |

| SFR Definition 8.3. SP: Stack Pointer                                 | 69  |

| SFR Definition 8.4. PSW: Program Status Word                          | 70  |

| SFR Definition 8.5. ACC: Accumulator                                  | 71  |

| SFR Definition 8.6. B: B Register                                     | 71  |

| SFR Definition 8.7. IE: Interrupt Enable                              | 75  |

| SFR Definition 8.8. IP: Interrupt Priority                            | 76  |

| SFR Definition 8.9. EIE1: Extended Interrupt Enable 1                 | 77  |

| SFR Definition 8.10. EIP1: Extended Interrupt Priority 1              | 78  |

| SFR Definition 8.11. IT01CF: INT0/INT1 Configuration                  |     |

| SFR Definition 8.12. PCON: Power Control                              |     |

| SFR Definition 9.1. RSTSRC: Reset Source                              | 87  |

| SFR Definition 10.1. PSCTL: Program Store R/W Control                 | 92  |

| SFR Definition 10.2. FLKEY: Flash Lock and Key                        |     |

| SFR Definition 10.3. FLSCL: Flash Scale                               |     |

| SFR Definition 11.1. OSCICL: Internal Oscillator Calibration          | 98  |

| SFR Definition 11.2. OSCICN: Internal Oscillator Control              |     |

| SFR Definition 11.3. OSCXCN: External Oscillator Control              | 100 |

| SFR Definition 12.1. XBR0: Port I/O Crossbar Register 0               |     |

| SFR Definition 12.2. XBR1: Port I/O Crossbar Register 1               |     |

| SFR Definition 12.3. XBR2: Port I/O Crossbar Register 2               | 108 |

| SFR Definition 12.4. P0: Port0 Register                               |     |

| SFR Definition 12.5. P0MDIN: Port0 Input Mode                         |     |

| SFR Definition 12.6. P0MDOUT: Port0 Output Mode                       |     |

| SFR Definition 13.1. SMB0CF: SMBus Clock/Configuration                | 118 |

| SFR Definition 13.2. SMB0CN: SMBus Control                            |     |

| SFR Definition 13.3. SMB0DAT: SMBus Data                              |     |

| SFR Definition 14.1. SCON0: Serial Port 0 Control                     |     |

| SFR Definition 14.2. SBUF0: Serial (UART0) Port Data Buffer           |     |

| SFR Definition 15.1. TCON: Timer Control                              |     |

| SFR Definition 15.2. TMOD: Timer Mode                                 |     |

| SFR Definition 15.3. CKCON: Clock Control                             | 149 |

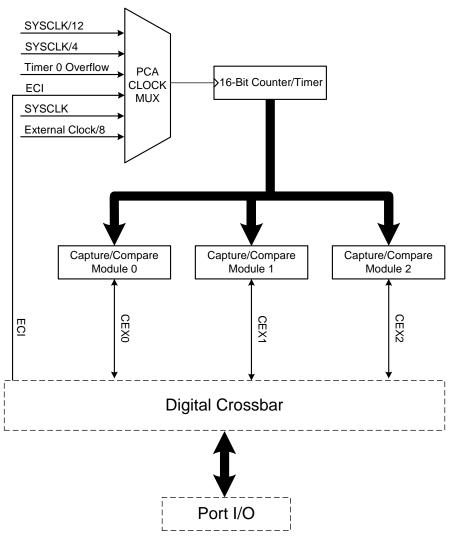

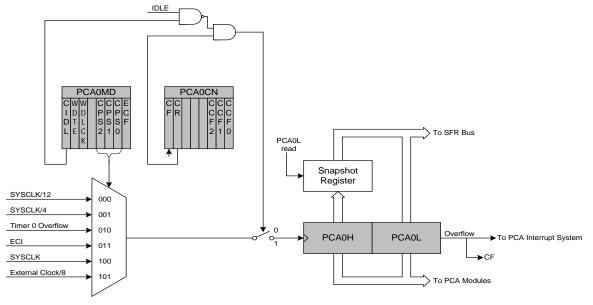

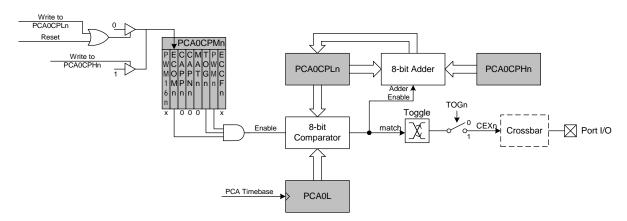

#### **1.6.** Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the three 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or the external oscillator clock source divided by 8. The external clock source selection is useful for real-time clock functionality, where the PCA is clocked by an external source while the internal oscillator drives the system clock.

Each capture/compare module can be configured to operate in one of six modes: Edge-Triggered Capture, Software Timer, High Speed Output, 8- or 16-bit Pulse Width Modulator, or Frequency Output. Additionally, Capture/Compare Module 2 offers watchdog timer (WDT) capabilities. Following a system reset, Module 2 is configured and enabled in WDT mode. The PCA Capture/Compare Module I/O and External Clock Input may be routed to Port I/O via the Digital Crossbar.

Figure 1.9. PCA Block Diagram

# C8051F300/1/2/3/4/5

# 2. Absolute Maximum Ratings

### Table 2.1. Absolute Maximum Ratings\*

| Parameter                                                                  | Conditions     | Min        | Тур       | Max        | Units    |

|----------------------------------------------------------------------------|----------------|------------|-----------|------------|----------|

| Ambient temperature under bias                                             |                | -55        |           | 125        | °C       |

| Storage Temperature                                                        |                | -65        | _         | 150        | °C       |

| Voltage on any Port I/O Pin or $\overline{\text{RST}}$ with respect to GND |                | -0.3       | _         | 5.8        | V        |

| Voltage on V <sub>DD</sub> with respect to GND                             |                | -0.3       | _         | 4.2        | V        |

| Maximum Total current through $V_{DD}$ and GND                             |                | _          | _         | 500        | mA       |

| Maximum output current sunk by RST or any Port pin                         |                | _          | _         | 100        | mA       |

| *Note: Stresses above those listed under "Absolute Maximu                  | m Ratings" may | cause perr | manent da | mage to th | e device |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

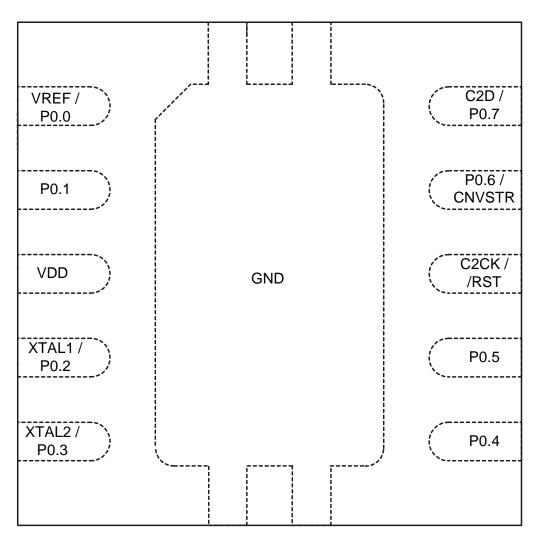

Figure 4.1. QFN-11 Pinout Diagram (Top View)

**CIP-51 Instruction Set Summary**, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 8.1.2. MOVX Instruction and Program Memory

The MOVX instruction is typically used to access external data memory (Note: the C8051F300/1/2/3/4/5 does not support external data or program memory). In the CIP-51, the MOVX instruction accesses the onchip program memory space implemented as re-programmable Flash memory. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to **Section "10. Flash Memory" on page 89** for further details.

| Mnemonic       | Description                              | Bytes | Clock<br>Cycles |

|----------------|------------------------------------------|-------|-----------------|

|                | Arithmetic Operations                    |       |                 |

| ADD A, Rn      | Add register to A                        | 1     | 1               |

| ADD A, direct  | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri     | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data   | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn     | Add register to A with carry             | 1     | 1               |

| ADDC A, direct | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri    | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data  | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn     | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri    | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data  | Subtract immediate from A with borrow    | 2     | 2               |

| INC A          | Increment A                              | 1     | 1               |

| INC Rn         | Increment register                       | 1     | 1               |

| INC direct     | Increment direct byte                    | 2     | 2               |

| INC @Ri        | Increment indirect RAM                   | 1     | 2               |

| DEC A          | Decrement A                              | 1     | 1               |

| DEC Rn         | Decrement register                       | 1     | 1               |

| DEC direct     | Decrement direct byte                    | 2     | 2               |

| DEC @Ri        | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR       | Increment Data Pointer                   | 1     | 1               |

| MUL AB         | Multiply A and B                         | 1     | 4               |

| DIV AB         | Divide A by B                            | 1     | 8               |

| DA A           | Decimal adjust A                         | 1     | 1               |

|                | Logical Operations                       |       |                 |

| ANL A, Rn      | AND Register to A                        | 1     | 1               |

| ANL A, direct  | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri     | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data   | AND immediate to A                       | 2     | 2               |

#### Table 8.1. CIP-51 Instruction Set Summary

| F8 | CPT0CN            | PCA0L    | PCA0H    | PCA0CPL0 | PCA0CPH0 |        |        |        |

|----|-------------------|----------|----------|----------|----------|--------|--------|--------|

| F0 | В                 | P0MDIN   |          |          |          |        | EIP1   |        |

| E8 | ADC0CN            | PCA0CPL1 | PCA0CPH1 | PCA0CPL2 | PCA0CPH2 |        |        | RSTSRC |

| E0 | ACC               | XBR0     | XBR1     | XBR2     | IT01CF   |        | EIE1   |        |

| D8 | PCA0CN            | PCA0MD   | PCA0CPM0 | PCA0CPM1 | PCA0CPM2 |        |        |        |

| D0 | PSW               | REF0CN   |          |          |          |        |        |        |

| C8 | TMR2CN            |          | TMR2RLL  | TMR2RLH  | TMR2L    | TMR2H  |        |        |

| C0 | SMB0CN            | SMB0CF   | SMB0DAT  |          | ADC0GT   |        | ADC0LT |        |

| B8 | IP                |          |          | AMX0SL   | ADC0CF   |        | ADC0   |        |

| B0 |                   | OSCXCN   | OSCICN   | OSCICL   |          |        | FLSCL  | FLKEY  |

| A8 | IE                |          |          |          |          |        |        |        |

| A0 |                   |          |          |          | POMDOUT  |        |        |        |

| 98 | SCON0             | SBUF0    |          |          |          | CPT0MD |        | CPT0MX |

| 90 |                   |          |          |          |          |        |        |        |

| 88 | TCON              | TMOD     | TL0      | TL1      | TH0      | TH1    | CKCON  | PSCTL  |

| 80 | P0                | SP       | DPL      | DPH      |          |        |        | PCON   |

| •  | 0(8)              | 1(9)     | 2(A)     | 3(B)     | 4(C)     | 5(D)   | 6(E)   | 7(F)   |

|    | (hit addragaable) |          |          |          |          |        |        |        |

## Table 8.2. Special Function Register (SFR) Memory Map

(bit addressable)

### Table 8.3. Special Function Registers\*

| Register      | Address             | Description                                             | Page<br>No. |

|---------------|---------------------|---------------------------------------------------------|-------------|

| ACC           | 0xE0                | Accumulator                                             | 71          |

| ADC0CF        | 0xBC                | ADC0 Configuration                                      | 43          |

| ADC0CN        | 0xE8                | ADC0 Control                                            | 44          |

| ADC0GT        | 0xC4                | ADC0 Greater-Than Compare Word                          | 46          |

| ADC0LT        | 0xC6                | ADC0 Less-Than Compare Word                             | 46          |

| ADC0          | 0xBE                | ADC0 Data Word                                          | 43          |

| AMX0SL        | 0xBB                | ADC0 Multiplexer Channel Select                         | 42          |

| В             | 0xF0                | B Register                                              | 71          |

| CKCON         | 0x8E                | Clock Control                                           | 149         |

| CPT0CN        | 0xF8                | Comparator0 Control                                     | 53          |

| CPT0MD        | 0x9D                | Comparator0 Mode Selection                              | 54          |

| CPT0MX        | 0x9F                | Comparator0 MUX Selection                               | 54          |

| DPH           | 0x83                | Data Pointer High                                       | 69          |

| DPL           | 0x82                | Data Pointer Low                                        | 68          |

| EIE1          | 0xE6                | Extended Interrupt Enable 1                             | 77          |

| EIP1          | 0xF6                | External Interrupt Priority 1                           | 78          |

| FLKEY         | 0xB7                | Flash Lock and Key                                      | 93          |

| *Note: SFRs a | are listed in alpha | betical order. All undefined SFR locations are reserved |             |

| Register Address |                    | Description                                              | Page<br>No. |

|------------------|--------------------|----------------------------------------------------------|-------------|

| FLSCL            | 0xB6               | Flash Scale                                              | 93          |

| IE               | 0xA8               | Interrupt Enable                                         | 75          |

| IP               | 0xB8               | Interrupt Priority                                       | 76          |

| IT01CF           | 0xE4               | INT0/INT1 Configuration Register                         | 79          |

| OSCICL           | 0xB3               | Internal Oscillator Calibration                          | 98          |

| OSCICN           | 0xB2               | Internal Oscillator Control                              | 98          |

| OSCXCN           | 0xB1               | External Oscillator Control                              | 100         |

| P0               | 0x80               | Port 0 Latch                                             | 109         |

| POMDIN           | 0xF1               | Port 0 Input Mode Configuration                          | 109         |

| POMDOUT          | 0xA4               | Port 0 Output Mode Configuration                         | 110         |

| PCA0CN           | 0xD8               | PCA Control                                              | 167         |

| PCA0MD           | 0xD9               | PCA Mode                                                 | 168         |

| PCA0CPH0         | 0xFC               | PCA Capture 0 High                                       | 171         |

| PCA0CPH1         | 0xEA               | PCA Capture 1 High                                       | 171         |

| PCA0CPH2         | 0xEC               | PCA Capture 2 High                                       | 171         |

| PCA0CPL0         | 0xFB               | PCA Capture 0 Low                                        | 171         |

| PCA0CPL1         | 0xE9               | PCA Capture 1 Low                                        | 171         |

| PCA0CPL2         | 0xEB               | PCA Capture 2 Low                                        | 171         |

| PCA0CPM0         | 0xDA               | PCA Module 0 Mode Register                               | 169         |

| PCA0CPM1         | 0xDB               | PCA Module 1 Mode Register                               | 169         |

| PCA0CPM2         | 0xDC               | PCA Module 2 Mode Register                               | 169         |

| PCA0H            | 0xFA               | PCA Counter High                                         | 170         |

| PCA0L            | 0xF9               | PCA Counter Low                                          | 170         |

| PCON             | 0x87               | Power Control                                            | 81          |

| PSCTL            | 0x8F               | Program Store R/W Control                                | 92          |

| PSW              | 0xD0               | Program Status Word                                      | 70          |

| REF0CN           | 0xD1               | Voltage Reference Control                                | 49          |

| RSTSRC           | 0xEF               | Reset Source Configuration/Status                        | 87          |

| SBUF0            | 0x99               | UART 0 Data Buffer                                       | 137         |

| SCON0            | 0x98               | UART 0 Control                                           | 136         |

| SMB0CF           | 0xC1               | SMBus Configuration                                      | 118         |

| SMB0CN           | 0xC0               | SMBus Control                                            | 120         |

| SMB0DAT          | 0xC2               | SMBus Data                                               | 122         |

| SP               | 0x81               | Stack Pointer                                            | 69          |

| TMR2CN           | 0xC8               | Timer/Counter 2 Control                                  | 154         |

| TCON             | 0x88               | Timer/Counter Control                                    | 147         |

| TH0              | 0x8C               | Timer/Counter 0 High                                     | 150         |

| *Note: SFRs a    | re listed in aloha | abetical order. All undefined SFR locations are reserved |             |

## Table 8.3. Special Function Registers\* (Continued)

| Register                                                                                                         | Address             | Description                                             | Page<br>No. |  |  |

|------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------|-------------|--|--|

| TH1                                                                                                              | 0x8D                | Timer/Counter 1 High                                    | 150         |  |  |

| TL0                                                                                                              | 0x8A                | Timer/Counter 0 Low                                     | 150         |  |  |

| TL1                                                                                                              | 0x8B                | Timer/Counter 1 Low                                     | 150         |  |  |

| TMOD                                                                                                             | 0x89                | Timer/Counter Mode                                      | 148         |  |  |

| TMR2RLH                                                                                                          | 0xCB                | Timer/Counter 2 Reload High                             | 154         |  |  |

| TMR2RLL                                                                                                          | 0xCA                | Timer/Counter 2 Reload Low                              | 154         |  |  |

| TMR2H                                                                                                            | 0xCD                | Timer/Counter 2 High                                    | 154         |  |  |

| TMR2L                                                                                                            | 0xCC                | Timer/Counter 2 Low                                     | 154         |  |  |

| XBR0                                                                                                             | 0xE1                | Port I/O Crossbar Control 0                             | 107         |  |  |

| XBR1                                                                                                             | 0xE2                | Port I/O Crossbar Control 1                             | 107         |  |  |

| XBR2                                                                                                             | 0xE3                | Port I/O Crossbar Control 2                             | 108         |  |  |

| 0x97, 0xAE, 0xAF, 0xB4,<br>0xB6, 0xBF, 0xCE, 0xD2,<br>0xD3, 0xD4, 0xD5, 0xD6,<br>0xD7, 0xDD, 0xDE, 0xDF,<br>0xF5 |                     | Reserved                                                |             |  |  |

| *Note: SFRs a                                                                                                    | are listed in alpha | betical order. All undefined SFR locations are reserved |             |  |  |

#### 8.2.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic I. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

#### SFR Definition 8.1. DPL: Data Pointer Low Byte

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                             |     | Cleared by HW? | Enable<br>Flag     | Priority<br>Control |

|-------------------------------|---------------------|-------------------|------------------------------------------|-----|----------------|--------------------|---------------------|

| Reset                         | 0x0000              | Тор               | None                                     | N/A | N/A            | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0 (/INT0)  | 0x0003              | 0                 | IE0 (TCON.1)                             | Y   | Y              | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow              | 0x000B              | 1                 | TF0 (TCON.5)                             | Y   | Y              | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1 (/INT1)  | 0x0013              | 2                 | IE1 (TCON.3)                             | Y   | Y              | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow              | 0x001B              | 3                 | TF1 (TCON.7)                             | Y   | Y              | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                         | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)           | Y   | N              | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow              | 0x002B              | 5                 | TF2H<br>(TMR2CN.7)<br>TF2L<br>(TMR2CN.6) | Y   | N              | ET2 (IE.5)         | PT2 (IP.5)          |

| SMBus Interface               | 0x0033              | 6                 | SI (SMB0CN.0)                            | Y   | N              | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| ADC0 Window Compare           | 0x003B              | 7                 | AD0WINT<br>(ADC0CN.3)                    | Y   | N              | EWADC0<br>(EIE1.1) | PWADC0<br>(EIP1.1)  |

| ADC0 Conversion Com-<br>plete | 0x0043              | 8                 | AD0INT<br>(ADC0CN.5)                     | Y   | N              | EADC0C<br>(EIE1.2) | PADC0C<br>(EIP1.2)  |

| Programmable Counter<br>Array | 0x004B              | 9                 | CF (PCA0CN.7)<br>CCFn<br>(PCA0CN.n)      | Y   | N              | EPCA0<br>(EIE1.3)  | PPCA0<br>(EIP1.3)   |

| Comparator0 Falling Edge      | 0x0053              | 10                | CP0FIF<br>(CPT0CN.4)                     | N   | N              | ECP0F<br>(EIE1.4)  | PCP0F<br>(EIP1.4)   |

| Comparator0 Rising Edge       | 0x005B              | 11                | CP0RIF<br>(CPT0CN.5)                     | N   | N              | ECP0R<br>(EIE1.5)  | PCP0R<br>(EIP1.5)   |

Table 8.4. Interrupt Summary

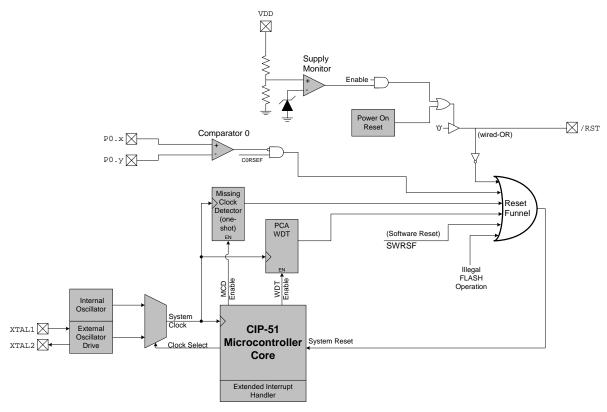

## 9. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the  $\overrightarrow{RST}$  pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to **Section "11. Oscillators" on page 97** for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (**Section "16.3. Watchdog Timer Mode" on page 164** details the use of the Watchdog Timer). Once the system clock source is stable, program execution begins at location 0x0000.

Figure 9.1. Reset Sources

| Parameter                                                     | Conditions                           | Min  | Тур  | Max | Units |  |  |

|---------------------------------------------------------------|--------------------------------------|------|------|-----|-------|--|--|

| Calibrated Internal Oscillator                                | C8051F300/1 devices<br>-40 to +85 °C | 24   | 24.5 | 25  | MHz   |  |  |

| Frequency                                                     | C8051F300/1 devices<br>0 to +70 °C   | 24.3 | 24.7 | 25  | MHz   |  |  |

| Uncalibrated Internal Oscillator<br>Frequency                 | C8051F302/3/4/5 devices              | 16   | 20   | 24  | MHz   |  |  |

| Internal Oscillator Supply Current<br>(from V <sub>DD</sub> ) | OSCICN.2 = 1                         |      | 450  |     | μA    |  |  |

#### **Table 11.1. Internal Oscillator Electrical Characteristics**

#### 11.2. External Oscillator Drive Circuit

-40 to +85 °C unless otherwise specified

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 11.1. A 10 M $\Omega$  resistor also must be wired across the XTAL2 and XTAL1 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 11.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 11.3).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.2 and P0.3 are occupied as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.3 is occupied as XTAL2. The Port I/O Crossbar should be configured to skip the occupied Port pins; see **Section "12.1. Priority Crossbar Decoder" on page 104** for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See **Section "12.2. Port I/O Initialization" on page 106** for details on Port input mode selection.

#### 11.3. System Clock Selection

The CLKSL bit in register OSCICN selects which oscillator is used as the system clock. CLKSL must be set to '1' for the system clock to run from the external oscillator; however the external oscillator may still clock peripherals (timers, PCA) when the internal oscillator is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillator, so long as the selected oscillator is enabled and has settled. The internal oscillator requires little start-up time and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no start-up time.

#### SFR Definition 11.3. OSCXCN: External Oscillator Control

|          | <b>D</b> 444                                                                                                                    | <b>D</b> 444         | -                                   | -         | <b>5</b> 4 4     | 5.44         | 5.444        | 5                    |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------|-----------|------------------|--------------|--------------|----------------------|--|--|

|          |                                                                                                                                 | R/W<br>XOSCMD1       |                                     | R         | R/W<br>XFCN2     | R/W<br>XFCN1 | R/W<br>XFCN0 | Reset Value          |  |  |

| Bit7     | Bit6                                                                                                                            | Bit5                 | Bit4                                |           | Bit2             |              | Bit0         | 00000000             |  |  |

| BIT      | BIto                                                                                                                            | BItS                 | BI[4                                | Bit3      | BItZ             | Bit1         | Bitu         | SFR Address:<br>0xB1 |  |  |

|          |                                                                                                                                 |                      |                                     |           |                  |              |              | UXDI                 |  |  |

| Bit7:    |                                                                                                                                 | ustal Oscillat       | or Valid Flag.                      |           |                  |              |              |                      |  |  |

| Ditr.    | (Read only w                                                                                                                    |                      |                                     |           |                  |              |              |                      |  |  |

|          | · ·                                                                                                                             |                      | used or not ye                      | t stable. |                  |              |              |                      |  |  |

|          | •                                                                                                                               |                      | nning and stat                      |           |                  |              |              |                      |  |  |

| Bits6-4: | XOSCMD2-0                                                                                                                       | ): External C        | scillator Mode                      | Bits.     |                  |              |              |                      |  |  |

|          | 00x: Externa                                                                                                                    | l Oscillator c       | ircuit off.                         |           |                  |              |              |                      |  |  |

|          | 010: Externa                                                                                                                    |                      |                                     |           |                  |              |              |                      |  |  |

|          |                                                                                                                                 |                      | ck Mode with o                      | •         | -                |              |              |                      |  |  |

|          |                                                                                                                                 |                      | with divide by                      | -         |                  |              |              |                      |  |  |

|          | •                                                                                                                               |                      | Mode with div                       | ide by 2  | stage.           |              |              |                      |  |  |

|          | 110: Crystal                                                                                                                    |                      |                                     | by 2 of   |                  |              |              |                      |  |  |

| Bit3:    | •                                                                                                                               |                      | ode with divide<br>Nrite = don't ca | •         | ige.             |              |              |                      |  |  |

| Bits2–0: |                                                                                                                                 |                      | lator Frequenc                      |           | h Rits           |              |              |                      |  |  |

| B102 0.  | 000-111: See                                                                                                                    |                      | •                                   |           |                  |              |              |                      |  |  |

|          | XFCN                                                                                                                            | Crystal (XC          | DSCMD = 11x)                        | RC ()     | (OSCMD =         | 10x) C       | (XOSCMD      | = 10x)               |  |  |

|          | 000                                                                                                                             | f ≤ 3                | 32 kHz                              |           | f≤25 kHz         |              | K Factor =   | 0.87                 |  |  |

|          | 001                                                                                                                             | 32 kHz <             | < f ≤ 84 kHz                        | 25 k      | Hz < f ≤ 50      | kHz          | K Factor =   | = 2.6                |  |  |

|          | 010                                                                                                                             | 84 kHz <             | : f ≤ 225 kHz                       | 50 kł     | Hz < f ≤ 100     | kHz          | K Factor =   | = 7.7                |  |  |

|          | 011                                                                                                                             | 225 kHz «            | < f ≤ 590 kHz                       | 100 k     | $Hz < f \le 200$ | ) kHz        | K Factor =   | = 22                 |  |  |

|          | 100                                                                                                                             | 590 kHz <            | < f ≤ 1.5 MHz                       | 200 k     | $Hz < f \le 400$ | ) kHz        | K Factor =   | = 65                 |  |  |

|          | 101                                                                                                                             | 1.5 MHz              | $< f \le 4 MHz$                     | 400 k     | $Hz < f \le 800$ | ) kHz        | K Factor =   | 180                  |  |  |

|          | 110                                                                                                                             | 4 MHz <              | : f ≤ 10 MHz                        | 800 k     | Hz < f ≤ 1.6     | MHz          | K Factor =   | 664                  |  |  |

|          | 111                                                                                                                             | 10 MHz «             | < f ≤ 30 MHz                        | 1.6 M     | Hz < f ≤ 3.2     | MHz          | K Factor =   | 1590                 |  |  |

| CRYSTA   |                                                                                                                                 | cuit from Fig        | ure 11.1, Optic                     | n 1· XO   | SCMD - 11        | <b>v</b> )   |              |                      |  |  |

| ORIGIA   |                                                                                                                                 |                      | natch crystal fr                    |           |                  | ^)           |              |                      |  |  |

|          | 2                                                                                                                               |                      |                                     |           | -                |              |              |                      |  |  |

| RC MOD   | E (Circuit fror                                                                                                                 | n Figure 11.1        | I, Option 2; XC                     | SCMD      | = 10x)           |              |              |                      |  |  |

|          |                                                                                                                                 |                      | natch frequend                      |           |                  |              |              |                      |  |  |

|          | $f = 1.23(10^3)$                                                                                                                | <b>/ (R x C)</b> , w | here                                |           |                  |              |              |                      |  |  |

|          | f = frequency                                                                                                                   |                      |                                     |           |                  |              |              |                      |  |  |

|          | C = capacito                                                                                                                    | r value in pF        |                                     |           |                  |              |              |                      |  |  |

|          | R = Pull-up ı                                                                                                                   | esistor value        | e in kΩ                             |           |                  |              |              |                      |  |  |

| C MODE   | (Circuit from                                                                                                                   | Figure 11.1,         | Option 3; XOS                       | SCMD =    | 10x)             |              |              |                      |  |  |

|          | <b>C MODE</b> (Circuit from Figure 11.1, Option 3; XOSCMD = 10x)<br>Choose K Factor (KF) for the oscillation frequency desired: |                      |                                     |           |                  |              |              |                      |  |  |

|          | $f = KF / (C \times V_{DD})$ , where                                                                                            |                      |                                     |           |                  |              |              |                      |  |  |

|          | f = frequency of oscillation in MHz                                                                                             |                      |                                     |           |                  |              |              |                      |  |  |

|          |                                                                                                                                 |                      | (TAL2 pin in pl                     | =         |                  |              |              |                      |  |  |

|          | $V_{DD} = Powe$                                                                                                                 | r Supply on I        | MCU in volts                        |           |                  |              |              |                      |  |  |

|          |                                                                                                                                 |                      |                                     |           |                  |              |              |                      |  |  |

#### SFR Definition 12.1. XBR0: Port I/O Crossbar Register 0

| R/W                                         | R/W<br>XSKP6 | R/W<br>XSKP5                                                         | R/W<br>XSKP4                                                               | R/W<br>XSKP3                                                        | R/W<br>XSKP2                               | R/W<br>XSKP1           | R/W<br>XSKP0 | Reset Value 0000000                     |  |

|---------------------------------------------|--------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------|------------------------|--------------|-----------------------------------------|--|

| Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR |              |                                                                      |                                                                            |                                                                     |                                            |                        |              |                                         |  |

| Bit7:<br>Bits6–0:                           |              | Crossbar S<br>elect Port p<br>or ADC or C<br>CNVSTR in<br>nding P0.n | kip Enable<br>bins to be sl<br>Comparator<br>nput) should<br>pin is not sl | Bits<br>kipped by th<br>) or used as<br>d be skippe<br>kipped by tl | s special fur<br>d by the Cr<br>he Crossba | nctions (VR<br>ossbar. |              | 0xE1<br>Ised as ana-<br>external oscil- |  |

#### SFR Definition 12.2. XBR1: Port I/O Crossbar Register 1

| R/W      | R/W                                                                          | R/W           | R/W         | R/W        | R/W       | R/W  | R/W    | Reset Value  |  |  |  |

|----------|------------------------------------------------------------------------------|---------------|-------------|------------|-----------|------|--------|--------------|--|--|--|

| -        | AOME                                                                         | CP0AOEN       | CPOOEN      | SYSCKE     |           | -    | UTX0EN | 7            |  |  |  |

| Bit7     | Bit6                                                                         | Bit5          | Bit4        | Bit3       | Bit2      | Bit1 | Bit0   | SFR Address: |  |  |  |

| Ditt     | Dito                                                                         | Dito          | Ditt        | Dito       | DIE       | Ditt | Dito   | 0xE2         |  |  |  |

|          |                                                                              |               |             |            |           |      |        | UNEZ         |  |  |  |

| Bits7–6: | PCA0ME: P                                                                    | CA Module     | /0 Enable   | Bits       |           |      |        |              |  |  |  |

|          | 00: All PCA                                                                  | I/O unavaila  | ble at Port | pins.      |           |      |        |              |  |  |  |

|          | 01: CEX0 rc                                                                  |               |             | •          |           |      |        |              |  |  |  |

|          | 10: CEX0, C                                                                  | EX1 routed    | to Port pin | s.         |           |      |        |              |  |  |  |

|          | 11: CEX0, C                                                                  | EX1, CEX2     | routed to F | Port pins. |           |      |        |              |  |  |  |

| Bit5:    |                                                                              | Comparator    |             |            | ut Enable |      |        |              |  |  |  |

|          | 0: Asynchronous CP0 unavailable at Port pin.                                 |               |             |            |           |      |        |              |  |  |  |

|          | 1: Asynchronous CP0 routed to Port pin.                                      |               |             |            |           |      |        |              |  |  |  |

| Bit4:    |                                                                              | omparator0    | •           | able       |           |      |        |              |  |  |  |

|          |                                                                              | ailable at Po |             |            |           |      |        |              |  |  |  |

| Dito     | 1: CP0 routed to Port pin.                                                   |               |             |            |           |      |        |              |  |  |  |

| Bit3:    |                                                                              | SYSCLK Out    |             |            |           |      |        |              |  |  |  |

|          | 0: /SYSCLK                                                                   |               | •           |            |           |      |        |              |  |  |  |

| Bit2:    | 1: /SYSCLK output routed to Port pin.<br>SMB0OEN: SMBus I/O Enable           |               |             |            |           |      |        |              |  |  |  |

| DILZ.    |                                                                              |               |             | inc        |           |      |        |              |  |  |  |

|          | 0: SMBus I/O unavailable at Port pins.<br>1: SDA, SCL routed to Port pins.   |               |             |            |           |      |        |              |  |  |  |

| Bit1:    | URX0EN: UART RX Enable                                                       |               |             |            |           |      |        |              |  |  |  |

| Ditt.    |                                                                              |               |             | in         |           |      |        |              |  |  |  |

|          | 0: UART RX0 unavailable at Port pin.<br>1: UART RX0 routed to Port pin P0.5. |               |             |            |           |      |        |              |  |  |  |

| Bit0:    | UTX0EN: UART TX Output Enable                                                |               |             |            |           |      |        |              |  |  |  |

|          | 0: UART TX0 unavailable at Port pin.                                         |               |             |            |           |      |        |              |  |  |  |

|          |                                                                              | 0 routed to I | •           |            |           |      |        |              |  |  |  |

|          |                                                                              |               |             |            |           |      |        |              |  |  |  |

#### 13.1. Supporting Documents

It is assumed the reader is familiar with or has access to the following supporting documents:

- 1. The I<sup>2</sup>C-Bus and How to Use It (including specifications), Philips Semiconductor.

- 2. The I<sup>2</sup>C-Bus Specification Version 2.0, Philips Semiconductor.

- 3. System Management Bus Specification Version 1.1, SBS Implementers Forum.

#### **13.2. SMBus Configuration**

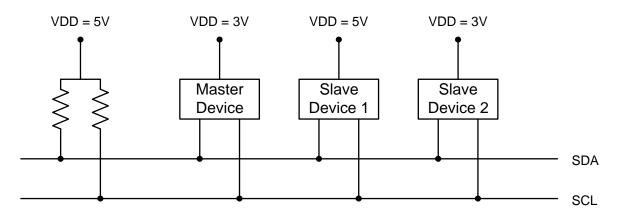

Figure 13.2 shows a typical SMBus configuration. The SMBus specification allows any recessive voltage between 3.0 and 5.0 V; different devices on the bus may operate at different voltage levels. The bidirectional SCL (serial clock) and SDA (serial data) lines must be connected to a positive power supply voltage through a pull-up resistor or similar circuit. Every device connected to the bus must have an open-drain or open-collector output for both the SCL and SDA lines, so that both are pulled high (recessive state) when the bus is free. The maximum number of devices on the bus is limited only by the requirement that the rise and fall times on the bus not exceed 300 ns and 1000 ns, respectively.

#### Figure 13.2. Typical SMBus Configuration

#### 13.3. SMBus Operation

Two types of data transfers are possible: data transfers from a master transmitter to an addressed slave receiver (WRITE), and data transfers from an addressed slave transmitter to a master receiver (READ). The master device initiates both types of data transfers and provides the serial clock pulses on SCL. The SMBus interface may operate as a master or a slave, and multiple master devices on the same bus are supported. If two or more masters attempt to initiate a data transfer simultaneously, an arbitration scheme is employed with a single master always winning the arbitration. Note that it is not necessary to specify one device as the Master in a system; any device that transmits a START and a slave address becomes the master for the duration of that transfer.

A typical SMBus transaction consists of a START condition followed by an address byte (Bits7–1: 7-bit slave address; Bit0: R/W direction bit), one or more bytes of data, and a STOP condition. Each byte that is received (by a master or slave) must be acknowledged (ACK) with a low SDA during a high SCL (see Figure 13.3). If the receiving device does not ACK, the transmitting device will read a NACK (not acknowledge), which is a high SDA during a high SCL.

|                | Valu                                        | ies | Read                                          | k   | Current SMbus State                                                                 | Typical Response Options                                                                                                                                                | Values<br>Written |     |     |

|----------------|---------------------------------------------|-----|-----------------------------------------------|-----|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|-----|

| Mode           | Status<br>Vector<br>ACKRQ<br>ARBLOST<br>ACK |     |                                               | ACK |                                                                                     |                                                                                                                                                                         |                   | STO | ACK |

|                | 0010                                        | 1   | 0                                             | X   | A slave address was received;<br>ACK requested.                                     | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0                 | 0   | 1   |

|                |                                             |     |                                               |     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0                 | 0   | 0   |

|                |                                             |     |                                               |     |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0                 | 0   | 1   |

|                |                                             | 1   | 1                                             | X   | Lost arbitration as master; slave<br>address received; ACK<br>requested.            | Acknowledge received<br>address (received slave<br>address match, R/W bit =<br>READ).                                                                                   | 0                 | 0   | 1   |

|                |                                             |     |                                               |     |                                                                                     | Do not acknowledge received address.                                                                                                                                    | 0                 | 0   | 0   |

| SLAVE RECEIVER |                                             |     |                                               |     |                                                                                     | Acknowledge received<br>address, and switch to trans-<br>mitter mode (received slave<br>address match, R/W bit =<br>WRITE); see <b>Section 13.5.4</b><br>for procedure. | 0                 | 0   | 1   |

| SL/            |                                             |     |                                               |     |                                                                                     | Reschedule failed transfer;<br>do not acknowledge received<br>address                                                                                                   | 1                 | 0   | 0   |

|                | 0010                                        | 0   | 1                                             | Х   | Lost arbitration while attempting a                                                 | Abort failed transfer.                                                                                                                                                  | 0                 | 0   | Х   |

|                | 0001                                        |     |                                               | V   | repeated START.                                                                     | Reschedule failed transfer.                                                                                                                                             | 1                 | 0   | X   |

|                | 0001                                        | 1   | 1 X Lost arbitration while attempting a STOP. |     | STOP.                                                                               | complete/aborted).                                                                                                                                                      | 0                 | 0   | 0   |

|                |                                             | 0   | 0                                             |     | A STOP was detected while<br>addressed as a Slave Transmitter<br>or Slave Receiver. | Clear STO.                                                                                                                                                              | 0                 | 0   | X   |

|                |                                             | 0   | 1                                             | Х   |                                                                                     | Abort transfer.                                                                                                                                                         | 0                 | 0   | Х   |

|                |                                             |     |                                               |     | STOP.                                                                               | Reschedule failed transfer.                                                                                                                                             | 1                 | 0   | X   |

|                | 0000                                        | 1   | 0                                             | X   | A slave byte was received; ACK requested.                                           | Acknowledge received byte;<br>Read SMB0DAT.                                                                                                                             | 0                 | 0   | 1   |

|                |                                             |     |                                               |     |                                                                                     | Do not acknowledge received byte.                                                                                                                                       | 0                 | 0   | 0   |

|                |                                             | 1   | 1                                             | х   | Lost arbitration while transmitting                                                 | Abort failed transfer.                                                                                                                                                  | 0                 | 0   | 0   |

|                |                                             |     |                                               |     | a data byte as master.                                                              | Reschedule failed transfer.                                                                                                                                             | 1                 | 0   | 0   |

#### Table 13.4. SMBus Status Decoding (Continued)

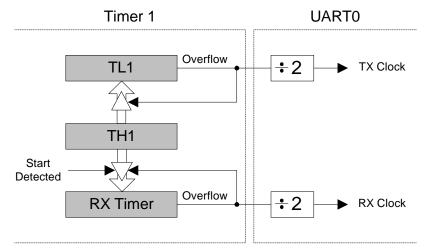

#### 14.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 14.2), which is not user accessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see **Section "15.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 145**). The Timer 1 reload value should be set so that over-flows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of five sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, or the external oscillator clock / 8. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 14.1.

$$UartBaudRate = \frac{T1_{CLK}}{(256 - T1H)} \times \frac{1}{2}$$

#### Equation 14.1. UART0 Baud Rate

Where  $T1_{CLK}$  is the frequency of the clock supplied to Timer 1, and T1H is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in **Section "15.2. Timer 2" on page 151**. A quick reference for typical baud rates and system clock frequencies is given in Tables 14.1 through 14.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1 (see **Section "15.1. Timer 0 and Timer 1" on page 143** for more details).

| <ul> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode.</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.</li> <li>Bit4: REN0: Receive Enable.</li> <li>This bit enables/disables the UART receiver.</li> <li>0: UART0 reception disabled.</li> <li>1: UART0 reception enabled.</li> <li>Bit3: TB80: Ninth Transmission Bit.</li> <li>The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode is not used in 8-bit UART Mode. Set or cleared by software as required.</li> <li>Bit2: RB80: Ninth Receive Bit.</li> <li>RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9 data bit in Mode 1.</li> <li>Bit1: T10: Transmit Interrupt Flag.</li> <li>Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bi bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the U interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt server.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Value  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>(bit addressable)</li> <li>(c) (bit addressable)</li> <li>(</li></ul>                                                                                                                                                                                                                                                     |        |

| <ul> <li>S0MODE: Serial Port 0 Operation Mode.</li> <li>This bit selects the UART0 Operation Mode.</li> <li>0: Mode 0: 8-bit UART with Variable Baud Rate</li> <li>1: Mode 1: 9-bit UART with Variable Baud Rate</li> <li>3it6: UNUSED. Read = 1b. Write = don't care.</li> <li>3it5: MCE0: Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode.</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.</li> <li>Bit4: REN0: Receive Enable.</li> <li>This bit enables/disables the UART receiver.</li> <li>0: UART0 reception disabled.</li> <li>1: UART0 reception enabled.</li> <li>Bit3: TB80: Ninth Transmission Bit.</li> <li>The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode.</li> <li>Bit4: RB80: Ninth Receive Bit.</li> <li>RB80: Ninth Receive Bit.</li> <li>RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 9 data bit in Mode 1.</li> <li>Bit1: T10: Transmit Interrupt Flag.</li> <li>Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bi bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the U interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt servutine. This bit must be cleared manually by software</li> <li>Bit0: R10: Receive Interrupt Flag.</li> <li>Set to 1'1 by hardware when a byte of data has been received by UART0 (set at the STO sampling time). When the UART0 interrupt is enabled, setting this bit to '1' causes the to vector to the</li></ul> |        |

| <ul> <li>This bit selects the UARTO Operation Mode.</li> <li>0: Mode 0: 8-bit UART with Variable Baud Rate</li> <li>1: Mode 1: 9-bit UART with Variable Baud Rate</li> <li>1: MOde 1: 9-bit UART with Variable Baud Rate</li> <li>Bit6: UNUSED. Read = 1b. Write = don't care.</li> <li>Bit5: MCE0: Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode.</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.</li> <li>Bit4: REN0: Receive Enable.</li> <li>This bit enables/disables the UART receiver.</li> <li>0: UARTO reception disabled.</li> <li>1: UART0 reception enabled.</li> <li>Bit3: TB80: Ninth Transmission Bit.</li> <li>The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode.</li> <li>Bit4: RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 1 data bit in Mode 1.</li> <li>Bit1: Ti0: Transmit Interrupt Flag.</li> <li>Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bid bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the U interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98     |

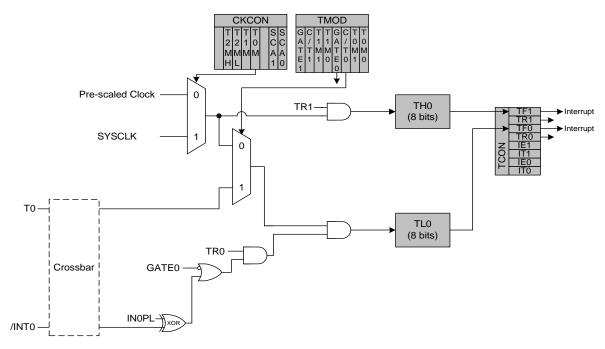

| <ul> <li>This bit selects the UART<sup>0</sup> Operation Mode.</li> <li>0: Mode 0: 8-bit UART with Variable Baud Rate</li> <li>1: Mode 1: 9-bit UART with Variable Baud Rate</li> <li>3it6: UNUSED. Read = 1b. Write = don't care.</li> <li>3it5: MCE0: Multiprocessor Communication Enable.</li> <li>The function of this bit is dependent on the Serial Port 0 Operation Mode.</li> <li>Mode 0: Checks for valid stop bit.</li> <li>0: Logic level of stop bit is ignored.</li> <li>1: RI0 will only be activated if stop bit is logic level 1.</li> <li>Mode 1: Multiprocessor Communications Enable.</li> <li>0: Logic level of ninth bit is ignored.</li> <li>1: RI0 is set and an interrupt is generated only when the ninth bit is logic 1.</li> <li>8it4: REN0: Receive Enable.</li> <li>This bit enables/disables the UART receiver.</li> <li>0: UART0 reception disabled.</li> <li>1: UART0 reception disabled.</li> <li>1: UART0 reception enabled.</li> <li>3it3: TB80: Ninth Transmission Bit.</li> <li>The logic level of this bit will be assigned to the ninth transmission bit in 9-bit UART Mode.</li> <li>3it4: RB80 is assigned the value of the STOP bit in Mode 0; it is assigned the value of the 1 data bit in Mode 1.</li> <li>3it1: T10: Transmit Interrupt Flag.</li> <li>Set by hardware when a byte of data has been transmitted by UART0 (after the 8th bid bit UART Mode, or at the beginning of the STOP bit in 9-bit UART Mode). When the U interrupt is enabled, setting this bit causes the CPU to vector to the UART0 interrupt service routine. This bit must be cleared manually by software</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |