Welcome to E-XFL.COM

**Embedded - Microcontrollers - Application** Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are Embedded - Microcontrollers -**Application Specific**?

Application charific microcontrollars are angineered to

| Details |

|---------|

|---------|

| Details                 |                                                                          |

|-------------------------|--------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                 |

| Applications            | RF4CE, Remote Control                                                    |

| Core Processor          | ARM® Cortex®-M3                                                          |

| Program Memory Type     | FLASH (128kB)                                                            |

| Controller Series       | STM32W                                                                   |

| RAM Size                | 8K x 8                                                                   |

| Interface               | I²C, SPI, UART/USART                                                     |

| Number of I/O           | 24                                                                       |

| Voltage - Supply        | 1.18V ~ 3.6V                                                             |

| Operating Temperature   | -40°C ~ 85°C                                                             |

| Mounting Type           | Surface Mount                                                            |

| Package / Case          | 48-VFQFN Exposed Pad                                                     |

| Supplier Device Package | 48-VFQFPN (7x7)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32w108cbu63tr |

|                         |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 46. Gating Timer 2 with OC1REF of Timer 1                                     |     |

|--------------------------------------------------------------------------------------|-----|

| Figure 47. Gating Timer 2 with enable of Timer 1                                     | 192 |

| Figure 48. Triggering timer 2 with update of Timer 1                                 | 193 |

| Figure 49. Triggering Timer 2 with enable of Timer 1                                 | 194 |

| Figure 50. Triggering Timers 1 and 2 with Timer 1 TI1 input                          |     |

| Figure 51. ADC block diagram                                                         |     |

| Figure 52. SWJ block diagram                                                         |     |

| Figure 53. Pin loading conditions                                                    |     |

| Figure 54. Pin input voltage                                                         |     |

| Figure 55. SPI timing diagram - slave mode and CPHA = 0                              | 253 |

| Figure 56. SPI timing diagram - slave mode and CPHA = $1^{(1)}$                      | 253 |

| Figure 57. SPI timing diagram - master mode <sup>(1)</sup>                           | 254 |

| Figure 58. Transmit power consumption                                                |     |

| Figure 59. Transmit output power                                                     |     |

| Figure 60. VFQFPN48 - 48-pin, 7x7 mm, 0.5 mm pitch very thin profile fine pitch quad |     |

| flat package outline                                                                 |     |

| Figure 61. VFQFPN48 - 48-pin, 7x7 mm, 0.5 mm pitch very thin profile fine pitch quad |     |

| flat package recommended footprint                                                   |     |

| Figure 62. VFQFPN40 - 40-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad |     |

| flat package outline                                                                 |     |

| Figure 63. VFQFPN40 - 40-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad |     |

| flat package recommended footprint                                                   |     |

| Figure 64. VFQFPN40 marking example (package top view)                               |     |

| Figure 65. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

| package outline                                                                      |     |

| Figure 66. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat |     |

| package recommended footprint                                                        |     |

| Figure 67. UFQFPN48 marking example (package top view)                               | 278 |

## 1.2 Overview

## 1.2.1 Functional description

The STM32W108xx radio receiver is a low-IF, super-heterodyne receiver. The architecture has been chosen to optimize co-existence with other devices in the 2.4 GHz band (namely, WIFI and Bluetooth), and to minimize power consumption. The receiver uses differential signal paths to reduce sensitivity to noise interference. Following RF amplification, the signal is downconverted by an image-rejecting mixer, filtered, and then digitized by an ADC.

The radio transmitter uses an efficient architecture in which the data stream directly modulates the VCO frequency. An integrated power amplifier (PA) provides the output power. Digital logic controls Tx path and output power calibration. If the STM32W108xx is to be used with an external PA, use the TX\_ACTIVE or nTX\_ACTIVE signal to control the timing of the external switching logic.

The integrated 4.8 GHz VCO and loop filter minimize off-chip circuitry. Only a 24 MHz crystal with its loading capacitors is required to establish the PLL local oscillator signal.

The MAC interfaces the on-chip RAM to the Rx and Tx baseband modules. The MAC provides hardware-based IEEE 802.15.4 packet-level filtering. It supplies an accurate symbol time base that minimizes the synchronization effort of the software stack and meets the protocol timing requirements. In addition, it provides timer and synchronization assistance for the IEEE 802.15.4 CSMA-CA algorithm.

The STM32W108xx integrates an ARM<sup>®</sup> Cortex<sup>®</sup>-M3 microprocessor, revision r1p1. This industry-leading core provides 32 bit performance and is very power efficient. It has excellent code density using the ARM<sup>®</sup> Thumb 2 instruction set. The processor can be operated at 12 MHz or 24 MHz when using the crystal oscillator, or at 6 MHz or 12 MHz when using the integrated high frequency RC oscillator.

The STM32W108xx has 128/192/256 Kbyte of Flash memory, 8/12/16 Kbyte of SRAM onchip, and the ARM configurable memory protection unit (MPU).

The STM32W108xx contains 24 GPIO pins shared with other peripheral or alternate functions. Because of flexible routing within the STM32W108xx, external devices can use the alternate functions on a variety of different GPIOs. The integrated Serial Controller SC1 can be configured for SPI (master or slave), I<sup>2</sup>C (master-only), or UART operation, and the Serial Controller SC2 can be configured for SPI (master or slave) or I<sup>2</sup>C (master-only) operation.

The STM32W108xx has a general purpose ADC which can sample analog signals from six GPIO pins in single-ended or differential modes. It can also sample the regulated supply VDD\_PADSA, the voltage reference VREF, and GND. The ADC has two selectable voltage ranges: 0 V to 1.2 V for the low voltage (input buffer disabled) and 0.1 V to VDD\_PADS minus 0.1 V for the high voltage supply (input buffer enabled). The ADC has a DMA mode to capture samples and automatically transfer them into RAM. The integrated voltage reference for the ADC, VREF, can be made available to external circuitry. An external voltage reference can also be driven into the ADC.

The STM32W108xx contains four oscillators: a high frequency 24 MHz external crystal oscillator (24 MHz HSE OSC), a high frequency 12 MHz internal RC oscillator (12 MHz HSI RC), an optional low frequency 32.768 kHz external crystal oscillator (32 kHz HSE OSC), and a 10 kHz internal RC oscillator (10 kHz LSI RC).

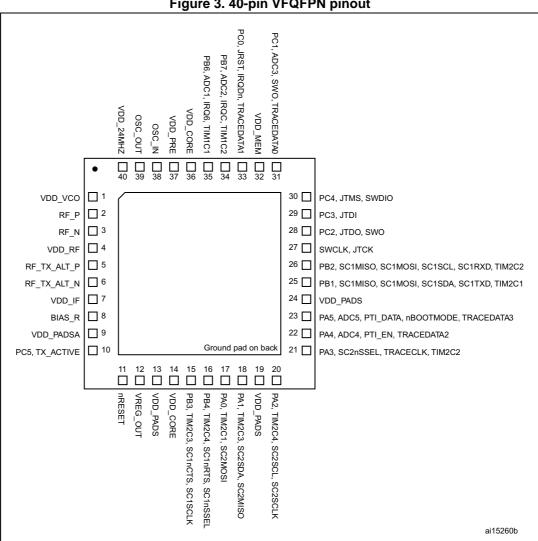

#### Figure 3. 40-pin VFQFPN pinout

## **Table 2. Pin descriptions**

| 48-Pin<br>Package<br>Pin no. | 40-Pin<br>Package<br>Pin no. | Signal      | Direction | Description                                                   |

|------------------------------|------------------------------|-------------|-----------|---------------------------------------------------------------|

| 1                            | 40                           | VDD_24MHZ   | Power     | 1.8V high-frequency oscillator supply                         |

| 2                            | 1                            | VDD_VCO     | Power     | 1.8V VCO supply                                               |

| 3                            | 2                            | RF_P        | I/O       | Differential (with RF_N) receiver input/transmitter output    |

| 4                            | 3                            | RF_N        | I/O       | Differential (with RF_P) receiver input/transmitter output    |

| 5                            | 4                            | VDD_RF      | Power     | 1.8V RF supply (LNA and PA)                                   |

| 6                            | 5                            | RF_TX_ALT_P | 0         | Differential (with RF_TX_ALT_N) transmitter output (optional) |

| 7                            | 6                            | RF_TX_ALT_N | 0         | Differential (with RF_TX_ALT_P) transmitter output (optional) |

| 8                            | 7                            | VDD_IF      | Power     | 1.8V IF supply (mixers and filters)                           |

| 9                            | 8                            | BIAS_R      | I         | Bias setting resistor                                         |

| 48-Pin<br>Package<br>Pin no. | 40-Pin<br>Package<br>Pin no. | Signal                           | Direction | Description                                                                                                                                                                                                                                    |

|------------------------------|------------------------------|----------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                              | PB3                              | I/O       | Digital I/O                                                                                                                                                                                                                                    |

|                              |                              | TIM2_CH3<br>(see Pin 22)         | 0         | Timer 2 channel 3 output<br>Enable remap with TIM2_OR[6]<br>Enable timer output in TIM2_CCER<br>Select alternate output function with GPIOB_CRL[15:12]                                                                                         |

|                              |                              |                                  | I         | Timer 2 channel 3 input. Enable remap with TIM2_OR[6].                                                                                                                                                                                         |

| 19                           | 15                           | UART_CTS                         | I         | UART CTS handshake of Serial Controller 1<br>Enable with SC1_UARTCR[5]<br>Select UART with SC1_CR                                                                                                                                              |

|                              |                              | SC1SCLK                          | 0         | SPI master clock of Serial Controller 1<br>Either disable timer output in TIM2_CCER or disable remap<br>with TIM2_OR[6]<br>Enable master with SC1_SPICR[4]<br>Select SPI with SC1_CR<br>Select alternate output function with GPIOB_CRL[15:12] |

|                              |                              |                                  | I         | SPI slave clock of Serial Controller 1<br>Enable slave with SC1_SPICR[4]<br>Select SPI with SC1_CR                                                                                                                                             |

|                              |                              | PB4                              | I/O       | Digital I/O                                                                                                                                                                                                                                    |

|                              |                              | TIM2_CH4<br>(see also<br>Pin 24) | 0         | Timer 2 channel 4 output<br>Enable remap with TIM2_OR[7]<br>Enable timer output in TIM2_CCER<br>Select alternate output function with GPIOB_CRH[3:0]                                                                                           |

|                              |                              |                                  | I         | Timer 2 channel 4 input. Enable remap with TIM2_OR[7].                                                                                                                                                                                         |

| 20                           | 16                           | UART_RTS                         | 0         | UART RTS handshake of Serial Controller 1<br>Either disable timer output in TIM2_CCER or disable remap<br>with TIM2_OR[7]<br>Enable with SC1_UARTCR[5]<br>Select UART with SC1_CR<br>Select alternate output function with GPIOB_CRH[3:0]      |

|                              |                              | SC1nSSEL                         | I         | SPI slave select of Serial Controller 1<br>Enable slave with SC1_SPICR[4]<br>Select SPI with SC1_CR                                                                                                                                            |

Table 2. Pin descriptions (continued)

# 4 Embedded memory

## 4.1 Memory organization and memory map

The bytes are coded in the memory in Little Endian format. The lowest numbered byte in a word is considered the word's least significant byte and the highest numbered byte the most significant.

For detailed mapping of peripheral registers, please refer to the relevant section.

All the memory areas that are not allocated to on-chip memories and peripherals are considered "Reserved").

Refer to Figure 4: STM32W108xB memory mapping, Figure 5: STM32W108CC and STM32W108CZ memory mapping, and Table 3: STM32W108xx peripheral register boundary addresses for the register boundary addresses of the peripherals available in all STM32W108xx devices.

## 6.1 **Power domains**

The STM32W108xx contains three power domains:

- An "always on domain" containing all logic and analog cells required to manage the STM32W108xx's power modes, including the GPIO controller and sleep timer. This domain must remain powered.

- A "core domain" containing the CPU, Nested Vectored Interrupt Controller (NVIC), and peripherals. To save power, this domain can be powered down using a mode called deep sleep.

- A "memory domain" containing the RAM and Flash memories. This domain is managed by the power management controller. When in deep sleep, the RAM portion of this domain is powered from the always-on domain supply to retain the RAM contents while the regulators are disabled. During deep sleep the Flash portion is completely powered down.

## 6.1.1 Internally regulated power

The preferred and recommended power configuration is to use the internal regulated power supplies to provide power to the core and memory domains. The internal regulators (VREG\_1V25 and VREG\_1V8) generate nominal 1.25 V and 1.8 V supplies. The 1.25 V supply is internally routed to the core domain and to an external pin. The 1.8 V supply is routed to an external pin where it can be externally routed back into the chip to supply the memory domain. The internal regulators are described in *Section 7: Integrated voltage regulator on page 90*.

When using the internal regulators, the always-on domain must be powered between 2.1 V and 3.6 V at all four VDD\_PADS pins.

When using the internal regulators, the VREG\_1V8 regulator output pin (VREG\_OUT) must be connected to the VDD\_MEM, VDD\_PADSA, VDD\_VCO, VDD\_RF, VDD\_IF, VDD\_PRE, and VDD\_SYNTH pins.

When using the internal regulators, the VREG\_1V25 regulator output and supply requires a connection between both VDD\_CORE pins.

## 6.1.2 Externally regulated power

Optionally, the on-chip regulators may be left unused, and the core and memory domains may instead be powered from external supplies. For simplicity, the voltage for the core domain can be raised to nominal 1.8 V, requiring only one external regulator. Note that if the core domain is powered at a higher voltage (1.8 V instead of 1.25 V) then power consumption increases. A regulator enable signal, REG\_EN, is provided for control of external regulators. This is an open-drain signal that requires an external pull-up resistor. If REG\_EN is not required to control external regulators it can be disabled (see Section 8.1.3: Forced functions on page 95).

Using an external regulator requires the always-on domain to be powered between 1.8 V and 3.6 V at all four VDD\_PADS pins.

When using an external regulator, the VREG\_1V8 regulator output pin (VREG\_OUT) must be left unconnected.

When using an external regulator, this external nominal 1.8 V supply has to be connected to both VDD\_CORE pins and to the VDD\_MEM, VDD\_PADSA, VDD\_VCO, VDD\_RF, VDD\_IF, VDD\_PRE and VDD\_SYNTH pins.

#### 0x4000 A020 Address: 0x0000 0000 Reset value: 31 30 29 28 27 26 25 24 23 22 21 20 18 17 19 Reserved 4 15 14 13 12 11 10 9 8 7 6 5 3 2 1 CMPB CMPA WRAP Reserved rw rw

## Sleep timer force interrupt register (SLPTMR\_IFR)

#### Bits 31:3 Reserved, must be kept at reset value

- Bit 2 CMPB: Force sleep timer compare B interrupt

- Bit 1 CMPA: Force sleep timer compare A interrupt

- Bit 0 WRAP: Force sleep timer wrap interrupt

#### Sleep timer interrupt enable register (SLPTMR\_IER)

| Address:     | 0x4000 A054 |

|--------------|-------------|

| Reset value: | 0x0000 0000 |

| 31 | 30 | 29 | 28 | 27 | 26 | 25      | 24  | 23     | 22 | 21 | 20 | 19 | 18   | 17   | 16   |

|----|----|----|----|----|----|---------|-----|--------|----|----|----|----|------|------|------|

|    |    |    |    |    |    |         | Res | served |    |    |    |    |      |      |      |

|    |    |    |    |    |    |         |     |        |    |    |    |    |      |      |      |

| 15 | 14 | 13 | 12 | 11 | 10 | 9       | 8   | 7      | 6  | 5  | 4  | 3  | 2    | 1    | 0    |

|    |    |    |    |    |    |         |     |        |    |    |    |    | CMPB | CMPA | WRAP |

|    |    |    |    |    |    | Reserve | ed  |        |    |    |    |    | rw   | rw   | rw   |

|    |    |    |    |    |    |         |     |        |    |    |    |    |      |      |      |

#### Bits 31:3 Reserved, must be kept at reset value

- Bit 2 CMPB: Sleep timer compare B

- Bit 1 CMPA: Sleep timer compare A

- Bit 0 WRAP: Sleep timer wrap

16

0

rw

## 8.5.9 External interrupt x configuration register (EXTIx\_CR)

Address offset: 0xBC14 (EXTIC\_CR) and 0xBC18 (EXTID\_CR) Reset value: 0x0000 000F (EXTIC\_CR) and 0x0000 0010 (EXTID\_CR)

| 31 | 30 | 29 | 28 | 27 | 26      | 25 | 24  | 23    | 22 | 21 | 20 | 19 | 18       | 17   | 16 |

|----|----|----|----|----|---------|----|-----|-------|----|----|----|----|----------|------|----|

|    |    |    |    |    |         |    | Res | erved |    |    |    |    |          |      |    |

|    |    |    |    |    |         |    |     |       |    |    |    |    |          |      |    |

| 15 | 14 | 13 | 12 | 11 | 10      | 9  | 8   | 7     | 6  | 5  | 4  | 3  | 2        | 1    | 0  |

|    |    |    |    |    | Reserve | d  |     |       |    |    |    | GF | PIO_SEL[ | 4:0] |    |

|    |    |    |    |    | Reserve | iu |     |       |    |    | rw | rw | rw       | rw   | rw |

#### Bits 31:5 Reserved, must be kept at reset value

Bits 4:0 GPIO\_SEL[4:0]: Pin assigned to EXTIx

| 0x00: PA0 | 0x0D: PB5                                          |

|-----------|----------------------------------------------------|

| 0x01: PA1 | 0x0E: PB6                                          |

| 0x02: PA2 | 0x0F: PB7                                          |

| 0x03: PA3 | 0x10: PC0                                          |

| 0x04: PA4 | 0x11: PC1                                          |

| 0x05: PA5 | 0x12: PC2                                          |

| 0x06: PA6 | 0x13: PC3                                          |

| 0x07: PA7 | 0x14: PC4                                          |

| 0x08: PB0 |                                                    |

| 0x09: PB1 | 0x15: PC5                                          |

| 0x0A: PB2 | 0x16: PC6                                          |

| 0x0B: PB3 | 0x17: PC7                                          |

| 0x0C: PB4 | 0x18 - 0x1F: Reserved, must be kept at reset value |

|           |                                                    |

## 8.5.10 PC TRACE or debug select register (GPIO\_PCTRACECR)

|    |          | Addre<br>Reset |    |    | x4000<br>x0000 |    |         |        |    |    |     |    |    |    |     |

|----|----------|----------------|----|----|----------------|----|---------|--------|----|----|-----|----|----|----|-----|

| 31 | 30       | 29             | 28 | 27 | 26             | 25 | 24      | 23     | 22 | 21 | 20  | 19 | 18 | 17 | 16  |

|    |          |                |    |    |                |    | Res     | served |    |    |     |    |    |    |     |

| 15 | 14       | 13             | 12 | 11 | 10             | 9  | 8       | 7      | 6  | 5  | 4   | 3  | 2  | 1  | 0   |

|    | Reserved |                |    |    |                |    |         |        |    |    | SEL |    |    |    |     |

|    |          |                |    |    |                |    | 1000110 |        |    |    |     |    |    |    | rws |

Bits 31:1 Reserved, must be kept at reset value

Bit 0 SEL: Channel encoding 1: PC trace 0: BB debug

## 9.6.1 Setup and configuration

The UART baud rate clock is produced by a programmable baud generator starting from the 24 Hz clock:

$$baud = \frac{24MHz}{2N+F}$$

The integer portion of the divisor, N, is written to the SC1\_UARTBRR1 register and the fractional part, F, to the SC1\_UARTBRR2 register. *Table 29* shows the values used to generate some common baud rates and their associated clock frequency error. The UART requires an internal clock that is at least eight times the baud rate clock, so the minimum allowable setting for SC1\_UARTBRR1 is '8'.

| Baud rate (bits/sec) | SC1_UARTBRR1 | SC1_UARTBRR2 | Baud rate error (%) |

|----------------------|--------------|--------------|---------------------|

| 300                  | 40000        | 0            | 0                   |

| 2400                 | 5000         | 0            | 0                   |

| 4800                 | 2500         | 0            | 0                   |

| 9600                 | 1250         | 0            | 0                   |

| 19200                | 625          | 0            | 0                   |

| 38400                | 312          | 1            | 0                   |

| 57600                | 208          | 1            | - 0.08              |

| 115200               | 104          | 0            | + 0.16              |

| 230400               | 52           | 0            | + 0.16              |

| 460800               | 26           | 0            | + 0.16              |

| 921600               | 13           | 0            | + 0.16              |

| Table 29. UART baud rate div | visors for common baud rates |

|------------------------------|------------------------------|

|------------------------------|------------------------------|

Note: The UART may receive corrupt bytes if the interbyte gap is long or there is a baud rate mismatch between receive and transmit. The UART may detect a parity and/or framing error on the corrupt byte, but there will not necessarily be any error detected. As a result, the device should be operated in systems where the other side of the communication link also uses a crystal as its timing reference, and baud rates should be selected to minimize the baud rate mismatch to the crystal tolerance. UART protocols should contain some form of error checking (e.g. CRC) at the packet level to detect, and retry in the event of errors.

The UART character frame format is determined by three bits in the SC1\_UARTCR register:

- STOP selects the number of stop bits in transmitted characters. (Only one stop bit is ever required in received characters.) If this bit is clear, characters are transmitted with one stop bit; if set, characters are transmitted with two stop bits.

- PCE controls whether or not received and transmitted characters include a parity bit. If PCE is clear, characters do not contain a parity bit, otherwise, characters do contain a parity bit.

- PS specifies whether transmitted and received parity bits contain odd or even parity. If this bit is clear, the parity bit is even, and if set, the parity bit is odd. Even parity is the exclusive-or of all of the data bits, and odd parity is the inverse of the even parity value. PS has no effect if PCE is clear.

## 9.9.2 Serial controller SPI control register (SCx\_SPICR)

Address offset: 0xC858 (SC1\_SPICR) and 0xC058 (SC2\_SPICR) Reset value: 0x0000 0000

| 31 | 30 | 29 | 28 | 27  | 26    | 25 | 24  | 23    | 22 | 21         | 20   | 19        | 18           | 17   | 16   |

|----|----|----|----|-----|-------|----|-----|-------|----|------------|------|-----------|--------------|------|------|

|    |    |    |    |     |       |    | Res | erved |    |            |      |           |              |      |      |

| 15 | 14 | 13 | 12 | 11  | 10    | 9  | 8   | 7     | 6  | 5          | 4    | 3         | 2            | 1    | 0    |

|    |    |    |    | Res | erved |    |     |       |    | RX<br>MODE | MSTR | RP<br>TEN | LSB<br>FIRST | CPHA | CPOL |

|    |    |    |    |     |       |    |     |       |    | rw         | rw   | rw        | rw           | rw   | rw   |

Bits 31:6 Reserved, must be kept at reset value

- Bit 5 RXMODE: Receiver-driven mode selection bit (SPI master mode only)

- 0: Initiate transactions when transmit data is available.

1: Initiate transactions when the receive buffer (FIFO or DMA) has space. Force immediate transmission of busy token or resend last byte (depending on **RPTEN**) and receive data into FIFO until the FIFO is full.

- Bit 4 MSTR: Master selection

- 0: Slave configuration

- 1: Master configuration

- Bit 3 RPTEN: Repeat enable

This bit controls behavior on a transmit buffer underrun condition in slave mode. Clear this bit to send the BUSY token (0xFF) and set this bit to repeat the last byte. Changes to this bit take effect when the transmit FIFO is empty and the transmit serializer is idle.

- Bit 2 LSBFIRST: Frame format

- 0: Most significant bit transmitted first

- 1: Least significant bit transmitted first

- Bit 1 CPHA: Clock phase

- 0: The first clock transition is the first data capture edge

- 1: The second clock transition is the first data capture edge

- Bit 0 CPOL: Clock polarity

- 0: CK to 0 when idle

- 1: CK to 1 when idle

| OxC810       SC1_DMATX<br>BEGADDAR       is       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 0xC80C       ENDADDBR       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2 <th2< th="">       2       2       2       <t< th=""><th></th></t<></th2<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |

| OxC80C       ENDADDBR       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2       2 <th2< th="">       2       2       2       <t< th=""><th></th></t<></th2<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                    |

| OxC810       SC1_DMATX<br>BEGADDAR       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |

| Reset value         SC1_DMATX         Son Matx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |

| OxC814       SC1_DMATX<br>ENDADDAR       SS1_S       SS1_S<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    |

| Reset value       Reset value <threset th="" value<="">       Reset value</threset>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |

| OxC818       BEGADDBR       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 0 0 0                            |

| Reset value       Reset value <threset th="" value<=""> <threset th="" value<=""></threset></threset>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0 0 0 0                            |

| OxC81C       ENDADDBR       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       P       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    |

| Reset value         SC1_DMARX<br>CNTAR         Si S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |

| OxC820       CNTAR       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                    |

| 0xC824         SC1_DMARX<br>CNTBR         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2         0/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |

| 0xC824         CNTBR         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2         2 <th2< th="">         2         2         2</th2<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0 0 0 0                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |