Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | -                                                                        |

| Number of I/O                  | 34                                                                       |

| Number of Gates                | 10000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                        |

| Package / Case                 | 48-VFQFN Exposed Pad                                                     |

| Supplier Device Package        | 48-QFN (6x6)                                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn010-2qng48 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|   | Introduction                                                                  | 7  |

|---|-------------------------------------------------------------------------------|----|

|   | Related Information                                                           |    |

| 1 | FPGA Array Architecture in Low Power Flash Devices                            | 9  |

|   | Device Architecture                                                           |    |

|   | FPGA Array Architecture Support                                               | 10 |

|   | Device Overview                                                               |    |

|   | Related Documents                                                             |    |

|   | List of Changes                                                               | 20 |

| 2 | Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs                         |    |

|   | Introduction                                                                  |    |

|   | Power Consumption Overview                                                    |    |

|   | Static (Idle) Mode                                                            |    |

|   | User Low Static (Idle) Mode                                                   |    |

|   | Sleep Mode                                                                    |    |

|   | Shutdown Mode                                                                 |    |

|   | Conclusion                                                                    |    |

|   | Related Documents                                                             |    |

|   | List of Changes                                                               | 28 |

| 3 | Global Resources in Low Power Flash Devices                                   |    |

|   | Introduction                                                                  |    |

|   | Global Architecture                                                           |    |

|   | Global Resource Support in Flash-Based Devices                                |    |

|   | VersaNet Global Network Distribution                                          |    |

|   | Spine Architecture                                                            |    |

|   | Using Clock Aggregation                                                       |    |

|   | Design Recommendations                                                        |    |

|   | Conclusion                                                                    |    |

|   | Related Documents                                                             |    |

|   | List of Changes                                                               | F0 |

| 4 | Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs | 61 |

|   | Introduction                                                                  |    |

|   | Overview of Clock Conditioning Circuitry                                      |    |

|   | CCC Support in Microsemi's Flash Devices                                      |    |

|   | Global Buffers with No Programmable Delays                                    |    |

|   | Global Buffer with Programmable Delay                                         |    |

|   | Global Buffers with PLL Function                                              | 67 |

|   | Global Input Selections                                                       | 71 |

|   | Device-Specific Layout                                                        | 78 |

#### Table of Contents

| 17 | Power-Up/-Down Behavior of Low Power Flash Devices | . 307 |

|----|----------------------------------------------------|-------|

|    | Introduction                                       | 307   |

|    | Flash Devices Support Power-Up Behavior            | 308   |

|    | Power-Up/-Down Sequence and Transient Current      |       |

|    | I/O Behavior at Power-Up/-Down                     | 311   |

|    | Cold-Sparing                                       | 316   |

|    | Hot-Swapping                                       |       |

|    | Conclusion                                         | 317   |

|    | Related Documents                                  | 318   |

|    | List of Changes                                    | 318   |

| Α  | Summary of Changes                                 | . 319 |

|    | History of Revision to Chapters                    |       |

| В  | Product Support                                    | . 321 |

|    | Customer Service                                   | 321   |

|    | Customer Technical Support Center                  | 32    |

|    | Technical Support                                  |       |

|    | Website                                            | 32′   |

|    | Contacting the Customer Technical Support Center   | 32′   |

|    | ITAR Technical Support                             |       |

|    | Indov                                              | 300   |

## **Device Overview**

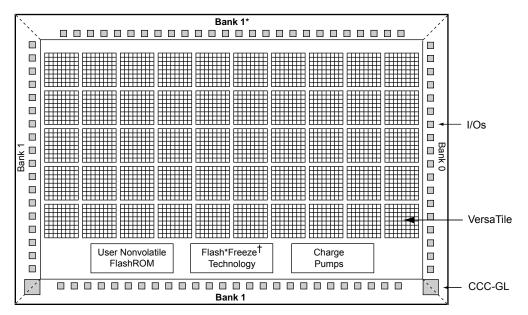

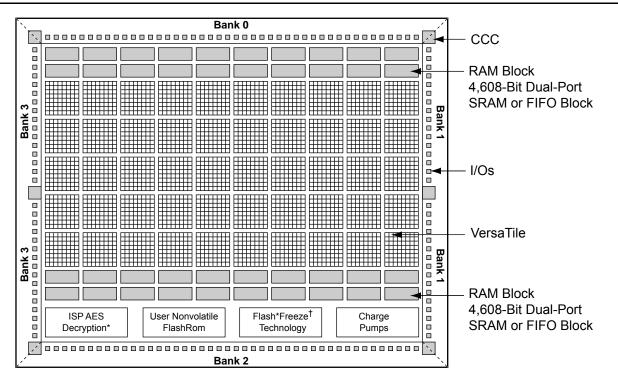

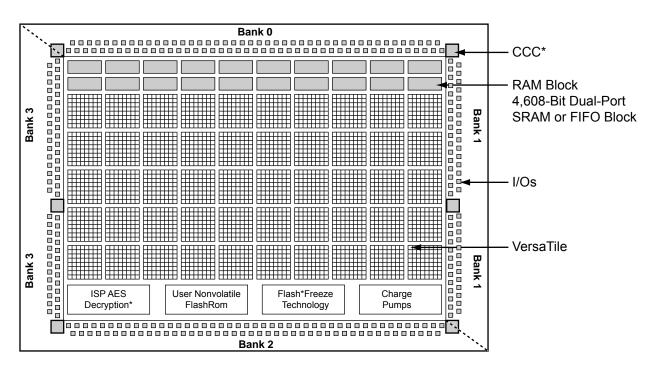

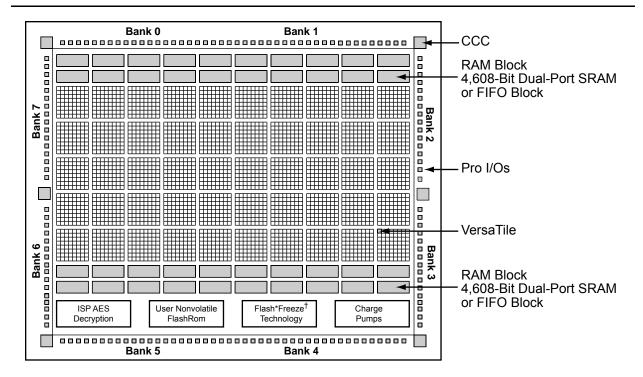

Low power flash devices consist of multiple distinct programmable architectural features (Figure 1-5 on page 13 through Figure 1-7 on page 14):

- FPGA fabric/core (VersaTiles)

- · Routing and clock resources (VersaNets)

- FlashROM

- · Dedicated SRAM and/or FIFO

- 30 k gate and smaller device densities do not support SRAM or FIFO.

- Automotive devices do not support FIFO operation.

- I/O structures

- Flash\*Freeze technology and low power modes

Notes: \* Bank 0 for the 30 k devices

† Flash\*Freeze mode is supported on IGLOO devices.

Figure 1-2 • IGLOO and ProASIC3 nano Device Architecture Overview with Two I/O Banks (applies to 10 k and 30 k device densities, excluding IGLOO PLUS devices)

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device Architecture Overview with Four I/O Banks (AGL600 device is shown)

Note: \* AGLP030 does not contain a PLL or support AES security.

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

Note: Flash\*Freeze technology only applies to IGLOOe devices.

Figure 1-7 • IGLOOe and ProASIC3E Device Architecture Overview (AGLE600 device is shown)

### I/O State of Newly Shipped Devices

Devices are shipped from the factory with a test design in the device. The power-on switch for VCC is OFF by default in this test design, so I/Os are tristated by default. Tristated means the I/O is not actively driven and floats. The exact value cannot be guaranteed when it is floating. Even in simulation software, a tristate value is marked as unknown. Due to process variations and shifts, tristated I/Os may float toward High or Low, depending on the particular device and leakage level.

If there is concern regarding the exact state of unused I/Os, weak pull-up/pull-down should be added to the floating I/Os so their state is controlled and stabilized.

Table 3-3 • Quadrant Global Pin Name (continued)

| 0.1.0.00       |                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •              | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GABO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GACO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBCO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDCO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GEAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GEBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GECO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

|                | GAB1/IOuxwByVz GACO/IOuxwByVz GAC1/IOuxwByVz GBA0/IOuxwByVz GBA1/IOuxwByVz GBB0/IOuxwByVz GBB1/IOuxwByVz GBC1/IOuxwByVz GBC1/IOuxwByVz GDA0/IOuxwByVz GDA1/IOuxwByVz GDA1/IOuxwByVz GDB1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GEA0/IOuxwByVz GEA0/IOuxwByVz GEA1/IOuxwByVz GEA1/IOuxwByVz GEA1/IOuxwByVz GEB1/IOuxwByVz |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

## **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

#### I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

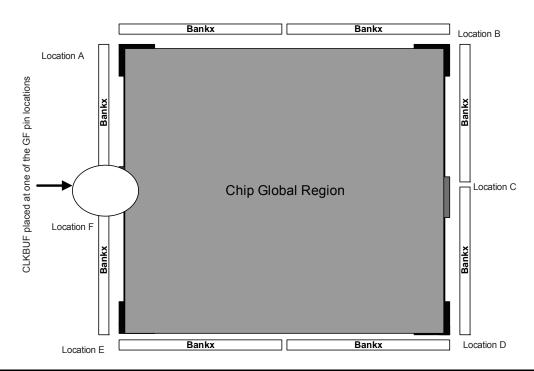

Figure 3-12 • Chip Global Region

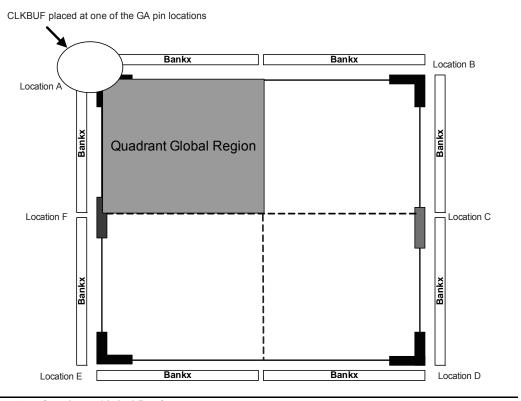

Figure 3-13 • Quadrant Global Region

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### **PLL Macro Signal Descriptions**

The PLL macro supports two inputs and up to six outputs. Table 4-3 gives a description of each signal.

Table 4-3 • Input and Output Signals of the PLL Block

| Signal    | Name                                  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----------|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKA      | Reference Clock                       | Input  | Reference clock input for PLL core; input clock for primary output clock, GLA                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| OADIVRST  | Reset Signal for the Output Divider A | Input  | For Fusion only. OADIVRST can be used when you bypass the PLL core (i.e., OAMUX = 001). The purpose of the OADIVRST signals is to reset the output of the final clock divider to synchronize it with the input to that divider when the PLL is bypassed. The signal is active on a low to high transition. The signal must be low for at least one divider input. If PLL core is used, this signal is "don't care" and the internal circuitry will generate the reset signal for the synchronization purpose. |  |

| OADIVHALF | Output A Division by<br>Half          | Input  | For Fusion only. Active high. Division by half feature. This feature can only be used when users bypass the PLL core (i.e., OAMUX 001) and the RC Oscillator (RCOSC) drives the CLKA input. This can be used to divide the 100 MHz RC oscillator by a factor of 1 2.5, 3.5, 4.5 14.5). Refer to Table 4-18 on page 95 for more information.                                                                                                                                                                   |  |

| EXTFB     | External Feedback                     | Input  | Allows an external signal to be compared to a reference clock in the PLL core's phase detector.                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| POWERDOWN | Power Down                            | Input  | Active low input that selects power-down mode and disables the PLL. With the POWERDOWN signal asserted, the PLL core sends 0 V signals on all of the outputs.                                                                                                                                                                                                                                                                                                                                                 |  |

| GLA       | Primary Output                        | Output | Primary output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| GLB       | Secondary 1 Output                    | Output | Secondary 1 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| YB        | Core 1 Output                         | Output | Core 1 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| GLC       | Secondary 2 Output                    | Output | Secondary 2 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| YC        | Core 2 Output                         | Output | Core 2 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| LOCK      | PLL Lock Indicator                    | Output | Active high signal indicating that steady-state lock has been achieved between CLKA and the PLL feedback signal                                                                                                                                                                                                                                                                                                                                                                                               |  |

#### Input Clock

The inputs to the input reference clock (CLKA) of the PLL can come from global input pins, regular I/O pins, or internally from the core. For Fusion families, the input reference clock can also be from the embedded RC oscillator or crystal oscillator.

## **Global Output Clocks**

GLA (Primary), GLB (Secondary 1), and GLC (Secondary 2) are the outputs of Global Multiplexer 1, Global Multiplexer 2, and Global Multiplexer 3, respectively. These signals (GLx) can be used to drive the high-speed global and quadrant networks of the low power flash devices.

A global multiplexer block consists of the input routing for selecting the input signal for the GLx clock and the output multiplexer, as well as delay elements associated with that clock.

#### **Core Output Clocks**

YB and YC are known as Core Outputs and can be used to drive internal logic without using global network resources. This is especially helpful when global network resources must be conserved and utilized for other timing-critical paths.

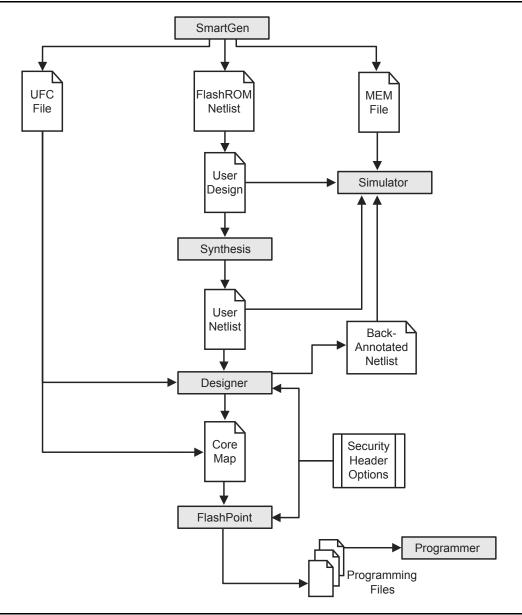

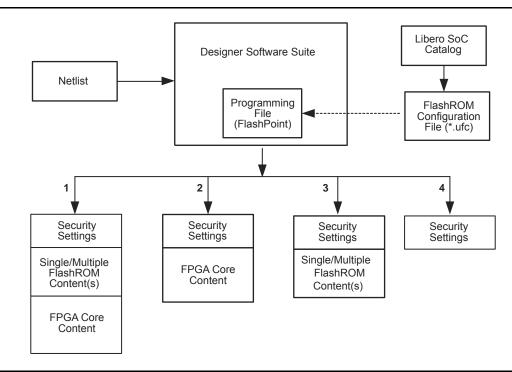

## FlashROM Design Flow

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

## Features Supported on Every I/O

Table 7-5 lists all features supported by transmitter/receiver for single-ended I/Os. Table 7-6 lists the performance of each I/O technology.

Table 7-5 • I/O Features

| Feature                           | Description                                                                                                                                           |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| All I/O                           | High performance (Table 7-6)                                                                                                                          |

|                                   | Electrostatic discharge (ESD) protection                                                                                                              |

|                                   | I/O register combining option                                                                                                                         |

| Single-Ended Transmitter Features | Hot-swap                                                                                                                                              |

|                                   | I/Os can be configured to behave in Flash*Freeze mode as tristate, HIGH, LOW, or to hold the previous state (not supported on ProASIC3 nano devices). |

|                                   | Programmable output slew rate: high and low                                                                                                           |

|                                   | Optional weak pull-up and pull-down resistors                                                                                                         |

|                                   | Output drive: 2 drive strengths (except for LVCMOS 1.2 V)                                                                                             |

|                                   | LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs                                                                                             |

| Single-Ended Receiver Features    | Selectable Schmitt trigger                                                                                                                            |

|                                   | 5 V–input–tolerant receiver (Table 7-12 on page 171)                                                                                                  |

|                                   | Separate ground plane for GNDQ pin and power plane for V <sub>CCI</sub> pin are used for input buffer to reduce output-induced noise.                 |

| DDR                               | DDR is supported for 60 k gate devices and above.                                                                                                     |

Table 7-6 • Maximum I/O Frequency

|                    | Maximum Performance                              |                                                                 |                                                   |  |  |

|--------------------|--------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------|--|--|

| Specification      | ProASIC3 nano 1.5 V<br>DC Core Supply<br>Voltage | IGLOO nano V2 or V5<br>Devices, 1.5 V DC Core<br>Supply Voltage | IGLOO nano V2,<br>1.2 V DC Core<br>Supply Voltage |  |  |

| LVTTL/LVCMOS 3.3 V | 200 MHz                                          | 180 MHz                                                         | TBD                                               |  |  |

| LVCMOS 2.5 V       | 250 MHz                                          | 230 MHz                                                         | TBD                                               |  |  |

| LVCMOS 1.8 V       | 200 MHz                                          | 180 MHz                                                         | TBD                                               |  |  |

| LVCMOS 1.5 V       | 130 MHz                                          | 120 MHz                                                         | TBD                                               |  |  |

| LVCMOS 1.2 V       | Not supported                                    | TBD                                                             | TBD                                               |  |  |

ProASIC3 nano FPGA Fabric User's Guide

#### I/O Features

Both IGLOO nano and ProASIC3 nano devices support multiple I/O features that make board design easier. For example, an I/O feature like Schmitt Trigger in the input buffer saves the board space that would be used by an external Schmitt trigger for a slow or noisy input signal. These features are also programmable for each I/O, which in turn gives flexibility in interfacing with other components. The following is a detailed description of all available features in nano devices.

#### I/O Programmable Features

Low power flash devices offer many flexible I/O features to support a wide variety of board designs. Some of the features are programmable, with a range for selection. Table 7-7 lists programmable I/O features and their ranges.

Table 7-7 • Programmable I/O Features (user control via I/O Attribute Editor)

| Feature                       | Description                    | Range               |

|-------------------------------|--------------------------------|---------------------|

| Slew Control Output slew rate |                                | HIGH, LOW           |

| Output Drive (mA)             | Output drive strength          | Depends on I/O type |

| Resistor Pull                 | Weak resistor pull circuit     | Up, Down, None      |

| Schmitt Trigger               | Schmitt trigger for input only | ON, OFF             |

#### **Hot-Swap Support**

All nano devices are hot-swappable.

The hot-swap feature appears as a read-only check box in the I/O Attribute Editor that shows whether an I/O is hot-swappable or not. Refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 307 for details on hot-swapping.

Hot-swapping is the operation of hot insertion or hot removal of a card in a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 7-8 on page 168 to Table 7-11 on page 169. The I/Os also need to be configured in hot-insertion mode if hot-plugging compliance is required. nano devices have an I/O structure that allows the support of Level 3 and Level 4 hot-swap with only two levels of staging.

I/O Software Control in Low Power Flash Devices

## **Automatically Assigning Technologies to I/O Banks**

The I/O Bank Assigner (IOBA) tool runs automatically when you run Layout. You can also use this tool from within the MultiView Navigator (Figure 8-17). The IOBA tool automatically assigns technologies and VREF pins (if required) to every I/O bank that does not currently have any technologies assigned to it. This tool is available when at least one I/O bank is unassigned.

To automatically assign technologies to I/O banks, choose I/O Bank Assigner from the **Tools** menu (or click the I/O Bank Assigner's toolbar button, shown in Figure 8-16).

#### Figure 8-16 • I/O Bank Assigner's Toolbar Button

Messages will appear in the Output window informing you when the automatic I/O bank assignment begins and ends. If the assignment is successful, the message "I/O Bank Assigner completed successfully" appears in the Output window, as shown in Figure 8-17.

Figure 8-17 • I/O Bank Assigner Displays Messages in Output Window

#### Types of Programming for Flash Devices

The number of devices to be programmed will influence the optimal programming methodology. Those available are listed below:

- · In-system programming

- Using a programmer

- Using a microprocessor or microcontroller

- · Device programmers

- Single-site programmers

- Multi-site programmers, batch programmers, or gang programmers

- Automated production (robotic) programmers

- Volume programming services

- Microsemi in-house programming

- Programming centers

#### In-System Programming

#### **Device Type Supported: Flash**

ISP refers to programming the FPGA after it has been mounted on the system printed circuit board. The FPGA may be preprogrammed and later reprogrammed using ISP.

The advantage of using ISP is the ability to update the FPGA design many times without any changes to the board. This eliminates the requirement of using a socket for the FPGA, saving cost and improving reliability. It also reduces programming hardware expenses, as the ISP methodology is die-/package-independent.

There are two methods of in-system programming: external and internal.

- Programmer ISP—Refer to the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" section on page 261 for more information.

- Using an external programmer and a cable, the device can be programmed through a header on the system board. In Microsemi SoC Products Group documentation, this is referred to as external ISP. Microsemi provides FlashPro4, FlashPro3, FlashPro Lite, or Silicon Sculptor 3 to perform external ISP. Note that Silicon Sculptor II and Silicon Sculptor 3 can only provide ISP for ProASIC and ProASICPLUS® families, not for SmartFusion, Fusion, IGLOO, or ProASIC3. Silicon Sculptor II and Silicon Sculptor 3 can be used for programming ProASIC and ProASICPLUS devices by using an adapter module (part number SMPA-ISP-ACTEL-3).

- Advantages: Allows local control of programming and data files for maximum security. The

programming algorithms and hardware are available from Microsemi. The only hardware

required on the board is a programming header.

- Limitations: A negligible board space requirement for the programming header and JTAG signal routing

- Microprocessor ISP—Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide for more information.

- Using a microprocessor and an external or internal memory, you can store the program in memory and use the microprocessor to perform the programming. In Microsemi documentation, this is referred to as internal ISP. Both the code for the programming algorithm and the FPGA programming file must be stored in memory on the board. Programming voltages must also be generated on the board.

- Advantages: The programming code is stored in the system memory. An external programmer is not required during programming.

- Limitations: This is the approach that requires the most design work, since some way of getting and/or storing the data is needed; a system interface to the device must be designed; and the low-level API to the programming firmware must be written and linked into the code provided by Microsemi. While there are benefits to this methodology, serious thought and planning should go into the decision.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

## IEEE 1532 (JTAG) Interface

The supported industry-standard IEEE 1532 programming interface builds on the IEEE 1149.1 (JTAG) standard. IEEE 1532 defines the standardized process and methodology for ISP. Both silicon and software issues are addressed in IEEE 1532 to create a simplified ISP environment. Any IEEE 1532 compliant programmer can be used to program low power flash devices. Device serialization is not supported when using the IEEE1532 standard. Refer to the standard for detailed information about IEEE 1532.

## **Security**

Unlike SRAM-based FPGAs that require loading at power-up from an external source such as a microcontroller or boot PROM, Microsemi nonvolatile devices are live at power-up, and there is no bitstream required to load the device when power is applied. The unique flash-based architecture prevents reverse engineering of the programmed code on the device, because the programmed data is stored in nonvolatile memory cells. Each nonvolatile memory cell is made up of small capacitors and any physical deconstruction of the device will disrupt stored electrical charges.

Each low power flash device has a built-in 128-bit Advanced Encryption Standard (AES) decryption core, except for the 30 k gate devices and smaller. Any FPGA core or FlashROM content loaded into the device can optionally be sent as encrypted bitstream and decrypted as it is loaded. This is particularly suitable for applications where device updates must be transmitted over an unsecured network such as the Internet. The embedded AES decryption core can prevent sensitive data from being intercepted (Figure 12-1 on page 265). A single 128-bit AES Key (32 hex characters) is used to encrypt FPGA core programming data and/or FlashROM programming data in the Microsemi tools. The low power flash devices also decrypt with a single 128-bit AES Key. In addition, low power flash devices support a Message Authentication Code (MAC) for authentication of the encrypted bitstream on-chip. This allows the encrypted bitstream to be authenticated and prevents erroneous data from being programmed into the device. The FPGA core, FlashROM, and Flash Memory Blocks (FBs), in Fusion only, can be updated independently using a programming file that is AES-encrypted (cipher text) or uses plain text.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

- 3. A single STAPL file or multiple STAPL files with multiple FlashROM contents. A single STAPL file will be generated if the device serialization feature is not used. You can program the whole FlashROM or selectively program individual pages.

- A single STAPL file to configure the security settings for the device, such as the AES Key and/or Pass Key.

Figure 12-4 • Flexible Programming File Generation for Different Applications

## **Programming Solution**

For device programming, any IEEE 1532–compliant programmer can be used; however, the FlashPro4/3/3X programmer must be used to control the low power flash device's rich security features and FlashROM programming options. The FlashPro4/3/3X programmer is a low-cost portable programmer for the Microsemi flash families. It can also be used with a powered USB hub for parallel programming. General specifications for the FlashPro4/3/3X programmer are as follows:

- Programming clock TCK is used with a maximum frequency of 20 MHz, and the default frequency is 4 MHz.

- Programming file STAPL

- Daisy chain Supported. You can use the ChainBuilder software to build the programming file for the chain.

- Parallel programming Supported. Multiple FlashPro4/3/3X programmers can be connected together using a powered USB hub or through the multiple USB ports on the PC.

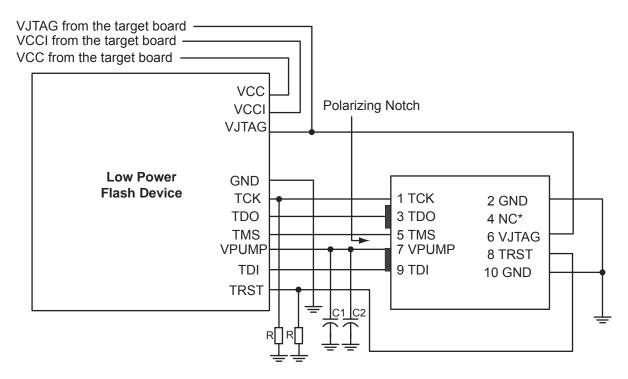

- Power supply The target board must provide VCC, VCCI, VPUMP, and VJTAG during programming. However, if there is only one device on the target board, the FlashPro4/3/3X programmer can generate the required VPUMP voltage from the USB port.

## **Board-Level Considerations**

A bypass capacitor is required from VPUMP to GND for all low power flash devices during programming. This bypass capacitor protects the devices from voltage spikes that may occur on the VPUMP supplies during the erase and programming cycles. Refer to the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for specific recommendations. For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible. The bypass capacitor must be placed within 2.5 cm of the device pins.

Note: \*NC (FlashPro3/3X); Prog\_Mode (FlashPro4). Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 12-6 • Board Layout and Programming Header Top View

## **Troubleshooting Signal Integrity**

#### Symptoms of a Signal Integrity Problem

A signal integrity problem can manifest itself in many ways. The problem may show up as extra or dropped bits during serial communication, changing the meaning of the communication. There is a normal variation of threshold voltage and frequency response between parts even from the same lot. Because of this, the effects of signal integrity may not always affect different devices on the same board in the same way. Sometimes, replacing a device appears to make signal integrity problems go away, but this is just masking the problem. Different parts on identical boards will exhibit the same problem sooner or later. It is important to fix signal integrity problems early. Unless the signal integrity problems are severe enough to completely block all communication between the device and the programmer, they may show up as subtle problems. Some of the FlashPro4/3/3X exit codes that are caused by signal integrity problems are listed below. Signal integrity problems are not the only possible cause of these

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

| Date                     | Changes                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010<br>(continued) | The "Chain Integrity Test Error Analyze Chain Failure" section was renamed to the "Scan Chain Failure" section, and the Analyze Chain command was changed to Scan Chain. It was noted that occasionally a faulty programmer can cause scan chain failures.                                                                                                                                   | 272  |

| v1.5<br>(August 2009)    | The "CoreMP7 Device Security" section was removed from "Security in ARM-Enabled Low Power Flash Devices", since M7-enabled devices are no longer supported.                                                                                                                                                                                                                                  | 265  |

| v1.4<br>(December 2008)  | The "ISP Architecture" section was revised to include information about core voltage for IGLOO V2 and ProASIC3L devices, as well as 50 mV increments allowable in Designer software.                                                                                                                                                                                                         | 261  |

|                          | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                            | 262  |

|                          | A second capacitor was added to Figure 12-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                                                                                                  | 271  |

| v1.3<br>(October 2008)   | The "ISP Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                  | 262  |

| v1.2<br>(June 2008)      | The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs Supporting ISP:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                    | 262  |

| v1.1<br>(March 2008)     | The "ISP Architecture" section was updated to included the IGLOO PLUS family in the discussion of family-specific support. The text, "When 1.2 V is used, the device can be reprogrammed in-system at 1.5 V only," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when all supplies (VCC, VCCI, and VJTAG) are at 1.5 V." | 261  |

|                          | The "ISP Support in Flash-Based Devices" section and Table 12-1 • Flash-Based FPGAs Supporting ISP were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 262  |

|                          | The "Security" section was updated to mention that 15 k gate devices do not have a built-in 128-bit decryption core.                                                                                                                                                                                                                                                                         | 264  |

|                          | Table 12-2 • Power Supplies was revised to remove the Normal Operation column and add a table note stating, "All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation."                                                                                                                                                                           | 263  |

|                          | The "ISP Programming Header Information" section was revised to change FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT. Table 12-3 • Programming Header Ordering Codes was updated with the same change, as well as adding the part number FFSD-05-D-06.00-01-N, a 10-pin cable with 50-mil-pitch sockets.                                                                                        | 269  |

|                          | The "Board-Level Considerations" section was updated to describe connecting two capacitors in parallel across VPUMP and GND for proper programming.                                                                                                                                                                                                                                          | 271  |

| v1.0<br>(January 2008)   | Information was added to the "Programming Voltage (VPUMP) and VJTAG" section about the JTAG interface pin.                                                                                                                                                                                                                                                                                   | 263  |

| 51900055-2/7.06          | ACTgen was changed to SmartGen.                                                                                                                                                                                                                                                                                                                                                              | N/A  |

|                          | In Figure 12-6 • Board Layout and Programming Header Top View, the order of the text was changed to:  VJTAG from the target board  VCCI from the target board  VCC from the target board                                                                                                                                                                                                     | 271  |

# A - Summary of Changes

## **History of Revision to Chapters**

The following table lists chapters that were affected in each revision of this document. Each chapter includes its own change history because it may appear in other device family user's guides. Refer to the individual chapter for a list of specific changes.

| Revision<br>(month/year)       | Chapter Affected                                                                                                                                    | List of Changes (page number) |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Revision 5<br>(September 2012) | "Microprocessor Programming of Microsemi's Low Power Flash Devices" was revised.                                                                    | 290                           |

| Revision 4<br>(August 2012)    | "FPGA Array Architecture in Low Power Flash Devices" was revised.                                                                                   | 20                            |

|                                | The "Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs" chapter was added (SAR 32020).                                                          | 21                            |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "SRAM and FIFO Memories in Microsemi's Low Power Flash Devices" was revised.                                                                        | 157                           |

|                                | "I/O Structures in nano Devices" was revised.                                                                                                       | 183                           |

|                                | The "Pin Descriptions" and "Packaging" chapters were removed. This information is now published in the datasheet for each product line (SAR 34772). | N/A                           |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                              | 273                           |

|                                | "Boundary Scan in Low Power Flash Devices" was revised.                                                                                             | 296                           |

| Revision 3<br>(December 2011)  | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "UJTAG Applications in Microsemi's Low Power Flash Devices" was revised.                                                                            | 306                           |

| Revision 2<br>(June 2011)      | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "I/O Structures in nano Devices" was revised.                                                                                                       | 183                           |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                      | 204                           |

|                                | "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" was revised.                                              | 273                           |

| Revision 1<br>(July 2010)      | "Global Resources in Low Power Flash Devices" was revised.                                                                                          | 59                            |

|                                | "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" was revised.                                                        | 113                           |

|                                | "I/O Software Control in Low Power Flash Devices" was revised.                                                                                      | 204                           |

|                                | "DDR for Microsemi's Low Power Flash Devices" was revised.                                                                                          | 219                           |

|                                | "Programming Flash Devices" was revised.                                                                                                            | 232                           |