Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 34                                                                        |

| Number of Gates                | 10000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package        | 48-QFN (6x6)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn010-2qng48i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note: † Flash\*Freeze mode is supported on IGLOO devices.

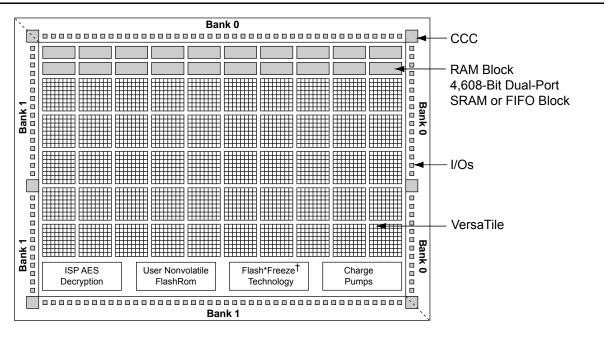

Figure 1-3 • IGLOO Device Architecture Overview with Two I/O Banks with RAM and PLL (60 k and 125 k gate densities)

Note: † Flash\*Freeze mode is supported on IGLOO devices.

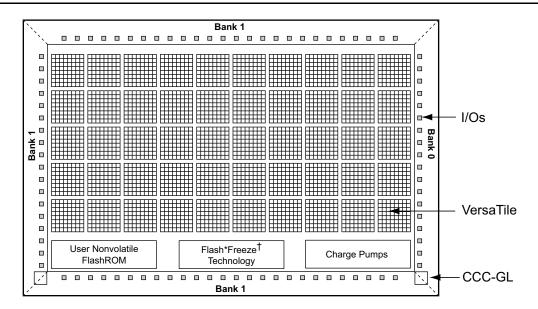

Figure 1-4 • IGLOO Device Architecture Overview with Three I/O Banks (AGLN015, AGLN020, A3PN015, and A3PN020)

#### Figure 3-18 • Globals Management GUI in Designer

- 3. Occasionally, the synthesis tool assigns a global macro to clock nets, even though the fanout is significantly less than other asynchronous signals. Select **Demote global nets whose fanout is less than** and enter a reasonable value for fanouts. This frees up some global networks from the signals that have very low fanouts. This can also be done using PDC.

- 4. Use a local clock network for the signals that do not need to go to the whole chip but should have low skew. This local clock network assignment can only be done using PDC.

- 5. Assign the I/O buffer using MVN if you have fixed I/O assignment. As shown in Figure 3-10 on page 45, there are three sets of global pins that have a hardwired connection to each global network. Do not try to put multiple CLKBUF macros in these three sets of global pins. For example, do not assign two CLKBUFs to GAA0x and GAA2x pins.

- 6. You must click **Commit** at the end of MVN assignment. This runs the pre-layout checker and checks the validity of global assignment.

- 7. Always run Compile with the **Keep existing physical constraints** option on. This uses the quadrant clock network assignment in the MVN assignment and checks if you have the desired signals on the global networks.

- 8. Run Layout and check the timing.

ProASIC3 nano FPGA Fabric User's Guide

YB and YC are identical to GLB and GLC, respectively, with the exception of a higher selectable final output delay. The SmartGen PLL Wizard will configure these outputs according to user specifications and can enable these signals with or without the enabling of Global Output Clocks.

The above signals can be enabled in the following output groupings in both internal and external feedback configurations of the static PLL:

- · One output GLA only

- Two outputs GLA + (GLB and/or YB)

- Three outputs GLA + (GLB and/or YB) + (GLC and/or YC)

## **PLL Macro Block Diagram**

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global network access, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC).

There are delay elements in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven in the following ways:

- 1. By an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

- 2. Directly from the FPGA core.

- 3. From an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

During power-up, the PLL outputs will toggle around the maximum frequency of the voltage-controlled oscillator (VCO) gear selected. Toggle frequencies can range from 40 MHz to 250 MHz. This will continue as long as the clock input (CLKA) is constant (HIGH or LOW). This can be prevented by LOW assertion of the POWERDOWN signal.

The visual PLL configuration in SmartGen, a component of the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user.

Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

| Config.<br>Bits | Signal              | Name                             | Description                                                                                                                                     |  |

|-----------------|---------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 83              | RXCSEL <sup>1</sup> | CLKC input selection             | Select the CLKC input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 82              | RXBSEL <sup>1</sup> | CLKB input selection             | Select the CLKB input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 81              | RXASEL <sup>1</sup> | CLKA input selection             | Select the CLKA input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                  |  |

| 80              | RESETEN             | Reset Enable                     | Enables (active high) the synchronization of PLL output dividers after dynamic reconfiguration (SUPDATE). The Reset Enable signal is READ-ONLY. |  |

| 79              | DYNCSEL             | Clock Input C Dynamic<br>Select  | Configures clock input C to be sent to GLC for dynamic control. <sup>2</sup>                                                                    |  |

| 78              | DYNBSEL             | Clock Input B Dynamic<br>Select  | Configures clock input B to be sent to GLB for dynamic control. <sup>2</sup>                                                                    |  |

| 77              | DYNASEL             | Clock Input A Dynamic<br>Select  | Configures clock input A for dynamic PLL configuration. <sup>2</sup>                                                                            |  |

| <76:74>         | VCOSEL[2:0]         | VCO Gear Control                 | Three-bit VCO Gear Control for four frequence ranges (refer to Table 4-19 on page 95 and Table 4-20 on page 95).                                |  |

| 73              | STATCSEL            | MUX Select on Input C            | MUX selection for clock input C <sup>2</sup>                                                                                                    |  |

| 72              | STATBSEL            | MUX Select on Input B            | MUX selection for clock input B <sup>2</sup>                                                                                                    |  |

| 71              | STATASEL            | MUX Select on Input A            | MUX selection for clock input A <sup>2</sup>                                                                                                    |  |

| <70:66>         | DLYC[4:0]           | YC Output Delay                  | Sets the output delay value for YC.                                                                                                             |  |

| <65:61>         | DLYB[4:0]           | YB Output Delay                  | Sets the output delay value for YB.                                                                                                             |  |

| <60:56>         | DLYGLC[4:0]         | GLC Output Delay                 | Sets the output delay value for GLC.                                                                                                            |  |

| <55:51>         | DLYGLB[4:0]         | GLB Output Delay                 | Sets the output delay value for GLB.                                                                                                            |  |

| <50:46>         | DLYGLA[4:0]         | Primary Output Delay             | Primary GLA output delay                                                                                                                        |  |

| 45              | XDLYSEL             | System Delay Select              | When selected, inserts System Delay in the feedback path in Figure 4-20 on page 85.                                                             |  |

| <44:40>         | FBDLY[4:0]          | Feedback Delay                   | Sets the feedback delay value for the feedback element in Figure 4-20 on page 85.                                                               |  |

| <39:38>         | FBSEL[1:0]          | Primary Feedback Delay<br>Select | Controls the feedback MUX: no delay, include programmable delay element, or use external feedback.                                              |  |

| <37:35>         | OCMUX[2:0]          | Secondary 2 Output<br>Select     | Selects from the VCO's four phase outputs for GLC/YC.                                                                                           |  |

| <34:32>         | OBMUX[2:0]          | Secondary 1 Output<br>Select     | Selects from the VCO's four phase outputs for GLB/YB.                                                                                           |  |

#### Notes:

- 1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

- 2. This value depends on the input clock source, so Layout must complete before these bits can be set.

After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools >

Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

```

DYNCCC Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN), .GLA(GLA), .LOCK(LOCK),

.CLKB(CLKB), .GLB(GLB), .YB(), .CLKC(CLKC), .GLC(GLC), .YC(), .SDIN(SDIN),

.SCLK(SCLK), .SSHIFT(SSHIFT), .SUPDATE(SUPDATE), .MODE(MODE), .SDOUT(SDOUT),

.OADIV0(GND), .OADIV1(GND), .OADIV2(VCC), .OADIV3(GND), .OADIV4(GND), .OAMUX0(GND),

.OAMUX1(GND), .OAMUX2(VCC), .DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND),

.DLYGLA3(GND), .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND), .OBMUX2(GND), .DLYYB0(GND),

.DLYYB1(GND), .DLYYB2(GND), .DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND),

.DLYGLB1(GND), .DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

. \texttt{OCDIV1}(\texttt{GND}) \,, \, \, . \texttt{OCDIV2}(\texttt{GND}) \,, \, \, . \texttt{OCDIV3}(\texttt{GND}) \,, \, \, . \texttt{OCDIV4}(\texttt{GND}) \,, \, \, . \texttt{OCMUX0}(\texttt{GND}) \,, \, \, . \texttt{OCMUX1}(\texttt{GND}) \,, \, \, . \\

. \texttt{OCMUX2}(\texttt{GND}) \,, \; . \texttt{DLYYC0}(\texttt{GND}) \,, \; . \texttt{DLYYC1}(\texttt{GND}) \,, \; . \texttt{DLYYC2}(\texttt{GND}) \,, \; . \texttt{DLYYC3}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND})

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND), .DLYGLC4(GND),

.FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(VCC), .FINDIV3(GND), .FINDIV4(GND),

.FINDIV5(GND), .FINDIV6(GND), .FBDIV0(GND), .FBDIV1(GND), .FBDIV2(GND),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(VCC), .FBDIV6(GND), .FBDLY1(GND), .FBDLY1(GND),

.FBDLY2(GND), .FBDLY3(GND), .FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND),

.XDLYSEL(GND), .VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(VCC));

defparam Core.VCOFREQUENCY = 165.000;

```

endmodule

## **Delayed Clock Configuration**

The CLKDLY macro can be generated with the desired delay and input clock source (Hardwired I/O, External I/O, or Core Logic), as in Figure 4-28.

#### Figure 4-28 • Delayed Clock Configuration Dialog Box

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

: delay_macro

Name

Family

: ProASIC3

: Verilog

Output Format

: Delayed Clock

Type

Delay Index

CLKA Source

: Hardwired I/O

Total Clock Delay = 0.935 ns.

The resultant CLKDLY macro Verilog netlist is as follows:

module delay_macro(GL,CLK);

output GL;

input CLK;

```

ProASIC3 nano FPGA Fabric User's Guide

• Use quadrant global region assignments by finding the clock net associated with the CCC macro under the Nets tab and creating a quadrant global region for the net, as shown in Figure 4-33.

Figure 4-33 • Quadrant Clock Assignment for a Global Net

#### External I/O-Driven CCCs

The above-mentioned recommendation for proper layout techniques will ensure the correct assignment. It is possible that, especially with External I/O–Driven CCC macros, placement of the CCC macro in a desired location may not be achieved. For example, assigning an input port of an External I/O–Driven CCC near a particular CCC location does not guarantee global assignments to the desired location. This is because the clock inputs of External I/O–Driven CCCs can be assigned to any I/O location; therefore, it is possible that the CCC connected to the clock input will be routed to a location other than the one closest to the I/O location, depending on resource availability and placement constraints.

#### **Clock Placer**

The clock placer is a placement engine for low power flash devices that places global signals on the chip global and quadrant global networks. Based on the clock assignment constraints for the chip global and quadrant global clocks, it will try to satisfy all constraints, as well as creating quadrant clock regions when necessary. If the clock placer fails to create the quadrant clock regions for the global signals, it will report an error and stop Layout.

The user must ensure that the constraints set to promote clock signals to quadrant global networks are valid.

## **Cascading CCCs**

The CCCs in low power flash devices can be cascaded. Cascading CCCs can help achieve more accurate PLL output frequency results than those achievable with a single CCC. In addition, this technique is useful when the user application requires the output clock of the PLL to be a multiple of the reference clock by an integer greater than the maximum feedback divider value of the PLL (divide by 128) to achieve the desired frequency.

For example, the user application may require a 280 MHz output clock using a 2 MHz input reference clock, as shown in Figure 4-34 on page 110.

FlashROM in Microsemi's Low Power Flash Devices

## Conclusion

The Fusion, IGLOO, and ProASIC3 families are the only FPGAs that offer on-chip FlashROM support. This document presents information on the FlashROM architecture, possible applications, programming, access through the JTAG and UJTAG interface, and integration into your design. In addition, the Libero tool set enables easy creation and modification of the FlashROM content.

The nonvolatile FlashROM block in the FPGA can be customized, enabling multiple applications.

Additionally, the security offered by the low power flash devices keeps both the contents of FlashROM and the FPGA design safe from system over-builders, system cloners, and IP thieves.

## **Related Documents**

### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/documents/FlashPro UG.pdf

## **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                                                                                                                                                                                                                      | Changes                                                                                                                                                                           |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| July 2010                                                                                                                                                                                                                 | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                         |          |

| v1.4<br>(December 2008)                                                                                                                                                                                                   | IGLOO nano and ProASIC3 nano devices were added to Table 5-1 • Flash-Based FPGAs.                                                                                                 |          |

| v1.3<br>(October 2008)                                                                                                                                                                                                    | The "FlashROM Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                  |          |

|                                                                                                                                                                                                                           | Figure 5-2 • Fusion Device Architecture Overview (AFS600) was replaced. Figure 5-5 • Programming FlashROM Using AES was revised to change "Fusion" to "Flash Device."             | 119, 121 |

|                                                                                                                                                                                                                           | The FlashPoint User's Guide was removed from the "User's Guides" section, as its content is now part of the FlashPro User's Guide.                                                | 130      |

| v1.2 (June 2008)  The following changes were made to the family descriptions in Table 5-1 • Flash Based FPGAs: • ProASIC3L was updated to include 1.5 V. • The number of PLLs for ProASIC3E was changed from five to six. |                                                                                                                                                                                   | 118      |

| v1.1<br>(March 2008)                                                                                                                                                                                                      | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new. |          |

#### **SRAM Features**

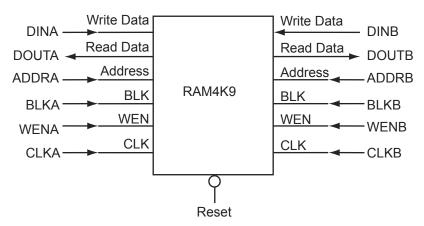

#### RAM4K9 Macro

RAM4K9 is the dual-port configuration of the RAM block (Figure 6-4). The RAM4K9 nomenclature refers to both the deepest possible configuration and the widest possible configuration the dual-port RAM block can assume, and does not denote a possible memory aspect ratio. The RAM block can be configured to the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, and 512×9. RAM4K9 is fully synchronous and has the following features:

- Two ports that allow fully independent reads and writes at different frequencies

- Selectable pipelined or nonpipelined read

- Active-low block enables for each port

- Toggle control between read and write mode for each port

- · Active-low asynchronous reset

- Pass-through write data or hold existing data on output. In pass-through mode, the data written to the write port will immediately appear on the read port.

- Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

Note: For timing diagrams of the RAM signals, refer to the appropriate family datasheet.

Figure 6-4 • RAM4K9 Simplified Configuration

#### Signal Descriptions for RAM4K9

Note: Automotive ProASIC3 devices support single-port SRAM capabilities, or dual-port SRAM only under specific conditions. Dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). Since Libero SoC macro libraries support a dual-port macro only, certain modifications must be made. These are detailed below.

The following signals are used to configure the RAM4K9 memory element:

#### **WIDTHA and WIDTHB**

These signals enable the RAM to be configured in one of four allowable aspect ratios (Table 6-2 on page 138).

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WIDTHB should be tied to ground.

Note: For timing diagrams of the RAM signals, refer to the appropriate family datasheet.

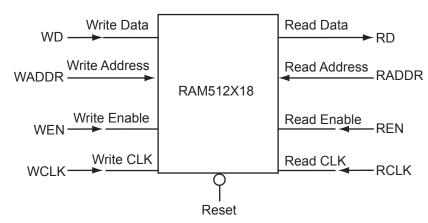

Figure 6-5 • 512X18 Two-Port RAM Block Diagram

#### Signal Descriptions for RAM512X18

RAM512X18 has slightly different behavior from RAM4K9, as it has dedicated read and write ports.

#### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 6-5).

Table 6-5 • Aspect Ratio Settings for WW[1:0]

| WW[1:0] | RW[1:0] | D×W      |

|---------|---------|----------|

| 01      | 01      | 512×9    |

| 10      | 10      | 256×18   |

| 00, 11  | 00, 11  | Reserved |

#### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512×9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, RD[17:9] are undefined.

#### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256×18 aspect ratio is used for write or read, WADDR[8] and RADDR[8] are unused and must be grounded.

#### WCLK and RCLK

These signals are the write and read clocks, respectively. They can be clocked on the rising or falling edge of WCLK and RCLK.

#### WEN and REN

These signals are the write and read enables, respectively. They are both active-low by default. These signals can be configured as active-high.

#### **RESET**

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### **PIPE**

This signal is used to specify pipelined read on the output. A LOW on PIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

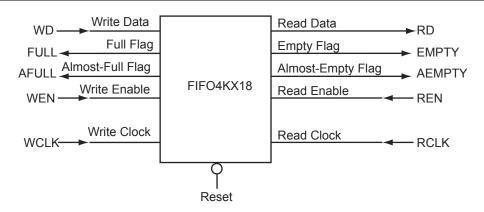

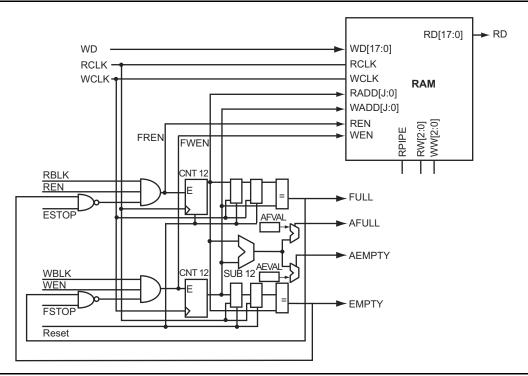

Figure 6-6 • FIFO4KX18 Block Diagram

Figure 6-7 • RAM Block with Embedded FIFO Controller

The FIFOs maintain a separate read and write address. Whenever the difference between the write address and the read address is greater than or equal to the almost-full value (AFVAL), the Almost-Full flag is asserted. Similarly, the Almost-Empty flag is asserted whenever the difference between the write address and read address is less than or equal to the almost-empty value (AEVAL).

Due to synchronization between the read and write clocks, the Empty flag will deassert after the second read clock edge from the point that the write enable asserts. However, since the Empty flag is synchronized to the read clock, it will assert after the read clock reads the last data in the FIFO. Also, since the Full flag is dependent on the actual hardware configuration, it will assert when the actual physical implementation of the FIFO is full.

For example, when a user configures a 128×18 FIFO, the actual physical implementation will be a 256×18 FIFO element. Since the actual implementation is 256×18, the Full flag will not trigger until the

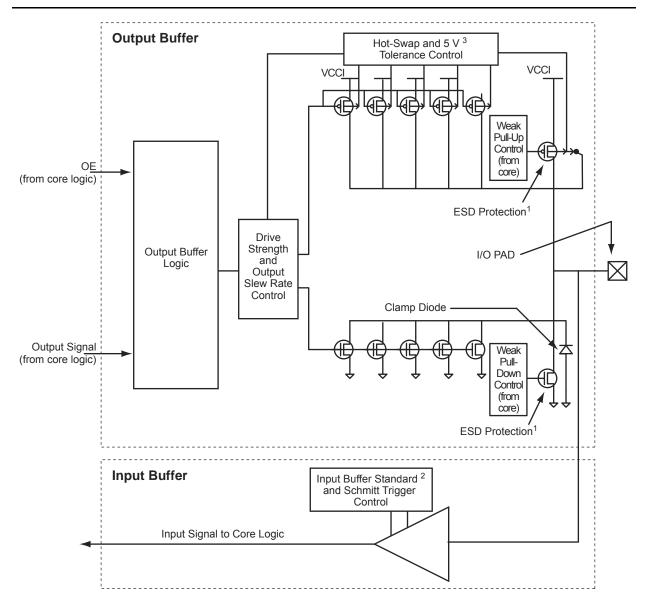

## I/O Bank Structure

Low power flash device I/Os are divided into multiple technology banks. The number of banks is device-dependent, supporting two, three, or four banks. Each bank has its own  $V_{CCI}$  power supply pin. Refer to Figure 7-2 on page 160 for more information.

#### Notes:

- 1. All NMOS transistors connected to the I/O pad serve as ESD protection.

- 2. See Table 7-2 on page 162 for available I/O standards.

- 3. 5 V tolerance requires external resistor.

Figure 7-3 • Simplified I/O Buffer Circuitry

ProASIC3 nano FPGA Fabric User's Guide

- If one of the registers has a PRE pin, all the other registers that are candidates for combining in the I/O must have a PRE pin.

- If one of the registers has neither a CLR nor a PRE pin, all the other registers that are candidates for combining must have neither a CLR nor a PRE pin.

- If the clear or preset pins are present, they must have the same polarity.

- If the clear or preset pins are present, they must be driven by the same signal (net).

- For single-tile devices (10 k, 15 k, and 20 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock function (both CLR and CLK are shared among all registers):

- Both the Output and Output Enable registers must not have an E pin (clock enable).

- 4. For dual-tile devices (60 k, 125 k, and 250 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock and enable function:

- Both the Output and Output Enable registers must have an E pin (clock enable), or none at all.

- If the E pins are present, they must have the same polarity. The CLK pins must also have the same polarity.

In some cases, the user may want registers to be combined with the input of a bibuf while maintaining the output as-is. This can be achieved by using PDC commands as follows:

```

set_io <signal name> -REGISTER yes ----register will combine

set_preserve <signal name> ----register will not combine

```

## Weak Pull-Up and Weak Pull-Down Resistors

nano devices support optional weak pull-up and pull-down resistors on each I/O pin. When the I/O is pulled up, it is connected to the  $V_{\text{CCI}}$  of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to the datasheet for more information.

For low power applications and when using IGLOO nano devices, configuration of the pull-up or pull-down of the I/O can be used to set the I/O to a known state while the device is in Flash\*Freeze mode. Refer to "Flash\*Freeze Technology and Low Power Modes" in an applicable FPGA fabric user's guide for more information.

The Flash\*Freeze (FF) pin cannot be configured with a weak pull-down or pull-up I/O attribute, as the signal needs to be driven at all times.

## **Output Slew Rate Control**

The slew rate is the amount of time an input signal takes to get from logic LOW to logic HIGH or vice versa

It is commonly defined as the propagation delay between 10% and 90% of the signal's voltage swing. Slew rate control is available for the output buffers of low power flash devices. The output buffer has a programmable slew rate for both HIGH-to-LOW and LOW-to-HIGH transitions.

The slew rate can be implemented by using a PDC command (Table 7-5 on page 163), setting it "High" or "Low" in the I/O Attribute Editor in Designer, or instantiating a special I/O macro. The default slew rate value is "High."

Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

## **Output Drive**

The output buffers of nano devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

I/O Software Control in Low Power Flash Devices

## Flash FPGAs I/O Support

The flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

Table 8-1 • Flash-Based FPGAs

| Series                            | Family*              | Description                                                                                                                                                                                    |  |

|-----------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGL00                             | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |

|                                   | IGLO0e               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |

|                                   | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |

|                                   | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |

| ProASIC3                          | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |

|                                   | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |

|                                   | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |

|                                   | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |

|                                   | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |

|                                   | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |

| Automotive ProASIC3 ProASIC3 FPG/ |                      | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |

| Fusion                            | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Input Support for DDR**

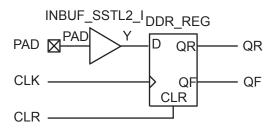

The basic structure to support a DDR input is shown in Figure 9-2. Three input registers are used to capture incoming data, which is presented to the core on each rising edge of the I/O register clock. Each I/O tile supports DDR inputs.

Figure 9-2 • DDR Input Register Support in Low Power Flash Devices

## **Output Support for DDR**

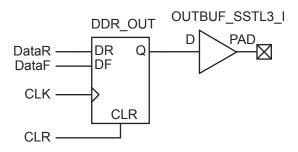

The basic DDR output structure is shown in Figure 9-1 on page 205. New data is presented to the output every half clock cycle.

Note: DDR macros and I/O registers do not require additional routing. The combiner automatically recognizes the DDR macro and pushes its registers to the I/O register area at the edge of the chip. The routing delay from the I/O registers to the I/O buffers is already taken into account in the DDR macro.

Figure 9-3 • DDR Output Register (SSTL3 Class I)

· Programming Centers

Microsemi programming hardware policy also applies to programming centers. Microsemi expects all programming centers to use certified programmers to program Microsemi devices. If a programming center uses noncertified programmers to program Microsemi devices, the "Noncertified Programmers" policy applies.

## **Important Programming Guidelines**

## **Preprogramming Setup**

Before programming, several steps are required to ensure an optimal programming yield.

### Use Proper Handling and Electrostatic Discharge (ESD) Precautions

Microsemi FPGAs are sensitive electronic devices that are susceptible to damage from ESD and other types of mishandling. For more information about ESD, refer to the *Quality and Reliability Guide*, beginning with page 41.

# Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)

The files used to program Microsemi flash devices (\*.bit, \*.stp, \*.pdb) contain important information about the switches that will be programmed in the FPGA. Find the latest version and corresponding release notes at http://www.microsemi.com/soc/download/software/designer/. Also, programming files must always be zipped during file transfer to avoid the possibility of file corruption.

### Use the Latest Version of the Programming Software

The programming software is frequently updated to accommodate yield enhancements in FPGA manufacturing. These updates ensure maximum programming yield and minimum programming times. Before programming, always check the version of software being used to ensure it is the most recent. Depending on the programming software, refer to one of the following:

- · FlashPro: http://www.microsemi.com/soc/download/program\_debug/flashpro/

- · Silicon Sculptor: http://www.microsemi.com/soc/download/program\_debug/ss/

### Use the Most Recent Adapter Module with Silicon Sculptor

Occasionally, Microsemi makes modifications to the adapter modules to improve programming yields and programming times. To identify the latest version of each module before programming, visit <a href="http://www.microsemi.com/soc/products/hardware/program">http://www.microsemi.com/soc/products/hardware/program</a> debug/ss/modules.aspx.

#### Perform Routine Hardware Self-Diagnostic Test

- Adapter modules must be regularly cleaned. Adapter modules need to be inserted carefully into the programmer to make sure the DIN connectors (pins at the back side) are not damaged.

- FlashPro

The self-test is only applicable when programming with FlashPro and FlashPro3 programmers. It is not supported with FlashPro4 or FlashPro Lite. To run the self-diagnostic test, follow the instructions given in the "Performing a Self-Test" section of http://www.microsemi.com/soc/documents/FlashPro UG.pdf.

Silicon Sculptor

The self-diagnostic test verifies correct operation of the pin drivers, power supply, CPU, memory, and adapter module. This test should be performed with an adapter module installed and before every programming session. At minimum, the test must be executed every week. To perform self-diagnostic testing using the Silicon Sculptor software, perform the following steps, depending on the operating system:

- DOS: From anywhere in the software, type ALT + D.

- Windows: Click Device > choose Actel Diagnostic > select the Test tab > click OK.

Silicon Sculptor programmers must be verified annually for calibration. Refer to the *Silicon Sculptor Verification of Calibration Work Instruction* document on the website.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

Table 12-4 • Programming Header Pin Numbers and Description

| Pin | Signal             | Source                  | Description                                                                                                                        |  |

|-----|--------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | TCK                | Programmer              | JTAG Clock                                                                                                                         |  |

| 2   | GND <sup>1</sup>   | -                       | Signal Reference                                                                                                                   |  |

| 3   | TDO                | Target Board            | Test Data Output                                                                                                                   |  |

| 4   | NC                 | -                       | No Connect (FlashPro3/3X); Prog_Mode (FlashPro4) See note associated with Figure 12-5 on page 26 regarding Prog_Mode on FlashPro4. |  |

| 5   | TMS                | Programmer              | Test Mode Select                                                                                                                   |  |

| 6   | VJTAG              | Target Board            | JTAG Supply Voltage                                                                                                                |  |

| 7   | VPUMP <sup>2</sup> | Programmer/Target Board | Programming Supply Voltage                                                                                                         |  |

| 8   | nTRST              | Programmer              | JTAG Test Reset (Hi-Z with 10 k $\Omega$ pull-down, HIGH LOW, or toggling)                                                         |  |

| 9   | TDI                | Programmer              | Test Data Input                                                                                                                    |  |

| 10  | GND <sup>1</sup>   | _                       | Signal Reference                                                                                                                   |  |

#### Notes:

- 1. Both GND pins must be connected.

- 2. FlashPro4/3/3X can provide VPUMP if there is only one device on the target board.

Power-Up/-Down Behavior of Low Power Flash Devices

## Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 17-1 support power-up behavior and the functions described in this document.

Table 17-1 • Flash-Based FPGAs

| Series                             | Family*              | Description                                                              |  |

|------------------------------------|----------------------|--------------------------------------------------------------------------|--|

| IGLOO                              | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |  |

|                                    | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |  |

|                                    | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |  |

|                                    | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |  |

| ProASIC3                           | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |  |

|                                    | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |  |

| ProASIC3 nano Lowest-cost solution |                      | Lowest-cost solution with enhanced I/O capabilities                      |  |

|                                    | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |  |

|                                    | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |  |

|                                    | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |  |

|                                    | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Figure 17-3 • I/O State when VCCI Is Powered before VCC

## **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up—to—functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 17-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 17-2 on page 311 and Figure 17-3.

Table 17-2 • Power-Up Functional Activation Levels for VCC and VCCI

| Device                                                                                                | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.2 V*                          | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 17-4 on page 313 and Figure 17-5 on page 314 for more information.