Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                         |

|--------------------------------|-------------------------------------------------------------------------|

| Product Status                 | Active                                                                  |

| Number of LABs/CLBs            | -                                                                       |

| Number of Logic Elements/Cells | -                                                                       |

| Total RAM Bits                 | -                                                                       |

| Number of I/O                  | 34                                                                      |

| Number of Gates                | 10000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                         |

| Mounting Type                  | Surface Mount                                                           |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                       |

| Package / Case                 | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package        | 48-QFN (6x6)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn010-qng48 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### ProASIC3 nano FPGA Fabric User's Guide

|   | PLL Core Specifications                                                  | . 84 |

|---|--------------------------------------------------------------------------|------|

|   | Functional Description                                                   | . 85 |

|   | Software Configuration                                                   | . 96 |

|   | Detailed Usage Information                                               | 104  |

|   | Recommended Board-Level Considerations                                   | 112  |

|   | Conclusion                                                               | 113  |

|   | Related Documents                                                        | 113  |

|   | List of Changes                                                          | 113  |

|   |                                                                          |      |

| 5 | FlashROM in Microsemi's Low Power Flash Devices                          | 117  |

|   | Introduction                                                             |      |

|   | Architecture of User Nonvolatile FlashROM                                |      |

|   | FlashROM Support in Flash-Based Devices                                  |      |

|   | FlashROM Applications                                                    | 120  |

|   | FlashROM Security                                                        |      |

|   | Programming and Accessing FlashROM                                       | 122  |

|   | FlashROM Design Flow                                                     | 124  |

|   | Custom Serialization Using FlashROM                                      | 129  |

|   | Conclusion                                                               | 130  |

|   | Related Documents                                                        | 130  |

|   | List of Changes                                                          | 130  |

|   |                                                                          |      |

| 3 | SRAM and FIFO Memories in Microsemi's Low Power Flash Devices            |      |

|   | Introduction                                                             |      |

|   | Device Architecture                                                      |      |

|   | SRAM/FIFO Support in Flash-Based Devices                                 |      |

|   | SRAM and FIFO Architecture                                               |      |

|   | Memory Blocks and Macros                                                 |      |

|   | Initializing the RAM/FIFO                                                |      |

|   | Software Support                                                         |      |

|   | Conclusion                                                               |      |

|   | List of Changes                                                          | 157  |

| _ | WO OL 1                                                                  | 4    |

|   | I/O Structures in nano Devices.                                          |      |

|   | Introduction                                                             |      |

|   | Low Power Flash Device I/O Support                                       |      |

|   | nano Standard I/Os                                                       |      |

|   | I/O Architecture                                                         |      |

|   | I/O Standards                                                            |      |

|   | Wide Range I/O Support                                                   |      |

|   | I/O Features                                                             |      |

|   | Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout |      |

|   | I/O Software Support                                                     |      |

|   | User I/O Naming Convention                                               |      |

|   | I/O Bank Architecture and CCC Naming Conventions                         |      |

|   | Board-Level Considerations                                               |      |

|   | Conclusion                                                               |      |

|   | Related Documents                                                        |      |

|   | List of Changes                                                          | 183  |

FPGA Array Architecture in Low Power Flash Devices

# **FPGA Array Architecture Support**

The flash FPGAs listed in Table 1-1 support the architecture features described in this document.

Table 1-1 • Flash-Based FPGAs

| Series    | Family*              | Description                                                                                                                                                                                    |

|-----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO®    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|           | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|           | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|           | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC®3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|           | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|           | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|           | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|           | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|           | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|           | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion    | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

# IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Table 2-4 shows the current draw in Sleep mode for an A3P250 device with the following test conditions: VCCI = VMV; VCC = VJTAG = VPUMP = GND.

Table 2-4 • A3P250 Current Draw in Sleep Mode

|                           | A3P250                |                                |  |  |  |  |

|---------------------------|-----------------------|--------------------------------|--|--|--|--|

| Typical Conditions        | I <sub>CCI</sub> (μA) | I <sub>CCI</sub> (μA) per Bank |  |  |  |  |

| VCCI = 3.3 V              | 31.57                 | 7.89                           |  |  |  |  |

| VCCI = 2.5 V              | 23.96                 | 5.99                           |  |  |  |  |

| VCCI = 1.8 V              | 17.32                 | 4.33                           |  |  |  |  |

| VCCI = 1.5 V              | 14.46                 | 3.62                           |  |  |  |  |

| I <sub>CC</sub> FPGA Core | 0.0                   | 0.0                            |  |  |  |  |

| Leakage Current per I/O   | 0.1                   | 0.1                            |  |  |  |  |

| VPUMP                     | 0.0                   | 0.0                            |  |  |  |  |

Note: The data in this table were taken under typical conditions and are based on characterization. The data is not guaranteed.

Table 2-5 shows the current draw in Sleep mode for an A3PE600 device with the following test conditions: VCCI = VMV; VCC = VJTAG = VPUMP = GND.

Table 2-5 • A3PE600 Current Draw in Sleep Mode

|                           | A3PE600               |                                |  |  |  |  |

|---------------------------|-----------------------|--------------------------------|--|--|--|--|

| Typical Conditions        | I <sub>CCI</sub> (μA) | I <sub>CCI</sub> (μA) per Bank |  |  |  |  |

| VCCI = 3.3 V              | 59.85                 | 7.48                           |  |  |  |  |

| VCCI = 2.5 V              | 45.50                 | 5.69                           |  |  |  |  |

| VCCI = 1.8 V              | 32.98                 | 4.12                           |  |  |  |  |

| VCCI = 1.5 V              | 27.66                 | 3.46                           |  |  |  |  |

| VCCI = 0 V or Floating    | 0.0                   | 0.0                            |  |  |  |  |

| I <sub>CC</sub> FPGA Core | 0.0                   | 0.0                            |  |  |  |  |

| Leakage Current per I/O   | 0.1                   | 0.1                            |  |  |  |  |

| I <sub>PUMP</sub>         | 0.0                   | 0.0                            |  |  |  |  |

Note: The data in this table were taken under typical conditions and are based on characterization. The data is not quaranteed.

ProASIC3/E and ProASIC3 nano devices were designed such that before device power-up, all I/Os are in tristate mode. The I/Os will remain tristated during power-up until the last voltage supply (VCC or VCCI) is powered to its functional level. After the last supply reaches the functional level, the outputs will exit the tristate mode and drive the logic at the input of the output buffer. The behavior of user I/Os is independent of the VCC and VCCI sequence or the state of other FPGA voltage supplies (VPUMP and VJTAG). During power-down, device I/Os become tristated once the first power supply (VCC or VCCI) drops below its brownout voltage level. The I/O behavior during power-down is also independent of voltage supply sequencing.

Figure 2-5 on page 27 shows a timing diagram for the FPGA core entering the activation and deactivation trip points for a typical application when the VCC power supply ramp rate is  $100 \, \mu s$  (ramping from  $0 \, V$  to  $1.5 \, V$ ). This is, in fact, the timing diagram for the FPGA entering and exiting Sleep mode, as it is dependent on powering down or powering up VCC. Depending on the ramp rate of the power supply and board-level configurations, the user can easily calculate how long it takes for the core to become active or inactive. For more information, refer to the "Power-Up/-Down Behavior of Low Power Flash Devices" section on page 307.

### Simple Design Example

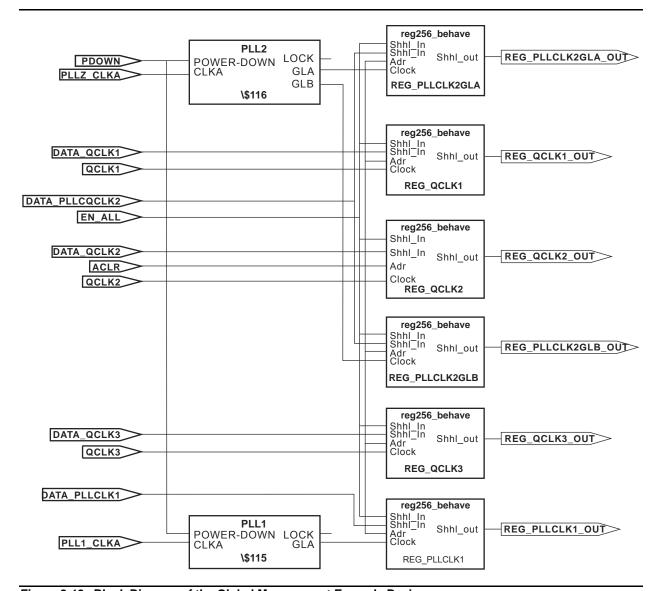

Consider a design consisting of six building blocks (shift registers) and targeted for an A3PE600-PQ208 (Figure 3-16 on page 52). The example design consists of two PLLs (PLL1 has GLA only; PLL2 has both GLA and GLB), a global reset (ACLR), an enable (EN\_ALL), and three external clock domains (QCLK1, QCLK2, and QCLK3) driving the different blocks of the design. Note that the PQ208 package only has two PLLs (which access the chip global network). Because of fanout, the global reset and enable signals need to be assigned to the chip global resources. There is only one free chip global for the remaining global (QCLK1, QCLK2, QCLK3). Place two of these signals on the quadrant global resource. The design example demonstrates manually assignment of QCLK1 and QCLK2 to the quadrant global using the PDC command.

Figure 3-19 • Block Diagram of the Global Management Example Design

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                                      | Page   |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                                                    | N/A    |

|                         | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                                                                                                                                    | N/A    |

|                         | The "Global Architecture" section and "VersaNet Global Network Distribution" section were revised for clarity (SARs 20646, 24779).                                                                                                                                                                                           | 31, 33 |

|                         | The "I/O Banks and Global I/Os" section was moved earlier in the document, renamed to "Chip and Quadrant Global I/Os", and revised for clarity. Figure 3-4 • Global Connections Details, Figure 3-6 • Global Inputs, Table 3-2 • Chip Global Pin Name, and Table 3-3 • Quadrant Global Pin Name are new (SARs 20646, 24779). | 35     |

|                         | The "Clock Aggregation Architecture" section was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                | 41     |

|                         | Figure 3-7 • Chip Global Aggregation was revised (SARs 20646, 24779).                                                                                                                                                                                                                                                        | 43     |

|                         | The "Global Macro and Placement Selections" section is new (SARs 20646, 24779).                                                                                                                                                                                                                                              | 48     |

| v1.4<br>(December 2008) | The "Global Architecture" section was updated to include 10 k devices, and to include information about VersaNet global support for IGLOO nano devices.                                                                                                                                                                      | 31     |

|                         | The Table 3-1 • Flash-Based FPGAs was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                               | 32     |

|                         | The "VersaNet Global Network Distribution" section was updated to include 10 k devices and to note an exception in global lines for nano devices.                                                                                                                                                                            | 33     |

|                         | Figure 3-2 • Simplified VersaNet Global Network (30 k gates and below) is new.                                                                                                                                                                                                                                               | 34     |

|                         | The "Spine Architecture" section was updated to clarify support for 10 k and nano devices.                                                                                                                                                                                                                                   | 41     |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                  | 41     |

|                         | The figure in the CLKBUF_LVDS/LVPECL row of Table 3-8 • Clock Macros was updated to change CLKBIBUF to CLKBUF.                                                                                                                                                                                                               | 46     |

| v1.3<br>(October 2008)  | A third bullet was added to the beginning of the "Global Architecture" section: In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.                                                                                         | 31     |

|                         | The "Global Resource Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                      | 32     |

|                         | Table 3-4 • Globals/Spines/Rows for IGLOO and ProASIC3 Devices was updated to include A3PE600/L in the device column.                                                                                                                                                                                                        | 41     |

|                         | Table note 1 was revised in Table 3-9 • I/O Standards within CLKBUF to include AFS600 and AFS1500.                                                                                                                                                                                                                           | 47     |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 3-1 • Flash-Based FPGAs: • ProASIC3L was updated to include 1.5 V.                                                                                                                                                                                       | 32     |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                               |        |

#### Notes:

- 1. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 2. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

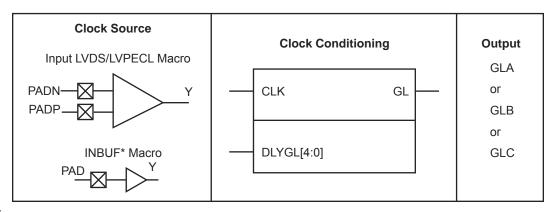

Figure 4-3 • CCC Options: Global Buffers with Programmable Delay

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay. The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the software will automatically place the dedicated global I/O in the appropriate locations. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the low power flash family. The available INBUF macros are described in the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

The CLKDLY macro can be driven directly from the FPGA core. The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate the clock input driven by the hardwired I/O connection.

The visual CLKDLY configuration in the SmartGen area of the Microsemi Libero System-on-Chip (SoC) and Designer tools allows the user to select the desired amount of delay and configures the delay elements appropriately. SmartGen also allows the user to select the input clock source. SmartGen will automatically instantiate the special macro, PLLINT, when needed.

# **CLKDLY Macro Signal Descriptions**

The CLKDLY macro supports one input and one output. Each signal is described in Table 4-2.

Table 4-2 • Input and Output Description of the CLKDLY Macro

| Signal | Name            | I/O    | Description                                                       |

|--------|-----------------|--------|-------------------------------------------------------------------|

| CLK    | Reference Clock | Input  | Reference clock input                                             |

| GL     | Global Output   | Output | Primary output clock to respective global/quadrant clock networks |

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **CLKDLY Macro Usage**

When a CLKDLY macro is used in a CCC location, the programmable delay element is used to allow the clock delays to go to the global network. In addition, the user can bypass the PLL in a CCC location integrated with a PLL, but use the programmable delay that is associated with the global network by instantiating the CLKDLY macro. The same is true when using programmable delay elements in a CCC location with no PLLs (the user needs to instantiate the CLKDLY macro). There is no difference between the programmable delay elements used for the PLL and the CLKDLY macro. The CCC will be configured to use the programmable delay elements in accordance with the macro instantiated by the user.

As an example, if the PLL is not used in a particular CCC location, the designer is free to specify up to three CLKDLY macros in the CCC, each of which can have its own input frequency and delay adjustment options. If the PLL core is used, assuming output to only one global clock network, the other two global clock networks are free to be used by either connecting directly from the global inputs or connecting from one or two CLKDLY macros for programmable delay.

The programmable delay elements are shown in the block diagram of the PLL block shown in Figure 4-6 on page 71. Note that any CCC locations with no PLL present contain only the programmable delay blocks going to the global networks (labeled "Programmable Delay Type 2"). Refer to the "Clock Delay Adjustment" section on page 86 for a description of the programmable delay types used for the PLL. Also refer to Table 4-14 on page 94 for Programmable Delay Type 1 step delay values, and Table 4-15 on page 94 for Programmable Delay Type 2 step delay values. CCC locations with a PLL present can be configured to utilize only the programmable delay blocks (Programmable Delay Type 2) going to the global networks A, B, and C.

Global network A can be configured to use only the programmable delay element (bypassing the PLL) if the PLL is not used in the design. Figure 4-6 on page 71 shows a block diagram of the PLL, where the programmable delay elements are used for the global networks (Programmable Delay Type 2).

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **PLL Macro Signal Descriptions**

The PLL macro supports two inputs and up to six outputs. Table 4-3 gives a description of each signal.

Table 4-3 • Input and Output Signals of the PLL Block

| Signal    | Name                                  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKA      | Reference Clock                       | Input  | Reference clock input for PLL core; input clock for primary output clock, GLA                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OADIVRST  | Reset Signal for the Output Divider A | Input  | For Fusion only. OADIVRST can be used when you bypass the PLL core (i.e., OAMUX = 001). The purpose of the OADIVRST signals is to reset the output of the final clock divider to synchronize it with the input to that divider when the PLL is bypassed. The signal is active on a low to high transition. The signal must be low for at least one divider input. If PLL core is used, this signal is "don't care" and the internal circuitry will generate the reset signal for the synchronization purpose. |

| OADIVHALF | Output A Division by<br>Half          | Input  | For Fusion only. Active high. Division by half feature. This feature can only be used when users bypass the PLL core (i.e., OAMUX = 001) and the RC Oscillator (RCOSC) drives the CLKA input. This can be used to divide the 100 MHz RC oscillator by a factor of 1.5, 2.5, 3.5, 4.5 14.5). Refer to Table 4-18 on page 95 for more information.                                                                                                                                                              |

| EXTFB     | External Feedback                     | Input  | Allows an external signal to be compared to a reference clock in the PLL core's phase detector.                                                                                                                                                                                                                                                                                                                                                                                                               |

| POWERDOWN | Power Down                            | Input  | Active low input that selects power-down mode and disables the PLL. With the POWERDOWN signal asserted, the PLL core sends 0 V signals on all of the outputs.                                                                                                                                                                                                                                                                                                                                                 |

| GLA       | Primary Output                        | Output | Primary output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GLB       | Secondary 1 Output                    | Output | Secondary 1 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YB        | Core 1 Output                         | Output | Core 1 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GLC       | Secondary 2 Output                    | Output | Secondary 2 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YC        | Core 2 Output                         | Output | Core 2 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LOCK      | PLL Lock Indicator                    | Output | Active high signal indicating that steady-state lock has been achieved between CLKA and the PLL feedback signal                                                                                                                                                                                                                                                                                                                                                                                               |

### Input Clock

The inputs to the input reference clock (CLKA) of the PLL can come from global input pins, regular I/O pins, or internally from the core. For Fusion families, the input reference clock can also be from the embedded RC oscillator or crystal oscillator.

# **Global Output Clocks**

GLA (Primary), GLB (Secondary 1), and GLC (Secondary 2) are the outputs of Global Multiplexer 1, Global Multiplexer 2, and Global Multiplexer 3, respectively. These signals (GLx) can be used to drive the high-speed global and quadrant networks of the low power flash devices.

A global multiplexer block consists of the input routing for selecting the input signal for the GLx clock and the output multiplexer, as well as delay elements associated with that clock.

## **Core Output Clocks**

YB and YC are known as Core Outputs and can be used to drive internal logic without using global network resources. This is especially helpful when global network resources must be conserved and utilized for other timing-critical paths.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Dynamic PLL Configuration**

To generate a dynamically reconfigurable CCC, the user should select **Dynamic CCC** in the configuration section of the SmartGen GUI (Figure 4-26). This will generate both the CCC core and the configuration shift register / control bit MUX.

### Figure 4-26 • SmartGen GUI

Even if dynamic configuration is selected in SmartGen, the user must still specify the static configuration data for the CCC (Figure 4-27). The specified static configuration is used whenever the MODE signal is set to LOW and the CCC is required to function in the static mode. The static configuration data can be used as the default behavior of the CCC where required.

Figure 4-27 • Dynamic CCC Configuration in SmartGen

# 5 – FlashROM in Microsemi's Low Power Flash Devices

### Introduction

The Fusion, IGLOO, and ProASIC3 families of low power flash-based devices have a dedicated nonvolatile FlashROM memory of 1,024 bits, which provides a unique feature in the FPGA market. The FlashROM can be read, modified, and written using the JTAG (or UJTAG) interface. It can be read but not modified from the FPGA core. Only low power flash devices contain on-chip user nonvolatile memory (NVM).

# **Architecture of User Nonvolatile FlashROM**

Low power flash devices have 1 kbit of user-accessible nonvolatile flash memory on-chip that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits (16 bytes) during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core. Figure 5-1 shows the FlashROM logical structure.

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports synchronous read. The address is latched on the rising edge of the clock, and the new output data is stable after the falling edge of the same clock cycle. For more information, refer to the timing diagrams in the DC and Switching Characteristics chapter of the appropriate datasheet. The FlashROM can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

|                            | Byte Number in Bank |    |    |    |    |    | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |   |   |

|----------------------------|---------------------|----|----|----|----|----|----------------------|---|---|---|---|---|---|---|---|---|---|

|                            |                     | 15 | 14 | 13 | 12 | 11 | 10                   | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| of                         | 7                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| SB (                       | 6                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| 3 MSB<br>EAD)              | 5                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| —                          | 4                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| m<br>SR (                  | 3                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Number 3 MS<br>ADDR (READ) | 2                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Bank Number<br>ADDR (R     | 1                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

| Ä                          | 0                   |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |   |

Figure 5-1 • FlashROM Architecture

ProASIC3 nano FPGA Fabric User's Guide

## FlashROM Generation and Instantiation in the Design

The SmartGen core generator, available in Libero SoC and Designer, is the only tool that can be used to generate the FlashROM content. SmartGen has several user-friendly features to help generate the FlashROM contents. Instead of selecting each byte and assigning values, you can create a region within a page, modify the region, and assign properties to that region. The FlashROM user interface, shown in Figure 5-10, includes the configuration grid, existing regions list, and properties field. The properties field specifies the region-specific information and defines the data used for that region. You can assign values to the following properties:

- Static Fixed Data—Enables you to fix the data so it cannot be changed during programming time.

This option is useful when you have fixed data stored in this region, which is required for the

operation of the design in the FPGA. Key storage is one example.

- 2. Static Modifiable Data—Select this option when the data in a particular region is expected to be static data (such as a version number, which remains the same for a long duration but could conceivably change in the future). This option enables you to avoid changing the value every time you enter new data.

- 3. Read from File—This provides the full flexibility of FlashROM usage to the customer. If you have a customized algorithm for generating the FlashROM data, you can specify this setting. You can then generate a text file with data for as many devices as you wish to program, and load that into the FlashPoint programming file generation software to get programming files that include all the data. SmartGen will optionally pass the location of the file where the data is stored if the file is specified in SmartGen. Each text file has only one type of data format (binary, decimal, hex, or ASCII text). The length of each data file must be shorter than or equal to the selected region length. If the data is shorter than the selected region length, the most significant bits will be padded with 0s. For multiple text files for multiple regions, the first lines are for the first device. In SmartGen, Load Sim. Value From File allows you to load the first device data in the MEM file for simulation.

- 4. Auto Increment/Decrement—This scenario is useful when you specify the contents of FlashROM for a large number of devices in a series. You can specify the step value for the serial number and a maximum value for inventory control. During programming file generation, the actual number of devices to be programmed is specified and a start value is fed to the software.

Figure 5-10 • SmartGen GUI of the FlashROM

# Conclusion

Fusion, IGLOO, and ProASIC3 devices provide users with extremely flexible SRAM blocks for most design needs, with the ability to choose between an easy-to-use dual-port memory or a wide-word twoport memory. Used with the built-in FIFO controllers, these memory blocks also serve as highly efficient FIFOs that do not consume user gates when implemented. The SmartGen core generator provides a fast and easy way to configure these memory elements for use in designs.

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                                                                                                                                                                 | Page |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|--|

| August 2012             | The note connected with Figure 6-3 • Supported Basic RAM Macros, regarding RAM4K9, was revised to explain that it applies only to part numbers of certain revisions and earlier (SAR 29574).                                                                                                            |      |  |  |  |  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                                                                                                                                                               |      |  |  |  |  |

| v1.5<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 6-1 • Flash-Based FPGAs.                                                                                                                                                                                                                       | 134  |  |  |  |  |

|                         | IGLOO nano and ProASIC3 nano devices were added to Figure 6-8 • Interfacing TAP Ports and SRAM Blocks.                                                                                                                                                                                                  | 148  |  |  |  |  |

| v1.4<br>(October 2008)  | The "SRAM/FIFO Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                       | 134  |  |  |  |  |

|                         | The "SRAM and FIFO Architecture" section was modified to remove "IGLOO and ProASIC3E" from the description of what the memory block includes, as this statement applies to all memory blocks.                                                                                                           | 135  |  |  |  |  |

|                         | Wording in the "Clocking" section was revised to change "IGLOO and ProASIC3 devices support inversion" to "Low power flash devices support inversion." The reference to IGLOO and ProASIC3 development tools in the last paragraph of the section was changed to refer to development tools in general. | 141  |  |  |  |  |

|                         | The "ESTOP and FSTOP Usage" section was updated to refer to FIFO counters in devices in general rather than only IGLOO and ProASIC3E devices.                                                                                                                                                           | 144  |  |  |  |  |

| v1.3<br>(August 2008)   | The note was removed from Figure 6-7 • RAM Block with Embedded FIFO Controller and placed in the WCLK and RCLK description.                                                                                                                                                                             | 142  |  |  |  |  |

|                         | The "WCLK and RCLK" description was revised.                                                                                                                                                                                                                                                            | 143  |  |  |  |  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 6-1 • Flash-Based FPGAs:                                                                                                                                                                                                            | 134  |  |  |  |  |

|                         | ProASIC3L was updated to include 1.5 V.                                                                                                                                                                                                                                                                 |      |  |  |  |  |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                          |      |  |  |  |  |

| v1.1<br>(March 2008)    | The "Introduction" section was updated to include the IGLOO PLUS family.                                                                                                                                                                                                                                | 131  |  |  |  |  |

|                         | The "Device Architecture" section was updated to state that 15 k gate devices do not support SRAM and FIFO.                                                                                                                                                                                             | 131  |  |  |  |  |

|                         | The first note in Figure 6-1 • IGLOO and ProASIC3 Device Architecture Overview was updated to include mention of 15 k gate devices, and IGLOO PLUS was added to the second note.                                                                                                                        | 133  |  |  |  |  |

### Table 7-8 • Hot-Swap Level 1

| Description                            | Cold-swap                                                                                                                                                                                  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                | No                                                                                                                                                                                         |

| Bus State                              | -                                                                                                                                                                                          |

| Card Ground Connection                 | -                                                                                                                                                                                          |

| Device Circuitry Connected to Bus Pins | -                                                                                                                                                                                          |

| Example Application                    | System and card with Microsemi FPGA chip are powered down, and the card is plugged into the system. Then the power supplies are turned on for the system but not for the FPGA on the card. |

| Compliance of nano Devices             | Compliant                                                                                                                                                                                  |

### Table 7-9 • Hot-Swap Level 2

| Description                            | Hot-swap while reset                                                                                                                                          |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Applied to Device                | Yes                                                                                                                                                           |

| Bus State                              | Held in reset state                                                                                                                                           |

| Card Ground Connection                 | Reset must be maintained for 1 ms before, during, and after insertion/removal.                                                                                |

| Device Circuitry Connected to Bus Pins | -                                                                                                                                                             |

| Example Application                    | In the PCI hot-plug specification, reset control circuitry isolates the card busses until the card supplies are at their nominal operating levels and stable. |

| Compliance of nano Devices             | Compliant                                                                                                                                                     |

I/O Software Control in Low Power Flash Devices

# Flash FPGAs I/O Support

The flash FPGAs listed in Table 8-1 support I/Os and the functions described in this document.

Table 8-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |  |  |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IGLOO    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |  |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

# IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 8-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

I/O Software Control in Low Power Flash Devices

### **Output Buffers**

There are two variations: Regular and Special.

If the **Regular** variation is selected, only the Width (1 to 128) needs to be entered. The default value for Width is 1.

The **Special** variation has Width, Technology, Output Drive, and Slew Rate options.

#### **Bidirectional Buffers**

There are two variations: Regular and Special.

The **Regular** variation has Enable Polarity (Active High, Active Low) in addition to the Width option.

The **Special** variation has Width, Technology, Output Drive, Slew Rate, and Resistor Pull-Up/-Down options.

### **Tristate Buffers**

Same as Bidirectional Buffers.

#### DDR

There are eight variations: DDR with Regular Input Buffers, Special Input Buffers, Regular Output Buffers, Special Output Buffers, Regular Tristate Buffers, Special Tristate Buffers, Regular Bidirectional Buffers, and Special Bidirectional Buffers.

These variations resemble the options of the previous I/O macro. For example, the Special Input Buffers variation has Width, Technology, Voltage Level, and Resistor Pull-Up/-Down options. DDR is not available on IGLOO PLUS devices.

- 4. Once the desired configuration is selected, click the **Generate** button. The Generate Core window opens (Figure 8-4).

- 5. Enter a name for the macro. Click **OK**. The core will be generated and saved to the appropriate location within the project files (Figure 8-5 on page 191).

### Figure 8-4 • Generate Core Window

6. Instantiate the I/O macro in the top-level code.

The user must instantiate the DDR\_REG or DDR\_OUT macro in the design. Use SmartGen to generate both these macros and then instantiate them in your top level. To combine the DDR macros with the I/O, the following rules must be met:

### **Device Programmers**

### Single Device Programmer

Single device programmers are used to program a device before it is mounted on the system board.

The advantage of using device programmers is that no programming hardware is required on the system board. Therefore, no additional components or board space are required.

Adapter modules are purchased with single device programmers to support the FPGA packages used. The FPGA is placed in the adapter module and the programming software is run from a PC. Microsemi supplies the programming software for all of the Microsemi programmers. The software allows for the selection of the correct die/package and programming files. It will then program and verify the device.

Single-site programmers

A single-site programmer programs one device at a time. Microsemi offers Silicon Sculptor 3, built by BP Microsystems, as a single-site programmer. Silicon Sculptor 3 and associated software are available only from Microsemi.

- Advantages: Lower cost than multi-site programmers. No additional overhead for programming on the system board. Allows local control of programming and data files for maximum security. Allows on-demand programming on-site.

- Limitations: Only programs one device at a time.

- Multi-site programmers

Often referred to as batch or gang programmers, multi-site programmers can program multiple devices at the same time using the same programming file. This is often used for large volume programming and by programming houses. The sites often have independent processors and memory enabling the sites to operate concurrently, meaning each site may start programming the same file independently. This enables the operator to change one device while the other sites continue programming, which increases throughput. Multiple adapter modules for the same package are required when using a multi-site programmer. Silicon Sculptor I, II, and 3 programmers can be cascaded to program multiple devices in a chain. Multi-site programmers, such as the BP2610 and BP2710, can also be purchased from BP Microsystems. When using BP Microsystems multi-site programmers, users must use programming adapter modules available only from Microsemi. Visit the Microsemi SoC Products Group website to view the part numbers of the desired adapter module:

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx.

Also when using BP Microsystems programmers, customers must use Microsemi programming software to ensure the best programming result will occur.

- Advantages: Provides the capability of programming multiple devices at the same time. No additional overhead for programming on the system board. Allows local control of programming and data files for maximum security.

- Limitations: More expensive than a single-site programmer

- · Automated production (robotic) programmers

Automated production programmers are based on multi-site programmers. They consist of a large input tray holding multiple parts and a robotic arm to select and place parts into appropriate programming sockets automatically. When the programming of the parts is complete, the parts are removed and placed in a finished tray. The automated programmers are often used in volume programming houses to program parts for which the programming time is small. BP Microsystems part number BP4710, BP4610, BP3710 MK2, and BP3610 are available for this purpose. Auto programmers cannot be used to program RTAX-S devices.

Where an auto-programmer is used, the appropriate open-top adapter module from BP Microsystems must be used.

## **Programming Solutions**

Details for the available programmers can be found in the programmer user's guides listed in the "Related Documents" section on page 231.

All the programmers except FlashPro4, FlashPro3, FlashPro Lite, and FlashPro require adapter modules, which are designed to support device packages. All modules are listed on the Microsemi SoC Products Group website at

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx. They are not listed in this document, since this list is updated frequently with new package options and any upgrades required to improve programming yield or support new families.

Table 10-3 • Programming Solutions

| Programmer                 | Vendor             | ISP              | Single<br>Device | Multi-Device                | Availability                                     |

|----------------------------|--------------------|------------------|------------------|-----------------------------|--------------------------------------------------|

| FlashPro4                  | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro3                  | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro Lite <sup>2</sup> | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Available                                        |

| FlashPro                   | Microsemi          | Only             | Yes              | Yes <sup>1</sup>            | Discontinued                                     |

| Silicon Sculptor 3         | Microsemi          | Yes <sup>3</sup> | Yes              | Cascade option (up to two)  | Available                                        |

| Silicon Sculptor II        | Microsemi          | Yes <sup>3</sup> | Yes              | Cascade option (up to two)  | Available                                        |

| Silicon Sculptor           | Microsemi          | Yes              | Yes              | Cascade option (up to four) | Discontinued                                     |

| Sculptor 6X                | Microsemi          | No               | Yes              | Yes                         | Discontinued                                     |

| BP MicroProgrammers        | BP<br>Microsystems | No               | Yes              | Yes                         | Contact BP<br>Microsystems at<br>www.bpmicro.com |

### Notes:

- 1. Multiple devices can be connected in the same JTAG chain for programming.

- 2. If FlashPro Lite is used for programming, the programmer derives all of its power from the target pc board's VDD supply. The FlashPro Lite's VPP and VPN power supplies use the target pc board's VDD as a power source. The target pc board must supply power to both the VDDP and VDD power pins of the ProASICPLUS device in addition to supplying VDD to the FlashPro Lite. The target pc board needs to provide at least 500 mA of current to the FlashPro Lite VDD connection for programming.

- 3. Silicon Sculptor II and Silicon Sculptor 3 can only provide ISP for ProASIC and ProASIC families, not for Fusion, IGLOO, or ProASIC3 devices.

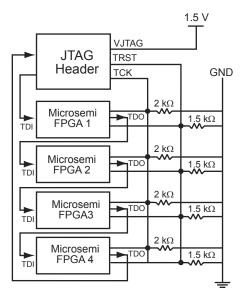

Note: TCK is correctly wired with an equivalent tie-off resistance of  $500\,\Omega$ , which satisfies the table for VJTAG of 1.5 V. The resistor values for TRST are not appropriate in this case, as the tie-off resistance of  $375\,\Omega$  is below the recommended minimum for VJTAG = 1.5 V, but would be appropriate for a VJTAG setting of 2.5 V or 3.3 V.

Figure 15-3 • Parallel Resistance on JTAG Chain of Devices

# **Advanced Boundary Scan Register Settings**

You will not be able to control the order in which I/Os are released from boundary scan control. Testing has produced cases where, depending on I/O placement and FPGA routing, a 5 ns glitch has been seen on exiting programming mode. The following setting is recommended to prevent such I/O glitches:

- 1. In the FlashPro software, configure the advanced BSR settings for **Specify I/O Settings During Programming**.

- 2. Set the input BSR cell to Low for the input I/O.

Power-Up/-Down Behavior of Low Power Flash Devices

# Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 17-1 support power-up behavior and the functions described in this document.

Table 17-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.