Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 49                                                                        |

| Number of Gates                | 30000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 68-VFQFN Exposed Pad                                                      |

| Supplier Device Package        | 68-QFN (8x8)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-z1qng68 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

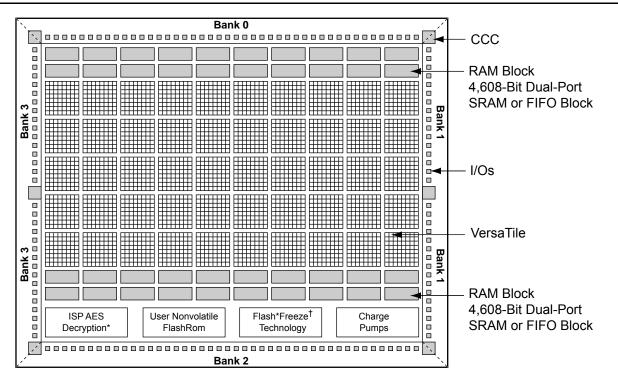

Figure 1-5 • IGLOO, IGLOO nano, ProASIC3 nano, and ProASIC3/L Device Architecture Overview with Four I/O Banks (AGL600 device is shown)

Note: \* AGLP030 does not contain a PLL or support AES security.

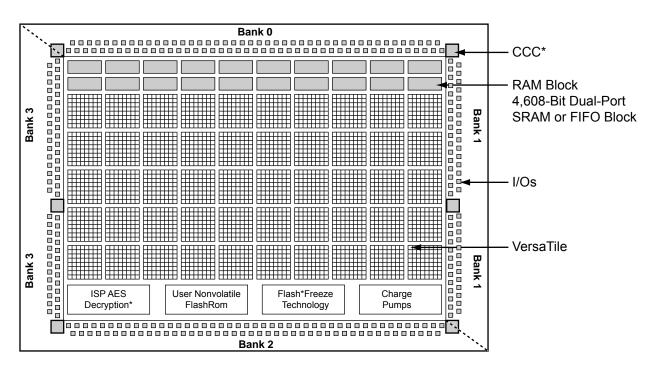

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

Global Resources in Low Power Flash Devices

### Step 1

Run Synthesis with default options. The Synplicity log shows the following device utilization:

#### Cell usage:

|          | cell count | area | count*area |

|----------|------------|------|------------|

| DFN1E1C1 | 1536       | 2.0  | 3072.0     |

| BUFF     | 278        | 1.0  | 278.0      |

| INBUF    | 10         | 0.0  | 0.0        |

| VCC      | 9          | 0.0  | 0.0        |

| GND      | 9          | 0.0  | 0.0        |

| OUTBUF   | 6          | 0.0  | 0.0        |

| CLKBUF   | 3          | 0.0  | 0.0        |

| PLL      | 2          | 0.0  | 0.0        |

| TOTAL    | 1853       |      | 3350.0     |

## Step 2

Run Compile with the **Promote regular nets whose fanout is greater than** option selected in Designer; you will see the following in the Compile report:

| Device utilization report:              |       |      |        |       |           |  |  |  |  |

|-----------------------------------------|-------|------|--------|-------|-----------|--|--|--|--|

| ======================================= |       |      |        |       |           |  |  |  |  |

| CORE                                    | Used: | 1536 | Total: | 13824 | (11.11%)  |  |  |  |  |

| IO (W/ clocks)                          | Used: | 19   | Total: | 147   | (12.93%)  |  |  |  |  |

| Differential IO                         | Used: | 0    | Total: | 65    | (0.00%)   |  |  |  |  |

| GLOBAL                                  | Used: | 8    | Total: | 18    | (44.44%)  |  |  |  |  |

| PLL                                     | Used: | 2    | Total: | 2     | (100.00%) |  |  |  |  |

| RAM/FIFO                                | Used: | 0    | Total: | 24    | (0.00%)   |  |  |  |  |

| FlashROM                                | Used: | 0    | Total: | 1     | (0.00%)   |  |  |  |  |

|                                         |       |      |        |       |           |  |  |  |  |

The following nets have been assigned to a global resource:

| Fanout |                        | Name    | abbigned to a groba |

|--------|------------------------|---------|---------------------|

| 1536   | INT_NET                | Net :   | EN_ALL_c            |

|        |                        | Driver: | EN_ALL_pad_CLKINT   |

|        |                        | Source: | AUTO PROMOTED       |

| 1536   | ${\tt SET/RESET\_NET}$ | Net :   | ACLR_c              |

|        |                        | Driver: | ACLR_pad_CLKINT     |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK1_c             |

|        |                        | Driver: | QCLK1_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK2_c             |

|        |                        | Driver: | QCLK2_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | QCLK3_c             |

|        |                        | Driver: | QCLK3_pad_CLKINT    |

|        |                        | Source: | AUTO PROMOTED       |

| 256    | CLK_NET                | Net :   | \$1N14              |

|        |                        | Driver: | \$1I5/Core          |

|        |                        | Source: | ESSENTIAL           |

| 256    | CLK_NET                | Net :   | \$1N12              |

|        |                        | Driver: | \$1I6/Core          |

|        |                        | Source: | ESSENTIAL           |

| 256    | CLK_NET                | Net :   | \$1N10              |

|        |                        | Driver: | \$1I6/Core          |

|        |                        | Source: | ESSENTIAL           |

Designer will promote five more signals to global due to high fanout. There are eight signals assigned to global networks.

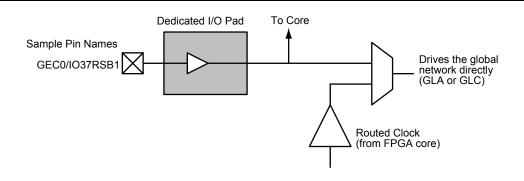

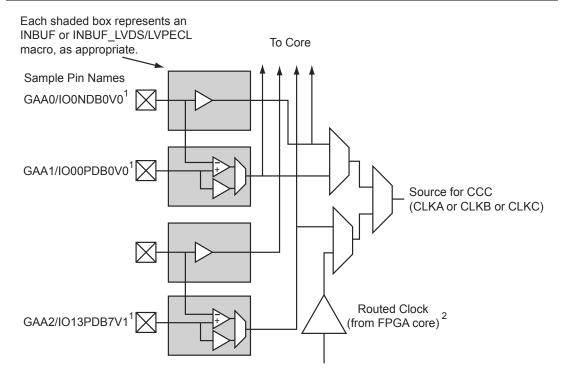

Figure 4-7 • Clock Input Sources (30 k gates devices and below)

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

#### Notes:

- Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of a PLL, CLKDLY, or CLKINT macro.

- b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS/B-LVDS/M-LVDS/DDR) in a relevant global pin location.

- 3. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT (60 k gates devices and above)

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## **PLL Core Specifications**

PLL core specifications can be found in the DC and Switching Characteristics chapter of the appropriate family datasheet.

## **Loop Bandwidth**

Common design practice for systems with a low-noise input clock is to have PLLs with small loop bandwidths to reduce the effects of noise sources at the output. Table 4-6 shows the PLL loop bandwidth, providing a measure of the PLL's ability to track the input clock and jitter.

Table 4-6 • -3 dB Frequency of the PLL

|                    | Minimum                                 | Typical                                | Maximum                                |

|--------------------|-----------------------------------------|----------------------------------------|----------------------------------------|

|                    | (T <sub>a</sub> = +125°C, VCCA = 1.4 V) | (T <sub>a</sub> = +25°C, VCCA = 1.5 V) | (T <sub>a</sub> = -55°C, VCCA = 1.6 V) |

| -3 dB<br>Frequency | 15 kHz                                  | 25 kHz                                 | 45 kHz                                 |

## **PLL Core Operating Principles**

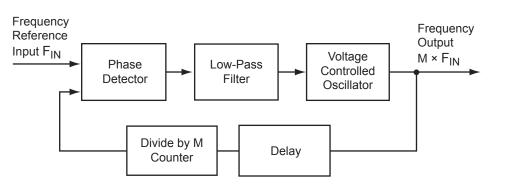

This section briefly describes the basic principles of PLL operation. The PLL core is composed of a phase detector (PD), a low-pass filter (LPF), and a four-phase voltage-controlled oscillator (VCO). Figure 4-19 illustrates a basic single-phase PLL core with a divider and delay in the feedback path.

Figure 4-19 • Simplified PLL Core with Feedback Divider and Delay

The PLL is an electronic servo loop that phase-aligns the PD feedback signal with the reference input. To achieve this, the PLL dynamically adjusts the VCO output signal according to the average phase difference between the input and feedback signals.

The first element is the PD, which produces a voltage proportional to the phase difference between its inputs. A simple example of a digital phase detector is an Exclusive-OR gate. The second element, the LPF, extracts the average voltage from the phase detector and applies it to the VCO. This applied voltage alters the resonant frequency of the VCO, thus adjusting its output frequency.

Consider Figure 4-19 with the feedback path bypassing the divider and delay elements. If the LPF steadily applies a voltage to the VCO such that the output frequency is identical to the input frequency, this steady-state condition is known as lock. Note that the input and output phases are also identical. The PLL core sets a LOCK output signal HIGH to indicate this condition.

Should the input frequency increase slightly, the PD detects the frequency/phase difference between its reference and feedback input signals. Since the PD output is proportional to the phase difference, the change causes the output from the LPF to increase. This voltage change increases the resonant frequency of the VCO and increases the feedback frequency as a result. The PLL dynamically adjusts in this manner until the PD senses two phase-identical signals and steady-state lock is achieved. The opposite (decreasing PD output signal) occurs when the input frequency decreases.

Now suppose the feedback divider is inserted in the feedback path. As the division factor M (shown in Figure 4-20 on page 85) is increased, the average phase difference increases. The average phase

## **Phase Adjustment**

The four phases available (0, 90, 180, 270) are phases with respect to VCO (PLL output). The VCO is divided to achieve the user's CCC required output frequency (GLA, YB/GLB, YC/GLC). The division happens after the selection of the VCO phase. The effective phase shift is actually the VCO phase shift divided by the output divider. This is why the visual CCC shows both the actual achievable phase and more importantly the actual delay that is equivalent to the phase shift that can be achieved.

## **Dynamic PLL Configuration**

The CCCs can be configured both statically and dynamically.

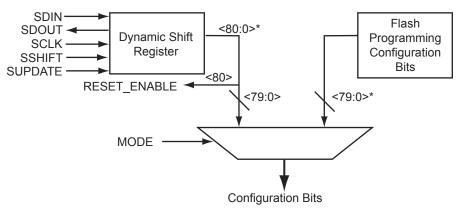

In addition to the ports available in the Static CCC, the Dynamic CCC has the dynamic shift register signals that enable dynamic reconfiguration of the CCC. With the Dynamic CCC, the ports CLKB and CLKC are also exposed. All three clocks (CLKA, CLKB, and CLKC) can be configured independently. The CCC block is fully configurable. The following two sources can act as the CCC configuration bits.

### Flash Configuration Bits

The flash configuration bits are the configuration bits associated with programmed flash switches. These bits are used when the CCC is in static configuration mode. Once the device is programmed, these bits cannot be modified. They provide the default operating state of the CCC.

### **Dynamic Shift Register Outputs**

This source does not require core reprogramming and allows core-driven dynamic CCC reconfiguration. When the dynamic register drives the configuration bits, the user-defined core circuit takes full control over SDIN, SDOUT, SCLK, SSHIFT, and SUPDATE. The configuration bits can consequently be dynamically changed through shift and update operations in the serial register interface. Access to the logic core is accomplished via the dynamic bits in the specific tiles assigned to the PLLs.

Figure 4-21 illustrates a simplified block diagram of the MUX architecture in the CCCs.

Note: \*For Fusion, bit <88:81> is also needed.

Figure 4-21 • The CCC Configuration MUX Architecture

The selection between the flash configuration bits and the bits from the configuration register is made using the MODE signal shown in Figure 4-21. If the MODE signal is logic HIGH, the dynamic shift register configuration bits are selected. There are 81 control bits to configure the different functions of the CCC.

Table 4-9 to Table 4-15 on page 94 provide descriptions of the configuration data for the configuration bits.

### Table 4-9 • Input Clock Divider, FINDIV[6:0] (/n)

| FINDIV<6:0> State | Divisor | New Frequency Factor |

|-------------------|---------|----------------------|

| 0                 | 1       | 1.00000              |

| 1                 | 2       | 0.50000              |

| :                 | :       | :                    |

| 127               | 128     | 0.0078125            |

### Table 4-10 • Feedback Clock Divider, FBDIV[6:0] (/m)

| FBDIV<6:0> State | Divisor | New Frequency Factor |

|------------------|---------|----------------------|

| 0                | 1       | 1                    |

| 1                | 2       | 2                    |

| :                | :       | :                    |

| 127              | 128     | 128                  |

### Table 4-11 • Output Frequency Dividers

A Output Divider, OADIV <4:0> (/u);

B Output Divider, OBDIV <4:0> (/v);

C Output Divider, OCDIV <4:0> (/w)

| OADIV<4:0>; OBDIV<4:0>;<br>CDIV<4:0> State | Divisor | New Frequency Factor |

|--------------------------------------------|---------|----------------------|

| 0                                          | 1       | 1.00000              |

| 1                                          | 2       | 0.50000              |

| :                                          | i i     | i i                  |

| 31                                         | 32      | 0.03125              |

### Table 4-12 • MUXA, MUXB, MUXC

| OAMUX<2:0>; OBMUX<2:0>; OCMUX<2:0> State | MUX Input Selected                                                                                             |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 0                                        | None. Six-input MUX and PLL are bypassed. Clock passes only through global MUX and goes directly into HC ribs. |

| 1                                        | Not available                                                                                                  |

| 2                                        | PLL feedback delay line output                                                                                 |

| 3                                        | Not used                                                                                                       |

| 4                                        | PLL VCO 0° phase shift                                                                                         |

| 5                                        | PLL VCO 270° phase shift                                                                                       |

| 6                                        | PLL VCO 180° phase shift                                                                                       |

| 7                                        | PLL VCO 90° phase shift                                                                                        |

```

DYNCCC Core(.CLKA(CLKA), .EXTFB(GND), .POWERDOWN(POWERDOWN), .GLA(GLA), .LOCK(LOCK),

.CLKB(CLKB), .GLB(GLB), .YB(), .CLKC(CLKC), .GLC(GLC), .YC(), .SDIN(SDIN),

.SCLK(SCLK), .SSHIFT(SSHIFT), .SUPDATE(SUPDATE), .MODE(MODE), .SDOUT(SDOUT),

.OADIV0(GND), .OADIV1(GND), .OADIV2(VCC), .OADIV3(GND), .OADIV4(GND), .OAMUX0(GND),

.OAMUX1(GND), .OAMUX2(VCC), .DLYGLA0(GND), .DLYGLA1(GND), .DLYGLA2(GND),

.DLYGLA3(GND), .DLYGLA4(GND), .OBDIV0(GND), .OBDIV1(GND), .OBDIV2(GND),

.OBDIV3(GND), .OBDIV4(GND), .OBMUX0(GND), .OBMUX1(GND), .OBMUX2(GND), .DLYYB0(GND),

.DLYYB1(GND), .DLYYB2(GND), .DLYYB3(GND), .DLYYB4(GND), .DLYGLB0(GND),

.DLYGLB1(GND), .DLYGLB2(GND), .DLYGLB3(GND), .DLYGLB4(GND), .OCDIV0(GND),

. \texttt{OCDIV1}(\texttt{GND}) \,, \, \, . \texttt{OCDIV2}(\texttt{GND}) \,, \, \, . \texttt{OCDIV3}(\texttt{GND}) \,, \, \, . \texttt{OCDIV4}(\texttt{GND}) \,, \, \, . \texttt{OCMUX0}(\texttt{GND}) \,, \, \, . \texttt{OCMUX1}(\texttt{GND}) \,, \, \, . \\

. \texttt{OCMUX2}(\texttt{GND}) \,, \; . \texttt{DLYYC0}(\texttt{GND}) \,, \; . \texttt{DLYYC1}(\texttt{GND}) \,, \; . \texttt{DLYYC2}(\texttt{GND}) \,, \; . \texttt{DLYYC3}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND}) \,, \; . \texttt{DLYYC4}(\texttt{GND})

.DLYGLC0(GND), .DLYGLC1(GND), .DLYGLC2(GND), .DLYGLC3(GND), .DLYGLC4(GND),

.FINDIV0(VCC), .FINDIV1(GND), .FINDIV2(VCC), .FINDIV3(GND), .FINDIV4(GND),

.FINDIV5(GND), .FINDIV6(GND), .FBDIV0(GND), .FBDIV1(GND), .FBDIV2(GND),

.FBDIV3(GND), .FBDIV4(GND), .FBDIV5(VCC), .FBDIV6(GND), .FBDLY1(GND), .FBDLY1(GND),

.FBDLY2(GND), .FBDLY3(GND), .FBDLY4(GND), .FBSEL0(VCC), .FBSEL1(GND),

.XDLYSEL(GND), .VCOSEL0(GND), .VCOSEL1(GND), .VCOSEL2(VCC));

defparam Core.VCOFREQUENCY = 165.000;

```

endmodule

## **Delayed Clock Configuration**

The CLKDLY macro can be generated with the desired delay and input clock source (Hardwired I/O, External I/O, or Core Logic), as in Figure 4-28.

#### Figure 4-28 • Delayed Clock Configuration Dialog Box

After setting all the required parameters, users can generate one or more PLL configurations with HDL or EDIF descriptions by clicking the **Generate** button. SmartGen gives the option of saving session results and messages in a log file:

```

Macro Parameters

: delay_macro

Name

Family

: ProASIC3

: Verilog

Output Format

: Delayed Clock

Type

Delay Index

CLKA Source

: Hardwired I/O

Total Clock Delay = 0.935 ns.

The resultant CLKDLY macro Verilog netlist is as follows:

module delay_macro(GL,CLK);

output GL;

input CLK;

```

#### Figure 4-31 • Static Timing Analysis Using SmartTime

#### **Place-and-Route Stage Considerations**

Several considerations must be noted to properly place the CCC macros for layout.

For CCCs with clock inputs configured with the Hardwired I/O-Driven option:

- PLL macros must have the clock input pad coming from one of the GmA\* locations.

- CLKDLY macros must have the clock input pad coming from one of the Global I/Os.

If a PLL with a Hardwired I/O input is used at a CCC location and a Hardwired I/O–Driven CLKDLY macro is used at the same CCC location, the clock input of the CLKDLY macro must be chosen from one of the GmB\* or GmC\* pin locations. If the PLL is not used or is an External I/O–Driven or Core Logic–Driven PLL, the clock input of the CLKDLY macro can be sourced from the GmA\*, GmB\*, or GmC\* pin locations.

For CCCs with clock inputs configured with the External I/O–Driven option, the clock input pad can be assigned to any regular I/O location (IO\*\*\*\*\*\*\*\*\*\*\*\*\* pins). Note that since global I/O pins can also be used as regular I/Os, regardless of CCC function (CLKDLY or PLL), clock inputs can also be placed in any of these I/O locations.

By default, the Designer layout engine will place global nets in the design at one of the six chip globals. When the number of globals in the design is greater than six, the Designer layout engine will automatically assign additional globals to the quadrant global networks of the low power flash devices. If the user wishes to decide which global signals should be assigned to chip globals (six available) and which to the quadrant globals (three per quadrant for a total of 12 available), the assignment can be achieved with PinEditor, ChipPlanner, or by importing a placement constraint file. Layout will fail if the

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

global assignments are not allocated properly. See the "Physical Constraints for Quadrant Clocks" section for information on assigning global signals to the quadrant clock networks.

Promoted global signals will be instantiated with CLKINT macros to drive these signals onto the global network. This is automatically done by Designer when the Auto-Promotion option is selected. If the user wishes to assign the signals to the quadrant globals instead of the default chip globals, this can done by using ChipPlanner, by declaring a physical design constraint (PDC), or by importing a PDC file.

### Physical Constraints for Quadrant Clocks

If it is necessary to promote global clocks (CLKBUF, CLKINT, PLL, CLKDLY) to quadrant clocks, the user can define PDCs to execute the promotion. PDCs can be created using PDC commands (pre-compile) or the MultiView Navigator (MVN) interface (post-compile). The advantage of using the PDC flow over the MVN flow is that the Compile stage is able to automatically promote any regular net to a global net before assigning it to a quadrant. There are three options to place a quadrant clock using PDC commands:

- Place a clock core (not hardwired to an I/O) into a quadrant clock location.

- Place a clock core (hardwired to an I/O) into an I/O location (set\_io) or an I/O module location (set\_location) that drives a quadrant clock location.

- Assign a net driven by a regular net or a clock net to a quadrant clock using the following command:

```

assign_local_clock -net <net name> -type quadrant <quadrant clock region> where

```

<net name> is the name of the net assigned to the local user clock region.

<quadrant clock region> defines which quadrant the net should be assigned to. Quadrant

clock regions are defined as UL (upper left), UR (upper right), LL (lower left), and LR (lower right).

Note: If the net is a regular net, the software inserts a CLKINT buffer on the net.

#### For example:

```

assign_local_clock -net localReset -type quadrant UR

```

Keep in mind the following when placing quadrant clocks using MultiView Navigator:

#### Hardwired I/O-Driven CCCs

Find the associated clock input port under the Ports tab, and place the input port at one of the Gmn\* locations using PinEditor or I/O Attribute Editor, as shown in Figure 4-32.

Figure 4-32 • Port Assignment for a CCC with Hardwired I/O Clock Input

# 6 - SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## Introduction

As design complexity grows, greater demands are placed upon an FPGA's embedded memory. Fusion, IGLOO, and ProASIC3 devices provide the flexibility of true dual-port and two-port SRAM blocks. The embedded memory, along with built-in, dedicated FIFO control logic, can be used to create cascading RAM blocks and FIFOs without using additional logic gates.

IGLOO, IGLOO PLUS, and ProASIC3L FPGAs contain an additional feature that allows the device to be put in a low power mode called Flash\*Freeze. In this mode, the core draws minimal power (on the order of 2 to 127  $\mu$ W) and still retains values on the embedded SRAM/FIFO and registers. Flash\*Freeze technology allows the user to switch to Active mode on demand, thus simplifying power management and the use of SRAM/FIFOs.

## **Device Architecture**

The low power flash devices feature up to 504 kbits of RAM in 4,608-bit blocks (Figure 6-1 on page 132 and Figure 6-2 on page 133). The total embedded SRAM for each device can be found in the datasheets. These memory blocks are arranged along the top and bottom of the device to allow better access from the core and I/O (in some devices, they are only available on the north side of the device). Every RAM block has a flexible, hardwired, embedded FIFO controller, enabling the user to implement efficient FIFOs without sacrificing user gates.

In the IGLOO and ProASIC3 families of devices, the following memories are supported:

- 30 k gate devices and smaller do not support SRAM and FIFO.

- 60 k and 125 k gate devices support memories on the north side of the device only.

- 250 k devices and larger support memories on the north and south sides of the device.

In Fusion devices, the following memories are supported:

- AFS090 and AFS250 support memories on the north side of the device only.

- · AFS600 and AFS1500 support memories on the north and south sides of the device.

Table 6-10 • RAM and FIFO Memory Block Consumption

|       |    |               |                                 |                                |                                |                                                | Depth                                           |                                                 |                                                    |                                                    |                                                   |                                                    |

|-------|----|---------------|---------------------------------|--------------------------------|--------------------------------|------------------------------------------------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------|----------------------------------------------------|---------------------------------------------------|----------------------------------------------------|

|       | Ī  |               | 25                              | 56                             | 512                            | 1,024                                          | 2,048                                           | 4,096                                           | 8,192                                              | 16,384                                             | 32,768                                            | 65,536                                             |

|       | Ī  |               | Two-Port                        | Dual-Port                      | Dual-Port                      | Dual-Port                                      | Dual-Port                                       | Dual-Port                                       | Dual-Port                                          | Dual-Port                                          | Dual-Port                                         | Dual-Port                                          |

|       | 1  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 1                                               | 2                                                  | 4                                                  | 8                                                 | 16 × 1                                             |

|       | Ī  | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2,048 × 2                                       | 4,096 × 1                                       | 2 × (4,096 × 1)<br>Cascade Deep                    | 4 × (4,096 × 1)<br>Cascade Deep                    | 8 × (4,096 × 1)<br>Cascade Deep                   | 16 × (4,096 × 1)<br>Cascade Deep                   |

|       | 2  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 1                                               | 2                                               | 4                                                  | 8                                                  | 16                                                | 32                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024×4                                        | 2,048 × 2                                       | 2 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 2 Wide   | 8 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 2 Wide   | 16 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 2 Wide | 32 × (4,096 × 1)<br>Cascaded 16<br>Deep and 2 Wide |

|       | 4  | Number Block  | 1                               | 1                              | 1                              | 1                                              | 2                                               | 4                                               | 8                                                  | 16                                                 | 32                                                | 64                                                 |

|       |    | Configuration | Any                             | Any                            | Any                            | 1,024 × 4                                      | 2 × (2,048 × 2)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded Wide                | 4 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 4 Wide   | 16 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 4 Wide  | 32 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 4 Wide | 64 × (4,096 × 1)<br>Cascaded 16<br>Deep and 4 Wide |

|       | 8  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 | 64                                                |                                                    |

|       |    | Configuration | Any                             | Any                            | Any                            | 2 × (1,024 × 4)<br>Cascaded Wide               | 4 × (2,048 × 2)<br>Cascaded Wide                | 8 × (4,096 × 1)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 8 Wide  | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 8 Wide  | 64 × (4,096 × 1)<br>Cascaded 8 Deep<br>and 8 Wide |                                                    |

|       | 9  | Number Block  | 1                               | 1                              | 1                              | 2                                              | 4                                               | 8                                               | 16                                                 | 32                                                 |                                                   |                                                    |

|       | Ī  | Configuration | Any                             | Any                            | Any                            | 2 × (512 × 9)<br>Cascaded Deep                 | 4 × (512 × 9)<br>Cascaded Deep                  | 8 × (512 × 9)<br>Cascaded Deep                  | 16 × (512 × 9)<br>Cascaded Deep                    | 32 × (512 × 9)<br>Cascaded Deep                    |                                                   |                                                    |

|       | 16 | Number Block  | 1                               | 1                              | 1                              | 4                                              | 8                                               | 16                                              | 32                                                 | 64                                                 |                                                   |                                                    |

| Width |    | Configuration | 256 × 18                        | 256 × 18                       | 256 × 18                       | 4 × (1,024 × 4)<br>Cascaded Wide               | 8 × (2,048 × 2)<br>Cascaded Wide                | 16 × (4,096 × 1)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 16 Wide | 32 × (4,096 × 1)<br>Cascaded 4 Deep<br>and 16 Wide |                                                   |                                                    |

|       | 18 | Number Block  | 1                               | 2                              | 2                              | 4                                              | 8                                               | 18                                              | 32                                                 |                                                    |                                                   |                                                    |

|       | -  | Configuration | 256 × 8                         | 2 × (512 × 9)<br>Cascaded Wide | 2 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 2 Wide | 8 × (512 × 9)<br>Cascaded 4 Deep<br>and 2 Wide  | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 2 Wide | 16 × (512 × 9)<br>Cascaded 16<br>Deep and 2 Wide   |                                                    |                                                   |                                                    |

|       | 32 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              | 64                                                 |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 8 × (1,024 × 4)<br>Cascaded Wide               | 16 × (2,048 × 2)<br>Cascaded Wide               | 32 × (4,096 × 1)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded 2 Deep<br>and 32 Wide |                                                    |                                                   |                                                    |

|       | 36 | Number Block  | 2                               | 4                              | 4                              | 8                                              | 16                                              | 32                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 2 × (256 × 18)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded Wide | 4 × (512 × 9)<br>Cascaded 2 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 4 Wide | 16 × (512 × 9)<br>Cascaded 8 Deep<br>and 4 Wide |                                                    |                                                    |                                                   |                                                    |

|       | 64 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              | 64                                              |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (1,024 × 4)<br>Cascaded Wide              | 32 × (2,048 × 2)<br>Cascaded Wide               | 64 × (4,096 × 1)<br>Cascaded Wide               |                                                    |                                                    |                                                   |                                                    |

|       | 72 | Number Block  | 4                               | 8                              | 8                              | 16                                             | 32                                              |                                                 |                                                    |                                                    |                                                   |                                                    |

|       |    | Configuration | 4 × (256 × 18)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 8 × (512 × 9)<br>Cascaded Wide | 16 × (512 × 9)<br>Cascaded Wide                | 16 × (512 × 9)<br>Cascaded 4 Deep<br>and 8 Wide |                                                 |                                                    |                                                    |                                                   |                                                    |

Memory configurations represented by grayed cells are not supported.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## Initializing the RAM/FIFO

The SRAM blocks can be initialized with data to use as a lookup table (LUT). Data initialization can be accomplished either by loading the data through the design logic or through the UJTAG interface. The UJTAG macro is used to allow access from the JTAG port to the internal logic in the device. By sending the appropriate initialization string to the JTAG Test Access Port (TAP) Controller, the designer can put the JTAG circuitry into a mode that allows the user to shift data into the array logic through the JTAG port using the UJTAG macro. For a more detailed explanation of the UJTAG macro, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 117.

A user interface is required to receive the user command, initialization data, and clock from the UJTAG macro. The interface must synchronize and load the data into the correct RAM block of the design. The main outputs of the user interface block are the following:

- Memory block chip select: Selects a memory block for initialization. The chip selects signals for each memory block that can be generated from different user-defined pockets or simple logic, such as a ring counter (see below).

- · Memory block write address: Identifies the address of the memory cell that needs to be initialized.

- Memory block write data: The interface block receives the data serially from the UTDI port of the UJTAG macro and loads it in parallel into the write data ports of the memory blocks.

- Memory block write clock: Drives the WCLK of the memory block and synchronizes the write data, write address, and chip select signals.

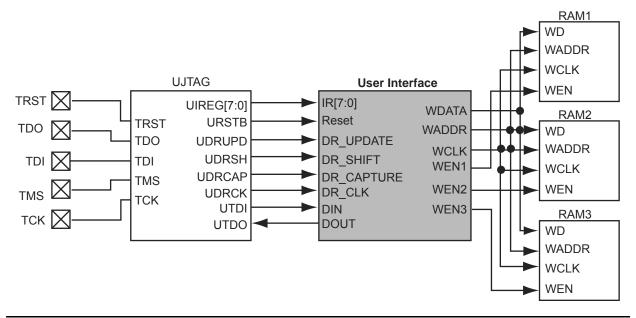

Figure 6-8 shows the user interface between UJTAG and the memory blocks.

Figure 6-8 • Interfacing TAP Ports and SRAM Blocks

An important component of the interface between the UJTAG macro and the RAM blocks is a serial-in/parallel-out shift register. The width of the shift register should equal the data width of the RAM blocks. The RAM data arrives serially from the UTDI output of the UJTAG macro. The data must be shifted into a shift register clocked by the JTAG clock (provided at the UDRCK output of the UJTAG macro).

Then, after the shift register is fully loaded, the data must be transferred to the write data port of the RAM block. To synchronize the loading of the write data with the write address and write clock, the output of the shift register can be pipelined before driving the RAM block.

The write address can be generated in different ways. It can be imported through the TAP using a different instruction opcode and another shift register, or generated internally using a simple counter. Using a counter to generate the address bits and sweep through the address range of the RAM blocks is

## 7 - I/O Structures in nano Devices

## Introduction

Low power flash devices feature a flexible I/O structure, supporting a range of mixed voltages (1.2 V, 1.5 V, 2.5 V, and 3.3 V) through bank-selectable voltages. IGLOO® and ProASIC3 nano devices support standard I/Os with the addition of Schmitt trigger and hot-swap capability.

Users designing I/O solutions are faced with a number of implementation decisions and configuration choices that can directly impact the efficiency and effectiveness of their final design. The flexible I/O structure, supporting a wide variety of voltages and I/O standards, enables users to meet the growing challenges of their many diverse applications. The Microsemi Libero® System-on-Chip (SoC) software provides an easy way to implement I/O that will result in robust I/O design.

This document describes Standard I/O types used for the nano devices in terms of he supported standards. It then explains the individual features and how to implement them in Libero SoC.

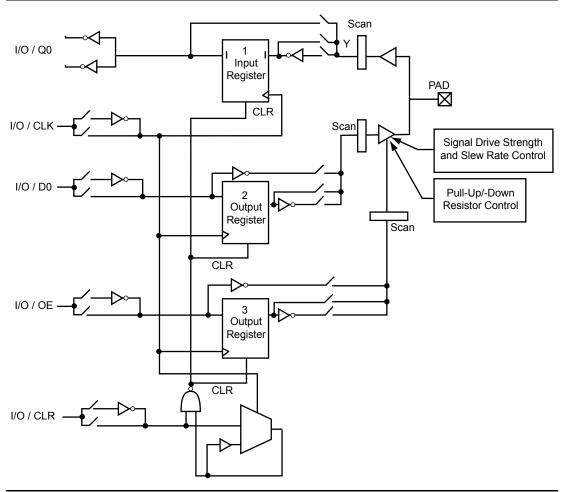

Figure 7-1 • I/O Block Logical Representation for Single-Tile Designs (10 k, 15 k, and 20 k devices)

# I/O Software Support

In Microsemi's Libero software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards.

Table 7-15 • nano I/O Attributes vs. I/O Standard Applications

|                      | SLEW             |                                                          |          | OUT_LOAD<br>(output only) |                    |                    |            |                     |

|----------------------|------------------|----------------------------------------------------------|----------|---------------------------|--------------------|--------------------|------------|---------------------|

| I/O Standard         | (output<br>only) | OUT_DRIVE (output only)                                  | RES_PULL | IGLOO<br>nano             | ProASIC<br>3 nano  | Schmitt<br>Trigger | Hold State | Combine<br>Register |

| LVTTL/<br>LVCMOS3.3  | 1                | <b>√</b> (8)                                             | ✓        | 1                         | 1                  | ✓                  | 1          | 1                   |

| LVCMOS2.5            | 1                | <b>√</b> (8)                                             | ✓        | ✓                         | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.8            | 1                | <b>√</b> (4)                                             | ✓        | 1                         | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.5            | 1                | <b>√</b> (2)                                             | ✓        | 1                         | ✓                  | ✓                  | ✓          | ✓                   |

| LVCMOS1.2            | 1                | <b>√</b> (2)                                             | ✓        | 1                         | _                  | 1                  | ✓          | ✓                   |

| Software<br>Defaults | HIGH             | Refer to<br>numbers in<br>parentheses<br>in above cells. | None     | All<br>Devices:<br>5 pF   | 10 pF or<br>35 pF* | Off                | Off        | No                  |

Note: \*10 pF for A3PN010, A3PN015, and A3PN020; 35 pF for A3PN060, A3PN125, and A3PN250.

#### ProASIC3 nano FPGA Fabric User's Guide

#### **VHDL**

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_BiDir_HSTL_I_LowEnb is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; QR, QF : out std_logic;

PAD : inout std_logic) ;

end DDR_BiDir_HSTL_I_LowEnb;

architecture DEF_ARCH of DDR_BiDir_HSTL_I_LowEnb is

component INV

port(A : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

component BIBUF_HSTL_I

port(PAD : inout std_logic := 'U'; D, E : in std_logic := 'U'; Y : out std_logic);

end component;

signal TrienAux, D, Q : std_logic ;

begin

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

DDR_REG_0_inst : DDR_REG

port map(D => D, CLK => CLK, CLR => CLR, QR => QR, QF => QF);

BIBUF_HSTL_I_0_inst : BIBUF_HSTL_I

port map(PAD => PAD, D => Q, E => TrienAux, Y => D);

end DEF_ARCH;

```

Table 11-6 and Table 11-7 show all available options. If you want to implement custom levels, refer to the "Advanced Options" section on page 256 for information on each option and how to set it.

3. When done, click **Finish** to generate the Security Header programming file.

Table 11-6 • All IGLOO and ProASIC3 Header File Security Options

| Security Option       | FlashROM Only | FPGA Core Only | Both FlashROM and FPGA |

|-----------------------|---------------|----------------|------------------------|

| No AES / no FlashLock | ✓             | ✓              | ✓                      |

| FlashLock only        | ✓             | ✓              | ✓                      |

| AES and FlashLock     | ✓             | ✓              | ✓                      |

Note:  $\checkmark$  = options that may be used

Table 11-7 • All Fusion Header File Security Options

| Security Option       | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / No FlashLock | 1             | ✓              | ✓            | ✓   |

| FlashLock             | 1             | ✓              | ✓            | ✓   |

| AES and FlashLock     | 1             | ✓              | 1            | 1   |

## Generation of Programming Files with AES Encryption— Application 3

This section discusses how to generate design content programming files needed specifically at unsecured or remote locations to program devices with a Security Header (FlashLock Pass Key and AES key) already programmed ("Application 2: Nontrusted Environment—Unsecured Location" section on page 243 and "Application 3: Nontrusted Environment—Field Updates/Upgrades" section on page 244). In this case, the encrypted programming file must correspond to the AES key already programmed into the device. If AES encryption was previously selected to encrypt the FlashROM, FBs, and FPGA array, AES encryption must be set when generating the programming file for them. AES encryption can be applied to the FlashROM only, the FBs only, the FPGA array only, or all. The user must ensure both the FlashLock Pass Key and the AES key match those already programmed to the device(s), and all security settings must match what was previously programmed. Otherwise, the encryption and/or device unlocking will not be recognized when attempting to program the device with the programming file.

The generated programming file will be AES-encrypted.

In this scenario, generate the programming file as follows:

Deselect Security settings and select the portion of the device to be programmed (Figure 11-17 on page 254). Select Programming previously secured device(s). Click Next.

Security in Low Power Flash Devices

#### **STAPL File with AES Encryption**

- Does not contain AES key / FlashLock Key information

- Intended for transmission through web or service to unsecured locations for programming

```

NOTE "CREATOR" "Designer Version: 6.1.1.108";

NOTE "DEVICE" "A3PE600";

NOTE "PACKAGE" "208 PQFP";

NOTE "DATE" "2005/04/08";

NOTE "STAPL_VERSION" "JESD71";

NOTE "IDCODE" "$123261CF";

NOTE "DESIGN" "counter32";

NOTE "CHECKSUM" "$EF57";

NOTE "SAVE_DATA" "FROMStream";

NOTE "SECURITY" "ENCRYPT FROM CORE ";

NOTE "ALG_VERSION" "1";

NOTE "MAX_FREQ" "200000000";

NOTE "SILSIG" "$000000000";

```

## Conclusion

The new and enhanced security features offered in Fusion, IGLOO, and ProASIC3 devices provide state-of-the-art security to designs programmed into these flash-based devices. Microsemi low power flash devices employ the encryption standard used by NIST and the U.S. government—AES using the 128-bit Rijndael algorithm.

The combination of an on-chip AES decryption engine and FlashLock technology provides the highest level of security against invasive attacks and design theft, implementing the most robust and secure ISP solution. These security features protect IP within the FPGA and protect the system from cloning, wholesale "black box" copying of a design, invasive attacks, and explicit IP or data theft.

## **Glossary**

| Term                             | Explanation                                                                                                                                                                   |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Security Header programming file | Programming file used to program the FlashLock Pass Key and/or AES key into the device to secure the FPGA, FlashROM, and/or FBs.                                              |  |

| AES (encryption) key             | 128-bit key defined by the user when the AES encryption option is set in the Microsemi Designer software when generating the programming file.                                |  |

| FlashLock Pass Key               | 128-bit key defined by the user when the FlashLock option is set in the Microsemi Designer software when generating the programming file.                                     |  |

|                                  | The FlashLock Key protects the security settings programmed to the device. Once a device is programmed with FlashLock, whatever settings were chosen at that time are secure. |  |

| FlashLock                        | The combined security features that protect the device content from attacks. These features are the following:                                                                |  |

|                                  | Flash technology that does not require an external bitstream to program the device                                                                                            |  |

|                                  | FlashLock Pass Key that secures device content by locking the security settings and preventing access to the device as defined by the user                                    |  |

|                                  | AES key that allows secure, encrypted device reprogrammability                                                                                                                |  |

## References

National Institute of Standards and Technology. "ADVANCED ENCRYPTION STANDARD (AES) Questions and Answers." 28 January 2002 (10 January 2005).

See http://csrc.nist.gov/archive/aes/index1.html for more information.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

## IEEE 1532 (JTAG) Interface

The supported industry-standard IEEE 1532 programming interface builds on the IEEE 1149.1 (JTAG) standard. IEEE 1532 defines the standardized process and methodology for ISP. Both silicon and software issues are addressed in IEEE 1532 to create a simplified ISP environment. Any IEEE 1532 compliant programmer can be used to program low power flash devices. Device serialization is not supported when using the IEEE1532 standard. Refer to the standard for detailed information about IEEE 1532.

## **Security**

Unlike SRAM-based FPGAs that require loading at power-up from an external source such as a microcontroller or boot PROM, Microsemi nonvolatile devices are live at power-up, and there is no bitstream required to load the device when power is applied. The unique flash-based architecture prevents reverse engineering of the programmed code on the device, because the programmed data is stored in nonvolatile memory cells. Each nonvolatile memory cell is made up of small capacitors and any physical deconstruction of the device will disrupt stored electrical charges.

Each low power flash device has a built-in 128-bit Advanced Encryption Standard (AES) decryption core, except for the 30 k gate devices and smaller. Any FPGA core or FlashROM content loaded into the device can optionally be sent as encrypted bitstream and decrypted as it is loaded. This is particularly suitable for applications where device updates must be transmitted over an unsecured network such as the Internet. The embedded AES decryption core can prevent sensitive data from being intercepted (Figure 12-1 on page 265). A single 128-bit AES Key (32 hex characters) is used to encrypt FPGA core programming data and/or FlashROM programming data in the Microsemi tools. The low power flash devices also decrypt with a single 128-bit AES Key. In addition, low power flash devices support a Message Authentication Code (MAC) for authentication of the encrypted bitstream on-chip. This allows the encrypted bitstream to be authenticated and prevents erroneous data from being programmed into the device. The FPGA core, FlashROM, and Flash Memory Blocks (FBs), in Fusion only, can be updated independently using a programming file that is AES-encrypted (cipher text) or uses plain text.

UJTAG Applications in Microsemi's Low Power Flash Devices

## **UJTAG Support in Flash-Based Devices**

The flash-based FPGAs listed in Table 16-1 support the UJTAG feature and the functions described in this document.

Table 16-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                    |  |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                              |  |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                          |  |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                            |  |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                     |  |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                        |  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                       |  |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                            |  |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                          |  |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                    |  |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                          |  |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                           |  |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmab analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flas memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 16-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 16-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.