Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 34                                                                        |

| Number of Gates                | 30000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package        | 48-QFN (6x6)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-zqng48i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Clock Aggregation Architecture**

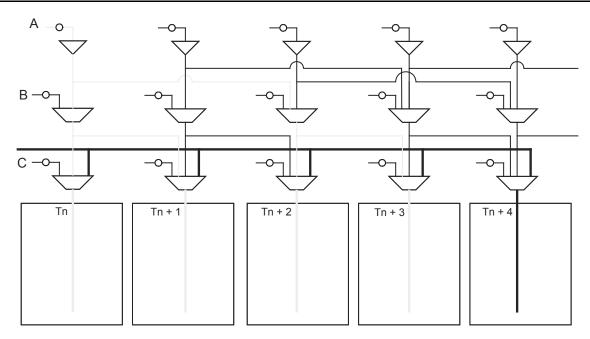

This clock aggregation feature allows a balanced clock tree, which improves clock skew. The physical regions for clock aggregation are defined from left to right and shift by one spine. For chip global networks, there are three types of clock aggregation available, as shown in Figure 3-10:

- Long lines that can drive up to four adjacent spines (A)

- · Long lines that can drive up to two adjacent spines (B)

- · Long lines that can drive one spine (C)

There are three types of clock aggregation available for the quadrant spines, as shown in Figure 3-10:

- I/Os or local resources that can drive up to four adjacent spines

- I/Os or local resources that can drive up to two adjacent spines

- I/Os or local resources that can drive one spine

As an example, A3PE600 and AFS600 devices have twelve spine locations: T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, and B6. Table 3-7 shows the clock aggregation you can have in A3PE600 and AFS600.

Figure 3-10 • Four Spines Aggregation

Table 3-7 • Spine Aggregation in A3PE600 or AFS600

| Clock Aggregation | Spine                                                                |

|-------------------|----------------------------------------------------------------------|

| 1 spine           | T1, T2, T3, T4, T5, T6, B1, B2, B3, B4, B5, B6                       |

| 2 spines          | T1:T2, T2:T3, T3:T4, T4:T5, T5:T6, B1:B2, B2:B3, B3:B4, B4:B5, B5:B6 |

| 4 spines          | B1:B4, B2:B5, B3:B6, T1:T4, T2:T5, T3:T6                             |

The clock aggregation for the quadrant spines can cross over from the left to right quadrant, but not from top to bottom. The quadrant spine assignment T1:T4 is legal, but the quadrant spine assignment T1:B1 is not legal. Note that this clock aggregation is hardwired. You can always assign signals to spine T1 and B2 by instantiating a buffer, but this may add skew in the signal.

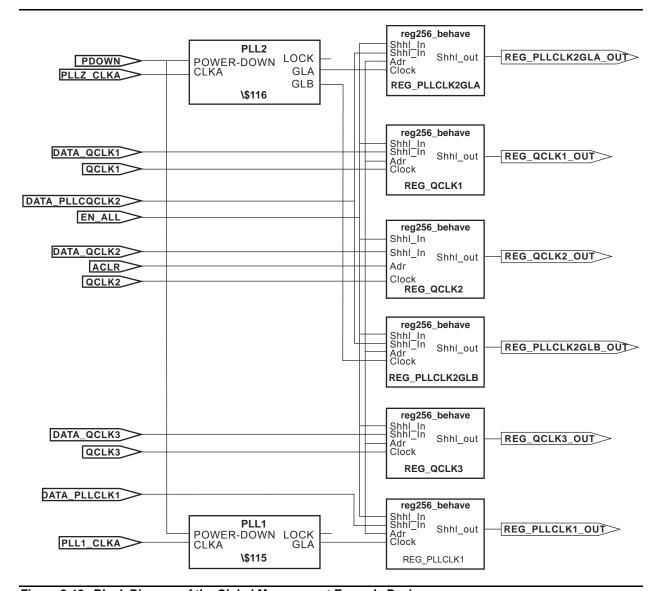

## Simple Design Example

Consider a design consisting of six building blocks (shift registers) and targeted for an A3PE600-PQ208 (Figure 3-16 on page 52). The example design consists of two PLLs (PLL1 has GLA only; PLL2 has both GLA and GLB), a global reset (ACLR), an enable (EN\_ALL), and three external clock domains (QCLK1, QCLK2, and QCLK3) driving the different blocks of the design. Note that the PQ208 package only has two PLLs (which access the chip global network). Because of fanout, the global reset and enable signals need to be assigned to the chip global resources. There is only one free chip global for the remaining global (QCLK1, QCLK2, QCLK3). Place two of these signals on the quadrant global resource. The design example demonstrates manually assignment of QCLK1 and QCLK2 to the quadrant global using the PDC command.

Figure 3-19 • Block Diagram of the Global Management Example Design

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Global Buffers with No Programmable Delays**

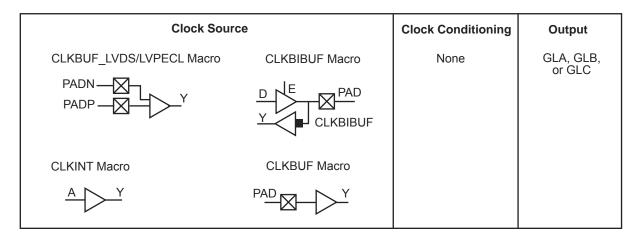

Access to the global / quadrant global networks can be configured directly from the global I/O buffer, bypassing the CCC functional block (as indicated by the dotted lines in Figure 4-1 on page 61). Internal signals driven by the FPGA core can use the global / quadrant global networks by connecting via the routed clock input of the multiplexer tree.

There are many specific CLKBUF macros supporting the wide variety of single-ended I/O inputs (CLKBUF) and differential I/O standards (CLKBUF\_LVDS/LVPECL) in the low power flash families. They are used when connecting global I/Os directly to the global/quadrant networks.

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

When an internal signal needs to be connected to the global/quadrant network, the CLKINT macro is used to connect the signal to the routed clock input of the network's MUX tree.

To utilize direct connection from global I/Os or from internal signals to the global/quadrant networks, CLKBUF, CLKBUF LVPECL/LVDS, and CLKINT macros are used (Figure 4-2).

- The CLKBUF and CLKBUF\_LVPECL/LVDS<sup>1</sup> macros are composite macros that include an I/O macro driving a global buffer, which uses a hardwired connection.

- The CLKBUF, CLKBUF\_LVPECL/LVDS<sup>1</sup> and CLKINT macros are pass-through clock sources and do not use the PLL or provide any programmable delay functionality.

- The CLKINT macro provides a global buffer function driven internally by the FPGA core.

The available CLKBUF macros are described in the *IGLOO*, *ProASIC3*, *SmartFusion*, and *Fusion Macro Library Guide*.

Note: IGLOO nano and ProASIC nano devices do not support differential inputs.

Figure 4-2 • CCC Options: Global Buffers with No Programmable Delay

# **Global Buffer with Programmable Delay**

Clocks requiring clock adjustments can utilize the programmable delay cores before connecting to the global / quadrant global networks. A maximum of 18 CCC global buffers can be instantiated in a device—three per CCC and up to six CCCs per device.

Each CCC functional block contains a programmable delay element for each of the global networks (up to three), and users can utilize these features by using the corresponding macro (Figure 4-3 on page 65).

<sup>1.</sup> B-LVDS and M-LVDS are supported with the LVDS macro.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **PLL Macro Signal Descriptions**

The PLL macro supports two inputs and up to six outputs. Table 4-3 gives a description of each signal.

Table 4-3 • Input and Output Signals of the PLL Block

| Signal    | Name                                  | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKA      | Reference Clock                       | Input  | Reference clock input for PLL core; input clock for primary output clock, GLA                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| OADIVRST  | Reset Signal for the Output Divider A | Input  | For Fusion only. OADIVRST can be used when you bypass the PLL core (i.e., OAMUX = 001). The purpose of the OADIVRST signals is to reset the output of the final clock divider to synchronize it with the input to that divider when the PLL is bypassed. The signal is active on a low to high transition. The signal must be low for at least one divider input. If PLL core is used, this signal is "don't care" and the internal circuitry will generate the reset signal for the synchronization purpose. |

| OADIVHALF | Output A Division by<br>Half          | Input  | For Fusion only. Active high. Division by half feature. This feature can only be used when users bypass the PLL core (i.e., OAMUX = 001) and the RC Oscillator (RCOSC) drives the CLKA input. This can be used to divide the 100 MHz RC oscillator by a factor of 1.5, 2.5, 3.5, 4.5 14.5). Refer to Table 4-18 on page 95 for more information.                                                                                                                                                              |

| EXTFB     | External Feedback                     | Input  | Allows an external signal to be compared to a reference clock in the PLL core's phase detector.                                                                                                                                                                                                                                                                                                                                                                                                               |

| POWERDOWN | Power Down                            | Input  | Active low input that selects power-down mode and disables the PLL. With the POWERDOWN signal asserted, the PLL core sends 0 V signals on all of the outputs.                                                                                                                                                                                                                                                                                                                                                 |

| GLA       | Primary Output                        | Output | Primary output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GLB       | Secondary 1 Output                    | Output | Secondary 1 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YB        | Core 1 Output                         | Output | Core 1 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GLC       | Secondary 2 Output                    | Output | Secondary 2 output clock to respective global/quadrant clock networks                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| YC        | Core 2 Output                         | Output | Core 2 output clock to local routing network                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LOCK      | PLL Lock Indicator                    | Output | Active high signal indicating that steady-state lock has been achieved between CLKA and the PLL feedback signal                                                                                                                                                                                                                                                                                                                                                                                               |

#### Input Clock

The inputs to the input reference clock (CLKA) of the PLL can come from global input pins, regular I/O pins, or internally from the core. For Fusion families, the input reference clock can also be from the embedded RC oscillator or crystal oscillator.

# **Global Output Clocks**

GLA (Primary), GLB (Secondary 1), and GLC (Secondary 2) are the outputs of Global Multiplexer 1, Global Multiplexer 2, and Global Multiplexer 3, respectively. These signals (GLx) can be used to drive the high-speed global and quadrant networks of the low power flash devices.

A global multiplexer block consists of the input routing for selecting the input signal for the GLx clock and the output multiplexer, as well as delay elements associated with that clock.

# **Core Output Clocks**

YB and YC are known as Core Outputs and can be used to drive internal logic without using global network resources. This is especially helpful when global network resources must be conserved and utilized for other timing-critical paths.

#### IGLOO and ProASIC3 CCC Locations

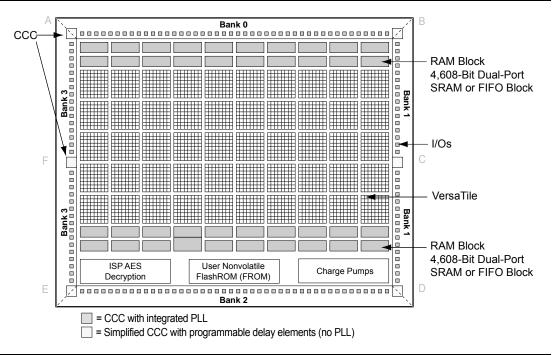

In all IGLOO and ProASIC3 devices (except 10 k through 30 k gate devices, which do not contain PLLs), six CCCs are located in the same positions as the IGLOOe and ProASIC3E CCCs. Only one of the CCCs has an integrated PLL and is located in the middle of the west (middle left) side of the device. The other five CCCs are simplified CCCs and are located in the four corners and the middle of the east side of the device (Figure 4-14).

Figure 4-14 • CCC Locations in IGLOO and ProASIC3 Family Devices (except 10 k through 30 k gate devices)

Note: The number and architecture of the banks are different for some devices.

10 k through 30 k gate devices do not support PLL features. In these devices, there are two CCC-GLs at the lower corners (one at the lower right, and one at the lower left). These CCC-GLs do not have programmable delays.

DEVICE\_INFO displays the FlashROM content, serial number, Design Name, and checksum, as shown below:

```

EXPORT IDCODE[32] = 123261CF

EXPORT SILSIG[32] = 00000000

User information:

CHECKSUM: 61A0

Design Name:

Programming Method: STAPL

Algorithm Version: 1

Programmer: UNKNOWN

_____

FlashROM Information :

______

Security Setting :

Encrypted FlashROM Programming Enabled.

Encrypted FPGA Array Programming Enabled.

```

The Libero SoC file manager recognizes the UFC and MEM files and displays them in the appropriate view. Libero SoC also recognizes the multiple programming files if you choose the option to generate multiple files for multiple FlashROM contents in Designer. These features enable a user-friendly flow for the FlashROM generation and programming in Libero SoC.

# **Custom Serialization Using FlashROM**

You can use FlashROM for device serialization or inventory control by using the Auto Inc region or Read From File region. FlashPoint will automatically generate the serial number sequence for the Auto Inc region with the **Start Value**, **Max Value**, and **Step Value** provided. If you have a unique serial number generation scheme that you prefer, the Read From File region allows you to import the file with your serial number scheme programmed into the region. See the *FlashPro User's Guide* for custom serialization file format information.

The following steps describe how to perform device serialization or inventory control using FlashROM:

- Generate FlashROM using SmartGen. From the Properties section in the FlashROM Settings dialog box, select the **Auto Inc** or **Read From File** region. For the Auto Inc region, specify the desired step value. You will not be able to modify this value in the FlashPoint software.

- 2. Go through the regular design flow and finish place-and-route.

- 3. Select **Programming File in Designer** and open **Generate Programming File** (Figure 5-12 on page 128).

- 4. Click **Program FlashROM**, browse to the UFC file, and click **Next**. The FlashROM Settings window appears, as shown in Figure 5-13 on page 128.

- 5. Select the FlashROM page you want to program and the data value for the configured regions. The STAPL file generated will contain only the data that targets the selected FlashROM page.

- 6. Modify properties for the serialization.

- For the Auto Inc region, specify the Start and Max values.

- For the Read From File region, select the file name of the custom serialization file.

- 7. Select the FlashROM programming file type you want to generate from the two options below:

- Single programming file for all devices: generates one programming file with all FlashROM values.

- One programming file per device: generates a separate programming file for each FlashROM value.

- 8. Enter the number of devices you want to program and generate the required programming file.

- 9. Open the programming software and load the programming file. The programming software, FlashPro3 and Silicon Sculptor II, supports the device serialization feature. If, for some reason, the device fails to program a part during serialization, the software allows you to reuse or skip the serial data. Refer to the FlashPro User's Guide for details.

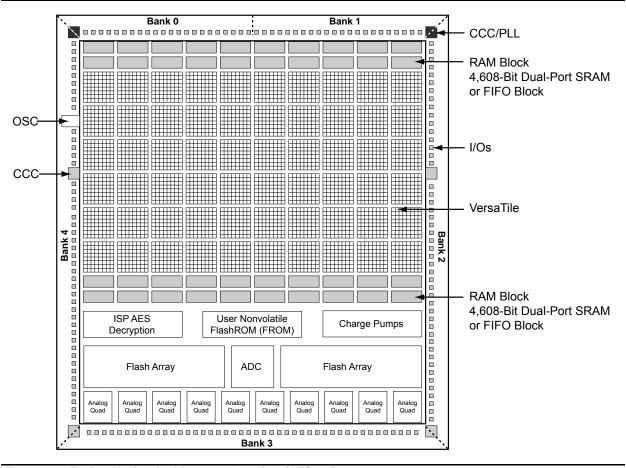

Figure 6-2 • Fusion Device Architecture Overview (AFS600)

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Designer software will automatically facilitate falling-edge clocks by bubble-pushing the inversion to previous stages.

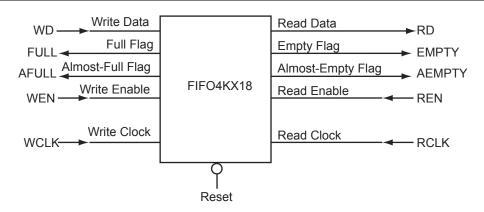

Figure 6-6 • FIFO4KX18 Block Diagram

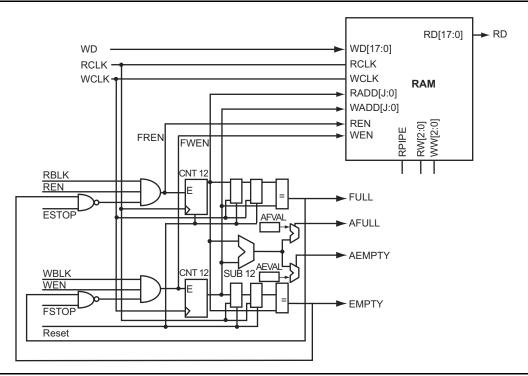

Figure 6-7 • RAM Block with Embedded FIFO Controller

The FIFOs maintain a separate read and write address. Whenever the difference between the write address and the read address is greater than or equal to the almost-full value (AFVAL), the Almost-Full flag is asserted. Similarly, the Almost-Empty flag is asserted whenever the difference between the write address and read address is less than or equal to the almost-empty value (AEVAL).

Due to synchronization between the read and write clocks, the Empty flag will deassert after the second read clock edge from the point that the write enable asserts. However, since the Empty flag is synchronized to the read clock, it will assert after the read clock reads the last data in the FIFO. Also, since the Full flag is dependent on the actual hardware configuration, it will assert when the actual physical implementation of the FIFO is full.

For example, when a user configures a 128×18 FIFO, the actual physical implementation will be a 256×18 FIFO element. Since the actual implementation is 256×18, the Full flag will not trigger until the

## Pipeline Register

endmodule

endmodule

```

module D_pipeline (Data, Clock, Q);

input [3:0] Data;

input Clock;

output [3:0] Q;

reg [3:0] Q;

always @ (posedge Clock) Q <= Data;</pre>

```

#### 4x4 RAM Block (created by SmartGen Core Generator)

```

module mem_block(DI,DO,WADDR,RADDR,WRB,RDB,WCLOCK,RCLOCK);

input [3:0] DI;

output [3:0] DO;

input [1:0] WADDR, RADDR;

input WRB, RDB, WCLOCK, RCLOCK;

wire WEBP, WEAP, VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

INV WEBUBBLEB(.A(WRB), .Y(WEBP));

RAM4K9 RAMBLOCKO(.ADDRA11(GND), .ADDRA10(GND), .ADDRA9(GND), .ADDRA8(GND),

.ADDRA7(GND), .ADDRA6(GND), .ADDRA5(GND), .ADDRA4(GND), .ADDRA3(GND), .ADDRA2(GND),

.ADDRA1(RADDR[1]), .ADDRA0(RADDR[0]), .ADDRB11(GND), .ADDRB10(GND), .ADDRB9(GND),

.ADDRB8(GND), .ADDRB7(GND), .ADDRB6(GND), .ADDRB5(GND), .ADDRB4(GND), .ADDRB3(GND),

.ADDRB2(GND), .ADDRB1(WADDR[1]), .ADDRB0(WADDR[0]), .DINA8(GND), .DINA7(GND),

.DINA6(GND), .DINA5(GND), .DINA4(GND), .DINA3(GND), .DINA2(GND), .DINA1(GND),

.DINAO(GND), .DINB8(GND), .DINB7(GND), .DINB6(GND), .DINB5(GND), .DINB4(GND),

.DINB3(DI[3]), .DINB2(DI[2]), .DINB1(DI[1]), .DINB0(DI[0]), .WIDTHA0(GND),

.WIDTHA1(VCC), .WIDTHB0(GND), .WIDTHB1(VCC), .PIPEA(GND), .PIPEB(GND),

.WMODEA(GND), .WMODEB(GND), .BLKA(WEAP), .BLKB(WEBP), .WENA(VCC), .WENB(GND),

.CLKA(RCLOCK), .CLKB(WCLOCK), .RESET(VCC), .DOUTA8(), .DOUTA7(), .DOUTA6(),

. \verb"DOUTA5()", .DOUTA4()", .DOUTA3(DO[3])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA2(DO[

.DOUTA0(DO[0]), .DOUTB8(), .DOUTB7(), .DOUTB5(), .DOUTB5(), .DOUTB4(), .DOUTB3(),

.DOUTB2(), .DOUTB1(), .DOUTB0());

INV WEBUBBLEA(.A(RDB), .Y(WEAP));

```

ProASIC3 nano FPGA Fabric User's Guide

SmartGen enables the user to configure the desired RAM element to use either a single clock for read and write, or two independent clocks for read and write. The user can select the type of RAM as well as the width/depth and several other parameters (Figure 6-13).

## Figure 6-13 • SmartGen Memory Configuration Interface

SmartGen also has a Port Mapping option that allows the user to specify the names of the ports generated in the memory block (Figure 6-14).

#### Figure 6-14 • Port Mapping Interface for SmartGen-Generated Memory

SmartGen also configures the FIFO according to user specifications. Users can select no flags, static flags, or dynamic flags. Static flag settings are configured using configuration flash and cannot be altered

#### I/O Structures in nano Devices

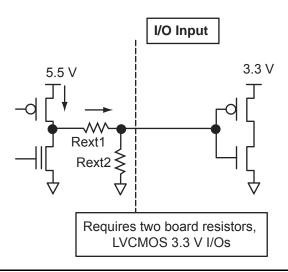

Example 2 (low-medium speed, medium current):

```

Rtx_out_high = Rtx_out_low = 10 \Omega

R1 = 220 \Omega (±5%), P(r1)min = 0.018 \Omega

R2 = 390 \Omega (±5%), P(r2)min = 0.032 \Omega

Imax_tx = 5.5 V / (220 × 0.95 + 390 × 0.95 + 10) = 9.17 mA

t_{RISE} = t_{FALL} = 4 ns at C_pad_load = 10 pF (includes up to 25% safety margin)

t_{RISE} = t_{FALL} = 20 ns at C_pad_load = 50 pF (includes up to 25% safety margin)

```

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin (rx) < 3.6 V when the transmitter sends a logic 1. This range of Vin\_dc(rx) must be assured for any combination of transmitter supply (5 V  $\pm$  0.5 V), transmitter output resistance, and board resistor tolerances.

Temporary overshoots are allowed according to the overshoot and undershoot table in the datasheet.

#### Solution 1

Figure 7-5 • Solution 1

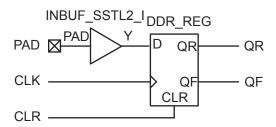

# **DDR Input Register**

Figure 9-5 • DDR Input Register (SSTL2 Class I)

The corresponding structural representations, as generated by SmartGen, are shown below:

#### Verilog

end DEF\_ARCH;

```

module DDR_InBuf_SSTL2_I(PAD,CLR,CLK,QR,QF);

input PAD, CLR, CLK;

output QR, QF;

wire Y;

INBUF_SSTL2_I INBUF_SSTL2_I_0_inst(.PAD(PAD),.Y(Y));

DDR_REG_DDR_REG_O_inst(.D(Y),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

endmodule

VHDL

library ieee;

use ieee.std_logic_1164.all;

--The correct library will be inserted automatically by SmartGen

library proasic3; use proasic3.all;

--library fusion; use fusion.all;

--library igloo; use igloo.all;

entity DDR_InBuf_SSTL2_I is

port(PAD, CLR, CLK : in std_logic; QR, QF : out std_logic) ;

end DDR_InBuf_SSTL2_I;

architecture DEF_ARCH of DDR_InBuf_SSTL2_I is

component INBUF_SSTL2_I

port(PAD : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

signal Y : std_logic ;

begin

INBUF_SSTL2_I_0_inst : INBUF_SSTL2_I

port map(PAD => PAD, Y => Y);

DDR_REG_0_inst : DDR_REG

\label{eq:clk_port_map} \texttt{port_map}(\texttt{D} => \texttt{Y}, \texttt{CLK} => \texttt{CLK}, \texttt{CLR} => \texttt{CLR}, \texttt{QR} => \texttt{QR}, \texttt{QF} => \texttt{QF});

```

#### Signal Integrity While Using ISP

For ISP of flash devices, customers are expected to follow the board-level guidelines provided on the Microsemi SoC Products Group website. These guidelines are discussed in the datasheets and application notes (refer to the "Related Documents" section of the datasheet for application note links). Customers are also expected to troubleshoot board-level signal integrity issues by measuring voltages and taking oscilloscope plots.

## **Programming Failure Allowances**

Microsemi has strict policies regarding programming failure allowances. Please refer to *Programming and Functional Failure Guidelines* on the Microsemi SoC Products Group website for details.

## **Contacting the Customer Support Group**

Highly skilled engineers staff the Customer Applications Center from 7:00 A.M. to 6:00 P.M., Pacific time, Monday through Friday. You can contact the center by one of the following methods:

#### Electronic Mail

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. Microsemi monitors the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and contact information for efficient processing of your request. The technical support email address is soc tech@microsemi.com.

#### Telephone

Our Technical Support Hotline answers all calls. The center retrieves information, such as your name, company name, telephone number, and question. Once this is done, a case number is assigned. Then the center forwards the information to a queue where the first available applications engineer receives the data and returns your call. The phone hours are from 7:00 A.M. to 6:00 P.M., Pacific time, Monday through Friday.

The Customer Applications Center number is (800) 262-1060.

European customers can call +44 (0) 1256 305 600.

ProASIC3 nano FPGA Fabric User's Guide

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level (Figure 11-12). Click **Next**.

If you want to select different options for the FPGA and/or FlashROM, this can be set by clicking **Custom Level**. Refer to the "Advanced Options" section on page 256 for different custom security level options and descriptions of each.

Figure 11-12 • Medium Security Level Selected for Low Power Flash Devices

#### Figure 11-19 • FlashLock Pass Key, Previously Programmed Devices

It is important to note that when the security settings need to be updated, the user also needs to select the **Security settings** check box in Step 1, as shown in Figure 11-10 on page 248 and Figure 11-11 on page 248, to modify the security settings. The user must consider the following:

- If only a new AES key is necessary, the user must re-enter the same Pass Key previously programmed into the device in Designer and then generate a programming file with the same Pass Key and a different AES key. This ensures the programming file can be used to access and program the device and the new AES key.

- If a new Pass Key is necessary, the user can generate a new programming file with a new Pass Key (with the same or a new AES key if desired). However, for programming, the user must first load the original programming file with the Pass Key that was previously used to unlock the device. Then the new programming file can be used to program the new security settings.

# **Advanced Options**

As mentioned, there may be applications where more complicated security settings are required. The "Custom Security Levels" section in the *FlashPro User's Guide* describes different advanced options available to aid the user in obtaining the best available security settings.

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

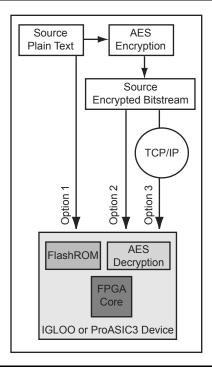

Figure 12-2 shows different applications for ISP programming.

- 1. In a trusted programming environment, you can program the device using the unencrypted (plaintext) programming file.

- 2. You can program the AES Key in a trusted programming environment and finish the final programming in an untrusted environment using the AES-encrypted (cipher text) programming file.

- 3. For the remote ISP updating/reprogramming, the AES Key stored in the device enables the encrypted programming bitstream to be transmitted through the untrusted network connection.

Microsemi low power flash devices also provide the unique Microsemi FlashLock feature, which protects the Pass Key and AES Key. Unless the original FlashLock Pass Key is used to unlock the device, security settings cannot be modified. Microsemi does not support read-back of FPGA core-programmed data; however, the FlashROM contents can selectively be read back (or disabled) via the JTAG port based on the security settings established by the Microsemi Designer software. Refer to the "Security in Low Power Flash Devices" section on page 235 for more information.

Figure 12-2 • Different ISP Use Models

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

Table 12-4 • Programming Header Pin Numbers and Description

| Pin | Signal             | Source                  | Description                                                                                                                          |

|-----|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TCK                | Programmer              | JTAG Clock                                                                                                                           |

| 2   | GND <sup>1</sup>   | -                       | Signal Reference                                                                                                                     |

| 3   | TDO                | Target Board            | Test Data Output                                                                                                                     |

| 4   | NC                 | -                       | No Connect (FlashPro3/3X); Prog_Mode (FlashPro4). See note associated with Figure 12-5 on page 269 regarding Prog_Mode on FlashPro4. |

| 5   | TMS                | Programmer              | Test Mode Select                                                                                                                     |

| 6   | VJTAG              | Target Board            | JTAG Supply Voltage                                                                                                                  |

| 7   | VPUMP <sup>2</sup> | Programmer/Target Board | Programming Supply Voltage                                                                                                           |

| 8   | nTRST              | Programmer              | JTAG Test Reset (Hi-Z with 10 $k\Omega$ pull-down, HIGH, LOW, or toggling)                                                           |

| 9   | TDI                | Programmer              | Test Data Input                                                                                                                      |

| 10  | GND <sup>1</sup>   | _                       | Signal Reference                                                                                                                     |

#### Notes:

- 1. Both GND pins must be connected.

- 2. FlashPro4/3/3X can provide VPUMP if there is only one device on the target board.

# 13 – Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Introduction

The IGLOO<sup>®</sup> and ProASIC<sup>®</sup>3L families offer devices that can be powered by either 1.5 V or, in the case of V2 devices, a core supply voltage anywhere in the range of 1.2 V to 1.5 V, in 50 mV increments.

Since IGLOO and ProASIC3L devices are flash-based, they can be programmed and reprogrammed multiple times in-system using Microsemi FlashPro3. FlashPro3 uses the JTAG standard interface (IEEE 1149.1) and STAPL file (defined in JESD 71 to support programming of programmable devices using IEEE 1149.1) for in-system configuration/programming (IEEE 1532) of a device. Programming can also be executed by other methods, such as an embedded microcontroller that follows the same standards above.

All IGLOO and ProASIC3L devices must be programmed with the VCC core voltage at 1.5 V. Therefore, applications using IGLOO or ProASIC3L devices powered by a 1.2 V supply must switch the core supply to 1.5 V for in-system programming.

The purpose of this document is to describe an easy-to-use and cost-effective solution for switching the core supply voltage from 1.2 V to 1.5 V during in-system programming for IGLOO and ProASIC3L devices.

### ProASIC3 nano FPGA Fabric User's Guide

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                   | Changes                                                                                                                                               | Page |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010              | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.             | N/A  |

| v1.1<br>(October 2008) | The "Introduction" was revised to include information about the core supply voltage range of operation in V2 devices.                                 | 275  |

|                        | IGLOO nano device support was added to Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit.                                           | 276  |

|                        | The "Circuit Description" section was updated to include IGLOO PLUS core operation from 1.2 V to 1.5 V in 50 mV increments.                           | 277  |

| v1.0<br>(August 2008)  | The "Microsemi's Flash Families Support Voltage Switching Circuit" section was revised to include new families and make the information more concise. | 276  |

# **Microprocessor Programming Support in Flash Devices**

The flash-based FPGAs listed in Table 14-1 support programming with a microprocessor and the functions described in this document.

Table 14-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGL00    | IGL00                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

# **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 14-1. Where the information applies to only one device or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.