Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |  |

|--------------------------------|---------------------------------------------------------------------------|--|

| Product Status                 | Active                                                                    |  |

| Number of LABs/CLBs            | -                                                                         |  |

| Number of Logic Elements/Cells | -                                                                         |  |

| Total RAM Bits                 | -                                                                         |  |

| Number of I/O                  | 77                                                                        |  |

| Number of Gates                | 30000                                                                     |  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |  |

| Mounting Type                  | Surface Mount                                                             |  |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |  |

| Package / Case                 | 100-TQFP                                                                  |  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |  |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn030-zvqg100 |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs

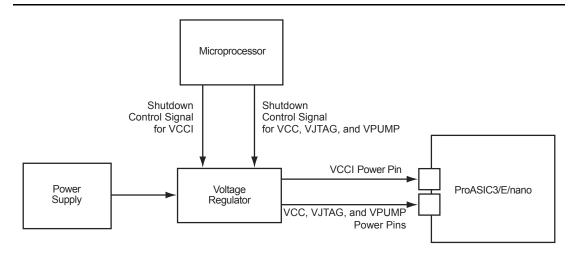

Alternatively, Figure 2-7 shows how a microprocessor can be used with a voltage regulator's shutdown pin to turn the power supplies connected to the device on or off.

Figure 2-7 • Controlling Power On/Off State Using Microprocessor and Voltage Regulator

Though Sleep mode or Shutdown mode can be used to save power, the content of the SRAM and the state of the registers is lost when power is turned off if no other measure is taken. To keep the original contents of the device, a low-cost external serial EEPROM can be used to save and restore the device contents when entering and exiting Sleep mode. In the *Embedded SRAM Initialization Using External Serial EEPROM* application note, detailed information and a reference design are provided to initialize the embedded SRAM using an external serial EEPROM. The user can easily customize the reference design to save and restore the FPGA state when entering and exiting Sleep mode. The microcontroller will need to manage this activity, so before powering down VCC, the data must be read from the FPGA and stored externally. Similarly, after the FPGA is powered up, the microcontroller must allow the FPGA to load the data from external memory and restore its original state.

## Conclusion

Microsemi ProASIC3/E and ProASIC3 nano FPGAs inherit low power consumption capability from their nonvolatile and live-at-power-up flash-based technology. Power consumption can be reduced further using the Static (Idle), User Low Static (Idle), Sleep, or Shutdown power modes. All these features result in a low-power, cost-effective, single-chip solution designed specifically for power-sensitive electronics applications.

## **Related Documents**

## **Application Notes**

Embedded SRAM Initialization Using External Serial EEPROM http://www.microsemi.com/soc/documents/EmbeddedSRAMInit AN.pdf

# 3 – Global Resources in Low Power Flash Devices

## Introduction

IGLOO, Fusion, and ProASIC3 FPGA devices offer a powerful, low-delay VersaNet global network scheme and have extensive support for multiple clock domains. In addition to the Clock Conditioning Circuits (CCCs) and phase-locked loops (PLLs), there is a comprehensive global clock distribution network called a VersaNet global network. Each logical element (VersaTile) input and output port has access to these global networks. The VersaNet global networks can be used to distribute low-skew clock signals or high-fanout nets. In addition, these highly segmented VersaNet global networks contain spines (the vertical branches of the global network tree) and ribs that can reach all the VersaTiles inside their region. This allows users the flexibility to create low-skew local clock networks using spines. This document describes VersaNet global networks and discusses how to assign signals to these global networks and spines in a design flow. Details concerning low power flash device PLLs are described in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" section on page 61. This chapter describes the low power flash devices' global architecture and uses of these global networks in designs.

## **Global Architecture**

Low power flash devices offer powerful and flexible control of circuit timing through the use of global circuitry. Each chip has up to six CCCs, some with PLLs.

- In IGLOOe, ProASIC3EL, and ProASIC3E devices, all CCCs have PLLs—hence, 6 PLLs per device (except the PQ208 package, which has only 2 PLLs).

- In IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, and ProASIC3L devices, the west CCC contains a PLL core (except in 10 k through 30 k devices).

- In Fusion devices, the west CCC also contains a PLL core. In the two larger devices (AFS600 and AFS1500), the west and east CCCs each contain a PLL.

Refer to Table 4-6 on page 84 for details. Each PLL includes delay lines, a phase shifter (0°, 90°, 180°, 270°), and clock multipliers/dividers. Each CCC has all the circuitry needed for the selection and interconnection of inputs to the VersaNet global network. The east and west CCCs each have access to three chip global lines on each side of the chip (six chip global lines total). The CCCs at the four corners each have access to three quadrant global lines in each quadrant of the chip (except in 10 k through 30 k gate devices).

The nano 10 k, 15 k, and 20 k devices support four VersaNet global resources, and 30 k devices support six global resources. The 10 k through 30 k devices have simplified CCCs called CCC-GLs.

The flexible use of the VersaNet global network allows the designer to address several design requirements. User applications that are clock-resource-intensive can easily route external or gated internal clocks using VersaNet global routing networks. Designers can also drastically reduce delay penalties and minimize resource usage by mapping critical, high-fanout nets to the VersaNet global network.

Note: Microsemi recommends that you choose the appropriate global pin and use the appropriate global resource so you can realize these benefits.

The following sections give an overview of the VersaNet global network, the structure of the global network, access point for the global networks, and the clock aggregation feature that enables a design to have very low clock skew using spines.

Table 3-3 • Quadrant Global Pin Name (continued)

| 0.1.0.00       |                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •              | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GABO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GACO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GAC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GBCO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GBC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GDCO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GDC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GEAO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEA1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GEBO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEB1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

| GECO/IOuxwByVz | The output of the different pair will drive the global.                                                                                                                                                                                                                                                                                                  |

| GEC1/IOuxwByVz |                                                                                                                                                                                                                                                                                                                                                          |

|                | GAB1/IOuxwByVz GACO/IOuxwByVz GAC1/IOuxwByVz GBA0/IOuxwByVz GBA1/IOuxwByVz GBB0/IOuxwByVz GBB1/IOuxwByVz GBC1/IOuxwByVz GBC1/IOuxwByVz GDA0/IOuxwByVz GDA1/IOuxwByVz GDB1/IOuxwByVz GDB1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GDC1/IOuxwByVz GEA0/IOuxwByVz GEA0/IOuxwByVz GEA0/IOuxwByVz GEA1/IOuxwByVz GEA1/IOuxwByVz GEB1/IOuxwByVz |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

## **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

### I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

Global Resources in Low Power Flash Devices

## External I/O or Local signal as Clock Source

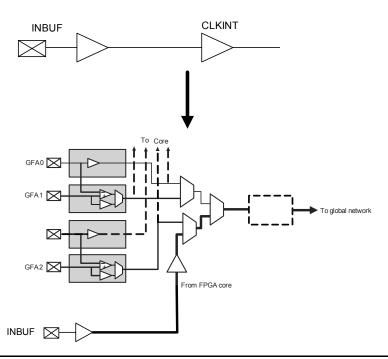

External I/O refers to regular I/O pins are labeled with the I/O convention IOuxwByVz. You can allow the external I/O or internal signal to access the global. To allow the external I/O or internal signal to access the global network, you need to instantiate the CLKINT macro. Refer to Figure 3-4 on page 35 for an example illustration of the connections. Instead of using CLKINT, you can also use PDC to promote signals from external I/O or internal signal to the global network. However, it may cause layout issues because of synthesis logic replication. Refer to the "Global Promotion and Demotion Using PDC" section on page 51 for details.

Figure 3-14 • CLKINT Macro

## **Using Global Macros in Synplicity**

The Synplify<sup>®</sup> synthesis tool automatically inserts global buffers for nets with high fanout during synthesis. By default, Synplicity<sup>®</sup> puts six global macros (CLKBUF or CLKINT) in the netlist, including any global instantiation or PLL macro. Synplify always honors your global macro instantiation. If you have a PLL (only primary output is used) in the design, Synplify adds five more global buffers in the netlist. Synplify uses the following global counting rule to add global macros in the netlist:

- 1. CLKBUF: 1 global buffer

- 2. CLKINT: 1 global buffer

- 3. CLKDLY: 1 global buffer

- 4. PLL: 1 to 3 global buffers

- GLA, GLB, GLC, YB, and YC are counted as 1 buffer.

- GLB or YB is used or both are counted as 1 buffer.

- GLC or YC is used or both are counted as 1 buffer.

### Figure 3-18 • Globals Management GUI in Designer

- 3. Occasionally, the synthesis tool assigns a global macro to clock nets, even though the fanout is significantly less than other asynchronous signals. Select **Demote global nets whose fanout is less than** and enter a reasonable value for fanouts. This frees up some global networks from the signals that have very low fanouts. This can also be done using PDC.

- 4. Use a local clock network for the signals that do not need to go to the whole chip but should have low skew. This local clock network assignment can only be done using PDC.

- 5. Assign the I/O buffer using MVN if you have fixed I/O assignment. As shown in Figure 3-10 on page 45, there are three sets of global pins that have a hardwired connection to each global network. Do not try to put multiple CLKBUF macros in these three sets of global pins. For example, do not assign two CLKBUFs to GAA0x and GAA2x pins.

- 6. You must click **Commit** at the end of MVN assignment. This runs the pre-layout checker and checks the validity of global assignment.

- 7. Always run Compile with the **Keep existing physical constraints** option on. This uses the quadrant clock network assignment in the MVN assignment and checks if you have the desired signals on the global networks.

- 8. Run Layout and check the timing.

# **CCC Support in Microsemi's Flash Devices**

The flash FPGAs listed in Table 4-1 support the CCC feature and the functions described in this document.

Table 4-1 • Flash-Based FPGAs

| Series              | Family*             | Description                                                                                                                                                                                    |  |

|---------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO               | IGLOO               | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |  |

|                     | IGLOOe              | Higher density IGLOO FPGAs with six PLLs and additional I/O standa                                                                                                                             |  |

|                     | IGLOO PLUS          | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |  |

|                     | IGLOO nano          | The industry's lowest-power, smallest-size solution                                                                                                                                            |  |

| ProASIC3            |                     | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |  |

|                     |                     | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |  |

|                     | ProASIC3 nano       | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |  |

|                     | ProASIC3L           | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |  |

|                     | RT ProASIC3         | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |  |

| Military ProASIC3/E |                     | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |  |

|                     | Automotive ProASIC3 | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |  |

| Fusion              | Fusion              | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 4-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

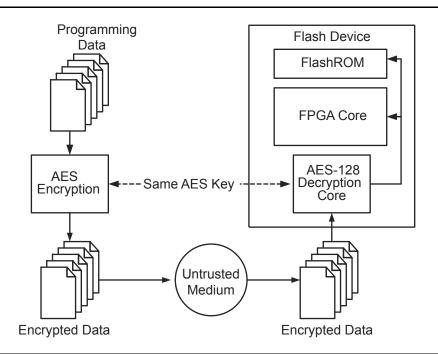

# FlashROM Security

Low power flash devices have an on-chip Advanced Encryption Standard (AES) decryption core, combined with an enhanced version of the Microsemi flash-based lock technology (FlashLock®). Together, they provide unmatched levels of security in a programmable logic device. This security applies to both the FPGA core and FlashROM content. These devices use the 128-bit AES (Rijndael) algorithm to encrypt programming files for secure transmission to the on-chip AES decryption core. The same algorithm is then used to decrypt the programming file. This key size provides approximately  $3.4 \times 10^{38}$  possible 128-bit keys. A computing system that could find a DES key in a second would take approximately 149 trillion years to crack a 128-bit AES key. The 128-bit FlashLock feature in low power flash devices works via a FlashLock security Pass Key mechanism, where the user locks or unlocks the device with a user-defined key. Refer to the "Security in Low Power Flash Devices" section on page 235.

If the device is locked with certain security settings, functions such as device read, write, and erase are disabled. This unique feature helps to protect against invasive and noninvasive attacks. Without the correct Pass Key, access to the FPGA is denied. To gain access to the FPGA, the device first must be unlocked using the correct Pass Key. During programming of the FlashROM or the FPGA core, you can generate the security header programming file, which is used to program the AES key and/or FlashLock Pass Key. The security header programming file can also be generated independently of the FlashROM and FPGA core content. The FlashLock Pass Key is not stored in the FlashROM.

Low power flash devices with AES-based security allow for secure remote field updates over public networks such as the Internet, and ensure that valuable intellectual property (IP) remains out of the hands of IP thieves. Figure 5-5 shows this flow diagram.

Figure 5-5 • Programming FlashROM Using AES

## Pipeline Register

endmodule

endmodule

```

module D_pipeline (Data, Clock, Q);

input [3:0] Data;

input Clock;

output [3:0] Q;

reg [3:0] Q;

always @ (posedge Clock) Q <= Data;</pre>

```

## 4x4 RAM Block (created by SmartGen Core Generator)

```

module mem_block(DI,DO,WADDR,RADDR,WRB,RDB,WCLOCK,RCLOCK);

input [3:0] DI;

output [3:0] DO;

input [1:0] WADDR, RADDR;

input WRB, RDB, WCLOCK, RCLOCK;

wire WEBP, WEAP, VCC, GND;

VCC VCC_1_net(.Y(VCC));

GND GND_1_net(.Y(GND));

INV WEBUBBLEB(.A(WRB), .Y(WEBP));

RAM4K9 RAMBLOCKO(.ADDRA11(GND), .ADDRA10(GND), .ADDRA9(GND), .ADDRA8(GND),

.ADDRA7(GND), .ADDRA6(GND), .ADDRA5(GND), .ADDRA4(GND), .ADDRA3(GND), .ADDRA2(GND),

.ADDRA1(RADDR[1]), .ADDRA0(RADDR[0]), .ADDRB11(GND), .ADDRB10(GND), .ADDRB9(GND),

.ADDRB8(GND), .ADDRB7(GND), .ADDRB6(GND), .ADDRB5(GND), .ADDRB4(GND), .ADDRB3(GND),

.ADDRB2(GND), .ADDRB1(WADDR[1]), .ADDRB0(WADDR[0]), .DINA8(GND), .DINA7(GND),

.DINA6(GND), .DINA5(GND), .DINA4(GND), .DINA3(GND), .DINA2(GND), .DINA1(GND),

.DINAO(GND), .DINB8(GND), .DINB7(GND), .DINB6(GND), .DINB5(GND), .DINB4(GND),

.DINB3(DI[3]), .DINB2(DI[2]), .DINB1(DI[1]), .DINB0(DI[0]), .WIDTHA0(GND),

.WIDTHA1(VCC), .WIDTHB0(GND), .WIDTHB1(VCC), .PIPEA(GND), .PIPEB(GND),

.WMODEA(GND), .WMODEB(GND), .BLKA(WEAP), .BLKB(WEBP), .WENA(VCC), .WENB(GND),

.CLKA(RCLOCK), .CLKB(WCLOCK), .RESET(VCC), .DOUTA8(), .DOUTA7(), .DOUTA6(),

. \verb"DOUTA5()", .DOUTA4()", .DOUTA3(DO[3])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA1(DO[1])", .DOUTA2(DO[2])", .DOUTA2(DO[

.DOUTA0(DO[0]), .DOUTB8(), .DOUTB7(), .DOUTB5(), .DOUTB5(), .DOUTB4(), .DOUTB3(),

.DOUTB2(), .DOUTB1(), .DOUTB0());

INV WEBUBBLEA(.A(RDB), .Y(WEAP));

```

#### ProASIC3 nano FPGA Fabric User's Guide

## I/O Bank Resource Usage

This is an important portion of the report. The user must meet the requirements stated in this table. Figure 8-10 shows the I/O Bank Resource Usage table included in the I/O bank report:

### Figure 8-10 • I/O Bank Resource Usage Table

The example in Figure 8-10 shows that none of the I/O macros is assigned to the bank because more than one VCCI is detected.

## I/O Voltage Usage

The I/O Voltage Usage table provides the number of VREF (E devices only) and  $V_{CCI}$  assignments required in the design. If the user decides to make I/O assignments manually (PDC or MVN), the issues listed in this table must be resolved before proceeding to Layout. As stated earlier, VREF assignments must be made if there are any voltage-referenced I/Os.

Figure 8-11 shows the I/O Voltage Usage table included in the I/O bank report.

### Figure 8-11 • I/O Voltage Usage Table

The table in Figure 8-11 indicates that there are two voltage-referenced I/Os used in the design. Even though both of the voltage-referenced I/O technologies have the same VCCI voltage, their VREF voltages are different. As a result, two I/O banks are needed to assign the VCCI and VREF voltages.

In addition, there are six single-ended I/Os used that have the same VCCI voltage. Since two banks are already assigned with the same VCCI voltage and there are enough unused bonded I/Os in

ProASIC3 nano FPGA Fabric User's Guide

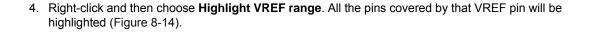

## Figure 8-14 • VREF Range

Using PinEditor or ChipPlanner, VREF pins can also be assigned (Figure 8-15).

### Figure 8-15 • Assigning VREF from PinEditor

To unassign a VREF pin:

- 1. Select the pin to unassign.

- 2. Right-click and choose **Use Pin for VREF.** The check mark next to the command disappears. The VREF pin is now a regular pin.

Resetting the pin may result in unassigning I/O cores, even if they are locked. In this case, a warning message appears so you can cancel the operation.

After you assign the VREF pins, right-click a VREF pin and choose **Highlight VREF Range** to see how many I/Os are covered by that pin. To unhighlight the range, choose **Unhighlight All** from the **Edit** menu.

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                                                   |     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| August 2012             | The notes in Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666).                           |     |

| June 2011               | Figure 8-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.                                 |     |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                                                      | 199 |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                                              |     |

| July 2010               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                                                 | N/A |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 8-1 • Flash-Based FPGAs.                                                                                                                         |     |

|                         | The notes for Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.                             | 187 |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                                          |     |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 8-1 • Flash-Based FPGAs:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six. |     |

| v1.1<br>(March 2008)    | This document was previously part of the I/O Structures in IGLOO and ProASIC3  Devices document. The content was separated and made into a new document.                                                  |     |

|                         | Table 8-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                                                      | 187 |

#### ProASIC3 nano FPGA Fabric User's Guide

### **VHDL**

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_BiDir_HSTL_I_LowEnb is

port(DataR, DataF, CLR, CLK, Trien : in std_logic; QR, QF : out std_logic;

PAD : inout std_logic) ;

end DDR_BiDir_HSTL_I_LowEnb;

architecture DEF_ARCH of DDR_BiDir_HSTL_I_LowEnb is

component INV

port(A : in std_logic := 'U'; Y : out std_logic) ;

end component;

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic);

end component;

component DDR_REG

port(D, CLK, CLR : in std_logic := 'U'; QR, QF : out std_logic);

end component;

component BIBUF_HSTL_I

port(PAD : inout std_logic := 'U'; D, E : in std_logic := 'U'; Y : out std_logic);

end component;

signal TrienAux, D, Q : std_logic ;

begin

Inv_Tri : INV

port map(A => Trien, Y => TrienAux);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

DDR_REG_0_inst : DDR_REG

port map(D => D, CLK => CLK, CLR => CLR, QR => QR, QF => QF);

BIBUF_HSTL_I_0_inst : BIBUF_HSTL_I

port map(PAD => PAD, D => Q, E => TrienAux, Y => D);

end DEF_ARCH;

```

# Programming Support in Flash Devices

The flash FPGAs listed in Table 10-1 support flash in-system programming and the functions described in this document.

#### Table 10-1 • Flash-Based FPGAs

| Series                               | Family*                                                | Description                                                                                                                                                                                                   |  |

|--------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IGLOO                                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze |                                                                                                                                                                                                               |  |

|                                      | IGLOOe                                                 | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                                         |  |

|                                      | IGLOO nano                                             | The industry's lowest-power, smallest-size solution, supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                      |  |

|                                      | IGLOO PLUS                                             | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                                    |  |

| ProASIC3                             | ProASIC3                                               | Low power, high-performance 1.5 V FPGAs                                                                                                                                                                       |  |

|                                      | ProASIC3E                                              | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                                      |  |

|                                      | ProASIC3 nano                                          | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                                           |  |

|                                      | ProASIC3L                                              | ProASIC3 FPGAs supporting 1.2 V to 1.5 V core voltage with Flash*Freeze technology                                                                                                                            |  |

|                                      | RT ProASIC3                                            | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                                   |  |

| Military ProASIC3/EL Military temper |                                                        | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                                         |  |

|                                      | Automotive ProASIC3                                    | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                                          |  |

| SmartFusion                          | SmartFusion                                            | Mixed-signal FPGA integrating FPGA fabric, programmable microcontroller subsystem (MSS), including programmable analog and ARM <sup>®</sup> Cortex™-M3 hard processor and flash memory in a monolithic device |  |

| Fusion                               | Fusion                                                 | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex™-M1 soft processors, and flash memory into a monolithic device                             |  |

| ProASIC                              | ProASIC First generation ProASIC devices               |                                                                                                                                                                                                               |  |

|                                      | ProASIC <sup>PLUS</sup>                                | Second generation ProASIC devices                                                                                                                                                                             |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 10-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

## **Volume Programming Services**

#### **Device Type Supported: Flash and Antifuse**

Once the design is stable for applications with large production volumes, preprogrammed devices can be purchased. Table 10-2 describes the volume programming services.

Table 10-2 • Volume Programming Services

| Programmer                      | Vendor       | Availability            |

|---------------------------------|--------------|-------------------------|

| In-House Programming            | Microsemi    | Contact Microsemi Sales |

| Distributor Programming Centers | Memec Unique | Contact Distribution    |

| Independent Programming Centers | Various      | Contact Vendor          |

Advantages: As programming is outsourced, this solution is easier to implement than creating a substantial in-house programming capability. As programming houses specialize in large-volume programming, this is often the most cost-effective solution.

Limitations: There are some logistical issues with the use of a programming service provider, such as the transfer of programming files and the approval of First Articles. By definition, the programming file must be released to a third-party programming house. Nondisclosure agreements (NDAs) can be signed to help ensure data protection; however, for extremely security-conscious designs, this may not be an option.

- Microsemi In-House Programming

- When purchasing Microsemi devices in volume, IHP can be requested as part of the purchase. If this option is chosen, there is a small cost adder for each device programmed. Each device is marked with a special mark to distinguish it from blank parts. Programming files for the design will be sent to Microsemi. Sample parts with the design programmed, First Articles, will be returned for customer approval. Once approval of First Articles has been received, Microsemi will proceed with programming the remainder of the order. To request Microsemi IHP, contact your local Microsemi representative.

- · Distributor Programming Centers

If purchases are made through a distributor, many distributors will provide programming for their customers. Consult with your preferred distributor about this option.

## Signal Integrity While Using ISP

For ISP of flash devices, customers are expected to follow the board-level guidelines provided on the Microsemi SoC Products Group website. These guidelines are discussed in the datasheets and application notes (refer to the "Related Documents" section of the datasheet for application note links). Customers are also expected to troubleshoot board-level signal integrity issues by measuring voltages and taking oscilloscope plots.

## **Programming Failure Allowances**

Microsemi has strict policies regarding programming failure allowances. Please refer to *Programming and Functional Failure Guidelines* on the Microsemi SoC Products Group website for details.

## **Contacting the Customer Support Group**

Highly skilled engineers staff the Customer Applications Center from 7:00 A.M. to 6:00 P.M., Pacific time, Monday through Friday. You can contact the center by one of the following methods:

#### Electronic Mail

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. Microsemi monitors the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and contact information for efficient processing of your request. The technical support email address is soc tech@microsemi.com.

### Telephone

Our Technical Support Hotline answers all calls. The center retrieves information, such as your name, company name, telephone number, and question. Once this is done, a case number is assigned. Then the center forwards the information to a queue where the first available applications engineer receives the data and returns your call. The phone hours are from 7:00 A.M. to 6:00 P.M., Pacific time, Monday through Friday.

The Customer Applications Center number is (800) 262-1060.

European customers can call +44 (0) 1256 305 600.

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date      | Changes                                                                                                                                                                                                                                                                                                | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010 | FlashPro4 is a replacement for FlashPro3 and has been added to this chapter. FlashPro is no longer available.                                                                                                                                                                                          | N/A  |

|           | The chapter was updated to include SmartFusion devices.                                                                                                                                                                                                                                                | N/A  |

|           | The following were deleted:                                                                                                                                                                                                                                                                            | N/A  |

|           | "Live at Power-Up (LAPU) or Boot PROM" section                                                                                                                                                                                                                                                         |      |

|           | "Design Security" section                                                                                                                                                                                                                                                                              |      |

|           | Table 14-2 • Programming Features for Actel Devices and much of the text in the "Programming Features for Microsemi Devices" section                                                                                                                                                                   |      |

|           | "Programming Flash FPGAs" section                                                                                                                                                                                                                                                                      |      |

|           | "Return Material Authorization (RMA) Policies" section                                                                                                                                                                                                                                                 |      |

|           | The "Device Programmers" section was revised.                                                                                                                                                                                                                                                          | 225  |

|           | The Independent Programming Centers information was removed from the "Volume Programming Services" section.                                                                                                                                                                                            | 226  |

|           | Table 10-3 • Programming Solutions was revised to add FlashPro4 and note that FlashPro is discontinued. A note was added for FlashPro Lite regarding power supply requirements.                                                                                                                        | 227  |

|           | Most items were removed from Table 10-4 • Programming Ordering Codes, including FlashPro3 and FlashPro.                                                                                                                                                                                                | 228  |

|           | The "Programmer Device Support" section was deleted and replaced with a reference to the Microsemi SoC Products Group website for the latest information.                                                                                                                                              | 228  |

|           | The "Certified Programming Solutions" section was revised to add FlashPro4 and remove Silicon Sculptor I and Silicon Sculptor 6X. Reference to <i>Programming and Functional Failure Guidelines</i> was added.                                                                                         | 228  |

|           | The file type *.pdb was added to the "Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)" section.                                                                                                                                                        | 229  |

|           | Instructions on cleaning and careful insertion were added to the "Perform Routine Hardware Self-Diagnostic Test" section. Information was added regarding testing Silicon Sculptor programmers with an adapter module installed before every programming session verifying their calibration annually. | 229  |

|           | The "Signal Integrity While Using ISP" section is new.                                                                                                                                                                                                                                                 | 230  |

|           | The "Programming Failure Allowances" section was revised.                                                                                                                                                                                                                                              | 230  |

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 13-1 support the voltage switching circuit feature and the functions described in this document.

Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series                                                                                                                            | Family*              | Description                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------|--|

| IGL00                                                                                                                             | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |  |

|                                                                                                                                   | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |  |

|                                                                                                                                   | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |  |

|                                                                                                                                   | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |  |

| ProASIC3 ProASIC3L ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*F  RT ProASIC3 Radiation-tolerant RT3PE600L and RT3PE3000L |                      | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |  |

|                                                                                                                                   |                      | Radiation-tolerant RT3PE600L and RT3PE3000L                           |  |

|                                                                                                                                   | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |  |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# 15 – Boundary Scan in Low Power Flash Devices

# **Boundary Scan**

Low power flash devices are compatible with IEEE Standard 1149.1, which defines a hardware architecture and the set of mechanisms for boundary scan testing. JTAG operations are used during boundary scan testing.

The basic boundary scan logic circuit is composed of the TAP controller, test data registers, and instruction register (Figure 15-2 on page 294).

Low power flash devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (LSB, ID number, part number, and version). The boundary scan register observes and controls the state of each I/O pin. Each I/O cell has three boundary scan register cells, each with serial-in, serial-out, parallel-in, and parallel-out pins.

## **TAP Controller State Machine**

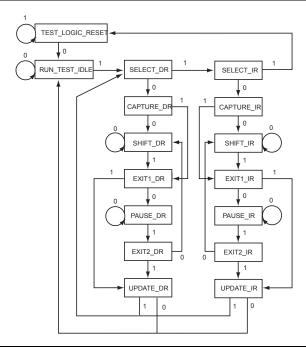

The TAP controller is a 4-bit state machine (16 states) that operates as shown in Figure 15-1.

The 1s and 0s represent the values that must be present on TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain HIGH for five TCK cycles. The TRST pin can also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

Figure 15-1 • TAP Controller State Machine

## **Fine Tuning**

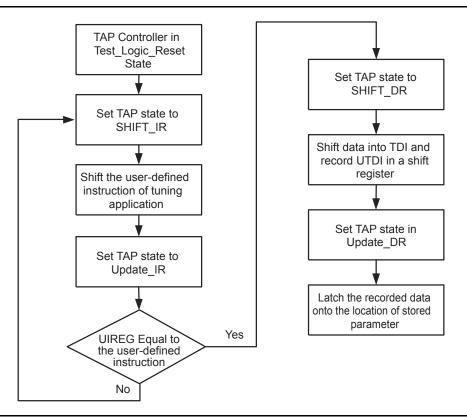

In some applications, design constants or parameters need to be modified after programming the original design. The tuning process can be done using the UJTAG tile without reprogramming the device with new values. If the parameters or constants of a design are stored in distributed registers or embedded SRAM blocks, the new values can be shifted onto the JTAG TAP Controller pins, replacing the old values. The UJTAG tile is used as the "bridge" for data transfer between the JTAG pins and the FPGA VersaTiles or SRAM logic. Figure 16-5 shows a flow chart example for fine-tuning application steps using the UJTAG tile.

In Figure 16-5, the TMS signal sets the TAP Controller state machine to the appropriate states. The flow mainly consists of two steps: a) shifting the defined instruction and b) shifting the new data. If the target parameter is constantly used in the design, the new data can be shifted into a temporary shift register from UTDI. The UDRSH output of UJTAG can be used as a shift-enable signal, and UDRCK is the shift clock to the shift register. Once the shift process is completed and the TAP Controller state is moved to the Update\_DR state, the UDRUPD output of the UJTAG can latch the new parameter value from the temporary register into a permanent location. This avoids any interruption or malfunctioning during the serial shift of the new value.

Figure 16-5 • Flow Chart Example of Fine-Tuning an Application Using UJTAG

Figure 17-3 • I/O State when VCCI Is Powered before VCC

## **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up—to—functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 17-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 17-2 on page 311 and Figure 17-3.

Table 17-2 • Power-Up Functional Activation Levels for VCC and VCCI

| Device                                                                                                | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.2 V*                          | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 17-4 on page 313 and Figure 17-5 on page 314 for more information.