Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

EXF

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 18432                                                                    |

| Number of I/O                  | 71                                                                       |

| Number of Gates                | 60000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                        |

| Package / Case                 | 100-TQFP                                                                 |

| Supplier Device Package        | 100-VQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-2vq100 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# *Microsemi*.

Table of Contents

| 17 | Power-Up/-Down Behavior of Low Power Flash Devices |     |

|----|----------------------------------------------------|-----|

|    | Introduction                                       | 307 |

|    | Flash Devices Support Power-Up Behavior            | 308 |

|    | Power-Up/-Down Sequence and Transient Current      | 309 |

|    | I/O Behavior at Power-Up/-Down                     | 311 |

|    | Cold-Sparing                                       | 316 |

|    | Hot-Swapping                                       | 317 |

|    | Conclusion                                         | 317 |

|    | Related Documents                                  | 318 |

|    | List of Changes                                    | 318 |

|    |                                                    |     |

| А  | Summary of Changes                                 | 319 |

|    | History of Revision to Chapters                    | 319 |

|    |                                                    |     |

| В  | Product Support                                    | 321 |

|    | Customer Service                                   | 321 |

|    | Customer Technical Support Center                  | 321 |

|    | Technical Support                                  | 321 |

|    | Website                                            | 321 |

|    | Contacting the Customer Technical Support Center   | 321 |

|    | ITAR Technical Support                             | 322 |

|    |                                                    |     |

|    | Index                                              | 323 |

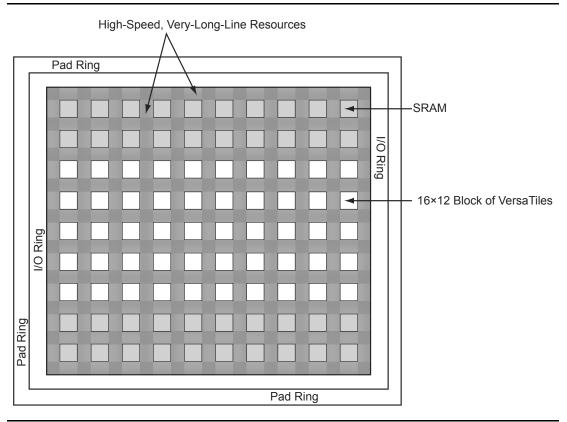

ProASIC3 nano FPGA Fabric User's Guide

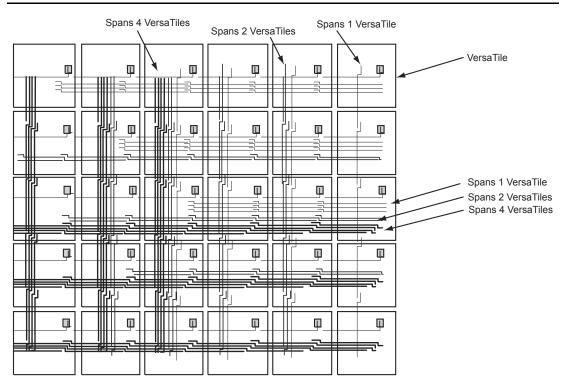

Figure 1-11 • Efficient Long-Line Resources

Figure 1-12 • Very-Long-Line Resources

Global Resources in Low Power Flash Devices

| Differential I/O Pairs | GAAO/IOuxwByVz | The output of the different pair will drive the global. |

|------------------------|----------------|---------------------------------------------------------|

|                        | ,              |                                                         |

|                        | GAA1/IOuxwByVz |                                                         |

|                        | GABO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAB1/IOuxwByVz |                                                         |

|                        | GACO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAC1/IOuxwByVz |                                                         |

|                        | GBAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBA1/IOuxwByVz |                                                         |

|                        | GBBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBB1/IOuxwByVz |                                                         |

|                        | GBCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBC1/IOuxwByVz |                                                         |

|                        | GDAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDA1/IOuxwByVz |                                                         |

|                        | GDBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDB1/IOuxwByVz |                                                         |

|                        | GDCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDC1/IOuxwByVz |                                                         |

|                        | GEAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEA1/IOuxwByVz |                                                         |

|                        | GEBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEB1/IOuxwByVz |                                                         |

|                        | GECO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEC1/IOuxwByVz |                                                         |

#### Table 3-3 • Quadrant Global Pin Name (continued)

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

### **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

### I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

Global Resources in Low Power Flash Devices

### **Global Macro and Placement Selections**

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a global / quadrant global network. For 60K gate devices and above, if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen, the first and second inputs are considered as paired, and the third input is paired with a regular I/O. The user then has the choice of selecting one of the two sets to be used as the global input source. There is also the option to allow an internal clock signal to feed the global network. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

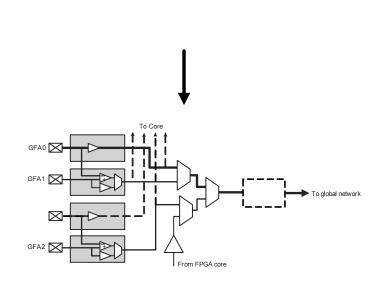

#### Hardwired I/O Clock Source

Hardwired I/O refers to global input pins that are hardwired to the multiplexer tree, which directly accesses the global network. These global input pins have designated pin locations and are indicated with the I/O naming convention Gmn (m refers to any one of the positions where the global buffers is available, and n refers to any one of the three global input MUXes and the pin number of the associated global location, m). Choosing this option provides the benefit of directly connecting to the global buffers, which provides less delay. See Figure 3-11 for an example illustration of the connections, shown in red. If a CLKBUF macro is initiated, the clock input can be placed at one of nine dedicated global input pin locations: GmA0, GmA1, GmA2, GmB0, GmB1, GmB2, GmC0, GmC1, or GmC2. Note that the placement of the global will determine whether you are using chip global or quadrant global. For example, if the CLKBIF is placed in one of the GF pin locations, it will use the chip global network; if the CLKBIF is placed in one of the GA pin locations, it will use the chip global network. This is shown in Figure 3-12 on page 49 and Figure 3-13 on page 49.

Figure 3-11 • CLKBUF Macro

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### CLKDLY Macro Usage

When a CLKDLY macro is used in a CCC location, the programmable delay element is used to allow the clock delays to go to the global network. In addition, the user can bypass the PLL in a CCC location integrated with a PLL, but use the programmable delay that is associated with the global network by instantiating the CLKDLY macro. The same is true when using programmable delay elements in a CCC location with no PLLs (the user needs to instantiate the CLKDLY macro). There is no difference between the programmable delay elements used for the PLL and the CLKDLY macro. The CCC will be configured to use the programmable delay elements in accordance with the macro instantiated by the user.

As an example, if the PLL is not used in a particular CCC location, the designer is free to specify up to three CLKDLY macros in the CCC, each of which can have its own input frequency and delay adjustment options. If the PLL core is used, assuming output to only one global clock network, the other two global clock networks are free to be used by either connecting directly from the global inputs or connecting from one or two CLKDLY macros for programmable delay.

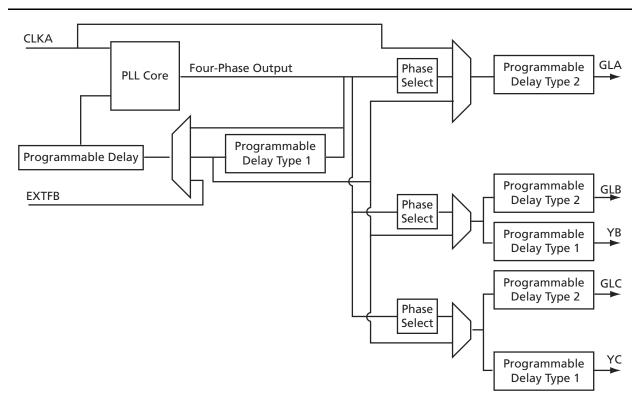

The programmable delay elements are shown in the block diagram of the PLL block shown in Figure 4-6 on page 71. Note that any CCC locations with no PLL present contain only the programmable delay blocks going to the global networks (labeled "Programmable Delay Type 2"). Refer to the "Clock Delay Adjustment" section on page 86 for a description of the programmable delay types used for the PLL. Also refer to Table 4-14 on page 94 for Programmable Delay Type 1 step delay values, and Table 4-15 on page 94 for Programmable Delay Type 2 step delay values. CCC locations with a PLL present can be configured to utilize only the programmable delay blocks (Programmable Delay Type 2) going to the global networks A, B, and C.

Global network A can be configured to use only the programmable delay element (bypassing the PLL) if the PLL is not used in the design. Figure 4-6 on page 71 shows a block diagram of the PLL, where the programmable delay elements are used for the global networks (Programmable Delay Type 2).

SmartGen also allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB, and YC). SmartGen allows the user to select the input clock source. SmartGen automatically instantiates the special macro, PLLINT, when needed.

Note: Clock divider and clock multiplier blocks are not shown in this figure or in SmartGen. They are automatically configured based on the user's required frequencies.

Figure 4-6 • CCC with PLL Block

# **Global Input Selections**

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a CCC functional block or to a global / quadrant global network. Figure 4-7 on page 72 and Figure 4-8 on page 72 show the detailed architecture of each global input structure for 30 k gate devices and below, as well as 60 k gate devices and above, respectively. For 60 k gate devices and above (Figure 4-7 on page 72), if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen (not applicable for IGLOO nano and ProASIC3 nano devices), the first and second inputs are considered as paired, and the third input is paired with a regular I/O.

The user then has the choice of selecting one of the two sets to be used as the clock input source to the CCC functional block. There is also the option to allow an internal clock signal to feed the global network or the CCC functional block. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

| Config.<br>Bits | Signal              | Name                             | Description                                                                                                                                              |

|-----------------|---------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 83              | RXCSEL <sup>1</sup> | CLKC input selection             | Select the CLKC input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                           |

| 82              | RXBSEL <sup>1</sup> | CLKB input selection             | Select the CLKB input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                           |

| 81              | RXASEL <sup>1</sup> | CLKA input selection             | Select the CLKA input clock source between RC oscillator and crystal oscillator (refer to Table 4-16 on page 94). <sup>2</sup>                           |

| 80              | RESETEN             | Reset Enable                     | Enables (active high) the synchronization of<br>PLL output dividers after dynamic<br>reconfiguration (SUPDATE). The Reset<br>Enable signal is READ-ONLY. |

| 79              | DYNCSEL             | Clock Input C Dynamic<br>Select  | Configures clock input C to be sent to GLC for dynamic control. <sup>2</sup>                                                                             |

| 78              | DYNBSEL             | Clock Input B Dynamic<br>Select  | Configures clock input B to be sent to GLB for dynamic control. <sup>2</sup>                                                                             |

| 77              | DYNASEL             | Clock Input A Dynamic<br>Select  | Configures clock input A for dynamic PLL configuration. <sup>2</sup>                                                                                     |

| <76:74>         | VCOSEL[2:0]         | VCO Gear Control                 | Three-bit VCO Gear Control for four frequency ranges (refer to Table 4-19 on page 95 and Table 4-20 on page 95).                                         |

| 73              | STATCSEL            | MUX Select on Input C            | MUX selection for clock input C <sup>2</sup>                                                                                                             |

| 72              | STATBSEL            | MUX Select on Input B            | MUX selection for clock input B <sup>2</sup>                                                                                                             |

| 71              | STATASEL            | MUX Select on Input A            | MUX selection for clock input A <sup>2</sup>                                                                                                             |

| <70:66>         | DLYC[4:0]           | YC Output Delay                  | Sets the output delay value for YC.                                                                                                                      |

| <65:61>         | DLYB[4:0]           | YB Output Delay                  | Sets the output delay value for YB.                                                                                                                      |

| <60:56>         | DLYGLC[4:0]         | GLC Output Delay                 | Sets the output delay value for GLC.                                                                                                                     |

| <55:51>         | DLYGLB[4:0]         | GLB Output Delay                 | Sets the output delay value for GLB.                                                                                                                     |

| <50:46>         | DLYGLA[4:0]         | Primary Output Delay             | Primary GLA output delay                                                                                                                                 |

| 45              | XDLYSEL             | System Delay Select              | When selected, inserts System Delay in the feedback path in Figure 4-20 on page 85.                                                                      |

| <44:40>         | FBDLY[4:0]          | Feedback Delay                   | Sets the feedback delay value for the feedback element in Figure 4-20 on page 85.                                                                        |

| <39:38>         | FBSEL[1:0]          | Primary Feedback Delay<br>Select | Controls the feedback MUX: no delay, include programmable delay element, or use external feedback.                                                       |

| <37:35>         | OCMUX[2:0]          | Secondary 2 Output<br>Select     | Selects from the VCO's four phase outputs for GLC/YC.                                                                                                    |

| <34:32>         | OBMUX[2:0]          | Secondary 1 Output<br>Select     | Selects from the VCO's four phase outputs for GLB/YB.                                                                                                    |

#### Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

Notes:

1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

This value depends on the input clock source, so Layout must complete before these bits can be set. After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools > Report > CCC\_Configuration. The report contains the appropriate settings for these bits. Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

| Config.<br>Bits | Signal      | Name                          | Description                                                                                                                                                    |

|-----------------|-------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <31:29>         | OAMUX[2:0]  | GLA Output Select             | Selects from the VCO's four phase outputs for GLA.                                                                                                             |

| <28:24>         | OCDIV[4:0]  | Secondary 2 Output<br>Divider | Sets the divider value for the GLC/YC outputs.<br>Also known as divider <i>w</i> in Figure 4-20 on<br>page 85. The divider value will be OCDIV[4:0]<br>+ 1.    |

| <23:19>         | OBDIV[4:0]  | Secondary 1 Output<br>Divider | Sets the divider value for the GLB/YB outputs.<br>Also known as divider $v$ in Figure 4-20 on<br>page 85. The divider value will be OBDIV[4:0]<br>+ 1.         |

| <18:14>         | OADIV[4:0]  | Primary Output Divider        | Sets the divider value for the GLA output. Also known as divider $u$ in Figure 4-20 on page 85. The divider value will be OADIV[4:0] + 1.                      |

| <13:7>          | FBDIV[6:0]  | Feedback Divider              | Sets the divider value for the PLL core<br>feedback. Also known as divider <i>m</i> in<br>Figure 4-20 on page 85. The divider value will<br>be FBDIV[6:0] + 1. |

| <6:0>           | FINDIV[6:0] | Input Divider                 | Input Clock Divider (/n). Sets the divider value for the input delay on CLKA. The divider value will be FINDIV[6:0] + 1.                                       |

#### Table 4-8 • Configuration Bit Descriptions for the CCC Blocks (continued)

Notes:

1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

This value depends on the input clock source, so Layout must complete before these bits can be set. After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools > Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

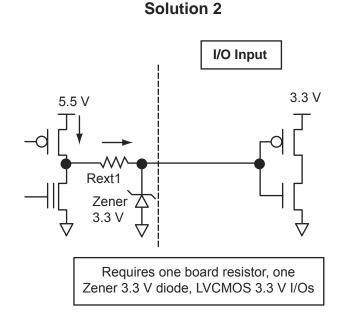

#### Solution 2

This solution requires one board resistor and one Zener 3.3 V diode, as demonstrated in Figure 7-6.

### Figure 7-6 • Solution 2

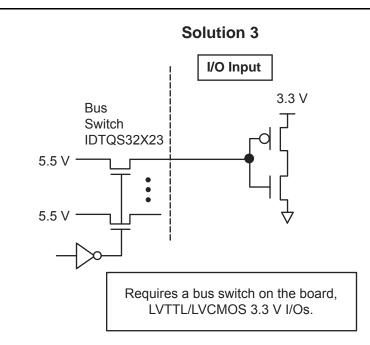

#### Solution 3

This solution requires a bus switch on the board, as demonstrated in Figure 7-7.

#### Figure 7-7 • Solution 3

# Microsemi

I/O Software Control in Low Power Flash Devices

# **List of Changes**

The following table lists critical changes that were made in each revision of the document.

| Date                    | Changes                                                                                                                                                                         | Page |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| August 2012             | The notes in Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to clarify which device families support programmable input delay (SAR 39666). | 187  |

| June 2011               | Figure 8-2 • SmartGen Catalog was updated (SAR 24310). Figure 8-3 • Expanded I/O Section and the step associated with it were deleted to reflect changes in the software.       | 188  |

|                         | The following rule was added to the "VREF Rules for the Implementation of Voltage-Referenced I/O Standards" section:                                                            | 199  |

|                         | Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os (SAR 24310).                    |      |

| July 2010               | Notes were added where appropriate to point out that IGLOO nano and ProASIC3 nano devices do not support differential inputs (SAR 21449).                                       | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 8-1 • Flash-Based FPGAs.                                                                                               | 186  |

|                         | The notes for Table 8-2 • Designer State (resulting from I/O attribute modification) were revised to indicate that skew control and input delay do not apply to nano devices.   | 187  |

| v1.3<br>(October 2008)  | The "Flash FPGAs I/O Support" section was revised to include new families and make the information more concise.                                                                | 186  |

| v1.2<br>(June 2008)     | The following changes were made to the family descriptions in Table 8-1 • Flash-<br>Based FPGAs:                                                                                | 186  |

|                         | ProASIC3L was updated to include 1.5 V.                                                                                                                                         |      |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                  |      |

| v1.1<br>(March 2008)    | This document was previously part of the <i>I/O Structures in IGLOO and ProASIC3 Devices</i> document. The content was separated and made into a new document.                  | N/A  |

|                         | Table 8-2 • Designer State (resulting from I/O attribute modification) was updated to include note 2 for IGLOO PLUS.                                                            | 187  |

DDR for Microsemi's Low Power Flash Devices

```

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

TRIBUFF_F_8U_0_inst : TRIBUFF_F_8U

port map(D => Q, E => TrienAux, PAD => PAD);

```

end DEF\_ARCH;

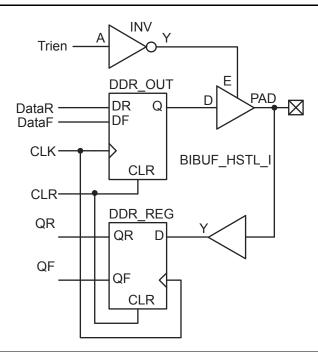

### **DDR Bidirectional Buffer**

Figure 9-8 • DDR Bidirectional Buffer, LOW Output Enable (HSTL Class II)

#### Verilog

module DDR\_BiDir\_HSTL\_I\_LowEnb(DataR,DataF,CLR,CLK,Trien,QR,QF,PAD);

```

input DataR, DataF, CLR, CLK, Trien;

output QR, QF;

inout PAD;

wire TrienAux, D, Q;

INV Inv_Tri(.A(Trien), .Y(TrienAux));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

DDR_REG DDR_REG_0_inst(.D(D),.CLK(CLK),.CLR(CLR),.QR(QR),.QF(QF));

BIBUF_HSTL_I BIBUF_HSTL_I_0_inst(.PAD(PAD),.D(Q),.E(TrienAux),.Y(D));

```

endmodule

Security in Low Power Flash Devices

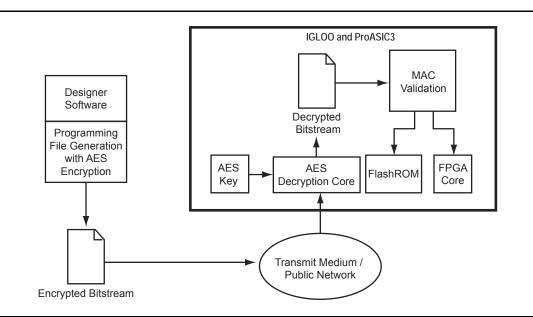

The AES key is securely stored on-chip in dedicated low power flash device flash memory and cannot be read out. In the first step, the AES key is generated and programmed into the device (for example, at a secure or trusted programming site). The Microsemi Designer software tool provides AES key generation capability. After the key has been programmed into the device, the device will only correctly decrypt programming files that have been encrypted with the same key. If the individual programming file content is incorrect, a Message Authentication Control (MAC) mechanism inside the device will fail in authenticating the programming file. In other words, when an encrypted programming file is being loaded into a device that has a different programmed AES key, the MAC will prevent this incorrect data from being loaded, preventing possible device damage. See Figure 11-3 on page 238 and Figure 11-4 on page 240 for graphical representations of this process.

It is important to note that the user decides what level of protection will be implemented for the device. When AES protection is desired, the FlashLock Pass Key must be set. The AES key is a content protection mechanism, whereas the FlashLock Pass Key is a device protection mechanism. When the AES key is programmed into the device, the device still needs the Pass Key to protect the FPGA and FlashROM contents and the security settings, including the AES key. Using the FlashLock Pass Key prevents modification of the design contents by means of simply programming the device with a different AES key.

#### AES Decryption and MAC Authentication

Low power flash devices have a built-in 128-bit AES decryption core, which decrypts the encrypted programming file and performs a MAC check that authenticates the file prior to programming.

MAC authenticates the entire programming data stream. After AES decryption, the MAC checks the data to make sure it is valid programming data for the device. This can be done while the device is still operating. If the MAC validates the file, the device will be erased and programmed. If the MAC fails to validate, then the device will continue to operate uninterrupted.

This will ensure the following:

- · Correct decryption of the encrypted programming file

- Prevention of erroneous or corrupted data being programmed during the programming file transfer

- Correct bitstream passed to the device for decryption

Figure 11-4 • Example Application Scenario Using AES in IGLOO and ProASIC3 Devices

1. National Institute of Standards and Technology, "ADVANCED ENCRYPTION STANDARD (AES) Questions and Answers," 28 January 2002 (10 January 2005). See http://csrc.nist.gov/archive/aes/index1.html for more information.

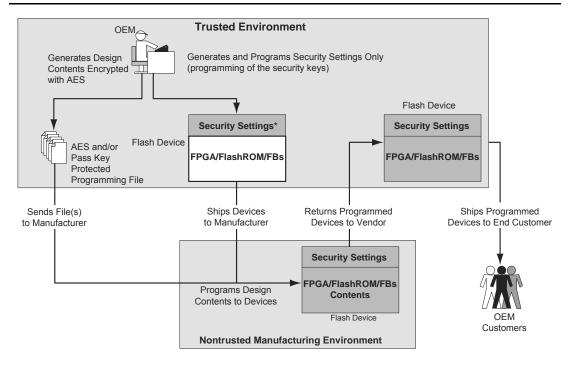

### Application 1: Trusted Environment

As illustrated in Figure 11-7, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi In-House Programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user generates a STAPL programming file from the Designer software in plaintext format, containing information on the entire design or the portion of the design to be programmed. The user can choose to employ the FlashLock Pass Key feature with the design. Once the design is programming is needed, the user can consider permanently securing the IGLOO and ProASIC3 device, as discussed in the "Permanent FlashLock" section on page 241.

### **Application 2: Nontrusted Environment—Unsecured Location**

Often, programming of devices is not performed in the same location as actual design implementation, to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, FlashROM, and (for Fusion) FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 11-7 shows a more detailed flow for this application.

Notes:

1. Programmed portion indicated with dark gray.

2. Programming of FBs applies to Fusion only.

Figure 11-7 • Application 2: Device Programming in a Nontrusted Environment

# **Generating Programming Files**

### Generation of the Programming File in a Trusted Environment— Application 1

As discussed in the "Application 1: Trusted Environment" section on page 243, in a trusted environment, the user can choose to program the device with plaintext bitstream content. It is possible to use plaintext for programming even when the FlashLock Pass Key option has been selected. In this application, it is not necessary to employ AES encryption protection. For AES encryption settings, refer to the next sections.

The generated programming file will include the security setting (if selected) and the plaintext programming file content for the FPGA array, FlashROM, and/or FBs. These options are indicated in Table 11-2 and Table 11-3.

| Security Protection   | FlashROM Only | FPGA Core Only | Both FlashROM<br>and FPGA |

|-----------------------|---------------|----------------|---------------------------|

| No AES / no FlashLock | 1             | ✓              | ✓                         |

| FlashLock only        | 1             | ✓              | ✓                         |

| AES and FlashLock     | _             | _              | _                         |

#### Table 11-2 • IGLOO and ProASIC3 Plaintext Security Options, No AES

#### Table 11-3 • Fusion Plaintext Security Options

| Security Protection   | FlashROM Only | FPGA Core Only | FB Core Only | All |

|-----------------------|---------------|----------------|--------------|-----|

| No AES / no FlashLock | ✓             | 1              | 1            | 1   |

| FlashLock             | ✓             | 1              | 1            | 1   |

| AES and FlashLock     | _             | _              | _            | _   |

Note: For all instructions, the programming of Flash Blocks refers to Fusion only.

For this scenario, generate the programming file as follows:

1. Select the **Silicon features to be programmed** (Security Settings, FPGA Array, FlashROM, Flash Memory Blocks), as shown in Figure 11-10 on page 248 and Figure 11-11 on page 248. Click **Next**.

If **Security Settings** is selected (i.e., the FlashLock security Pass Key feature), an additional dialog will be displayed to prompt you to select the security level setting. If no security setting is selected, you will be directed to Step 3.

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# Microsemi's Flash Families Support Voltage Switching Circuit

The flash FPGAs listed in Table 13-1 support the voltage switching circuit feature and the functions described in this document.

Table 13-1 • Flash-Based FPGAs Supporting Voltage Switching Circuit

| Series                 | Family <sup>*</sup>  | Description                                                           |

|------------------------|----------------------|-----------------------------------------------------------------------|

| IGLOO                  | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology     |

|                        | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards |

|                        | IGLOO nano           | The industry's lowest-power, smallest-size solution                   |

|                        | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                            |

| ProASIC3 ProASIC3L Pro |                      | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology |

|                        | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                           |

|                        | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 13-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio.*

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# **Circuit Verification**

The power switching circuit recommended above is implemented on Microsemi's Icicle board (Figure 13-2). On the Icicle board, VJTAGENB is used to control the N-Channel Digital FET; however, this circuit was modified to use TRST instead of VJTAGENB in this application. There are three important aspects of this circuit that were verified:

- 1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH

- 2. VCC rises to 1.5 V before programming begins.

- 3. VCC switches from 1.5 V to 1.2 V when TRST is LOW.

### **Verification Steps**

1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH.

#### Figure 13-2 • Core Voltage on the IGLOO AGL125-QNG132 Device

In the oscilloscope plots (Figure 13-2), the TRST from FlashPro3 and the VCC core voltage of the IGLOO device are labeled. This plot shows the rise characteristic of the TRST signal from FlashPro3. Once the TRST signal is asserted HIGH, the LTC3025 shown in Figure 13-1 on page 277 senses the increase in voltage and changes the output from 1.2 V to 1.5 V. It takes the circuit approximately 100  $\mu$ s to respond to TRST and change the voltage to 1.5 V on the VCC core.

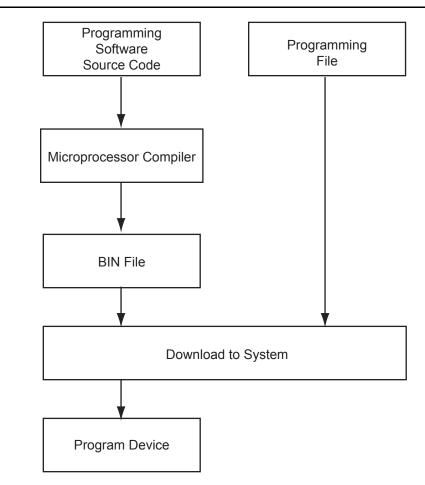

Microprocessor Programming of Microsemi's Low Power Flash Devices

Figure 14-3 • MCU FPGA Programming Model

### FlashROM

Microsemi low power flash devices have 1 kbit of user-accessible, nonvolatile, FlashROM on-chip. This nonvolatile FlashROM can be programmed along with the core or on its own using the standard IEEE 1532 JTAG programming interface.

The FlashROM is architected as eight pages of 128 bits. Each page can be individually programmed (erased and written). Additionally, on-chip AES security decryption can be used selectively to load data securely into the FlashROM (e.g., over public or private networks, such as the Internet). Refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 117.

# Microsemi

UJTAG Applications in Microsemi's Low Power Flash Devices

# Conclusion

Microsemi low power flash FPGAs offer many unique advantages, such as security, nonvolatility, reprogrammablity, and low power—all in a single chip. In addition, Fusion, IGLOO, and ProASIC3 devices provide access to the JTAG port from core VersaTiles while the device is in normal operating mode. A wide range of available user-defined JTAG opcodes allows users to implement various types of applications, exploiting this feature of these devices. The connection between the JTAG port and core tiles is implemented through an embedded and hardwired UJTAG tile. A UJTAG tile can be instantiated in designs using the UJTAG library cell. This document presents multiple examples of UJTAG applications, such as dynamic reconfiguration, silicon test and debug, fine-tuning of the design, and RAM initialization. Each of these applications offers many useful advantages.

# **Related Documents**

### **Application Notes**

RAM Initialization and ROM Emulation in ProASIC<sup>PLUS</sup> Devices http://www.microsemi.com/soc/documents/APA RAM Initd AN.pdf

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date                    | Changes                                                                                                                                                           | Page |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| December 2011           | Information on the drive strength and slew rate of TDO pins was added to the "Silicon Testing and Debugging" section (SAR 31749).                                 | 304  |

| July 2010               | This chapter is no longer published separately with its own part number and version but is now part of several FPGA fabric user's guides.                         | N/A  |

| v1.4<br>(December 2008) | IGLOO nano and ProASIC3 nano devices were added to Table 16-1 • Flash-Based FPGAs.                                                                                | 298  |

| v1.3<br>(October 2008)  | The "UJTAG Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                     | 298  |

|                         | The title of Table 16-3 • Configuration Bits of Fusion, IGLOO, and ProASIC3 CCC Blocks was revised to include Fusion.                                             | 302  |

| v1.2<br>(June 2008)     | <ul><li>The following changes were made to the family descriptions in Table 16-1 • Flash-Based FPGAs:</li><li>• ProASIC3L was updated to include 1.5 V.</li></ul> | 298  |

|                         | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                    |      |

| v1.1<br>(March 2008)    | The chapter was updated to include the IGLOO PLUS family and information regarding 15 k gate devices.                                                             | N/A  |

|                         | The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                       | 298  |

# **B** – **Product Support**

Microsemi SoC Products Group backs its products with various support services, including Customer Service, Customer Technical Support Center, a website, electronic mail, and worldwide sales offices. This appendix contains information about contacting Microsemi SoC Products Group and using these support services.

# **Customer Service**

Contact Customer Service for non-technical product support, such as product pricing, product upgrades, update information, order status, and authorization.

From North America, call 800.262.1060 From the rest of the world, call 650.318.4460 Fax, from anywhere in the world, 650.318.8044

# **Customer Technical Support Center**

Microsemi SoC Products Group staffs its Customer Technical Support Center with highly skilled engineers who can help answer your hardware, software, and design questions about Microsemi SoC Products. The Customer Technical Support Center spends a great deal of time creating application notes, answers to common design cycle questions, documentation of known issues, and various FAQs. So, before you contact us, please visit our online resources. It is very likely we have already answered your questions.

# **Technical Support**

Visit the Customer Support website (www.microsemi.com/soc/support/search/default.aspx) for more information and support. Many answers available on the searchable web resource include diagrams, illustrations, and links to other resources on the website.

# Website

You can browse a variety of technical and non-technical information on the SoC home page, at www.microsemi.com/soc.

# **Contacting the Customer Technical Support Center**

Highly skilled engineers staff the Technical Support Center. The Technical Support Center can be contacted by email or through the Microsemi SoC Products Group website.

### Email

You can communicate your technical questions to our email address and receive answers back by email, fax, or phone. Also, if you have design problems, you can email your design files to receive assistance. We constantly monitor the email account throughout the day. When sending your request to us, please be sure to include your full name, company name, and your contact information for efficient processing of your request.

The technical support email address is soc\_tech@microsemi.com.