Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 18432                                                                    |

| Number of I/O                  | 71                                                                       |

| Number of Gates                | 60000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                        |

| Package / Case                 | 100-TQFP                                                                 |

| Supplier Device Package        | 100-VQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn060-vqg100 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|   | Introduction                                                                  | 7    |

|---|-------------------------------------------------------------------------------|------|

|   | Contents                                                                      | 7    |

|   | Revision History                                                              | 7    |

|   | Related Information                                                           | 7    |

|   |                                                                               |      |

| 1 | FPGA Array Architecture in Low Power Flash Devices                            |      |

|   | Device Architecture                                                           |      |

|   | FPGA Array Architecture Support                                               |      |

|   | Device Overview                                                               |      |

|   | Related Documents                                                             |      |

|   | List of Changes                                                               | 20   |

| 2 | Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs                         | . 21 |

|   |                                                                               |      |

|   | Power Consumption Overview                                                    |      |

|   | Static (Idle) Mode                                                            |      |

|   | User Low Static (Idle) Mode                                                   |      |

|   | Sleep Mode                                                                    | 25   |

|   | Shutdown Mode                                                                 | 27   |

|   | Conclusion                                                                    | 28   |

|   | Related Documents                                                             | 28   |

|   | List of Changes                                                               | 29   |

| ~ | Olahal Daaraa in Laa Daaraa Flack Daariyaa                                    | 0.4  |

| 3 | Global Resources in Low Power Flash Devices.                                  |      |

|   | Introduction                                                                  |      |

|   | Global Resource Support in Flash-Based Devices                                |      |

|   | VersaNet Global Network Distribution                                          |      |

|   | Chip and Quadrant Global I/Os                                                 |      |

|   | Spine Architecture                                                            |      |

|   | Using Clock Aggregation                                                       |      |

|   | Design Recommendations                                                        |      |

|   |                                                                               |      |

|   | Related Documents                                                             |      |

|   | List of Changes                                                               |      |

|   |                                                                               |      |

| 4 | Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs | . 61 |

|   | Introduction                                                                  | 61   |

|   | Overview of Clock Conditioning Circuitry                                      | 61   |

|   | CCC Support in Microsemi's Flash Devices                                      |      |

|   | Global Buffers with No Programmable Delays                                    |      |

|   | Global Buffer with Programmable Delay                                         |      |

|   | Global Buffers with PLL Function                                              | 67   |

|   |                                                                               |      |

|   | Global Input Selections                                                       |      |

ProASIC3 nano FPGA Fabric User's Guide

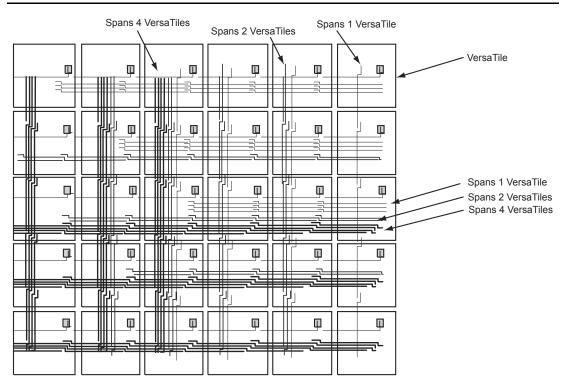

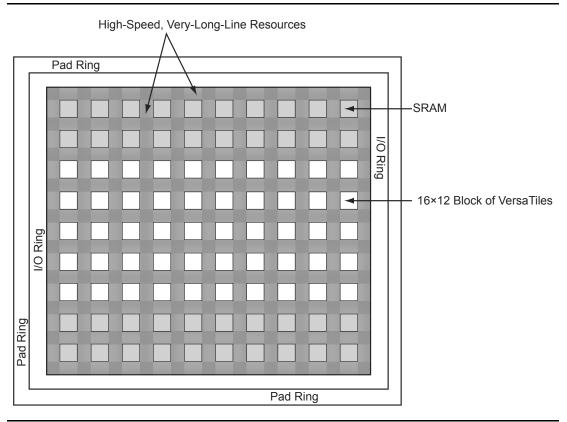

Figure 1-11 • Efficient Long-Line Resources

Figure 1-12 • Very-Long-Line Resources

Global Resources in Low Power Flash Devices

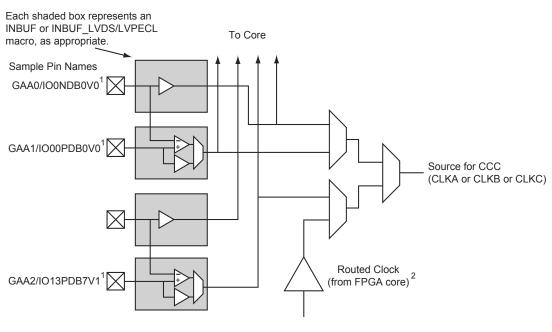

Figure 3-5 shows more detailed global input connections. It shows the global input pins connection to the northwest quadrant global networks. Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Figure 3-5 • Global I/O Overview

Global Resources in Low Power Flash Devices

| Differential I/O Pairs | GAAO/IOuxwByVz | The output of the different pair will drive the global. |

|------------------------|----------------|---------------------------------------------------------|

|                        | ,              |                                                         |

|                        | GAA1/IOuxwByVz |                                                         |

|                        | GABO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAB1/IOuxwByVz |                                                         |

|                        | GACO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAC1/IOuxwByVz |                                                         |

|                        | GBAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBA1/IOuxwByVz |                                                         |

|                        | GBBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBB1/IOuxwByVz |                                                         |

|                        | GBCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBC1/IOuxwByVz |                                                         |

|                        | GDAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDA1/IOuxwByVz |                                                         |

|                        | GDBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDB1/IOuxwByVz |                                                         |

|                        | GDCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDC1/IOuxwByVz |                                                         |

|                        | GEAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEA1/IOuxwByVz |                                                         |

|                        | GEBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEB1/IOuxwByVz |                                                         |

|                        | GECO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEC1/IOuxwByVz |                                                         |

### Table 3-3 • Quadrant Global Pin Name (continued)

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

## **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

## I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

standard for CLKBUF is LVTTL in the current Microsemi Libero  $^{\ensuremath{\mathbb{R}}}$  System-on-Chip (SoC) and Designer software.

| Name            | Description                                                    |

|-----------------|----------------------------------------------------------------|

| CLKBUF_LVCMOS5  | LVCMOS clock buffer with 5.0 V CMOS voltage level              |

| CLKBUF_LVCMOS33 | LVCMOS clock buffer with 3.3 V CMOS voltage level              |

| CLKBUF_LVCMOS25 | LVCMOS clock buffer with 2.5 V CMOS voltage level <sup>1</sup> |

| CLKBUF_LVCMOS18 | LVCMOS clock buffer with 1.8 V CMOS voltage level              |

| CLKBUF_LVCMOS15 | LVCMOS clock buffer with 1.5 V CMOS voltage level              |

| CLKBUF_LVCMOS12 | LVCMOS clock buffer with 1.2 V CMOS voltage level              |

| CLKBUF_PCI      | PCI clock buffer                                               |

| CLKBUF_PCIX     | PCIX clock buffer                                              |

| CLKBUF_GTL25    | GTL clock buffer with 2.5 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTL33    | GTL clock buffer with 3.3 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTLP25   | GTL+ clock buffer with 2.5 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_GTLP33   | GTL+ clock buffer with 3.3 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_HSTL_I   | HSTL Class I clock buffer <sup>1</sup>                         |

| CLKBUF_HSTL_II  | HSTL Class II clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_I  | SSTL2 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_II | SSTL2 Class II clock buffer <sup>1</sup>                       |

| CLKBUF_SSTL3_I  | SSTL3 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL3_II | SSTL3 Class II clock buffer <sup>1</sup>                       |

#### Table 3-9 • I/O Standards within CLKBUF

Notes:

- 1. Supported in only the IGLOOe, ProASIC3E, AFS600, and AFS1500 devices

- 2. By default, the CLKBUF macro uses the 3.3 V LVTTL I/O technology.

The current synthesis tool libraries only infer the CLKBUF or CLKINT macros in the netlist. All other global macros must be instantiated manually into your HDL code. The following is an example of CLKBUF LVCMOS25 global macro instantiations that you can copy and paste into your code:

### VHDL

```

component clkbuf_lvcmos25

port (pad : in std_logic; y : out std_logic);

end component

```

#### begin

```

-- concurrent statements

u2 : clkbuf_lvcmos25 port map (pad => ext_clk, y => int_clk);

end

```

## Verilog

module design (\_\_\_\_\_);

input \_\_\_\_; output \_\_\_\_;

clkbuf\_lvcmos25 u2 (.y(int\_clk), .pad(ext\_clk);

endmodule

# 4 – Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# Introduction

This document outlines the following device information: Clock Conditioning Circuit (CCC) features, PLL core specifications, functional descriptions, software configuration information, detailed usage information, recommended board-level considerations, and other considerations concerning clock conditioning circuits and global networks in low power flash devices or mixed signal FPGAs.

# **Overview of Clock Conditioning Circuitry**

In Fusion, IGLOO, and ProASIC3 devices, the CCCs are used to implement frequency division, frequency multiplication, phase shifting, and delay operations. The CCCs are available in six chip locations—each of the four chip corners and the middle of the east and west chip sides. For device-specific variations, refer to the "Device-Specific Layout" section on page 78.

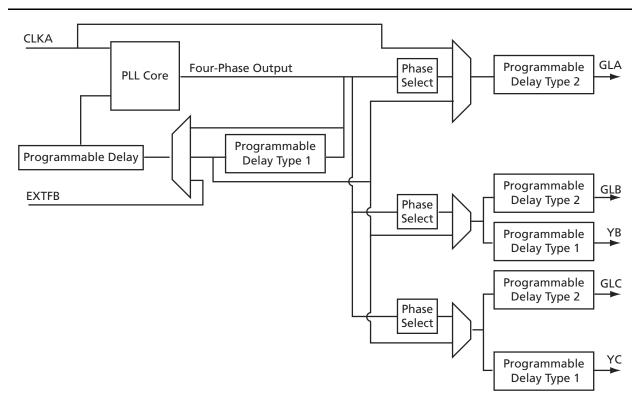

The CCC is composed of the following:

- PLL core

- 3 phase selectors

- 6 programmable delays and 1 fixed delay that advances/delays phase

- 5 programmable frequency dividers that provide frequency multiplication/division (not shown in Figure 4-6 on page 71 because they are automatically configured based on the user's required frequencies)

- · 1 dynamic shift register that provides CCC dynamic reconfiguration capability

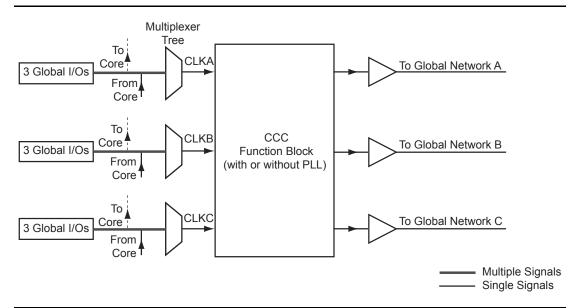

Figure 4-1 provides a simplified block diagram of the physical implementation of the building blocks in each of the CCCs.

Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3

SmartGen also allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB, and YC). SmartGen allows the user to select the input clock source. SmartGen automatically instantiates the special macro, PLLINT, when needed.

Note: Clock divider and clock multiplier blocks are not shown in this figure or in SmartGen. They are automatically configured based on the user's required frequencies.

Figure 4-6 • CCC with PLL Block

# **Global Input Selections**

Low power flash devices provide the flexibility of choosing one of the three global input pad locations available to connect to a CCC functional block or to a global / quadrant global network. Figure 4-7 on page 72 and Figure 4-8 on page 72 show the detailed architecture of each global input structure for 30 k gate devices and below, as well as 60 k gate devices and above, respectively. For 60 k gate devices and above (Figure 4-7 on page 72), if the single-ended I/O standard is chosen, there is flexibility to choose one of the global input pads (the first, second, and fourth input). Once chosen, the other I/O locations are used as regular I/Os. If the differential I/O standard is chosen (not applicable for IGLOO nano and ProASIC3 nano devices), the first and second inputs are considered as paired, and the third input is paired with a regular I/O.

The user then has the choice of selecting one of the two sets to be used as the clock input source to the CCC functional block. There is also the option to allow an internal clock signal to feed the global network or the CCC functional block. A multiplexer tree selects the appropriate global input for routing to the desired location. Note that the global I/O pads do not need to feed the global network; they can also be used as regular I/O pads.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

Each group of control bits is assigned a specific location in the configuration shift register. For a list of the 81 configuration bits (C[80:0]) in the CCC and a description of each, refer to "PLL Configuration Bits Description" on page 90. The configuration register can be serially loaded with the new configuration data and programmed into the CCC using the following ports:

- SDIN: The configuration bits are serially loaded into a shift register through this port. The LSB of the configuration data bits should be loaded first.

- SDOUT: The shift register contents can be shifted out (LSB first) through this port using the shift operation.

- SCLK: This port should be driven by the shift clock.

- SSHIFT: The active-high shift enable signal should drive this port. The configuration data will be shifted into the shift register if this signal is HIGH. Once SSHIFT goes LOW, the data shifting will be halted.

- SUPDATE: The SUPDATE signal is used to configure the CCC with the new configuration bits when shifting is complete.

To access the configuration ports of the shift register (SDIN, SDOUT, SSHIFT, etc.), the user should instantiate the CCC macro in his design with appropriate ports. Microsemi recommends that users choose SmartGen to generate the CCC macros with the required ports for dynamic reconfiguration.

Users must familiarize themselves with the architecture of the CCC core and its input, output, and configuration ports to implement the desired delay and output frequency in the CCC structure. Figure 4-22 shows a model of the CCC with configurable blocks and switches.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

### Table 4-13 • 2-Bit Feedback MUX

| FBSEL<1:0> State | MUX Input Selected                                          |

|------------------|-------------------------------------------------------------|

| 0                | Ground. Used for power-down mode in power-down logic block. |

| 1                | PLL VCO 0° phase shift                                      |

| 2                | PLL delayed VCO 0° phase shift                              |

| 3                | N/A                                                         |

### Table 4-14 • Programmable Delay Selection for Feedback Delay and Secondary Core Output Delays

| FBDLY<4:0>; DLYYB<4:0>; DLYYC<4:0> State | Delay Value             |

|------------------------------------------|-------------------------|

| 0                                        | Typical delay = 600 ps  |

| 1                                        | Typical delay = 760 ps  |

| 2                                        | Typical delay = 920 ps  |

| :                                        | :                       |

| 31                                       | Typical delay = 5.56 ns |

### Table 4-15 • Programmable Delay Selection for Global Clock Output Delays

| DLYGLA<4:0>; DLYGLB<4:0>; DLYGLC<4:0> State | Delay Value             |

|---------------------------------------------|-------------------------|

| 0                                           | Typical delay = 225 ps  |

| 1                                           | Typical delay = 760 ps  |

| 2                                           | Typical delay = 920 ps  |

| :                                           | :                       |

| 31                                          | Typical delay = 5.56 ns |

### Table 4-16 • Fusion Dynamic CCC Clock Source Selection

| RXASEL | DYNASEL | Source of CLKA     |

|--------|---------|--------------------|

| 1      | 0       | RC Oscillator      |

| 1      | 1       | Crystal Oscillator |

| RXBSEL | DYNBSEL | Source of CLKB     |

| 1      | 0       | RC Oscillator      |

| 1      | 1       | Crystal Oscillator |

| RXBSEL | DYNCSEL | Source of CLKC     |

| 1      | 0       | RC Oscillator      |

| 1      | 1       | Crystal Oscillator |

Table 4-17 • Fusion Dynamic CCC NGMUX Configuration

| GLMUXCFG<1:0> | NGMUX Select Signal | Supported Input Clocks to NGMUX |

|---------------|---------------------|---------------------------------|

| 00            | 0                   | GLA                             |

|               | 1                   | GLC                             |

| 01            | 0                   | GLA                             |

|               | 1                   | GLINT                           |

| 10            | 0                   | GLC                             |

|               | 1                   | GLINT                           |

ProASIC3 nano FPGA Fabric User's Guide

| Date                   | Changes                                                                                                                                                                                                                                                                                  | Page |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.2<br>(June 2008)    | <ul> <li>The following changes were made to the family descriptions in Figure 4-1 • Overview of the CCCs Offered in Fusion, IGLOO, and ProASIC3:</li> <li>• ProASIC3L was updated to include 1.5 V.</li> <li>• The number of PLLs for ProASIC3E was changed from five to six.</li> </ul> | 61   |

| v1.1<br>(March 2008)   | Table 4-1 • Flash-Based FPGAs and the associated text were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                         | 63   |

|                        | The "Global Input Selections" section was updated to include 15 k gate devices as supported I/O types for globals, for CCC only.                                                                                                                                                         | 71   |

|                        | Table 4-5 • Number of CCCs by Device Size and Package was revised to include ProASIC3L, IGLOO PLUS, A3P015, AGL015, AGLP030, AGLP060, and AGLP125.                                                                                                                                       | 78   |

|                        | The "IGLOO and ProASIC3 CCC Locations" section was revised to include 15 k gate devices in the exception statements, as they do not contain PLLs.                                                                                                                                        | 81   |

| v1.0<br>(January 2008) | Information about unlocking the PLL was removed from the "Dynamic PLL Configuration" section.                                                                                                                                                                                            | 87   |

|                        | In the "Dynamic PLL Configuration" section, information was added about running Layout and determining the exact setting of the ports.                                                                                                                                                   | 100  |

|                        | In Table 4-8 • Configuration Bit Descriptions for the CCC Blocks, the following bits were updated to delete "transport to the user" and reference the footnote at the bottom of the table: 79 to 71.                                                                                     | 90   |

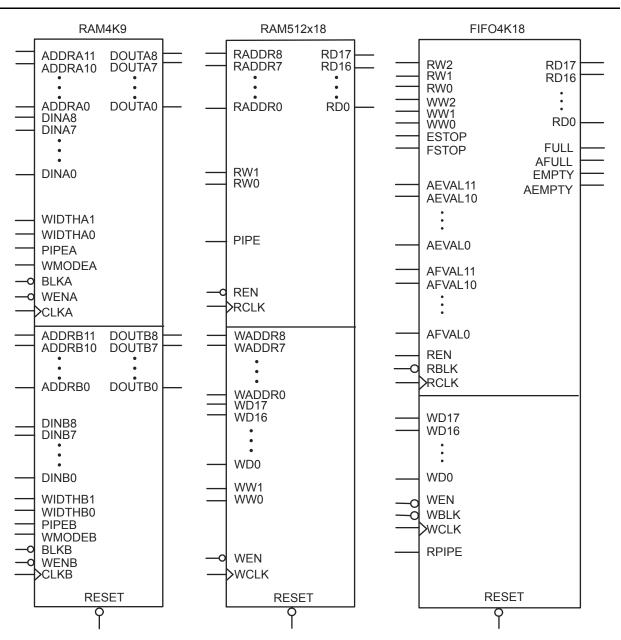

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Notes:

- Automotive ProASIC3 devices restrict RAM4K9 to a single port or to dual ports with the same clock 180° out of phase (inverted) between clock pins. In single-port mode, inputs to port B should be tied to ground to prevent errors during compile. This warning applies only to automotive ProASIC3 parts of certain revisions and earlier. Contact Technical Support at soc\_tech@microsemi.com for information on the revision number for a particular lot and date code.

- 2. For FIFO4K18, the same clock 180° out of phase (inverted) between clock pins should be used.

Figure 6-3 • Supported Basic RAM Macros

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

#### Table 6-2 • Allowable Aspect Ratio Settings for WIDTHA[1:0]

| WIDTHA[1:0] | WIDTHB[1:0] | D×W   |

|-------------|-------------|-------|

| 00          | 00          | 4k×1  |

| 01          | 01          | 2k×2  |

| 10          | 10          | 1k×4  |

| 11          | 11          | 512×9 |

Note: The aspect ratio settings are constant and cannot be changed on the fly.

### BLKA and BLKB

These signals are active-low and will enable the respective ports when asserted. When a BLKx signal is deasserted, that port's outputs hold the previous value.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, BLKB should be tied to ground.

### WENA and WENB

These signals switch the RAM between read and write modes for the respective ports. A LOW on these signals indicates a write operation, and a HIGH indicates a read.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WENB should be tied to ground.

### **CLKA and CLKB**

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

Note: For Automotive ProASIC3 devices, dual-port mode is supported if the clocks to the two SRAM ports are the same and 180° out of phase (i.e., the port A clock is the inverse of the port B clock). For use of this macro as a single-port SRAM, the inputs and clock of one port should be tied off (grounded) to prevent errors during design compile.

### PIPEA and PIPEB

These signals are used to specify pipelined read on the output. A LOW on PIPEA or PIPEB indicates a nonpipelined read, and the data appears on the corresponding output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the corresponding output in the next clock cycle.

Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, PIPEB should be tied to ground. For use in dual-port mode, the same clock with an inversion between the two clock pins of the macro should be used in the design to prevent errors during compile.

#### WMODEA and WMODEB

These signals are used to configure the behavior of the output when the RAM is in write mode. A LOW on these signals makes the output retain data from the previous read. A HIGH indicates pass-through behavior, wherein the data being written will appear immediately on the output. This signal is overridden when the RAM is being read.

# Note: When using the SRAM in single-port mode for Automotive ProASIC3 devices, WMODEB should be tied to ground.

### RESET

This active-low signal resets the control logic, forces the output hold state registers to zero, disables reads and writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory array.

While the RESET signal is active, read and write operations are disabled. As with any asynchronous reset signal, care must be taken not to assert it too close to the edges of active read and write clocks.

### ADDRA and ADDRB

These are used as read or write addresses, and they are 12 bits wide. When a depth of less than 4 k is specified, the unused high-order bits must be grounded (Table 6-3 on page 139).

# Low Power Flash Device I/O Support

The low power flash families listed in Table 7-1 support I/Os and the functions described in this document.

| Series   | Family <sup>*</sup> | Description                                                    |  |

|----------|---------------------|----------------------------------------------------------------|--|

| IGLOO    | IGLOO nano          | Lowest power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology |  |

| ProASIC3 | ProASIC3 nano       | Lowest cost 1.5 V FPGAs with balanced performance              |  |

### Table 7-1 • Flash-Based FPGAs

Note: \*The device name links to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

## IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 7-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

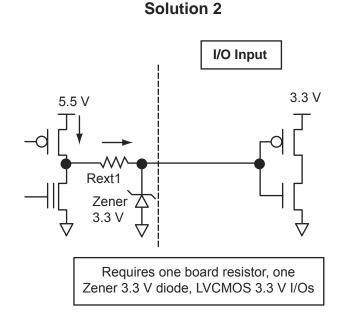

## Solution 2

This solution requires one board resistor and one Zener 3.3 V diode, as demonstrated in Figure 7-6.

## Figure 7-6 • Solution 2

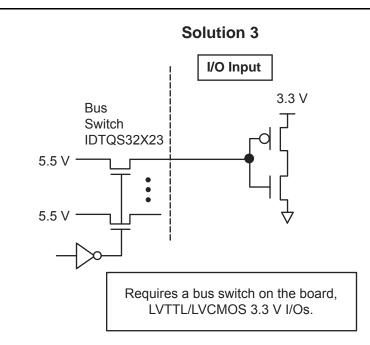

## Solution 3

This solution requires a bus switch on the board, as demonstrated in Figure 7-7.

### Figure 7-7 • Solution 3

DDR for Microsemi's Low Power Flash Devices

## **DDR Output Register**

### Figure 9-6 • DDR Output Register (SSTL3 Class I)

### Verilog

```

module DDR_OutBuf_SSTL3_I(DataR,DataF,CLR,CLK,PAD);

```

input DataR, DataF, CLR, CLK; output PAD;

wire Q, VCC;

```

VCC VCC_1_net(.Y(VCC));

DDR_OUT DDR_OUT_0_inst(.DR(DataR),.DF(DataF),.CLK(CLK),.CLR(CLR),.Q(Q));

OUTBUF_SSTL3_I OUTBUF_SSTL3_I_0_inst(.D(Q),.PAD(PAD));

```

endmodule

### VHDL

```

library ieee;

use ieee.std_logic_1164.all;

library proasic3; use proasic3.all;

entity DDR_OutBuf_SSTL3_I is

port(DataR, DataF, CLR, CLK : in std_logic; PAD : out std_logic) ;

end DDR_OutBuf_SSTL3_I;

architecture DEF_ARCH of DDR_OutBuf_SSTL3_I is

component DDR_OUT

port(DR, DF, CLK, CLR : in std_logic := 'U'; Q : out std_logic) ;

end component;

component OUTBUF_SSTL3_I

port(D : in std_logic := 'U'; PAD : out std_logic) ;

end component;

component VCC

port( Y : out std_logic);

end component;

signal Q, VCC_1_net : std_logic ;

begin

VCC_2_net : VCC port map(Y => VCC_1_net);

DDR_OUT_0_inst : DDR_OUT

port map(DR => DataR, DF => DataF, CLK => CLK, CLR => CLR, Q => Q);

OUTBUF_SSTL3_I_0_inst : OUTBUF_SSTL3_I

port map(D => Q, PAD => PAD);

```

end DEF\_ARCH;

Programming Flash Devices

## Volume Programming Services

### **Device Type Supported: Flash and Antifuse**

Once the design is stable for applications with large production volumes, preprogrammed devices can be purchased. Table 10-2 describes the volume programming services.

| Table 10-2 • Volume | Programming | Sarvicas |

|---------------------|-------------|----------|

|                     | Frogramming | Services |

| Programmer                      | Vendor       | Availability            |

|---------------------------------|--------------|-------------------------|

| In-House Programming            | Microsemi    | Contact Microsemi Sales |

| Distributor Programming Centers | Memec Unique | Contact Distribution    |

| Independent Programming Centers | Various      | Contact Vendor          |

Advantages: As programming is outsourced, this solution is easier to implement than creating a substantial in-house programming capability. As programming houses specialize in large-volume programming, this is often the most cost-effective solution.

Limitations: There are some logistical issues with the use of a programming service provider, such as the transfer of programming files and the approval of First Articles. By definition, the programming file must be released to a third-party programming house. Nondisclosure agreements (NDAs) can be signed to help ensure data protection; however, for extremely security-conscious designs, this may not be an option.

Microsemi In-House Programming

When purchasing Microsemi devices in volume, IHP can be requested as part of the purchase. If this option is chosen, there is a small cost adder for each device programmed. Each device is marked with a special mark to distinguish it from blank parts. Programming files for the design will be sent to Microsemi. Sample parts with the design programmed, First Articles, will be returned for customer approval. Once approval of First Articles has been received, Microsemi will proceed with programming the remainder of the order. To request Microsemi IHP, contact your local Microsemi representative.

Distributor Programming Centers

If purchases are made through a distributor, many distributors will provide programming for their customers. Consult with your preferred distributor about this option.

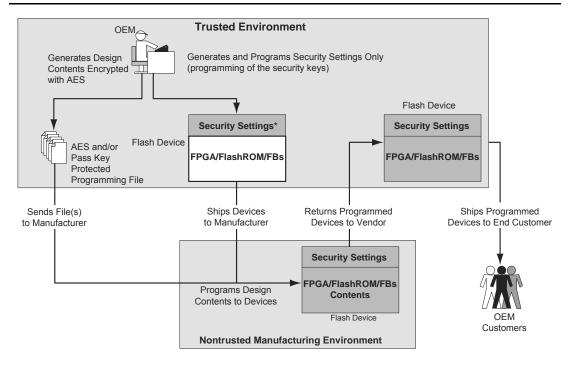

## Application 1: Trusted Environment

As illustrated in Figure 11-7, this application allows the programming of devices at design locations where research and development take place. Therefore, encryption is not necessary and is optional to the user. This is often a secure way to protect the design, since the design program files are not sent elsewhere. In situations where production programming is not available at the design location, programming centers (such as Microsemi In-House Programming) provide a way of programming designs at an alternative, secure, and trusted location. In this scenario, the user generates a STAPL programming file from the Designer software in plaintext format, containing information on the entire design or the portion of the design to be programmed. The user can choose to employ the FlashLock Pass Key feature with the design. Once the design is programming is needed, the user can consider permanently securing the IGLOO and ProASIC3 device, as discussed in the "Permanent FlashLock" section on page 241.

## **Application 2: Nontrusted Environment—Unsecured Location**

Often, programming of devices is not performed in the same location as actual design implementation, to reduce manufacturing cost. Overseas programming centers and contract manufacturers are examples of this scenario.

To achieve security in this case, the AES key and the FlashLock Pass Key can be initially programmed in-house (trusted environment). This is done by generating a programming file with only the security settings and no design contents. The design FPGA core, FlashROM, and (for Fusion) FB contents are generated in a separate programming file. This programming file must be set with the same AES key that was used to program to the device previously so the device will correctly decrypt this encrypted programming file. As a result, the encrypted design content programming file can be safely sent off-site to nontrusted programming locations for design programming. Figure 11-7 shows a more detailed flow for this application.

Notes:

1. Programmed portion indicated with dark gray.

2. Programming of FBs applies to Fusion only.

Figure 11-7 • Application 2: Device Programming in a Nontrusted Environment

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

errors, but this list is intended to show where problems can occur. FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems that may occur with impedance mismatching at higher frequencies. Customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots.

### Scan Chain Failure

Normally, the FlashPro4/3/3X Scan Chain command expects to see 0x1 on the TDO pin. If the command reports reading 0x0 or 0x3, it is seeing the TDO pin stuck at 0 or 1. The only time the TDO pin comes out of tristate is when the JTAG TAP state machine is in the Shift-IR or Shift-DR state. If noise or reflections on the TCK or TMS lines have disrupted the correct state transitions, the device's TAP state controller might not be in one of these two states when the programmer tries to read the device. When this happens, the output is floating when it is read and does not match the expected data value. This can also be caused by a broken TDO net. Only a small amount of data is read from the device during the Scan Chain command, so marginal problems may not always show up during this command. Occasionally a faulty programmer can cause intermittent scan chain failures.

### Exit 11

This error occurs during the verify stage of programming a device. After programming the design into the device, the device is verified to ensure it is programmed correctly. The verification is done by shifting the programming data into the device. An internal comparison is performed within the device to verify that all switches are programmed correctly. Noise induced by poor signal integrity can disrupt the writes and reads or the verification process and produce a verification error. While technically a verification error, the root cause is often related to signal integrity.

Refer to the *FlashPro User's Guide* for other error messages and solutions. For the most up-to-date known issues and solutions, refer to http://www.microsemi.com/soc/support.

# Conclusion

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low-cost, single-chip solution that is live at power-up through nonvolatile flash technology. The FlashLock Pass Key and 128-bit AES Key security features enable secure ISP in an untrusted environment. On-chip FlashROM enables a host of new applications, including device serialization, subscription-based applications, and IP addressing. Additionally, as the FlashROM is nonvolatile, all of these services can be provided without battery backup.

# **Related Documents**

## **User's Guides**

FlashPro User's Guide http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **Boundary Scan Support in Low Power Devices**

The information in this document applies to all Fusion, IGLOO, and ProASIC3 devices. For IGLOO, IGLOO PLUS, and ProASIC3L devices, the Flash\*Freeze pin must be deasserted for successful boundary scan operations. Devices cannot enter JTAG mode directly from Flash\*Freeze mode.

# **Boundary Scan Opcodes**

Low power flash devices support all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 15-2).

### Table 15-2 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

# **Boundary Scan Chain**

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain (Figure 15-2 on page 294), which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section in the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for pull-up/-down recommendations for TCK and TRST pins. Pull-down recommendations are also given in Table 15-3 on page 294

The following devices and families do not support cold-sparing:

- IGLOO: AGL060, AGL125, AGL250, AGL600, AGL1000

- ProASIC3: A3P060, A3P125, A3P250, A3P400, A3P600, A3P1000

- ProASIC3L: A3P250L, A3P600L, A3P1000L

- Military ProASIC3: A3P1000

# **Hot-Swapping**

Hot-swapping is the operation of hot insertion or hot removal of a card in a powered-up system. The I/Os need to be configured in hot-insertion mode if hot-swapping compliance is required. For more details on the levels of hot-swap compatibility in low power flash devices, refer to the "Hot-Swap Support" section in the I/O Structures chapter of the user's guide for the device you are using.

The following devices and families support hot-swapping:

- IGLOO: AGL015 and AGL030

- All IGLOO nano

- All IGLOO PLUS

- All IGLOOe

- ProASIC3L: A3PE3000L

- ProASIC3: A3P015 and A3P030

- All ProASIC3 nano

- All ProASIC3E

- Military ProASIC3EL: A3PE600L and A3PE3000L

- RT ProASIC3: RT3PE600L and RT3PE3000L

The following devices and families do not support hot-swapping:

- IGLOO: AGL060, AGL125, AGL250, AGL400, AGL600, AGL1000

- ProASIC3: A3P060, A3P125, A3P250, A3P400, A3P600, A3P1000

- ProASIC3L: A3P250L, A3P600L, A3P1000L

- Military ProASIC3: A3P1000

# Conclusion

Microsemi's low power flash FPGAs provide an excellent programmable logic solution for a broad range of applications. In addition to high performance, low cost, security, nonvolatility, and single chip, they are live at power-up (meet Level 0 of the LAPU classification) and offer clear and easy-to-use power-up/down characteristics. Unlike SRAM FPGAs, low power flash devices do not require any specific powerup/-down sequencing and have extremely low power-up inrush current in any power-up sequence. Microsemi low power flash FPGAs also support both cold-sparing and hot-swapping for applications requiring these capabilities.