Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 36864                                                                       |

| Number of I/O                  | 71                                                                          |

| Number of Gates                | 125000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 100-TQFP                                                                    |

| Supplier Device Package        | 100-VQFP (14x14)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn125-z2vqg100i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

|   | Introduction                                                                  | 7  |

|---|-------------------------------------------------------------------------------|----|

|   | Related Information                                                           |    |

| 1 | FPGA Array Architecture in Low Power Flash Devices                            | 9  |

|   | Device Architecture                                                           |    |

|   | FPGA Array Architecture Support                                               | 10 |

|   | Device Overview                                                               |    |

|   | Related Documents                                                             |    |

|   | List of Changes                                                               | 20 |

| 2 | Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs                         |    |

|   | Introduction                                                                  |    |

|   | Power Consumption Overview                                                    |    |

|   | Static (Idle) Mode                                                            |    |

|   | User Low Static (Idle) Mode                                                   |    |

|   | Sleep Mode                                                                    |    |

|   | Shutdown Mode                                                                 |    |

|   | Conclusion                                                                    |    |

|   | List of Changes                                                               |    |

|   | List of Changes                                                               | 28 |

| 3 | Global Resources in Low Power Flash Devices                                   |    |

|   | Introduction                                                                  |    |

|   | Global Architecture                                                           |    |

|   | Global Resource Support in Flash-Based Devices                                |    |

|   | VersaNet Global Network Distribution                                          |    |

|   | Spine Architecture                                                            |    |

|   | Using Clock Aggregation                                                       |    |

|   | Design Recommendations                                                        |    |

|   | Conclusion                                                                    |    |

|   | Related Documents                                                             |    |

|   | List of Changes                                                               | E0 |

| 4 | Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs | 61 |

|   | Introduction                                                                  |    |

|   | Overview of Clock Conditioning Circuitry                                      |    |

|   | CCC Support in Microsemi's Flash Devices                                      |    |

|   | Global Buffers with No Programmable Delays                                    |    |

|   | Global Buffer with Programmable Delay                                         |    |

|   | Global Buffers with PLL Function                                              |    |

|   | Global Input Selections                                                       | 71 |

|   | Device-Specific Layout                                                        | 78 |

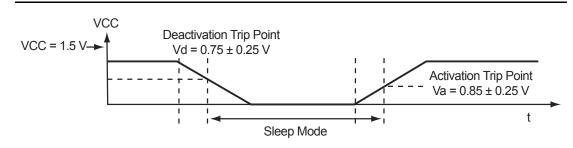

Figure 2-5 • Entering and Exiting Sleep Mode—Typical Timing Diagram

## **Shutdown Mode**

For all ProASIC3/E and ProASIC3 nano devices, shutdown mode can be entered by turning off all power supplies when device functionality is not needed. Cold-sparing and hot-insertion features in ProASIC3 nano devices enable the device to be powered down without turning off the entire system. When power returns, the live at power-up feature enables immediate operation of the device.

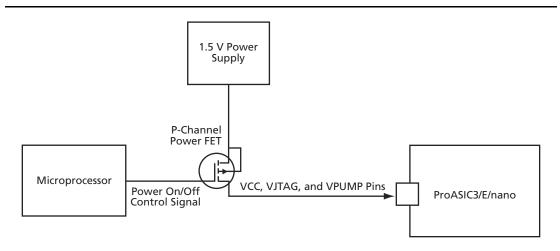

## Using Sleep Mode or Shutdown Mode in the System

Depending on the power supply and components used in an application, there are many ways to turn the power supplies connected to the device on or off. For example, Figure 2-6 shows how a microprocessor is used to control a power FET. It is recommended that power FETs with low on resistance be used to perform the switching action.

Figure 2-6 • Controlling Power On/Off State Using Microprocessor and Power FET

Global Resources in Low Power Flash Devices

# **Design Recommendations**

The following sections provide design flow recommendations for using a global network in a design.

- "Global Macros and I/O Standards"

- "Global Macro and Placement Selections" on page 48

- · "Using Global Macros in Synplicity" on page 50

- "Global Promotion and Demotion Using PDC" on page 51

- "Spine Assignment" on page 52

- · "Designer Flow for Global Assignment" on page 53

- "Simple Design Example" on page 55

- "Global Management in PLL Design" on page 57

- · "Using Spines of Occupied Global Networks" on page 58

#### Global Macros and I/O Standards

The larger low power flash devices have six chip global networks and four quadrant global networks. However, the same clock macros are used for assigning signals to chip globals and quadrant globals. Depending on the clock macro placement or assignment in the Physical Design Constraint (PDC) file or MultiView Navigator (MVN), the signal will use the chip global network or quadrant network. Table 3-8 lists the clock macros available for low power flash devices. Refer to the *IGLOO*, *ProASIC3*, *SmartFusion*, *and Fusion Macro Library Guide* for details.

Table 3-8 • Clock Macros

| Macro Name         | Description                                                                                                   | Symbol                                |

|--------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------|

| CLKBUF             | Input macro for Clock Network                                                                                 | PAD CLKBUF                            |

| CLKBUF_x           | Input macro for Clock Network with specific I/O standard                                                      | CLKBUF_X PAD Y                        |

| CLKBUF_LVDS/LVPECL | LVDS or LVPECL input macro<br>for Clock Network (not<br>supported for IGLOO nano or<br>ProASIC3 nano devices) |                                       |

| CLKINT             | Macro for internal clock interface                                                                            | A CLKINT                              |

| CLKBIBUF           | Bidirectional macro with input dedicated to routed Clock Network                                              | I I I I I I I I I I I I I I I I I I I |

Use these available macros to assign a signal to the global network. In addition to these global macros, PLL and CLKDLY macros can also drive the global networks. Use I/O-standard-specific clock macros (CLKBUF\_x) to instantiate a specific I/O standard for the global signals. Table 3-9 on page 47 shows the list of these I/O-standard-specific macros. Note that if you use these I/O-standard-specific clock macros, you cannot change the I/O standard later in the design stage. If you use the regular CLKBUF macro, you can use MVN or the PDC file in Designer to change the I/O standard. The default I/O

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

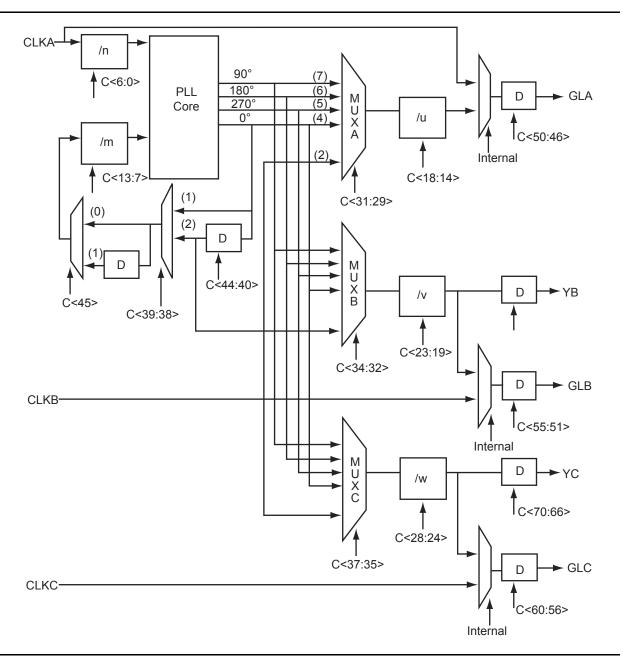

Each CCC can implement up to three independent global buffers (with or without programmable delay) or a PLL function (programmable frequency division/multiplication, phase shift, and delays) with up to three global outputs. Unused global outputs of a PLL can be used to implement independent global buffers, up to a maximum of three global outputs for a given CCC.

## **CCC Programming**

The CCC block is fully configurable, either via flash configuration bits set in the programming bitstream or through an asynchronous interface. This asynchronous dedicated shift register interface is dynamically accessible from inside the low power flash devices to permit parameter changes, such as PLL divide ratios and delays, during device operation.

To increase the versatility and flexibility of the clock conditioning system, the CCC configuration is determined either by the user during the design process, with configuration data being stored in flash memory as part of the device programming procedure, or by writing data into a dedicated shift register during normal device operation.

This latter mode allows the user to dynamically reconfigure the CCC without the need for core programming. The shift register is accessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 297 or the application note *Using Global Resources in Actel Fusion Devices*.

#### **Global Resources**

Low power flash and mixed signal devices provide three global routing networks (GLA, GLB, and GLC) for each of the CCC locations. There are potentially many I/O locations; each global I/O location can be chosen from only one of three possibilities. This is controlled by the multiplexer tree circuitry in each global network. Once the I/O location is selected, the user has the option to utilize the CCCs before the signals are connected to the global networks. The CCC in each location (up to six) has the same structure, so generating the CCC macros is always done with an identical software GUI. The CCCs in the corner locations drive the quadrant global networks, and the CCCs in the middle of the east and west chip sides drive the chip global networks. The quadrant global networks span only a quarter of the device, while the chip global networks span the entire device. For more details on global resources offered in low power flash devices, refer to the "Global Resources in Low Power Flash Devices" section on page 31.

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, or CLKC-GLC) of a given CCC. A PLL macro uses the CLKA CCC input to drive its reference clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output cannot be reused if the YB (or YC) output is used. Refer to the "PLL Macro Signal Descriptions" section on page 68 for more information.

Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- The FPGA core

#### Notes:

- 1. For INBUF\* driving a PLL macro or CLKDLY macro, the I/O will be hard-routed to the CCC; i.e., will be placed by software to a dedicated Global I/O.

- 2. IGLOO nano and ProASIC3 nano devices do not support differential inputs.

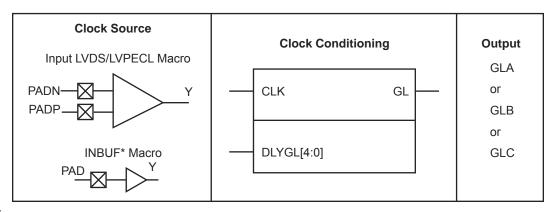

Figure 4-3 • CCC Options: Global Buffers with Programmable Delay

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay. The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the software will automatically place the dedicated global I/O in the appropriate locations. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the low power flash family. The available INBUF macros are described in the IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide.

The CLKDLY macro can be driven directly from the FPGA core. The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate the clock input driven by the hardwired I/O connection.

The visual CLKDLY configuration in the SmartGen area of the Microsemi Libero System-on-Chip (SoC) and Designer tools allows the user to select the desired amount of delay and configures the delay elements appropriately. SmartGen also allows the user to select the input clock source. SmartGen will automatically instantiate the special macro, PLLINT, when needed.

# **CLKDLY Macro Signal Descriptions**

The CLKDLY macro supports one input and one output. Each signal is described in Table 4-2.

Table 4-2 • Input and Output Description of the CLKDLY Macro

| Signal | Name            | I/O    | Description                                                       |

|--------|-----------------|--------|-------------------------------------------------------------------|

| CLK    | Reference Clock | Input  | Reference clock input                                             |

| GL     | Global Output   | Output | Primary output clock to respective global/quadrant clock networks |

ProASIC3 nano FPGA Fabric User's Guide

This section outlines the following device information: CCC features, PLL core specifications, functional descriptions, software configuration information, detailed usage information, recommended board-level considerations, and other considerations concerning global networks in low power flash devices.

## Clock Conditioning Circuits with Integrated PLLs

Each of the CCCs with integrated PLLs includes the following:

- 1 PLL core, which consists of a phase detector, a low-pass filter, and a four-phase voltagecontrolled oscillator

- 3 global multiplexer blocks that steer signals from the global pads and the PLL core onto the global networks

- · 6 programmable delays and 1 fixed delay for time advance/delay adjustments

- 5 programmable frequency divider blocks to provide frequency synthesis (automatically configured by the SmartGen macro builder tool)

## **Clock Conditioning Circuits without Integrated PLLs**

There are two types of simplified CCCs without integrated PLLs in low power flash devices.

- 1. The simplified CCC with programmable delays, which is composed of the following:

- 3 global multiplexer blocks that steer signals from the global pads and the programmable delay elements onto the global networks

- 3 programmable delay elements to provide time delay adjustments

- 2. The simplified CCC (referred to as CCC-GL) without programmable delay elements, which is composed of the following:

- A global multiplexer block that steer signals from the global pads onto the global networks

Figure 4-22 • CCC Block Control Bits – Graphical Representation of Assignments

#### SRAM Usage

The following descriptions refer to the usage of both RAM4K9 and RAM512X18.

#### Clocking

The dual-port SRAM blocks are only clocked on the rising edge. SmartGen allows falling-edge-triggered clocks by adding inverters to the netlist, hence achieving dual-port SRAM blocks that are clocked on either edge (rising or falling). For dual-port SRAM, each port can be clocked on either edge and by separate clocks by port. Note that for Automotive ProASIC3, the same clock, with an inversion between the two clock pins of the macro, should be used in design to prevent errors during compile.

Low power flash devices support inversion (bubble-pushing) throughout the FPGA architecture, including the clock input to the SRAM modules. Inversions added to the SRAM clock pin on the design schematic or in the HDL code will be automatically accounted for during design compile without incurring additional delay in the clock path.

The two-port SRAM can be clocked on the rising or falling edge of WCLK and RCLK.

If negative-edge RAM and FIFO clocking is selected for memory macros, clock edge inversion management (bubble-pushing) is automatically used within the development tools, without performance penalty.

#### **Modes of Operation**

There are two read modes and one write mode:

- Read Nonpipelined (synchronous—1 clock edge): In the standard read mode, new data is driven

onto the RD bus in the same clock cycle following RA and REN valid. The read address is

registered on the read port clock active edge, and data appears at RD after the RAM access time.

Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous—2 clock edges): The pipelined mode incurs an additional clock delay from address to data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting PIPE to ON enables this mode.

- Write (synchronous—1 clock edge): On the write clock active edge, the write data is written into

the SRAM at the write address when WEN is HIGH. The setup times of the write address, write

enables, and write data are minimal with respect to the write clock.

#### **RAM** Initialization

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism. The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

#### **FIFO Features**

The FIFO4KX18 macro is created by merging the RAM block with dedicated FIFO logic (Figure 6-6 on page 142). Since the FIFO logic can only be used in conjunction with the memory block, there is no separate FIFO controller macro. As with the RAM blocks, the FIFO4KX18 nomenclature does not refer to a possible aspect ratio, but rather to the deepest possible data depth and the widest possible data width. FIFO4KX18 can be configured into the following aspect ratios: 4,096×1, 2,048×2, 1,024×4, 512×9, and 256×18. In addition to being fully synchronous, the FIFO4KX18 also has the following features:

- · Four FIFO flags: Empty, Full, Almost-Empty, and Almost-Full

- Empty flag is synchronized to the read clock

- Full flag is synchronized to the write clock

- · Both Almost-Empty and Almost-Full flags have programmable thresholds

- · Active-low asynchronous reset

- Active-low block enable

- · Active-low write enable

- · Active-high read enable

- Ability to configure the FIFO to either stop counting after the empty or full states are reached or to allow the FIFO counters to continue

ProASIC3 nano FPGA Fabric User's Guide

- If one of the registers has a PRE pin, all the other registers that are candidates for combining in the I/O must have a PRE pin.

- If one of the registers has neither a CLR nor a PRE pin, all the other registers that are candidates for combining must have neither a CLR nor a PRE pin.

- If the clear or preset pins are present, they must have the same polarity.

- If the clear or preset pins are present, they must be driven by the same signal (net).

- For single-tile devices (10 k, 15 k, and 20 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock function (both CLR and CLK are shared among all registers):

- Both the Output and Output Enable registers must not have an E pin (clock enable).

- 4. For dual-tile devices (60 k, 125 k, and 250 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock and enable function:

- Both the Output and Output Enable registers must have an E pin (clock enable), or none at all.

- If the E pins are present, they must have the same polarity. The CLK pins must also have the same polarity.

In some cases, the user may want registers to be combined with the input of a bibuf while maintaining the output as-is. This can be achieved by using PDC commands as follows:

```

set_io <signal name> -REGISTER yes ----register will combine

set_preserve <signal name> ----register will not combine

```

## Weak Pull-Up and Weak Pull-Down Resistors

nano devices support optional weak pull-up and pull-down resistors on each I/O pin. When the I/O is pulled up, it is connected to the  $V_{\text{CCI}}$  of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to the datasheet for more information.

For low power applications and when using IGLOO nano devices, configuration of the pull-up or pull-down of the I/O can be used to set the I/O to a known state while the device is in Flash\*Freeze mode. Refer to "Flash\*Freeze Technology and Low Power Modes" in an applicable FPGA fabric user's guide for more information.

The Flash\*Freeze (FF) pin cannot be configured with a weak pull-down or pull-up I/O attribute, as the signal needs to be driven at all times.

# **Output Slew Rate Control**

The slew rate is the amount of time an input signal takes to get from logic LOW to logic HIGH or vice versa

It is commonly defined as the propagation delay between 10% and 90% of the signal's voltage swing. Slew rate control is available for the output buffers of low power flash devices. The output buffer has a programmable slew rate for both HIGH-to-LOW and LOW-to-HIGH transitions.

The slew rate can be implemented by using a PDC command (Table 7-5 on page 163), setting it "High" or "Low" in the I/O Attribute Editor in Designer, or instantiating a special I/O macro. The default slew rate value is "High."

Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

# **Output Drive**

The output buffers of nano devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

# I/O Software Support

In Microsemi's Libero software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards.

Table 7-15 • nano I/O Attributes vs. I/O Standard Applications

|                      | SLEW (output OUT_Di O Standard only) (output |                                                          |          |                         | LOAD<br>it only)   |     |            |                     |  |

|----------------------|----------------------------------------------|----------------------------------------------------------|----------|-------------------------|--------------------|-----|------------|---------------------|--|

| I/O Standard         |                                              |                                                          | RES_PULL | IGLOO<br>nano           |                    |     | Hold State | Combine<br>Register |  |

| LVTTL/<br>LVCMOS3.3  | 1                                            | <b>√</b> (8)                                             | ✓        | 1                       | 1                  | ✓   | 1          | 1                   |  |

| LVCMOS2.5            | 1                                            | <b>√</b> (8)                                             | ✓        | ✓                       | ✓                  | ✓   | ✓          | ✓                   |  |

| LVCMOS1.8            | 1                                            | <b>√</b> (4)                                             | ✓        | 1                       | ✓                  | ✓   | ✓          | ✓                   |  |

| LVCMOS1.5            | 1                                            | <b>√</b> (2)                                             | ✓        | 1                       | ✓                  | ✓   | ✓          | ✓                   |  |

| LVCMOS1.2            | 1                                            | <b>√</b> (2)                                             | ✓        | 1                       | _                  | 1   | 1          | ✓                   |  |

| Software<br>Defaults | HIGH                                         | Refer to<br>numbers in<br>parentheses<br>in above cells. | None     | All<br>Devices:<br>5 pF | 10 pF or<br>35 pF* | Off | Off        | No                  |  |

Note: \*10 pF for A3PN010, A3PN015, and A3PN020; 35 pF for A3PN060, A3PN125, and A3PN250.

Table 9-2 • DDR I/O Options (continued)

| DDR Register<br>Type I/O Type |                         | I/O Standard | Sub-Options     | Comments                                     |

|-------------------------------|-------------------------|--------------|-----------------|----------------------------------------------|

| Transmit Register             | Tristate                | Normal       | Enable Polarity | Low/high (low default)                       |

| (continued)                   | Buffer                  | LVTTL        | Output Drive    | 2, 4, 6, 8, 12,16, 24, 36 mA (8 mA default)  |

|                               |                         |              | Slew Rate       | Low/high (high default)                      |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         |              | Pull-Up/-Down   | None (default)                               |

|                               |                         | LVCMOS       | Voltage         | 1.5 V, 1.8 V, 2.5 V, 5 V (1.5 V default)     |

|                               |                         |              | Output Drive    | 2, 4, 6, 8, 12, 16, 24, 36 mA (8 mA default) |

|                               |                         |              | Slew Rate       | Low/high (high default)                      |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         |              | Pull-Up/-Down   | None (default)                               |

|                               |                         | PCI/PCI-X    | Enable Polarity | Low/high (low default)                       |

|                               |                         | GTL/GTL+     | Voltage         | 1.8 V, 2.5 V, 3.3 V (3.3 V default)          |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | HSTL         | Class           | I / II (I default)                           |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | SSTL2/SSTL3  | Class           | I / II (I default)                           |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               | Bidirectional<br>Buffer | Normal       | Enable Polarity | Low/high (low default)                       |

|                               |                         | LVTTL        | Output Drive    | 2, 4, 6, 8, 12, 16, 24, 36 mA (8 mA default) |

|                               |                         |              | Slew Rate       | Low/high (high default)                      |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         |              | Pull-Up/-Down   | None (default)                               |

|                               |                         | LVCMOS       | Voltage         | 1.5 V, 1.8 V, 2.5 V, 5 V (1.5 V default)     |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         |              | Pull-Up         | None (default)                               |

|                               |                         | PCI/PCI-X    | None            |                                              |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | GTL/GTL+     | Voltage         | 1.8 V, 2.5 V, 3.3 V (3.3 V default)          |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | HSTL         | Class           | I / II (I default)                           |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | SSTL2/SSTL3  | Class           | I / II (I default)                           |

|                               |                         |              | Enable Polarity | Low/high (low default)                       |

|                               |                         | <u> </u>     | <u> </u>        |                                              |

Note: \*IGLOO nano and ProASIC3 nano devices do not support differential inputs.

# **General Flash Programming Information**

## **Programming Basics**

When choosing a programming solution, there are a number of options available. This section provides a brief overview of those options. The next sections provide more detail on those options as they apply to Microsemi FPGAs.

#### Reprogrammable or One-Time-Programmable (OTP)

Depending on the technology chosen, devices may be reprogrammable or one-time-programmable. As the name implies, a reprogrammable device can be programmed many times. Generally, the contents of such a device will be completely overwritten when it is reprogrammed. All Microsemi flash devices are reprogrammable.

An OTP device is programmable one time only. Once programmed, no more changes can be made to the contents. Microsemi flash devices provide the option of disabling the reprogrammability for security purposes. This combines the convenience of reprogrammability during design verification with the security of an OTP technology for highly sensitive designs.

#### Device Programmer or In-System Programming

There are two fundamental ways to program an FPGA: using a device programmer or, if the technology permits, using in-system programming. A device programmer is a piece of equipment in a lab or on the production floor that is used for programming FPGA devices. The devices are placed into a socket mounted in a programming adapter module, and the appropriate electrical interface is applied. The programmed device can then be placed on the board. A typical programmer, used during development, programs a single device at a time and is referred to as a single-site engineering programmer.

With ISP, the device is already mounted onto the system printed circuit board when programming occurs. Typically, ISD programming is performed via a JTAG interface on the FPGA. The JTAG pins can be controlled either by an on-board resource, such as a microprocessor, or by an off-board programmer through a header connection. Once mounted, it can be programmed repeatedly and erased. If the application requires it, the system can be designed to reprogram itself using a microprocessor, without the use of any external programmer.

If multiple devices need to be programmed with the same program, various multi-site programming hardware is available in order to program many devices in parallel. Microsemi In House Programming is also available for this purpose.

# **Programming Features for Microsemi Devices**

#### Flash Devices

The flash devices supplied by Microsemi are reprogrammable by either a generic device programmer or ISP. Microsemi supports ISP using JTAG, which is supported by the FlashPro4 and FlashPro3, FlashPro Lite, Silicon Sculptor 3, and Silicon Sculptor II programmers.

Levels of ISP support vary depending on the device chosen:

- · All SmartFusion, Fusion, IGLOO, and ProASIC3 devices support ISP.

- IGLOO, IGLOOe, IGLOO nano V5, and IGLOO PLUS devices can be programmed in-system when the device is using a 1.5 V supply voltage to the FPGA core.

- IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only) or 1.5 V. IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

# 11 - Security in Low Power Flash Devices

# **Security in Programmable Logic**

The need for security on FPGA programmable logic devices (PLDs) has never been greater than today. If the contents of the FPGA can be read by an external source, the intellectual property (IP) of the system is vulnerable to unauthorized copying. Fusion, IGLOO, and ProASIC3 devices contain state-of-the-art circuitry to make the flash-based devices secure during and after programming. Low power flash devices have a built-in 128-bit Advanced Encryption Standard (AES) decryption core (except for 30 k gate devices and smaller). The decryption core facilitates secure in-system programming (ISP) of the FPGA core array fabric, the FlashROM, and the Flash Memory Blocks (FBs) in Fusion devices. The FlashROM, Flash Blocks, and FPGA core fabric can be programmed independently of each other, allowing the FlashROM or Flash Blocks to be updated without the need for change to the FPGA core fabric.

Microsemi has incorporated the AES decryption core into the low power flash devices and has also included the Microsemi flash-based lock technology, FlashLock. Together, they provide leading-edge security in a programmable logic device. Configuration data loaded into a device can be decrypted prior to being written to the FPGA core using the AES 128-bit block cipher standard. The AES encryption key is stored in on-chip, nonvolatile flash memory.

This document outlines the security features offered in low power flash devices, some applications and uses, as well as the different software settings for each application.

#### Figure 11-15 • Programming Fusion Security Settings Only

- 2. Choose the desired security level setting and enter the key(s).

- The **High** security level employs FlashLock Pass Key with AES Key protection.

- The **Medium** security level employs FlashLock Pass Key protection only.

Figure 11-16 • High Security Level to Implement FlashLock Pass Key and AES Key Protection

# FlashROM and Programming Files

Each low power flash device has 1 kbit of on-chip, nonvolatile flash memory that can be accessed from the FPGA core. This nonvolatile FlashROM is arranged in eight pages of 128 bits (Figure 12-3). Each page can be programmed independently, with or without the 128-bit AES encryption. The FlashROM can only be programmed via the IEEE 1532 JTAG port and cannot be programmed from the FPGA core. In addition, during programming of the FlashROM, the FPGA core is powered down automatically by the on-chip programming control logic.

|        |   | Byte Number in Page |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|--------|---|---------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|        |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|        | 7 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| _      | 6 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Number | 5 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Шn     | 4 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|        | 3 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Page   | 2 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Δ.     | 1 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|        | 0 |                     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

Figure 12-3 • FlashROM Architecture

When using FlashROM combined with AES, many subscription-based applications or device serialization applications are possible. The FROM configurator found in the Libero SoC Catalog supports easy management of the FlashROM contents, even over large numbers of devices. The FROM configurator can support FlashROM contents that contain the following:

- Static values

- Random numbers

- · Values read from a file

- · Independent updates of each page

In addition, auto-incrementing of fields is possible. In applications where the FlashROM content is different for each device, you have the option to generate a single STAPL file for all the devices or individual serialization files for each device. For more information on how to generate the FlashROM content for device serialization, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section on page 117.

Libero SoC includes a unique tool to support the generation and management of FlashROM and FPGA programming files. This tool is called FlashPoint.

Depending on the applications, designers can use the FlashPoint software to generate a STAPL file with different contents. In each case, optional AES encryption and/or different security settings can be set.

In Designer, when you click the Programming File icon, FlashPoint launches, and you can generate STAPL file(s) with four different cases (Figure 12-4 on page 268). When the serialization feature is used during the configuration of FlashROM, you can generate a single STAPL file that will program all the devices or an individual STAPL file for each device.

The following cases present the FPGA core and FlashROM programming file combinations that can be used for different applications. In each case, you can set the optional security settings (FlashLock Pass Key and/or AES Key) depending on the application.

- A single STAPL file or multiple STAPL files with multiple FlashROM contents and the FPGA core content. A single STAPL file will be generated if the device serialization feature is not used. You can program the whole FlashROM or selectively program individual pages.

- 2. A single STAPL file for the FPGA core content

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

# **Circuit Verification**

The power switching circuit recommended above is implemented on Microsemi's Icicle board (Figure 13-2). On the Icicle board, VJTAGENB is used to control the N-Channel Digital FET; however, this circuit was modified to use TRST instead of VJTAGENB in this application. There are three important aspects of this circuit that were verified:

- 1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH

- 2. VCC rises to 1.5 V before programming begins.

- 3. VCC switches from 1.5 V to 1.2 V when TRST is LOW.

# **Verification Steps**

1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH.

#### Figure 13-2 • Core Voltage on the IGLOO AGL125-QNG132 Device

In the oscilloscope plots (Figure 13-2), the TRST from FlashPro3 and the VCC core voltage of the IGLOO device are labeled. This plot shows the rise characteristic of the TRST signal from FlashPro3. Once the TRST signal is asserted HIGH, the LTC3025 shown in Figure 13-1 on page 277 senses the increase in voltage and changes the output from 1.2 V to 1.5 V. It takes the circuit approximately 100  $\mu s$  to respond to TRST and change the voltage to 1.5 V on the VCC core.

# **Programming Algorithm**

#### **JTAG Interface**

The low power flash families are fully compliant with the IEEE 1149.1 (JTAG) standard. They support all the mandatory boundary scan instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) as well as six optional public instructions (USERCODE, IDCODE, HIGHZ, and CLAMP).

#### **IEEE 1532**

The low power flash families are also fully compliant with the IEEE 1532 programming standard. The IEEE 1532 standard adds programming instructions and associated data registers to devices that comply with the IEEE 1149.1 standard (JTAG). These instructions and registers extend the capabilities of the IEEE 1149.1 standard such that the Test Access Port (TAP) can be used for configuration activities. The IEEE 1532 standard greatly simplifies the programming algorithm, reducing the amount of time needed to implement microprocessor ISP.

# Implementation Overview

To implement device programming with a microprocessor, the user should first download the C-based STAPL player or DirectC code from the Microsemi SoC Products Group website. Refer to the website for future updates regarding the STAPL player and DirectC code.

http://www.microsemi.com/soc/download/program\_debug/stapl/default.aspx

http://www.microsemi.com/soc/download/program\_debug/directc/default.aspx

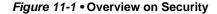

Using the easy-to-follow user's guide, create the low-level application programming interface (API) to provide the necessary basic functions. These API functions act as the interface between the programming software and the actual hardware (Figure 14-2).

Figure 14-2 • Device Programming Code Relationship

The API is then linked with the STAPL player or DirectC and compiled using the microprocessor's compiler. Once the entire code is compiled, the user must download the resulting binary into the MCU system's program memory (such as ROM, EEPROM, or flash). The system is now ready for programming.

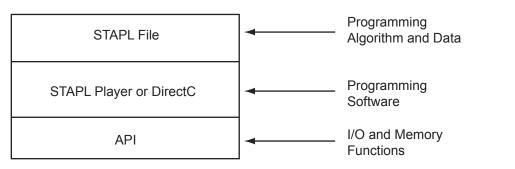

To program a design into the FPGA, the user creates a bitstream or STAPL file using the Microsemi Designer software, downloads it into the MCU system's volatile memory, and activates the stored programming binary file (Figure 14-3 on page 286). Once the programming is completed, the bitstream or STAPL file can be removed from the system, as the configuration profile is stored in the flash FPGA fabric and does not need to be reloaded at every system power-on.

#### STAPL vs. DirectC

Programming the low power flash devices is performed using DirectC or the STAPL player. Both tools use the STAPL file as an input. DirectC is a compiled language, whereas STAPL is an interpreted language. Microprocessors will be able to load the FPGA using DirectC much more quickly than STAPL. This speed advantage becomes more apparent when lower clock speeds of 8- or 16-bit microprocessors are used. DirectC also requires less memory than STAPL, since the programming algorithm is directly implemented. STAPL does have one advantage over DirectC—the ability to upgrade. When a new programming algorithm is required, the STAPL user simply needs to regenerate a STAPL file using the latest version of the Designer software and download it to the system. The DirectC user must download the latest version of DirectC from Microsemi, compile everything, and download the result into the system (Figure 14-4).

Figure 14-4 • STAPL vs. DirectC

# 17 – Power-Up/-Down Behavior of Low Power Flash Devices

## Introduction

Microsemi's low power flash devices are flash-based FPGAs manufactured on a 0.13  $\mu$ m process node. These devices offer a single-chip, reprogrammable solution and support Level 0 live at power-up (LAPU) due to their nonvolatile architecture.

Microsemi's low power flash FPGA families are optimized for logic area, I/O features, and performance. IGLOO® devices are optimized for power, making them the industry's lowest power programmable solution. IGLOO PLUS FPGAs offer enhanced I/O features beyond those of the IGLOO ultra-low power solution for I/O-intensive low power applications. IGLOO nano devices are the industry's lowest-power cost-effective solution. ProASIC3®L FPGAs balance low power with high performance. The ProASIC3 family is Microsemi's high-performance flash FPGA solution. ProASIC3 nano devices offer the lowest-cost solution with enhanced I/O capabilities.

Microsemi's low power flash devices exhibit very low transient current on each power supply during power-up. The peak value of the transient current depends on the device size, temperature, voltage levels, and power-up sequence.

The following devices can have inputs driven in while the device is not powered:

- · IGLOO (AGL015 and AGL030)

- · IGLOO nano (all devices)

- IGLOO PLUS (AGLP030, AGLP060, AGLP125)

- IGLOOe (AGLE600, AGLE3000)

- ProASIC3L (A3PE3000L)

- ProASIC3 (A3P015, A3P030)

- ProASIC3 nano (all devices)

- ProASIC3E (A3PE600, A3PE1500, A3PE3000)

- Military ProASIC3EL (A3PE600L, A3PE3000L, but not A3P1000)

- RT ProASIC3 (RT3PE600L, RT3PE3000L)

The driven I/Os do not pull up power planes, and the current draw is limited to very small leakage current, making them suitable for applications that require cold-sparing. These devices are hot-swappable, meaning they can be inserted in a live power system.<sup>1</sup>

For more details on the levels of hot-swap compatibility in Microsemi's low power flash devices, refer to the "Hot-Swap Support" section in the I/O Structures chapter of the FPGA fabric user's guide for the device you are using.

Figure 17-3 • I/O State when VCCI Is Powered before VCC

## **Power-Up to Functional Time**

At power-up, device I/Os exit the tristate mode and become functional once the last voltage supply in the power-up sequence (VCCI or VCC) reaches its functional activation level. The power-up—to—functional time is the time it takes for the last supply to power up from zero to its functional level. Note that the functional level of the power supply during power-up may vary slightly within the specification at different ramp-rates. Refer to Table 17-2 for the functional level of the voltage supplies at power-up.

Typical I/O behavior during power-up-to-functional time is illustrated in Figure 17-2 on page 311 and Figure 17-3.

Table 17-2 • Power-Up Functional Activation Levels for VCC and VCCI

| Device                                                                                                | VCC Functional<br>Activation Level (V) | VCCI Functional<br>Activation Level (V) |

|-------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.5 V* | 0.85 V ± 0.25 V                        | 0.9 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices running at VCC = 1.2 V*                          | 0.85 V ± 0.2 V                         | 0.9 V ± 0.15 V                          |

Note: \*V5 devices will require a 1.5 V VCC supply, whereas V2 devices can utilize either a 1.2 V or 1.5 V VCC.

Microsemi's low power flash devices meet Level 0 LAPU; that is, they can be functional prior to  $V_{CC}$  reaching the regulated voltage required. This important advantage distinguishes low power flash devices from their SRAM-based counterparts. SRAM-based FPGAs, due to their volatile technology, require hundreds of milliseconds after power-up to configure the design bitstream before they become functional. Refer to Figure 17-4 on page 313 and Figure 17-5 on page 314 for more information.