Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 71                                                                        |

| Number of Gates                | 125000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                         |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn125-zvqg100 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Global Resources in Low Power Flash Devices

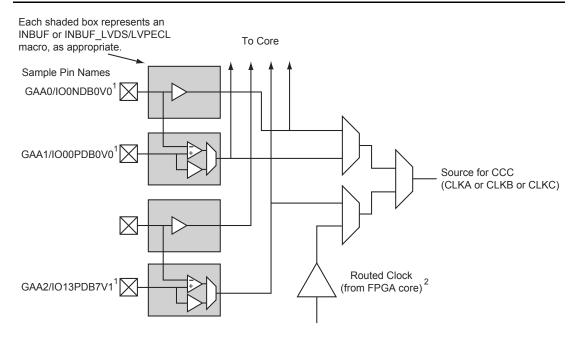

Figure 3-5 shows more detailed global input connections. It shows the global input pins connection to the northwest quadrant global networks. Each global buffer, as well as the PLL reference clock, can be driven from one of the following:

- · 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection (not supported for IGLOO nano or ProASIC3 nano devices)

- · The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

Note: Differential inputs are not supported for IGLOO nano or ProASIC3 nano devices.

Figure 3-5 • Global I/O Overview

Table 3-3 • Quadrant Global Pin Name

| I/O Type     | Beginning of I/O Name | Notes                                                      |

|--------------|-----------------------|------------------------------------------------------------|

| Single-Ended | GAAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAA1/IOuxwByVz        | quadrant global at a time                                  |

|              | GAA2/IOuxwByVz        |                                                            |

|              | GABO/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAB1/IOuxwByVz        | quadrant global at a time.                                 |

|              | GAB2/IOuxwByVz        |                                                            |

|              | GAC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a        |

|              | GAC1/IOuxwByVz        | quadrant global at a time.                                 |

|              | GAC2/IOuxwByVz        |                                                            |

|              | GBAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBA1/IOuxwByVz        | at a time.                                                 |

|              | GBA2/IOuxwByVz        |                                                            |

|              | GBBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBB1/IOuxwByVz        | at a time.                                                 |

|              | GBB2/IOuxwByVz        |                                                            |

|              | GBC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GBC1/IOuxwByVz        | at a time.                                                 |

|              | GBC2/IOuxwByVz        |                                                            |

|              | GDAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDA1/IOuxwByVz        | at a time.                                                 |

|              | GDA2/IOuxwByVz        |                                                            |

|              | GDBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDB1/IOuxwByVz        | at a time.                                                 |

|              | GDB2/IOuxwByVz        |                                                            |

|              | GDC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GDC1/IOuxwByVz        | at a time.                                                 |

|              | GDC2/IOuxwByVz        |                                                            |

|              | GEAO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEA1/IOuxwByVz        | at a time.                                                 |

|              | GEA2/IOuxwByVz        |                                                            |

|              | GEBO/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEB1/IOuxwByVz        | at a time.                                                 |

|              | GEB2/IOuxwByVz        |                                                            |

|              | GEC0/IOuxwByVz        | Only one of the I/Os can be directly connected to a global |

|              | GEC1/IOuxwByVz        | at a time.                                                 |

|              | GEC2/IOuxwByVz        |                                                            |

|              |                       |                                                            |

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

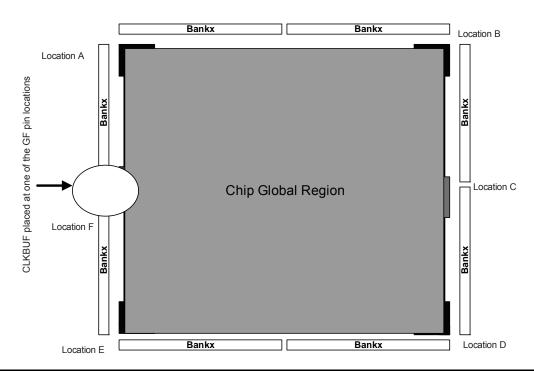

Figure 3-12 • Chip Global Region

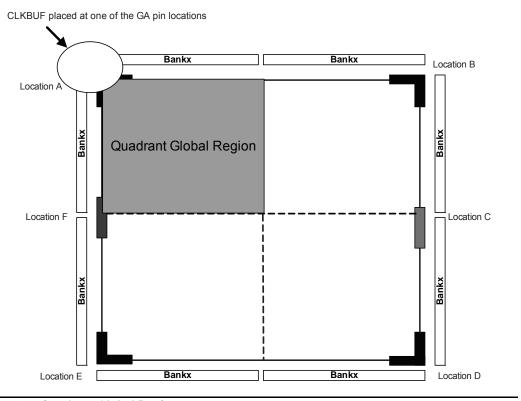

Figure 3-13 • Quadrant Global Region

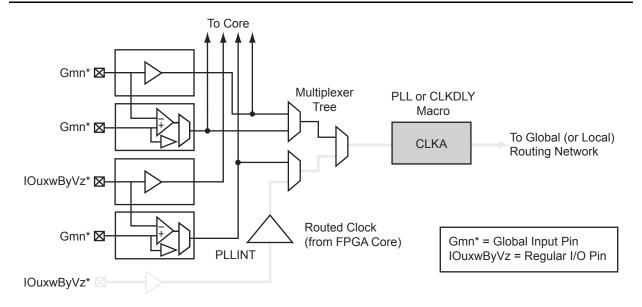

#### External I/O Clock Source

External I/O refers to regular I/O pins. The clock source is instantiated with one of the various INBUF options and accesses the CCCs via internal routing. The user has the option of assigning this input to any of the I/Os labeled with the I/O convention IOuxwByVz. Refer to the "User I/O Naming Conventions in I/O Structures" chapter of the appropriate device user's guide, and for Fusion, refer to the Fusion Family of Mixed Signal FPGAs datasheet for more information. Figure 4-11 gives a brief explanation of external I/O usage. Choosing this option provides the freedom of selecting any user I/O location but introduces additional delay because the signal connects to the routed clock input through internal routing before connecting to the CCC reference clock input.

For the External I/O option, the routed signal would be instantiated with a PLLINT macro before connecting to the CCC reference clock input. This instantiation is conveniently done automatically by SmartGen when this option is selected. Microsemi recommends using the SmartGen tool to generate the CCC macro. The instantiation of the PLLINT macro results in the use of the routed clock input of the I/O to connect to the PLL clock input. If not using SmartGen, manually instantiate a PLLINT macro before the PLL reference clock to indicate that the regular I/O driving the PLL reference clock should be used (see Figure 4-11 for an example illustration of the connections, shown in red).

In the above two options, the clock source must be instantiated with one of the various INBUF macros. The reference clock pins of the CCC functional block core macros must be driven by regular input macros (INBUFs), not clock input macros.

Figure 4-11 • Illustration of External I/O Usage

For Fusion devices, the input reference clock can also be from the embedded RC oscillator and crystal oscillator. In this case, the CCC configuration is the same as the hardwired I/O clock source, and users are required to instantiate the RC oscillator or crystal oscillator macro and connect its output to the input reference clock of the CCC block.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

## Loading the Configuration Register

The most important part of CCC dynamic configuration is to load the shift register properly with the configuration bits. There are different ways to access and load the configuration shift register:

- JTAG interface

- Logic core

- Specific I/O tiles

#### JTAG Interface

The JTAG interface requires no additional I/O pins. The JTAG TAP controller is used to control the loading of the CCC configuration shift register.

Low power flash devices provide a user interface macro between the JTAG pins and the device core logic. This macro is called UJTAG. A user should instantiate the UJTAG macro in his design to access the configuration register ports via the JTAG pins.

For more information on CCC dynamic reconfiguration using UJTAG, refer to the "UJTAG Applications in Microsemi's Low Power Flash Devices" section on page 297.

#### **Logic Core**

If the logic core is employed, the user must design a module to provide the configuration data and control the shifting and updating of the CCC configuration shift register. In effect, this is a user-designed TAP controller, which requires additional chip resources.

#### Specific I/O Tiles

If specific I/O tiles are used for configuration, the user must provide the external equivalent of a TAP controller. This does not require additional core resources but does use pins.

### Shifting the Configuration Data

To enter a new configuration, all 81 bits must shift in via SDIN. After all bits are shifted, SSHIFT must go LOW and SUPDATE HIGH to enable the new configuration. For simulation purposes, bits <71:73> and <77:80> are "don't care."

The SUPDATE signal must be LOW during any clock cycle where SSHIFT is active. After SUPDATE is asserted, it must go back to the LOW state until a new update is required.

## **PLL Configuration Bits Description**

Table 4-8 • Configuration Bit Descriptions for the CCC Blocks

| Config.<br>Bits | Signal                      | Name                | Description                                                                                                                |

|-----------------|-----------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| <88:87>         | GLMUXCFG [1:0] <sup>1</sup> | NGMUX configuration | The configuration bits specify the input clocks to the NGMUX (refer to Table 4-17 on page 94). <sup>2</sup>                |

| 86              | OCDIVHALF <sup>1</sup>      |                     | When the PLL is bypassed, the 100 MHz RC oscillator can be divided by the divider factor in Table 4-18 on page 95.         |

| 85              | OBDIVHALF <sup>1</sup>      |                     | When the PLL is bypassed, the 100 MHz RC oscillator can be divided by a 0.5 factor (refer to Table 4-18 on page 95).       |

| 84              | OADIVHALF <sup>1</sup>      |                     | When the PLL is bypassed, the 100 MHz RC oscillator can be divided by certain 0.5 factor (refer to Table 4-16 on page 94). |

#### Notes:

- 1. The <88:81> configuration bits are only for the Fusion dynamic CCC.

- This value depends on the input clock source, so Layout must complete before these bits can be set.

After completing Layout in Designer, generate the "CCC\_Configuration" report by choosing Tools > Report > CCC\_Configuration. The report contains the appropriate settings for these bits.

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

| Date                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                   | Page |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| v1.4<br>(December 2008) | The "CCC Support in Microsemi's Flash Devices" section was updated to include IGLOO nano and ProASIC3 nano devices.                                                                                                                                                                                                                                                                                                       | 63   |

|                         | Figure 4-2 • CCC Options: Global Buffers with No Programmable Delay was revised to add the CLKBIBUF macro.                                                                                                                                                                                                                                                                                                                | 64   |

|                         | The description of the reference clock was revised in Table 4-2 • Input and Output Description of the CLKDLY Macro.                                                                                                                                                                                                                                                                                                       | 65   |

|                         | Figure 4-7 • Clock Input Sources (30 k gates devices and below) is new. Figure 4-8 • Clock Input Sources Including CLKBUF, CLKBUF_LVDS/LVPECL, and CLKINT (60 k gates devices and above) applies to 60 k gate devices and above.                                                                                                                                                                                          | 72   |

|                         | The "IGLOO and ProASIC3" section was updated to include information for IGLOO nano devices.                                                                                                                                                                                                                                                                                                                               | 73   |

|                         | A note regarding Fusion CCCs was added to Figure 4-9 • Illustration of Hardwired I/O (global input pins) Usage for IGLOO and ProASIC3 devices 60 k Gates and Larger and the name of the figure was changed from Figure 4-8 • Illustration of Hardwired I/O (global input pins) Usage. Figure 4-10 • Illustration of Hardwired I/O (global input pins) Usage for IGLOO and ProASIC3 devices 30 k Gates and Smaller is new. | 74   |

|                         | Table 4-5 • Number of CCCs by Device Size and Package was updated to include IGLOO nano and ProASIC3 nano devices. Entries were added to note differences for the CS81, CS121, and CS201 packages.                                                                                                                                                                                                                        | 78   |

|                         | The "Clock Conditioning Circuits without Integrated PLLs" section was rewritten.                                                                                                                                                                                                                                                                                                                                          | 79   |

|                         | The "IGLOO and ProASIC3 CCC Locations" section was updated for nano devices.                                                                                                                                                                                                                                                                                                                                              | 81   |

|                         | Figure 4-13 • CCC Locations in the 15 k and 30 k Gate Devices was deleted.                                                                                                                                                                                                                                                                                                                                                | 4-20 |

| v1.3<br>(October 2008)  | This document was updated to include Fusion and RT ProASIC3 device information. Please review the document very carefully.                                                                                                                                                                                                                                                                                                | N/A  |

|                         | The "CCC Support in Microsemi's Flash Devices" section was updated.                                                                                                                                                                                                                                                                                                                                                       | 63   |

|                         | In the "Global Buffer with Programmable Delay" section, the following sentence was changed from:  "In this case, the I/O must be placed in one of the dedicated global I/O locations."                                                                                                                                                                                                                                    | 64   |

|                         | To "In this case, the software will automatically place the dedicated global I/O in the appropriate locations."                                                                                                                                                                                                                                                                                                           |      |

|                         | Figure 4-4 • CCC Options: Global Buffers with PLL was updated to include OADIVRST and OADIVHALF.                                                                                                                                                                                                                                                                                                                          | 67   |

|                         | In Figure 4-6 • CCC with PLL Block "fixed delay" was changed to "programmable delay".                                                                                                                                                                                                                                                                                                                                     | 67   |

|                         | Table 4-3 • Input and Output Signals of the PLL Block was updated to include OADIVRST and OADIVHALF descriptions.                                                                                                                                                                                                                                                                                                         | 68   |

|                         | Table 4-8 • Configuration Bit Descriptions for the CCC Blocks was updated to include configuration bits 88 to 81. Note 2 is new. In addition, the description for bit <76:74> was updated.                                                                                                                                                                                                                                | 90   |

|                         | Table 4-16 • Fusion Dynamic CCC Clock Source Selection and Table 4-17 • Fusion Dynamic CCC NGMUX Configuration are new.                                                                                                                                                                                                                                                                                                   | 94   |

|                         | Table 4-18 • Fusion Dynamic CCC Division by Half Configuration and Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families are new.                                                                                                                                                                                                                                                               | 95   |

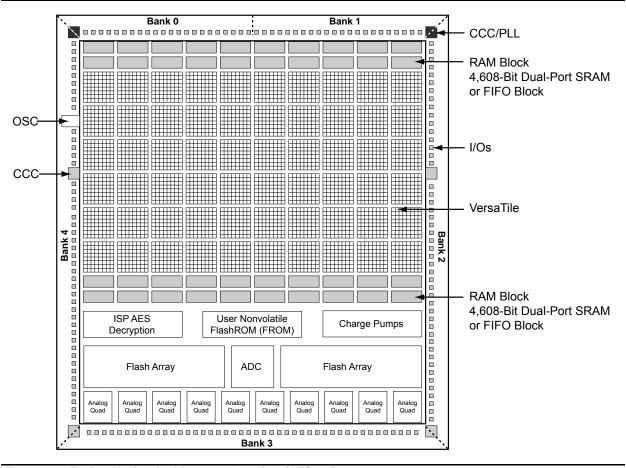

Figure 6-2 • Fusion Device Architecture Overview (AFS600)

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

## **SRAM/FIFO Support in Flash-Based Devices**

The flash FPGAs listed in Table 6-1 support SRAM and FIFO blocks and the functions described in this document.

Table 6-1 • Flash-Based FPGAs

| Series   | Family*              | Description                                                                                                                                                                                    |

|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                                                                                                                                        |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion   | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 6-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

SRAM and FIFO Memories in Microsemi's Low Power Flash Devices

Table 6-8 and Table 6-9 show the maximum potential width and depth configuration for each device. Note that 15 k and 30 k gate devices do not support RAM or FIFO.

Table 6-8 • Memory Availability per IGLOO and ProASIC3 Device

| De                                | vice                                   |                   | Maximum Potential Width <sup>1</sup> |                | Maximum Potential Wie |       | Maximum Potential I | Depth <sup>2</sup> |

|-----------------------------------|----------------------------------------|-------------------|--------------------------------------|----------------|-----------------------|-------|---------------------|--------------------|

| IGLOO<br>IGLOO nano<br>IGLOO PLUS | ProASIC3<br>ProASIC3 nano<br>ProASIC3L | RAM<br>Block<br>s | Depth                                | Width          | Depth                 | Width |                     |                    |

| AGL060<br>AGLN060<br>AGLP060      | A3P060<br>A3PN060                      | 4                 | 256                                  | 72 (4×18)      | 16,384 (4,096×4)      | 1     |                     |                    |

| AGL125<br>AGLN125<br>AGLP125      | A3P125<br>A3PN125                      | 8                 | 256                                  | 144 (8×18)     | 32,768 (4,094×8)      | 1     |                     |                    |

| AGL250<br>AGLN250                 | A3P250/L<br>A3PN250                    | 8                 | 256                                  | 144 (8×18)     | 32,768 (4,096×8)      | 1     |                     |                    |

| AGL400                            | A3P400                                 | 12                | 256                                  | 216 (12×18)    | 49,152 (4,096×12)     | 1     |                     |                    |

| AGL600                            | A3P600/L                               | 24                | 256                                  | 432 (24×18)    | 98,304 (4,096×24)     | 1     |                     |                    |

| AGL1000                           | A3P1000/L                              | 32                | 256                                  | 576 (32×18)    | 131,072 (4,096×32)    | 1     |                     |                    |

| AGLE600                           | A3PE600                                | 24                | 256                                  | 432 (24×18)    | 98,304 (4,096×24)     | 1     |                     |                    |

|                                   | A3PE1500                               | 60                | 256                                  | 1,080 (60×18)  | 245,760 (4,096×60)    | 1     |                     |                    |

| AGLE3000                          | A3PE3000/L                             | 112               | 256                                  | 2,016 (112×18) | 458,752 (4,096×112)   | 1     |                     |                    |

#### Notes:

- 1. Maximum potential width uses the two-port configuration.

- 2. Maximum potential depth uses the dual-port configuration.

Table 6-9 • Memory Availability per Fusion Device

|         |            | Maximum Potential Width <sup>1</sup> |               | Maximum Potential [ | Depth <sup>2</sup> |

|---------|------------|--------------------------------------|---------------|---------------------|--------------------|

| Device  | RAM Blocks | Depth                                | Width         | Depth               | Width              |

| AFS090  | 6          | 256                                  | 108 (6×18)    | 24,576 (4,094×6)    | 1                  |

| AFS250  | 8          | 256                                  | 144 (8×18)    | 32,768 (4,094×8)    | 1                  |

| AFS600  | 24         | 256                                  | 432 (24×18)   | 98,304 (4,096×24)   | 1                  |

| AFS1500 | 60         | 256                                  | 1,080 (60×18) | 245,760 (4,096×60)  | 1                  |

#### Notes:

- 1. Maximum potential width uses the two-port configuration.

- 2. Maximum potential depth uses the dual-port configuration.

# **List of Changes**

The following table lists critical changes that were made in each revision of the chapter.

| Date      | Changes                                                                                                                                                                                                                                                                                                | Page |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010 | FlashPro4 is a replacement for FlashPro3 and has been added to this chapter. FlashPro is no longer available.                                                                                                                                                                                          | N/A  |

|           | The chapter was updated to include SmartFusion devices.                                                                                                                                                                                                                                                | N/A  |

|           | The following were deleted:                                                                                                                                                                                                                                                                            | N/A  |

|           | "Live at Power-Up (LAPU) or Boot PROM" section                                                                                                                                                                                                                                                         |      |

|           | "Design Security" section                                                                                                                                                                                                                                                                              |      |

|           | Table 14-2 • Programming Features for Actel Devices and much of the text in the "Programming Features for Microsemi Devices" section                                                                                                                                                                   |      |

|           | "Programming Flash FPGAs" section                                                                                                                                                                                                                                                                      |      |

|           | "Return Material Authorization (RMA) Policies" section                                                                                                                                                                                                                                                 |      |

|           | The "Device Programmers" section was revised.                                                                                                                                                                                                                                                          | 225  |

|           | The Independent Programming Centers information was removed from the "Volume Programming Services" section.                                                                                                                                                                                            | 226  |

|           | Table 10-3 • Programming Solutions was revised to add FlashPro4 and note that FlashPro is discontinued. A note was added for FlashPro Lite regarding power supply requirements.                                                                                                                        | 227  |

|           | Most items were removed from Table 10-4 • Programming Ordering Codes, including FlashPro3 and FlashPro.                                                                                                                                                                                                | 228  |

|           | The "Programmer Device Support" section was deleted and replaced with a reference to the Microsemi SoC Products Group website for the latest information.                                                                                                                                              | 228  |

|           | The "Certified Programming Solutions" section was revised to add FlashPro4 and remove Silicon Sculptor I and Silicon Sculptor 6X. Reference to <i>Programming and Functional Failure Guidelines</i> was added.                                                                                         | 228  |

|           | The file type *.pdb was added to the "Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)" section.                                                                                                                                                        | 229  |

|           | Instructions on cleaning and careful insertion were added to the "Perform Routine Hardware Self-Diagnostic Test" section. Information was added regarding testing Silicon Sculptor programmers with an adapter module installed before every programming session verifying their calibration annually. | 229  |

|           | The "Signal Integrity While Using ISP" section is new.                                                                                                                                                                                                                                                 | 230  |

|           | The "Programming Failure Allowances" section was revised.                                                                                                                                                                                                                                              | 230  |

### Cortex-M1 Device Security

Cortex-M1—enabled devices are shipped with the following security features:

- FPGA array enabled for AES-encrypted programming and verification

- FlashROM enabled for AES-encrypted Write and Verify

- Fusion Embedded Flash Memory enabled for AES-encrypted Write

## **AES Encryption of Programming Files**

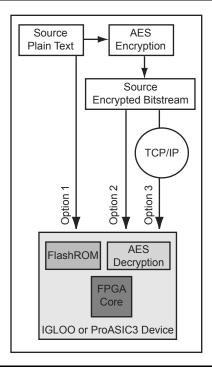

Low power flash devices employ AES as part of the security mechanism that prevents invasive and noninvasive attacks. The mechanism entails encrypting the programming file with AES encryption and then passing the programming file through the AES decryption core, which is embedded in the device. The file is decrypted there, and the device is successfully programmed. The AES master key is stored in on-chip nonvolatile memory (flash). The AES master key can be preloaded into parts in a secure programming environment (such as the Microsemi In-House Programming center), and then "blank" parts can be shipped to an untrusted programming or manufacturing center for final personalization with an AES-encrypted bitstream. Late-stage product changes or personalization can be implemented easily and securely by simply sending a STAPL file with AES-encrypted data. Secure remote field updates over public networks (such as the Internet) are possible by sending and programming a STAPL file with AES-encrypted data.

The AES key protects the programming data for file transfer into the device with 128-bit AES encryption. If AES encryption is used, the AES key is stored or preprogrammed into the device. To program, you must use an AES-encrypted file, and the encryption used on the file must match the encryption key already in the device.

The AES key is protected by a FlashLock security Pass Key that is also implemented in each device. The AES key is always protected by the FlashLock Key, and the AES-encrypted file does NOT contain the FlashLock Key. This FlashLock Pass Key technology is exclusive to the Microsemi flash-based device families. FlashLock Pass Key technology can also be implemented without the AES encryption option, providing a choice of different security levels.

In essence, security features can be categorized into the following three options:

- AES encryption with FlashLock Pass Key protection

- FlashLock protection only (no AES encryption)

- No protection

Each of the above options is explained in more detail in the following sections with application examples and software implementation options.

## Advanced Encryption Standard

The 128-bit AES standard (FIPS-192) block cipher is the NIST (National Institute of Standards and Technology) replacement for DES (Data Encryption Standard FIPS46-2). AES has been designed to protect sensitive government information well into the 21st century. It replaces the aging DES, which NIST adopted in 1977 as a Federal Information Processing Standard used by federal agencies to protect sensitive, unclassified information. The 128-bit AES standard has 3.4 × 10<sup>38</sup> possible 128-bit key variants, and it has been estimated that it would take 1,000 trillion years to crack 128-bit AES cipher text using exhaustive techniques. Keys are stored (securely) in low power flash devices in nonvolatile flash memory. All programming files sent to the device can be authenticated by the part prior to programming to ensure that bad programming data is not loaded into the part that may possibly damage it. All programming verification is performed on-chip, ensuring that the contents of low power flash devices remain secure.

Microsemi has implemented the 128-bit AES (Rijndael) algorithm in low power flash devices. With this key size, there are approximately  $3.4\times10^{38}$  possible 128-bit keys. DES has a 56-bit key size, which provides approximately  $7.2\times10^{16}$  possible keys. In their AES fact sheet, the National Institute of Standards and Technology uses the following hypothetical example to illustrate the theoretical security provided by AES. If one were to assume that a computing system existed that could recover a DES key in a second, it would take that same machine approximately 149 trillion years to crack a 128-bit AES key. NIST continues to make their point by stating the universe is believed to be less than 20 billion years old.  $^1$

ProASIC3 nano FPGA Fabric User's Guide

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level (Figure 11-12). Click **Next**.

If you want to select different options for the FPGA and/or FlashROM, this can be set by clicking **Custom Level**. Refer to the "Advanced Options" section on page 256 for different custom security level options and descriptions of each.

Figure 11-12 • Medium Security Level Selected for Low Power Flash Devices

Figure 12-2 shows different applications for ISP programming.

- 1. In a trusted programming environment, you can program the device using the unencrypted (plaintext) programming file.

- 2. You can program the AES Key in a trusted programming environment and finish the final programming in an untrusted environment using the AES-encrypted (cipher text) programming file.

- 3. For the remote ISP updating/reprogramming, the AES Key stored in the device enables the encrypted programming bitstream to be transmitted through the untrusted network connection.

Microsemi low power flash devices also provide the unique Microsemi FlashLock feature, which protects the Pass Key and AES Key. Unless the original FlashLock Pass Key is used to unlock the device, security settings cannot be modified. Microsemi does not support read-back of FPGA core-programmed data; however, the FlashROM contents can selectively be read back (or disabled) via the JTAG port based on the security settings established by the Microsemi Designer software. Refer to the "Security in Low Power Flash Devices" section on page 235 for more information.

Figure 12-2 • Different ISP Use Models

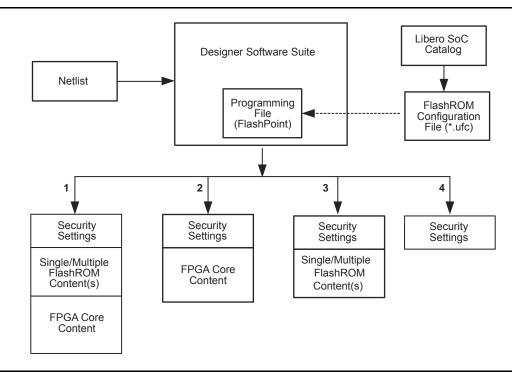

- 3. A single STAPL file or multiple STAPL files with multiple FlashROM contents. A single STAPL file will be generated if the device serialization feature is not used. You can program the whole FlashROM or selectively program individual pages.

- A single STAPL file to configure the security settings for the device, such as the AES Key and/or Pass Key.

Figure 12-4 • Flexible Programming File Generation for Different Applications

## **Programming Solution**

For device programming, any IEEE 1532–compliant programmer can be used; however, the FlashPro4/3/3X programmer must be used to control the low power flash device's rich security features and FlashROM programming options. The FlashPro4/3/3X programmer is a low-cost portable programmer for the Microsemi flash families. It can also be used with a powered USB hub for parallel programming. General specifications for the FlashPro4/3/3X programmer are as follows:

- Programming clock TCK is used with a maximum frequency of 20 MHz, and the default frequency is 4 MHz.

- Programming file STAPL

- Daisy chain Supported. You can use the ChainBuilder software to build the programming file for the chain.

- Parallel programming Supported. Multiple FlashPro4/3/3X programmers can be connected together using a powered USB hub or through the multiple USB ports on the PC.

- Power supply The target board must provide VCC, VCCI, VPUMP, and VJTAG during programming. However, if there is only one device on the target board, the FlashPro4/3/3X programmer can generate the required VPUMP voltage from the USB port.

## **ISP Programming Header Information**

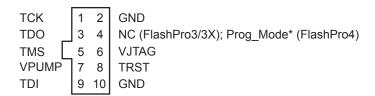

The FlashPro4/3/3X programming cable connector can be connected with a 10-pin, 0.1"-pitch programming header. The recommended programming headers are manufactured by AMP (103310-1) and 3M (2510-6002UB). If you have limited board space, you can use a compact programming header manufactured by Samtec (FTSH-105-01-L-D-K). Using this compact programming header, you are required to order an additional header adapter manufactured by Microsemi SoC Products Group (FP3-10PIN-ADAPTER-KIT).

Existing ProASICPLUS family customers who are using the Samtec Small Programming Header (FTSH-113-01-L-D-K) and are planning to migrate to IGLOO or ProASIC3 devices can also use FP3-10PIN-ADAPTER-KIT.

Table 12-3 • Programming Header Ordering Codes

| Manufacturer | Part Number           | Description                                                                                                                                                                                                                                                                                                                                        |

|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP          | 103310-1              | 10-pin, 0.1"-pitch cable header (right-angle PCB mount angle)                                                                                                                                                                                                                                                                                      |

| ЗМ           | 2510-6002UB           | 10-pin, 0.1"-pitch cable header (straight PCB mount angle)                                                                                                                                                                                                                                                                                         |

| Samtec       | FTSH-113-01-L-D-K     | Small programming header supported by FlashPro and Silicon Sculptor                                                                                                                                                                                                                                                                                |

| Samtec       | FTSH-105-01-L-D-K     | Compact programming header                                                                                                                                                                                                                                                                                                                         |

| Samtec       | FFSD-05-D-06.00-01-N  | 10-pin cable with 50 mil pitch sockets; included in FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                         |

| Microsemi    | FP3-10PIN-ADAPTER-KIT | Transition adapter kit to allow FP3 to be connected to a micro 10-pin header (50 mil pitch). Includes a 6 inch Samtec FFSD-05-D-06.00-01-N cable in the kit. The transition adapter board was previously offered as FP3-26PIN-ADAPTER and includes a 26-pin adapter for design transitions from ProASICPLUS based boards to ProASIC3 based boards. |

Note: \*Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 12-5 • Programming Header (top view)

Table 12-4 • Programming Header Pin Numbers and Description

| Pin | Signal             | Source                  | Description                                                                                                                          |

|-----|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TCK                | Programmer              | JTAG Clock                                                                                                                           |

| 2   | GND <sup>1</sup>   | -                       | Signal Reference                                                                                                                     |

| 3   | TDO                | Target Board            | Test Data Output                                                                                                                     |

| 4   | NC                 | -                       | No Connect (FlashPro3/3X); Prog_Mode (FlashPro4). See note associated with Figure 12-5 on page 269 regarding Prog_Mode on FlashPro4. |

| 5   | TMS                | Programmer              | Test Mode Select                                                                                                                     |

| 6   | VJTAG              | Target Board            | JTAG Supply Voltage                                                                                                                  |

| 7   | VPUMP <sup>2</sup> | Programmer/Target Board | Programming Supply Voltage                                                                                                           |

| 8   | nTRST              | Programmer              | JTAG Test Reset (Hi-Z with 10 $k\Omega$ pull-down, HIGH, LOW, or toggling)                                                           |

| 9   | TDI                | Programmer              | Test Data Input                                                                                                                      |

| 10  | GND <sup>1</sup>   | _                       | Signal Reference                                                                                                                     |

#### Notes:

- 1. Both GND pins must be connected.

- 2. FlashPro4/3/3X can provide VPUMP if there is only one device on the target board.

| Date                     | Changes                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010<br>(continued) | The "Chain Integrity Test Error Analyze Chain Failure" section was renamed to the "Scan Chain Failure" section, and the Analyze Chain command was changed to Scan Chain. It was noted that occasionally a faulty programmer can cause scan chain failures.                                                                                                                                   | 272  |

| v1.5<br>(August 2009)    | The "CoreMP7 Device Security" section was removed from "Security in ARM-Enabled Low Power Flash Devices", since M7-enabled devices are no longer supported.                                                                                                                                                                                                                                  | 265  |

| v1.4<br>(December 2008)  | The "ISP Architecture" section was revised to include information about core voltage for IGLOO V2 and ProASIC3L devices, as well as 50 mV increments allowable in Designer software.                                                                                                                                                                                                         | 261  |

|                          | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                            | 262  |

|                          | A second capacitor was added to Figure 12-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                                                                                                  | 271  |

| v1.3<br>(October 2008)   | The "ISP Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                  | 262  |

| v1.2<br>(June 2008)      | The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs Supporting ISP:  • ProASIC3L was updated to include 1.5 V.  • The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                    | 262  |

| v1.1<br>(March 2008)     | The "ISP Architecture" section was updated to included the IGLOO PLUS family in the discussion of family-specific support. The text, "When 1.2 V is used, the device can be reprogrammed in-system at 1.5 V only," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when all supplies (VCC, VCCI, and VJTAG) are at 1.5 V." | 261  |

|                          | The "ISP Support in Flash-Based Devices" section and Table 12-1 • Flash-Based FPGAs Supporting ISP were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 262  |

|                          | The "Security" section was updated to mention that 15 k gate devices do not have a built-in 128-bit decryption core.                                                                                                                                                                                                                                                                         | 264  |

|                          | Table 12-2 • Power Supplies was revised to remove the Normal Operation column and add a table note stating, "All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation."                                                                                                                                                                           | 263  |

|                          | The "ISP Programming Header Information" section was revised to change FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT. Table 12-3 • Programming Header Ordering Codes was updated with the same change, as well as adding the part number FFSD-05-D-06.00-01-N, a 10-pin cable with 50-mil-pitch sockets.                                                                                        | 269  |

|                          | The "Board-Level Considerations" section was updated to describe connecting two capacitors in parallel across VPUMP and GND for proper programming.                                                                                                                                                                                                                                          | 271  |

| v1.0<br>(January 2008)   | Information was added to the "Programming Voltage (VPUMP) and VJTAG" section about the JTAG interface pin.                                                                                                                                                                                                                                                                                   | 263  |

| 51900055-2/7.06          | ACTgen was changed to SmartGen.                                                                                                                                                                                                                                                                                                                                                              | N/A  |

|                          | In Figure 12-6 • Board Layout and Programming Header Top View, the order of the text was changed to:  VJTAG from the target board  VCCI from the target board  VCC from the target board                                                                                                                                                                                                     | 271  |

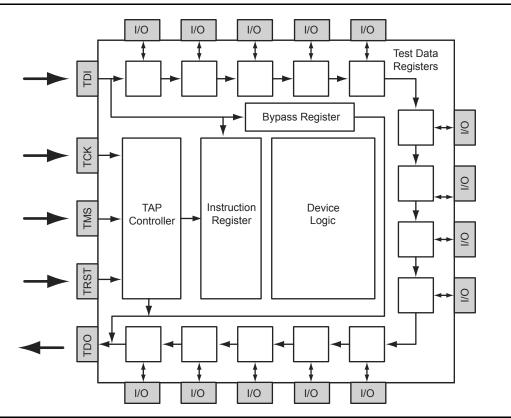

Figure 15-2 • Boundary Scan Chain

## **Board-Level Recommendations**

Table 15-3 gives pull-down recommendations for the TRST and TCK pins.

Table 15-3 • TRST and TCK Pull-Down Recommendations

| VJTAG          | Tie-Off Resistance*          |

|----------------|------------------------------|

| VJTAG at 3.3 V | 200 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 2.5 V | 200 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.8 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.5 V | 500 $\Omega$ to 1 k $\Omega$ |

| VJTAG at 1.2 V | TBD                          |

Note: Equivalent parallel resistance if more than one device is on JTAG chain (Figure 15-3)

UJTAG Applications in Microsemi's Low Power Flash Devices

## **UJTAG Support in Flash-Based Devices**

The flash-based FPGAs listed in Table 16-1 support the UJTAG feature and the functions described in this document.

Table 16-1 • Flash-Based FPGAs

| Series | Family*                                 | Description                                                                                                                                                                                    |

|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IGLOO  | IGLOO                                   | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology                                                                                                                              |

|        | IGLOOe                                  | Higher density IGLOO FPGAs with six PLLs and additional I/O standards                                                                                                                          |

|        | IGLOO nano                              | The industry's lowest-power, smallest-size solution                                                                                                                                            |

|        | IGLOO PLUS                              | IGLOO FPGAs with enhanced I/O capabilities                                                                                                                                                     |

|        | Low power, high-performance 1.5 V FPGAs |                                                                                                                                                                                                |

|        | ProASIC3E                               | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards                                                                                                                       |

|        | ProASIC3 nano                           | Lowest-cost solution with enhanced I/O capabilities                                                                                                                                            |

|        | ProASIC3L                               | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology                                                                                                                          |

|        | RT ProASIC3                             | Radiation-tolerant RT3PE600L and RT3PE3000L                                                                                                                                                    |

|        | Military ProASIC3/EL                    | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                          |

|        | Automotive ProASIC3                     | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                           |

| Fusion | Fusion                                  | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 16-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

## **ProASIC3 Terminology**

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 16-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.