Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

EXF

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | ·                                                                        |

| Total RAM Bits                 | 36864                                                                    |

| Number of I/O                  | 68                                                                       |

| Number of Gates                | 250000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | -20°C ~ 85°C (TJ)                                                        |

| Package / Case                 | 100-TQFP                                                                 |

| Supplier Device Package        | 100-VQFP (14x14)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn250-2vq100 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Introduction

## Contents

This user's guide contains information to help designers understand and use Microsemi's ProASIC<sup>®</sup>3 nano devices. Each chapter addresses a specific topic. Most of these chapters apply to other Microsemi device families as well. When a feature or description applies only to a specific device family, this is made clear in the text.

## **Revision History**

The revision history for each chapter is listed at the end of the chapter. Most of these chapters were formerly included in device handbooks. Some were originally application notes or information included in device datasheets.

A "Summary of Changes" table at the end of this user's guide lists the chapters that were changed in each revision of the document, with links to the "List of Changes" sections for those chapters.

# **Related Information**

Refer to the *ProASIC3 nano Low Power Flash FPGAs* datasheet for detailed specifications, timing, and package and pin information.

The website for ProASIC3 nano devices is /www.microsemi.com/soc/products/pa3nano/default.aspx.

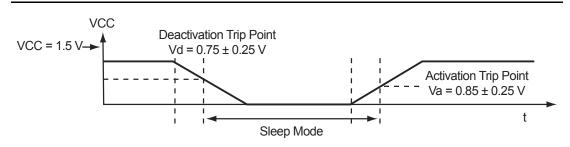

*Figure 2-5* • Entering and Exiting Sleep Mode—Typical Timing Diagram

## **Shutdown Mode**

For all ProASIC3/E and ProASIC3 nano devices, shutdown mode can be entered by turning off all power supplies when device functionality is not needed. Cold-sparing and hot-insertion features in ProASIC3 nano devices enable the device to be powered down without turning off the entire system. When power returns, the live at power-up feature enables immediate operation of the device.

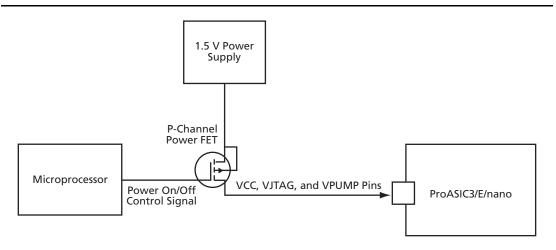

### Using Sleep Mode or Shutdown Mode in the System

Depending on the power supply and components used in an application, there are many ways to turn the power supplies connected to the device on or off. For example, Figure 2-6 shows how a microprocessor is used to control a power FET. It is recommended that power FETs with low on resistance be used to perform the switching action.

Figure 2-6 • Controlling Power On/Off State Using Microprocessor and Power FET

Global Resources in Low Power Flash Devices

| Differential I/O Pairs | GAAO/IOuxwByVz | The output of the different pair will drive the global. |

|------------------------|----------------|---------------------------------------------------------|

|                        | ,              |                                                         |

|                        | GAA1/IOuxwByVz |                                                         |

|                        | GABO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAB1/IOuxwByVz |                                                         |

|                        | GACO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GAC1/IOuxwByVz |                                                         |

|                        | GBAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBA1/IOuxwByVz |                                                         |

|                        | GBBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBB1/IOuxwByVz |                                                         |

|                        | GBCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GBC1/IOuxwByVz |                                                         |

|                        | GDAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDA1/IOuxwByVz |                                                         |

|                        | GDBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDB1/IOuxwByVz |                                                         |

|                        | GDCO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GDC1/IOuxwByVz |                                                         |

|                        | GEAO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEA1/IOuxwByVz |                                                         |

|                        | GEBO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEB1/IOuxwByVz |                                                         |

|                        | GECO/IOuxwByVz | The output of the different pair will drive the global. |

|                        | GEC1/IOuxwByVz |                                                         |

#### Table 3-3 • Quadrant Global Pin Name (continued)

Note: Only one of the I/Os can be directly connected to a quadrant at a time.

### **Unused Global I/O Configuration**

The unused clock inputs behave similarly to the unused Pro I/Os. The Microsemi Designer software automatically configures the unused global pins as inputs with pull-up resistors if they are not used as regular I/O.

## I/O Banks and Global I/O Standards

In low power flash devices, any I/O or internal logic can be used to drive the global network. However, only the global macro placed at the global pins will use the hardwired connection between the I/O and global network. Global signal (signal driving a global macro) assignment to I/O banks is no different from regular I/O assignment to I/O banks with the exception that you are limited to the pin placement location available. Only global signals compatible with both the VCCI and VREF standards can be assigned to the same bank.

YB and YC are identical to GLB and GLC, respectively, with the exception of a higher selectable final output delay. The SmartGen PLL Wizard will configure these outputs according to user specifications and can enable these signals with or without the enabling of Global Output Clocks.

The above signals can be enabled in the following output groupings in both internal and external feedback configurations of the static PLL:

- One output GLA only

- Two outputs GLA + (GLB and/or YB)

- Three outputs GLA + (GLB and/or YB) + (GLC and/or YC)

## PLL Macro Block Diagram

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global network access, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC). There are delay elements in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven in the following ways:

- By an INBUF\* macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

- 2. Directly from the FPGA core.

- 3. From an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

During power-up, the PLL outputs will toggle around the maximum frequency of the voltage-controlled oscillator (VCO) gear selected. Toggle frequencies can range from 40 MHz to 250 MHz. This will continue as long as the clock input (CLKA) is constant (HIGH or LOW). This can be prevented by LOW assertion of the POWERDOWN signal.

The visual PLL configuration in SmartGen, a component of the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user.

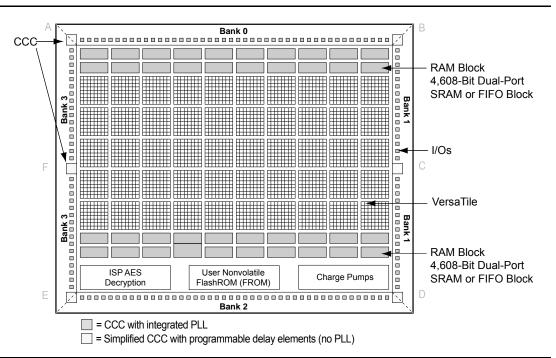

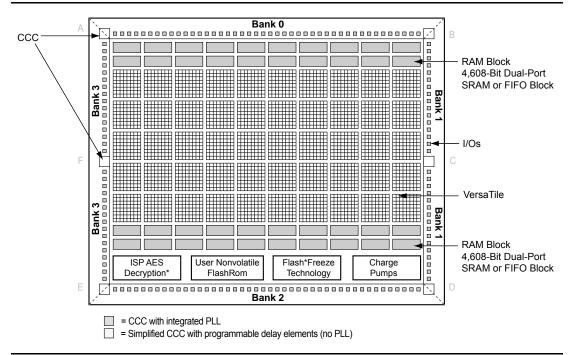

## **Fusion CCC Locations**

Fusion devices have six CCCs: one in each of the four corners and one each in the middle of the east and west sides of the device (Figure 4-17 and Figure 4-18). The device can have one integrated PLL in the middle of the west side of the device or two integrated PLLs in the middle of the east and west sides of the device (middle right and middle left).

*Figure 4-17* • CCC Locations in Fusion Family Devices (AFS090, AFS250, M1AFS250)

Figure 4-18 • CCC Locations in Fusion Family Devices (except AFS090, AFS250, M1AFS250)

Figure 4-36 • Second-Stage PLL Showing Input of 256 MHz from First Stage and Final Output of 280 MHz

Figure 4-37 shows the simulation results, where the first PLL's output period is 3.9 ns (~256 MHz), and the stage 2 (final) output period is 3.56 ns (~280 MHz).

Stage 2 Output Clock Period Stage 1 Output Clock Period

Figure 4-37 • Model Sim Simulation Results

## Microsemi

FlashROM in Microsemi's Low Power Flash Devices

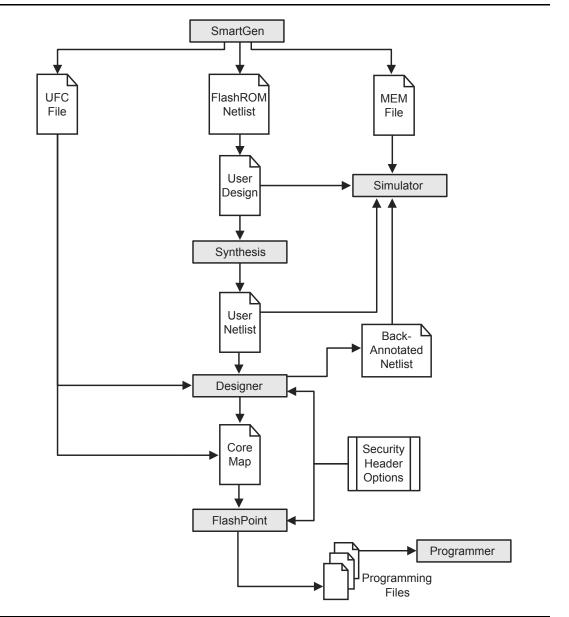

# **FlashROM Design Flow**

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

- If one of the registers has a PRE pin, all the other registers that are candidates for combining in the I/O must have a PRE pin.

- If one of the registers has neither a CLR nor a PRE pin, all the other registers that are candidates for combining must have neither a CLR nor a PRE pin.

- If the clear or preset pins are present, they must have the same polarity.

- If the clear or preset pins are present, they must be driven by the same signal (net).

- 3. For single-tile devices (10 k, 15 k, and 20 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock function (both CLR and CLK are shared among all registers):

- Both the Output and Output Enable registers must not have an E pin (clock enable).

- 4. For dual-tile devices (60 k, 125 k, and 250 k): Registers connected to an I/O on the Output and Output Enable pins must have the same clock and enable function:

- Both the Output and Output Enable registers must have an E pin (clock enable), or none at all.

- If the E pins are present, they must have the same polarity. The CLK pins must also have the same polarity.

In some cases, the user may want registers to be combined with the input of a bibuf while maintaining the output as-is. This can be achieved by using PDC commands as follows:

```

set_io <signal name> -REGISTER yes -----register will combine

set_preserve <signal name> ----register will not combine

```

### Weak Pull-Up and Weak Pull-Down Resistors

nano devices support optional weak pull-up and pull-down resistors on each I/O pin. When the I/O is pulled up, it is connected to the  $V_{CCI}$  of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to the datasheet for more information.

For low power applications and when using IGLOO nano devices, configuration of the pull-up or pulldown of the I/O can be used to set the I/O to a known state while the device is in Flash\*Freeze mode. Refer to "Flash\*Freeze Technology and Low Power Modes" in an applicable FPGA fabric user's guide for more information.

The Flash\*Freeze (FF) pin cannot be configured with a weak pull-down or pull-up I/O attribute, as the signal needs to be driven at all times.

### **Output Slew Rate Control**

The slew rate is the amount of time an input signal takes to get from logic LOW to logic HIGH or vice versa.

It is commonly defined as the propagation delay between 10% and 90% of the signal's voltage swing. Slew rate control is available for the output buffers of low power flash devices. The output buffer has a programmable slew rate for both HIGH-to-LOW and LOW-to-HIGH transitions.

The slew rate can be implemented by using a PDC command (Table 7-5 on page 163), setting it "High" or "Low" in the I/O Attribute Editor in Designer, or instantiating a special I/O macro. The default slew rate value is "High."

Microsemi recommends the high slew rate option to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected.

### **Output Drive**

The output buffers of nano devices can provide multiple drive strengths to meet signal integrity requirements. The LVTTL and LVCMOS (except 1.2 V LVCMOS) standards have selectable drive strengths.

Drive strength should also be selected according to the design requirements and noise immunity of the system.

### **Device Programmers**

#### Single Device Programmer

Single device programmers are used to program a device before it is mounted on the system board.

The advantage of using device programmers is that no programming hardware is required on the system board. Therefore, no additional components or board space are required.

Adapter modules are purchased with single device programmers to support the FPGA packages used. The FPGA is placed in the adapter module and the programming software is run from a PC. Microsemi supplies the programming software for all of the Microsemi programmers. The software allows for the selection of the correct die/package and programming files. It will then program and verify the device.

Single-site programmers

A single-site programmer programs one device at a time. Microsemi offers Silicon Sculptor 3, built by BP Microsystems, as a single-site programmer. Silicon Sculptor 3 and associated software are available only from Microsemi.

- Advantages: Lower cost than multi-site programmers. No additional overhead for programming on the system board. Allows local control of programming and data files for maximum security. Allows on-demand programming on-site.

- Limitations: Only programs one device at a time.

- Multi-site programmers

Often referred to as batch or gang programmers, multi-site programmers can program multiple devices at the same time using the same programming file. This is often used for large volume programming and by programming houses. The sites often have independent processors and memory enabling the sites to operate concurrently, meaning each site may start programming the same file independently. This enables the operator to change one device while the other sites continue programming, which increases throughput. Multiple adapter modules for the same package are required when using a multi-site programmer. Silicon Sculptor I, II, and 3 programmers can be cascaded to program multiple devices in a chain. Multi-site programmers, such as the BP2610 and BP2710, can also be purchased from BP Microsystems. When using BP Microsystems multi-site programmers, users must use programming adapter modules available only from Microsemi. Visit the Microsemi SoC Products Group website to view the part numbers of the desired adapter module:

http://www.microsemi.com/soc/products/hardware/program\_debug/ss/modules.aspx.

Also when using BP Microsystems programmers, customers must use Microsemi programming software to ensure the best programming result will occur.

- Advantages: Provides the capability of programming multiple devices at the same time. No

additional overhead for programming on the system board. Allows local control of

programming and data files for maximum security.

- Limitations: More expensive than a single-site programmer

- Automated production (robotic) programmers

Automated production programmers are based on multi-site programmers. They consist of a large input tray holding multiple parts and a robotic arm to select and place parts into appropriate programming sockets automatically. When the programming of the parts is complete, the parts are removed and placed in a finished tray. The automated programmers are often used in volume programming houses to program parts for which the programming time is small. BP Microsystems part number BP4710, BP4610, BP3710 MK2, and BP3610 are available for this purpose. Auto programmers cannot be used to program RTAX-S devices.

Where an auto-programmer is used, the appropriate open-top adapter module from BP Microsystems must be used.

Security in Low Power Flash Devices

3. Choose the desired settings for the FlashROM configurations to be programmed (Figure 11-13). Click **Finish** to generate the STAPL programming file for the design.

Figure 11-13 • FlashROM Configuration Settings for Low Power Flash Devices

### Generation of Security Header Programming File Only— Application 2

As mentioned in the "Application 2: Nontrusted Environment—Unsecured Location" section on page 243, the designer may employ FlashLock Pass Key protection or FlashLock Pass Key with AES encryption on the device before sending it to a nontrusted or unsecured location for device programming. To achieve this, the user needs to generate a programming file containing only the security settings desired (Security Header programming file).

Note: If AES encryption is configured, FlashLock Pass Key protection must also be configured.

The available security options are indicated in Table 11-4 and Table 11-5 on page 251.

| Security Option       | FlashROM Only | FPGA Core Only | Both FlashROM<br>and FPGA |

|-----------------------|---------------|----------------|---------------------------|

| No AES / no FlashLock | -             | -              | -                         |

| FlashLock only        | 1             | ✓              | ✓                         |

| AES and FlashLock     | <i>✓</i>      | <i>✓</i>       | ✓                         |

Table 11-4 • FlashLock Security Options for IGLOO and ProASIC3

Security in Low Power Flash Devices

#### Figure 11-15 • Programming Fusion Security Settings Only

- 2. Choose the desired security level setting and enter the key(s).

- The High security level employs FlashLock Pass Key with AES Key protection.

- The Medium security level employs FlashLock Pass Key protection only.

Figure 11-16 • High Security Level to Implement FlashLock Pass Key and AES Key Protection

# Programming Voltage (VPUMP) and VJTAG

Low-power flash devices support on-chip charge pumps, and therefore require only a single 3.3 V programming voltage for the VPUMP pin during programming. When the device is not being programmed, the VPUMP pin can be left floating or can be tied (pulled up) to any voltage between 0 V and 3.6 V<sup>2</sup>. During programming, the target board or the FlashPro4/3/3X programmer can provide VPUMP. FlashPro4/3/3X is capable of supplying VPUMP to a single device. If more than one device is to be programmed using FlashPro4/3/3X on a given board, FlashPro4/3/3X should not be relied on to supply the VPUMP voltage. A FlashPro4/3/3X programmer is not capable of providing reliable VJTAG voltage. The board must supply VJTAG voltage to the device and the VJTAG pin of the programmer header must be connected to the device VJTAG pin. Microsemi recommends that VPUMP<sup>3</sup> and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail. Refer to the "Board-Level Considerations" section on page 271 for capacitor requirements.

Low power flash device I/Os support a bank-based, voltage-supply architecture that simultaneously supports multiple I/O voltage standards (Table 12-2). By isolating the JTAG power supply in a separate bank from the user I/Os, low power flash devices provide greater flexibility with supply selection and simplify power supply and printed circuit board (PCB) design. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Microsemi recommends that TCK be tied to GND through a 200 ohm to 1 Kohm resistor. This prevents a possible totempole current on the input buffer stage. For TDI, TMS, and TRST pins, the devices provide an internal nominal 10 Kohm pull-up resistor. During programming, all I/O pins, except for JTAG interface pins, are tristated and weakly pulled up to VCCI. This isolates the part and prevents the signals from floating. The JTAG interface pins are driven by the FlashPro4/3/3X during programming, including the TRST pin, which is driven HIGH.

| Power Supply | Programming Mode                                           | Current during<br>Programming |

|--------------|------------------------------------------------------------|-------------------------------|

| VCC          | 1.2 V / 1.5 V                                              | < 70 mA                       |

| VCCI         | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V<br>(bank-selectable) | I/Os are weakly pulled up.    |

| VJTAG        | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V                      | < 20 mA                       |

| VPUMP        | 3.15 V to 3.45 V                                           | < 80 mA                       |

| Table | 12-2 • | Power | Supplies |

|-------|--------|-------|----------|

| , and |        |       | Cappiloo |

Note: All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation, except for IGLOO nano, where 1.2 V VCC and VJTAG programming is allowed.

# Nonvolatile Memory (NVM) Programming Voltage

SmartFusion and Fusion devices need stable VCCNVM/VCCENVM<sup>3</sup> (1.5 V power supply to the embedded nonvolatile memory blocks) and VCCOSC/VCCROSC<sup>4</sup> (3.3 V power supply to the integrated RC oscillator). The tolerance of VCCNVM/VCCENVM is  $\pm$  5% and VCCOSC/VCCROSC is  $\pm$  5%.

Unstable supply voltage on these pins can cause an NVM programming failure due to NVM page corruption. The NVM page can also be corrupted if the NVM reset pin has noise. This signal must be tied off properly.

Microsemi recommends installing the following capacitors<sup>5</sup> on the VCCNVM/VCCENVM and VCCOSC/VCCROSC pins:

- Add one bypass capacitor of 10  $\mu F$  for each power supply plane followed by an array of decoupling capacitors of 0.1  $\mu F.$

- Add one 0.1 µF capacitor near each pin.

<sup>2.</sup> During sleep mode in IGLOO devices connect VPUMP to GND.

VPUMP has to be quiet for successful programming. Therefore VPUMP must be separate and required capacitors must be installed close to the FPGA VPUMP pin.

<sup>4.</sup> VCCROSC is for SmartFusion.

<sup>5.</sup> The capacitors cannot guarantee reliable operation of the device if the board layout is not done properly.

# Microsemi

In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

| Date                     | Changes                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010<br>(continued) | The "Chain Integrity Test Error Analyze Chain Failure" section was renamed to the "Scan Chain Failure" section, and the Analyze Chain command was changed to Scan Chain. It was noted that occasionally a faulty programmer can cause scan chain failures.                                                                                                                                   |      |

| v1.5<br>(August 2009)    | The "CoreMP7 Device Security" section was removed from "Security in ARM-<br>Enabled Low Power Flash Devices", since M7-enabled devices are no longer<br>supported.                                                                                                                                                                                                                           | 265  |

| v1.4<br>(December 2008)  | The "ISP Architecture" section was revised to include information about core voltage for IGLOO V2 and ProASIC3L devices, as well as 50 mV increments allowable in Designer software.                                                                                                                                                                                                         | 261  |

|                          | IGLOO nano and ProASIC3 nano devices were added to Table 12-1 • Flash-Based FPGAs Supporting ISP.                                                                                                                                                                                                                                                                                            | 262  |

|                          | A second capacitor was added to Figure 12-6 • Board Layout and Programming Header Top View.                                                                                                                                                                                                                                                                                                  | 271  |

| v1.3<br>(October 2008)   | The "ISP Support in Flash-Based Devices" section was revised to include new families and make the information more concise.                                                                                                                                                                                                                                                                  | 262  |

| v1.2<br>(June 2008)      | <ul><li>The following changes were made to the family descriptions in Table 12-1 • Flash-Based FPGAs Supporting ISP:</li><li>ProASIC3L was updated to include 1.5 V.</li></ul>                                                                                                                                                                                                               | 262  |

|                          | The number of PLLs for ProASIC3E was changed from five to six.                                                                                                                                                                                                                                                                                                                               |      |

| v1.1<br>(March 2008)     | The "ISP Architecture" section was updated to included the IGLOO PLUS family in the discussion of family-specific support. The text, "When 1.2 V is used, the device can be reprogrammed in-system at 1.5 V only," was revised to state, "Although the device can operate at 1.2 V core voltage, the device can only be reprogrammed when all supplies (VCC, VCCI, and VJTAG) are at 1.5 V." | 261  |

|                          | The "ISP Support in Flash-Based Devices" section and Table 12-1 • Flash-Based FPGAs Supporting ISP were updated to include the IGLOO PLUS family. The "IGLOO Terminology" section and "ProASIC3 Terminology" section are new.                                                                                                                                                                | 262  |

|                          | The "Security" section was updated to mention that 15 k gate devices do not have a built-in 128-bit decryption core.                                                                                                                                                                                                                                                                         | 264  |

|                          | Table 12-2 • Power Supplies was revised to remove the Normal Operation column and add a table note stating, "All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation."                                                                                                                                                                           | 263  |

|                          | The "ISP Programming Header Information" section was revised to change FP3-26PIN-ADAPTER to FP3-10PIN-ADAPTER-KIT. Table 12-3 • Programming Header Ordering Codes was updated with the same change, as well as adding the part number FFSD-05-D-06.00-01-N, a 10-pin cable with 50-mil-pitch sockets.                                                                                        | 269  |

|                          | The "Board-Level Considerations" section was updated to describe connecting two capacitors in parallel across VPUMP and GND for proper programming.                                                                                                                                                                                                                                          | 271  |

| v1.0<br>(January 2008)   | Information was added to the "Programming Voltage (VPUMP) and VJTAG" section about the JTAG interface pin.                                                                                                                                                                                                                                                                                   | 263  |

| 51900055-2/7.06          | ACTgen was changed to SmartGen.                                                                                                                                                                                                                                                                                                                                                              | N/A  |

|                          | In Figure 12-6 • Board Layout and Programming Header Top View, the order of the text was changed to:<br>VJTAG from the target board<br>VCCI from the target board                                                                                                                                                                                                                            | 271  |

|                          | VCC from the target board                                                                                                                                                                                                                                                                                                                                                                    |      |

Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programming

## **Circuit Verification**

The power switching circuit recommended above is implemented on Microsemi's Icicle board (Figure 13-2). On the Icicle board, VJTAGENB is used to control the N-Channel Digital FET; however, this circuit was modified to use TRST instead of VJTAGENB in this application. There are three important aspects of this circuit that were verified:

- 1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH

- 2. VCC rises to 1.5 V before programming begins.

- 3. VCC switches from 1.5 V to 1.2 V when TRST is LOW.

### **Verification Steps**

1. The rise on VCC from 1.2 V to 1.5 V when TRST is HIGH.

#### Figure 13-2 • Core Voltage on the IGLOO AGL125-QNG132 Device

In the oscilloscope plots (Figure 13-2), the TRST from FlashPro3 and the VCC core voltage of the IGLOO device are labeled. This plot shows the rise characteristic of the TRST signal from FlashPro3. Once the TRST signal is asserted HIGH, the LTC3025 shown in Figure 13-1 on page 277 senses the increase in voltage and changes the output from 1.2 V to 1.5 V. It takes the circuit approximately 100  $\mu$ s to respond to TRST and change the voltage to 1.5 V on the VCC core.

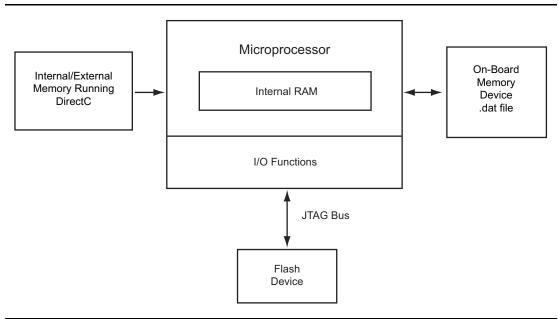

# 14 – Microprocessor Programming of Microsemi's Low Power Flash Devices

## Introduction

The Fusion, IGLOO, and ProASIC3 families of flash FPGAs support in-system programming (ISP) with the use of a microprocessor. Flash-based FPGAs store their configuration information in the actual cells within the FPGA fabric. SRAM-based devices need an external configuration memory, and hybrid nonvolatile devices store the configuration in a flash memory inside the same package as the SRAM FPGA. Since the programming of a true flash FPGA is simpler, requiring only one stage, it makes sense that programming with a microprocessor in-system should be simpler than with other SRAM FPGAs. This reduces bill-of-materials costs and printed circuit board (PCB) area, and increases system reliability.

Nonvolatile flash technology also gives the low power flash devices the advantage of a secure, low power, live-at-power-up, and single-chip solution. Low power flash devices are reprogrammable and offer time-to-market benefits at an ASIC-level unit cost. These features enable engineers to create high-density systems using existing ASIC or FPGA design flows and tools.

This document is an introduction to microprocessor programming only. To explain the difference between the options available, user's guides for DirectC and STAPL provide more detail on implementing each style.

Figure 14-1 • ISP Using Microprocessor

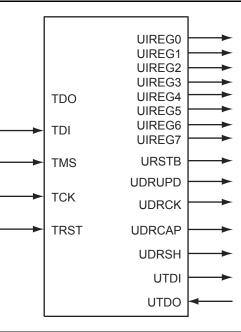

# **UJTAG Macro**

The UJTAG tiles can be instantiated in a design using the UJTAG macro from the Fusion, IGLOO, or ProASIC3 macro library. Note that "UJTAG" is a reserved name and cannot be used for any other userdefined blocks. A block symbol of the UJTAG tile macro is presented in Figure 16-2. In this figure, the ports on the left side of the block are connected to the JTAG TAP Controller, and the right-side ports are accessible by the FPGA core VersaTiles. The TDI, TMS, TDO, TCK, and TRST ports of UJTAG are only provided for design simulation purposes and should be treated as external signals in the design netlist. However, these ports must NOT be connected to any I/O buffer in the netlist. Figure 16-3 on page 300 illustrates the correct connection of the UJTAG macro to the user design netlist. Microsemi Designer software will automatically connect these ports to the TAP during place-and-route. Table 16-2 gives the port descriptions for the rest of the UJTAG ports:

| Port        | Description                                                                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UIREG [7:0] | This 8-bit bus carries the contents of the JTAG Instruction Register of each device. Instruction Register values 16 to 127 are not reserved and can be employed as user-defined instructions.                                                                                         |

| URSTB       | URSTB is an active-low signal and will be asserted when the TAP Controller is in Test-Logic-Reset mode. URSTB is asserted at power-up, and a power-on reset signal resets the TAP Controller. URSTB will stay asserted until an external TAP access changes the TAP Controller state. |

| UTDI        | This port is directly connected to the TAP's TDI signal.                                                                                                                                                                                                                              |

| UTDO        | This port is the user TDO output. Inputs to the UTDO port are sent to the TAP TDO output MUX when the IR address is in user range.                                                                                                                                                    |

| UDRSH       | Active-high signal enabled in the ShiftDR TAP state                                                                                                                                                                                                                                   |

| UDRCAP      | Active-high signal enabled in the CaptureDR TAP state                                                                                                                                                                                                                                 |

| UDRCK       | This port is directly connected to the TAP's TCK signal.                                                                                                                                                                                                                              |

| UDRUPD      | Active-high signal enabled in the UpdateDR TAP state                                                                                                                                                                                                                                  |

Table 16-2 • UJTAG Port Descriptions

Figure 16-2 • UJTAG Tile Block Symbol

# Microsemi

Power-Up/-Down Behavior of Low Power Flash Devices

# Flash Devices Support Power-Up Behavior

The flash FPGAs listed in Table 17-1 support power-up behavior and the functions described in this document.

#### Table 17-1 • Flash-Based FPGAs

| Series   | Family <sup>*</sup>  | Description                                                              |

|----------|----------------------|--------------------------------------------------------------------------|

| IGLOO    | IGLOO                | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLOOe               | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano           | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS           | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3             | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E            | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano        | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L            | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3          | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

|          | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                    |

|          | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                     |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 17-1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

Power-Up/-Down Behavior of Low Power Flash Devices

## **Transient Current on VCC**

The characterization of the transient current on VCC is performed on nearly all devices within the IGLOO, ProASIC3L, and ProASIC3 families. A sample size of five units is used from each device family member. All the device I/Os are internally pulled down while the transient current measurements are performed. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCC, when the power supply is powered at ramp-rates ranging from 15 V/ms to 0.15 V/ms, does not exceed the maximum standby current specified in the device datasheets. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO nano, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCC. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCC is typically in the range of 1–5 mA.

## **Transient Current on VCCI**

The characterization of the transient current on VCCI is performed on devices within the IGLOO, IGLOO nano, IGLOO PLUS, ProASIC3, ProASIC3 nano, and ProASIC3L groups of devices, similarly to VCC transient current measurements. For ProASIC3 devices, the measurements at typical conditions show that the maximum transient current on VCCI, when the power supply is powered at ramp-rates ranging from 33 V/ms to 0.33 V/ms, does not exceed the maximum standby current specified in the device datasheet. Refer to the DC and Switching Characteristics chapters of the *ProASIC3 Flash Family FPGAS* datasheet and *ProASIC3E Flash Family FPGAs* datasheet for more information.

Similarly, IGLOO, IGLOO PLUS, and ProASIC3L devices exhibit very low transient current on VCCI. The transient current does not exceed the typical operating current of the device while in active mode. For example, the characterization of AGL600-FG256 V2 and V5 devices has shown that the transient current on VCCI is typically in the range of 1–2 mA.

## **Brownout Voltage**

Brownout is a condition in which the voltage supplies are lower than normal, causing the device to malfunction as a result of insufficient power. In general, Microsemi does not guarantee the functionality of the design inside the flash FPGA if voltage supplies are below their minimum recommended operating condition. Microsemi has performed measurements to characterize the brownout levels of FPGA power supplies. Refer to Table 17-3 for device-specific brownout deactivation levels. For the purpose of characterization, a direct path from the device input to output is monitored while voltage supplies are lowered gradually. The brownout point is defined as the voltage level at which the output stops following the input. Characterization tests performed on several IGLOO, ProASIC3L, and ProASIC3 devices in typical operating conditions showed the brownout voltage levels to be within the specification.

During device power-down, the device I/Os become tristated once the first supply in the power-down sequence drops below its brownout deactivation voltage.

#### Table 17-3 • Brownout Deactivation Levels for VCC and VCCI

| Devices                                                                                                   | VCC Brownout<br>Deactivation Level (V) | VCCI Brownout<br>Deactivation Level (V) |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------|

| ProASIC3, ProASIC3 nano, IGLOO, IGLOO nano,<br>IGLOO PLUS and ProASIC3L devices running at<br>VCC = 1.5 V | 0.75 V ± 0.25 V                        | 0.8 V ± 0.3 V                           |

| IGLOO, IGLOO nano, IGLOO PLUS, and<br>ProASIC3L devices running at VCC = 1.2 V                            | 0.75 V ± 0.2 V                         | 0.8 V ± 0.15 V                          |

### PLL Behavior at Brownout Condition

When PLL power supply voltage and/or V<sub>CC</sub> levels drop below the V<sub>CC</sub> brownout levels mentioned above for 1.5 V and 1.2 V devices, the PLL output lock signal goes LOW and/or the output clock is lost. The following sections explain PLL behavior during and after the brownout condition.

#### VCCPLL and VCC Tied Together

In this condition, both VCC and VCCPLL drop below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level. During the brownout recovery, once VCCPLL and VCC reach the activation point (0.85  $\pm$  0.25 V or  $\pm$  0.2 V) again, the PLL output lock signal may still remain LOW with the PLL output clock signal toggling. If this condition occurs, there are two ways to recover the PLL output lock signal:

- 1. Cycle the power supplies of the PLL (power off and on) by using the PLL POWERDOWN signal.

- 2. Turn off the input reference clock to the PLL and then turn it back on.

#### Only VCCPLL Is at Brownout

In this case, only VCCPLL drops below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level and the VCC supply remains at nominal recommended operating voltage (1.5 V  $\pm$  0.075 V for 1.5 V devices and 1.2 V  $\pm$  0.06 V for 1.2 V devices). In this condition, the PLL behavior after brownout recovery is similar to initial power-up condition, and the PLL will regain lock automatically after VCCPLL is ramped up above the activation level (0.85  $\pm$  0.25 V or  $\pm$  0.2 V). No intervention is necessary in this case.

#### Only VCC Is at Brownout

In this condition, VCC drops below the 0.75 V ( $\pm$  0.25 V or  $\pm$  0.2 V) brownout level and VCCPLL remains at nominal recommended operating voltage (1.5 V  $\pm$  0.075 V for 1.5 V devices and 1.2 V  $\pm$  0.06 V for 1.2 V devices). During the brownout recovery, once VCC reaches the activation point again (0.85  $\pm$  0.25 V or  $\pm$  0.2 V), the PLL output lock signal may still remain LOW with the PLL output clock signal toggling. If this condition occurs, there are two ways to recover the PLL output lock signal:

- 1. Cycle the power supplies of the PLL (power off and on) by using the PLL POWERDOWN signal.

- 2. Turn off the input reference clock to the PLL and then turn it back on.

It is important to note that Microsemi recommends using a monotonic power supply or voltage regulator to ensure proper power-up behavior.

Power-Up/-Down Behavior of Low Power Flash Devices

### **Internal Pull-Up and Pull-Down**

Low power flash device I/Os are equipped with internal weak pull-up/-down resistors that can be used by designers. If used, these internal pull-up/-down resistors will be activated during power-up, once both VCC and VCCI are above their functional activation level. Similarly, during power-down, these internal pull-up/-down resistors will turn off once the first supply voltage falls below its brownout deactivation level.

# **Cold-Sparing**

In cold-sparing applications, voltage can be applied to device I/Os before and during power-up. Coldsparing applications rely on three important characteristics of the device:

- 1. I/Os must be tristated before and during power-up.

- 2. Voltage applied to the I/Os must not power up any part of the device.

- 3. VCCI should not exceed 3.6 V, per datasheet specifications.

As described in the "Power-Up to Functional Time" section on page 312, Microsemi's low power flash I/Os are tristated before and during power-up until the last voltage supply (VCC or VCCI) is powered up past its functional level. Furthermore, applying voltage to the FPGA I/Os does not pull up VCC or VCCI and, therefore, does not partially power up the device. Table 17-4 includes the cold-sparing test results on A3PE600-PQ208 devices. In this test, leakage current on the device I/O and residual voltage on the power supply rails were measured while voltage was applied to the I/O before power-up.

|            | Residual |       |                 |

|------------|----------|-------|-----------------|

| Device I/O | VCC      | VCCI  | Leakage Current |

| Input      | 0        | 0.003 | <1 µA           |

| Output     | 0        | 0.003 | <1 µA           |

Table 17-4 • Cold-Sparing Test Results for A3PE600 Devices

VCCI must not exceed 3.6 V, as stated in the datasheet specification. Therefore, ProASIC3E devices meet all three requirements stated earlier in this section and are suitable for cold-sparing applications. The following devices and families support cold-sparing:

IGLOO: AGL015 and AGL030

- All IGLOO nano

- All IGLOO PLUS

- All IGLOOe

- ProASIC3L: A3PE3000L

- ProASIC3: A3P015 and A3P030

- All ProASIC3 nano

- All ProASIC3E

- Military ProASIC3EL: A3PE600L and A3PE3000L

- RT ProASIC3: RT3PE600L and RT3PE3000L