# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 68                                                                        |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 100-TQFP                                                                  |

| Supplier Device Package        | 100-VQFP (14x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a3pn250-2vq100i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Microsemi

ProASIC3 nano FPGA Fabric User's Guide

| IEEE 1532 (JTAG) Interface                                                     |     |

|--------------------------------------------------------------------------------|-----|

| Security                                                                       |     |

| Security in ARM-Enabled Low Power Flash Devices                                |     |

| FlashROM and Programming Files                                                 |     |

| Programming Solution                                                           |     |

| ISP Programming Header Information                                             |     |

| Board-Level Considerations                                                     |     |

| Conclusion                                                                     |     |

| Related Documents                                                              |     |

| List of Changes                                                                |     |

|                                                                                |     |

| 13 Core Voltage Switching Circuit for IGLOO and ProASIC3L In-System Programmin | •   |

| Introduction                                                                   |     |

| Microsemi's Flash Families Support Voltage Switching Circuit                   |     |

| Circuit Description                                                            |     |

| Circuit Verification                                                           |     |

|                                                                                |     |

| Conclusion                                                                     |     |

| List of Changes                                                                |     |

| 14 Microprocessor Programming of Microsemi's Low Power Flash Devices           | 283 |

| Introduction                                                                   |     |

|                                                                                |     |

| Microprocessor Programming Support in Flash Devices                            |     |

| Programming Algorithm                                                          |     |

|                                                                                |     |

| Hardware Requirement                                                           |     |

| Security                                                                       |     |

| Conclusion                                                                     |     |

| List of Changes                                                                |     |

| 15 Boundary Scan in Low Power Flash Devices.                                   |     |

| Boundary Scan                                                                  |     |

| TAP Controller State Machine                                                   |     |

| Microsemi's Flash Devices Support the JTAG Feature                             |     |

| Boundary Scan Support in Low Power Devices                                     |     |

| Boundary Scan Opcodes                                                          |     |

| Boundary Scan Chain                                                            |     |

| Board-Level Recommendations                                                    |     |

| Advanced Boundary Scan Register Settings                                       |     |

| List of Changes                                                                |     |

|                                                                                |     |

| 16 UJTAG Applications in Microsemi's Low Power Flash Devices                   |     |

| Introduction                                                                   |     |

| UJTAG Support in Flash-Based Devices                                           |     |

| UJTAG Macro                                                                    |     |

| UJTAG Operation                                                                |     |

| Typical UJTAG Applications                                                     |     |

| Conclusion                                                                     |     |

| Related Documents                                                              |     |

| List of Changes                                                                |     |

# *Microsemi*.

Table of Contents

| 17 | Power-Up/-Down Behavior of Low Power Flash Devices |     |

|----|----------------------------------------------------|-----|

|    | Introduction                                       | 307 |

|    | Flash Devices Support Power-Up Behavior            | 308 |

|    | Power-Up/-Down Sequence and Transient Current      | 309 |

|    | I/O Behavior at Power-Up/-Down                     | 311 |

|    | Cold-Sparing                                       | 316 |

|    | Hot-Swapping                                       | 317 |

|    | Conclusion                                         | 317 |

|    | Related Documents                                  | 318 |

|    | List of Changes                                    | 318 |

|    |                                                    |     |

| А  | Summary of Changes                                 | 319 |

|    | History of Revision to Chapters                    | 319 |

|    |                                                    |     |

| В  | Product Support                                    | 321 |

|    | Customer Service                                   | 321 |

|    | Customer Technical Support Center                  | 321 |

|    | Technical Support                                  | 321 |

|    | Website                                            | 321 |

|    | Contacting the Customer Technical Support Center   | 321 |

|    | ITAR Technical Support                             | 322 |

|    |                                                    |     |

|    | Index                                              | 323 |

Note: Flash\*Freeze technology only applies to IGLOO and ProASIC3L families.

Note: \* AGLP030 does not contain a PLL or support AES security.

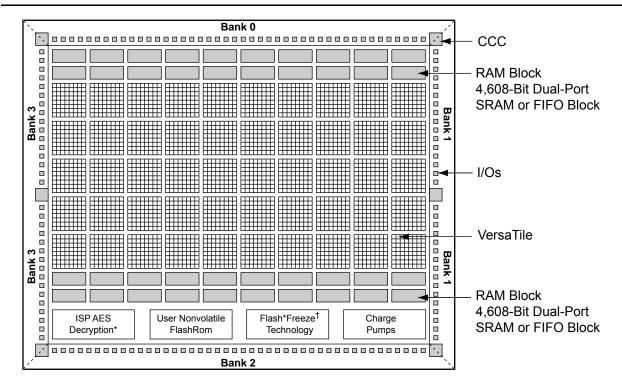

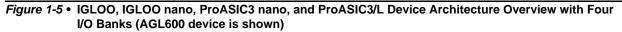

Figure 1-6 • IGLOO PLUS Device Architecture Overview with Four I/O Banks

Microsemi

# 2 – Low Power Modes in ProASIC3/E and ProASIC3 nano FPGAs

# Introduction

The demand for low power systems and semiconductors, combined with the strong growth observed for value-based FPGAs, is driving growing demand for low power FPGAs. For portable and battery-operated applications, power consumption has always been the greatest challenge. The battery life of a system and on-board devices has a direct impact on the success of the product. As a result, FPGAs used in these applications should meet low power consumption requirements.

ProASIC<sup>®</sup>3/E and ProASIC3 nano FPGAs offer low power consumption capability inherited from their nonvolatile and live-at-power-up (LAPU) flash technology. This application note describes the power consumption and how to use different power saving modes to further reduce power consumption for power-conscious electronics design.

## **Power Consumption Overview**

In evaluating the power consumption of FPGA technologies, it is important to consider it from a system point of view. Generally, the overall power consumption should be based on static, dynamic, inrush, and configuration power. Few FPGAs implement ways to reduce static power consumption utilizing sleep modes.

SRAM-based FPGAs use volatile memory for their configuration, so the device must be reconfigured after each power-up cycle. Moreover, during this initialization state, the logic could be in an indeterminate state, which might cause inrush current and power spikes. More complex power supplies are required to eliminate potential system power-up failures, resulting in higher costs. For portable electronics requiring frequent power-up and -down cycles, this directly affects battery life, requiring more frequent recharging or replacement.

SRAM-Based FPGA Total Power Consumption = P<sub>static</sub> + P<sub>dynamic</sub> + P<sub>inrush</sub> + P<sub>config</sub>

EQ 1

ProASIC3/E Total Power Consumption = P<sub>static</sub> + P<sub>dynamic</sub>

EQ 2

Unlike SRAM-based FPGAs, Microsemi flash-based FPGAs are nonvolatile and do not require power-up configuration. Additionally, Microsemi nonvolatile flash FPGAs are live at power-up and do not require additional support components. Total power consumption is reduced as the inrush current and configuration power components are eliminated.

Note that the static power component can be reduced in flash FPGAs (such as the ProASIC3/E devices) by entering User Low Static mode or Sleep mode. This leads to an extremely low static power component contribution to the total system power consumption.

The following sections describe the usage of Static (Idle) mode to reduce the power component, User Low Static mode to reduce the static power component, and Sleep mode and Shutdown mode to achieve a range of power consumption when the FPGA or system is idle. Table 2-1 on page 22 summarizes the different low power modes offered by ProASIC3/E devices.

standard for CLKBUF is LVTTL in the current Microsemi Libero  $^{\ensuremath{\mathbb{R}}}$  System-on-Chip (SoC) and Designer software.

| Name            | Description                                                    |

|-----------------|----------------------------------------------------------------|

| CLKBUF_LVCMOS5  | LVCMOS clock buffer with 5.0 V CMOS voltage level              |

| CLKBUF_LVCMOS33 | LVCMOS clock buffer with 3.3 V CMOS voltage level              |

| CLKBUF_LVCMOS25 | LVCMOS clock buffer with 2.5 V CMOS voltage level <sup>1</sup> |

| CLKBUF_LVCMOS18 | LVCMOS clock buffer with 1.8 V CMOS voltage level              |

| CLKBUF_LVCMOS15 | LVCMOS clock buffer with 1.5 V CMOS voltage level              |

| CLKBUF_LVCMOS12 | LVCMOS clock buffer with 1.2 V CMOS voltage level              |

| CLKBUF_PCI      | PCI clock buffer                                               |

| CLKBUF_PCIX     | PCIX clock buffer                                              |

| CLKBUF_GTL25    | GTL clock buffer with 2.5 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTL33    | GTL clock buffer with 3.3 V CMOS voltage level <sup>1</sup>    |

| CLKBUF_GTLP25   | GTL+ clock buffer with 2.5 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_GTLP33   | GTL+ clock buffer with 3.3 V CMOS voltage level <sup>1</sup>   |

| CLKBUF_HSTL_I   | HSTL Class I clock buffer <sup>1</sup>                         |

| CLKBUF_HSTL_II  | HSTL Class II clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_I  | SSTL2 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL2_II | SSTL2 Class II clock buffer <sup>1</sup>                       |

| CLKBUF_SSTL3_I  | SSTL3 Class I clock buffer <sup>1</sup>                        |

| CLKBUF_SSTL3_II | SSTL3 Class II clock buffer <sup>1</sup>                       |

#### Table 3-9 • I/O Standards within CLKBUF

Notes:

- 1. Supported in only the IGLOOe, ProASIC3E, AFS600, and AFS1500 devices

- 2. By default, the CLKBUF macro uses the 3.3 V LVTTL I/O technology.

The current synthesis tool libraries only infer the CLKBUF or CLKINT macros in the netlist. All other global macros must be instantiated manually into your HDL code. The following is an example of CLKBUF LVCMOS25 global macro instantiations that you can copy and paste into your code:

#### VHDL

```

component clkbuf_lvcmos25

port (pad : in std_logic; y : out std_logic);

end component

```

#### begin

```

-- concurrent statements

u2 : clkbuf_lvcmos25 port map (pad => ext_clk, y => int_clk);

end

```

## Verilog

module design (\_\_\_\_\_);

input \_\_\_\_; output \_\_\_\_;

clkbuf\_lvcmos25 u2 (.y(int\_clk), .pad(ext\_clk);

endmodule

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

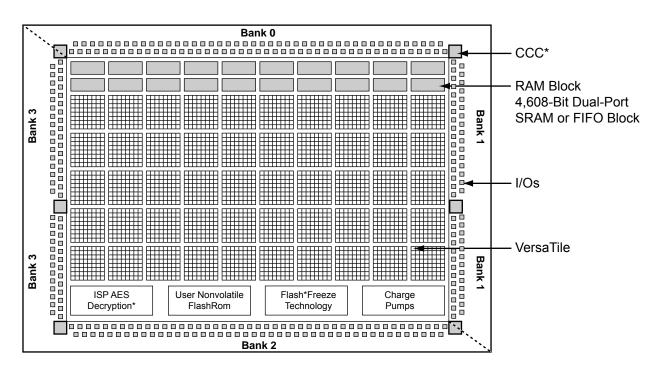

## Implementing EXTFB in ProASIC3/E Devices

When the external feedback (EXTFB) signal of the PLL in the ProASIC3/E devices is implemented, the phase detector of the PLL core receives the reference clock (CLKA) and EXTFB as inputs. EXTFB must be sourced as an INBUF macro and located at the global/chip clock location associated with the target PLL by Designer software. EXTFB cannot be sourced from the FPGA fabric.

The following example shows CLKA and EXTFB signals assigned to two global I/Os in the same global area of ProASIC3E device.

| OADIVHALF /<br>OBDIVHALF /<br>OCDIVHALF | OADIV<4:0> /<br>OBDIV<4:0> /<br>OCDIV<4:0><br>(in decimal) | Divider Factor | Input Clock<br>Frequency | Output Clock<br>Frequency (MHz)   |

|-----------------------------------------|------------------------------------------------------------|----------------|--------------------------|-----------------------------------|

| 1                                       | 2                                                          | 1.5            | 100 MHz RC               | 66.7                              |

|                                         | 4                                                          | 2.5            | Oscillator               | 40.0                              |

|                                         | 6                                                          | 3.5            |                          | 28.6                              |

|                                         | 8                                                          | 4.5            | 1                        | 22.2                              |

|                                         | 10                                                         | 5.5            | 1                        | 18.2                              |

|                                         | 12                                                         | 6.5            |                          | 15.4                              |

|                                         | 14                                                         | 7.5            |                          | 13.3                              |

|                                         | 16                                                         | 8.5            |                          | 11.8                              |

|                                         | 18                                                         | 9.5            |                          | 10.5                              |

|                                         | 20                                                         | 10.5           | 1                        | 9.5                               |

|                                         | 22                                                         | 11.5           |                          | 8.7                               |

|                                         | 24                                                         | 12.5           |                          | 8.0                               |

|                                         | 26                                                         | 13.5           |                          | 7.4                               |

|                                         | 28                                                         | 14.5           | 1                        | 6.9                               |

| 0                                       | 0–31                                                       | 1–32           | Other Clock Sources      | Depends on other divider settings |

#### Table 4-18 • Fusion Dynamic CCC Division by Half Configuration

#### Table 4-19 • Configuration Bit <76:75> / VCOSEL<2:1> Selection for All Families

|                     | VCOSEL[2:1]   |               |               |               |               |               |               |               |

|---------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

|                     | 00            |               | 01            |               | 10            |               | 11            |               |

| Voltage             | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) | Min.<br>(MHz) | Max.<br>(MHz) |

| IGLOO and IGLOO     | PLUS          |               |               |               | •             | •             |               |               |

| 1.2 V ± 5%          | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 160           |

| 1.5 V ± 5%          | 24            | 43.75         | 30            | 87.5          | 60            | 175           | 135           | 250           |

| ProASIC3L, RT Pro   | oASIC3, and   | Military Pro  | ASIC3/L       | •             | •             | •             | •             |               |

| 1.2 V ± 5%          | 24            | 35            | 30            | 70            | 60            | 140           | 135           | 250           |

| 1.5 V ± 5%          | 24            | 43.75         | 30            | 70            | 60            | 175           | 135           | 350           |

| ProASIC3 and Fusion |               |               |               |               |               |               |               |               |

| 1.5 V ± 5%          | 24            | 43.75         | 33.75         | 87.5          | 67.5          | 175           | 135           | 350           |

#### Table 4-20 • Configuration Bit <74> / VCOSEL<0> Selection for All Families

| VCOSEL[0] | Description                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0         | Fast PLL lock acquisition time with high tracking jitter. Refer to the corresponding datasheet for specific value and definition. |

| 1         | Slow PLL lock acquisition time with low tracking jitter. Refer to the corresponding datasheet for specific value and definition.  |

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

```

DLYGLC[4:0] 00000

DLYYB[4:0] 00000

DLYYC[4:0] 00000

VCOSEL[2:0] 100

```

Primary Clock Frequency 33.000 Primary Clock Phase Shift 0.000 Primary Clock Output Delay from CLKA 1.695

Secondaryl Clock Frequency 40.000 Secondaryl Clock Phase Shift 0.000 Secondaryl Clock Global Output Delay from CLKB 0.200

Secondary2 Clock Frequency 50.000 Secondary2 Clock Phase Shift 0.000 Secondary2 Clock Global Output Delay from CLKC 0.200

\*\*\*\*\*

| NAME     | SDIN    | VALUE   | TYPE     |

|----------|---------|---------|----------|

| FINDIV   | [6:0]   | 0000101 | EDIT     |

| FBDIV    | [13:7]  | 0100000 | EDIT     |

| OADIV    | [18:14] | 00100   | EDIT     |

| OBDIV    | [23:19] | 00000   | EDIT     |

| OCDIV    | [28:24] | 00000   | EDIT     |

| OAMUX    | [31:29] | 100     | EDIT     |

| OBMUX    | [34:32] | 000     | EDIT     |

| OCMUX    | [37:35] | 000     | EDIT     |

| FBSEL    | [39:38] | 01      | EDIT     |

| FBDLY    | [44:40] | 00000   | EDIT     |

| XDLYSEL  | [45]    | 0       | EDIT     |

| DLYGLA   | [50:46] | 00000   | EDIT     |

| DLYGLB   | [55:51] | 00000   | EDIT     |

| DLYGLC   | [60:56] | 00000   | EDIT     |

| DLYYB    | [65:61] | 00000   | EDIT     |

| DLYYC    | [70:66] | 00000   | EDIT     |

| STATASEL | [71]    | X       | MASKED   |

| STATBSEL | [72]    | X       | MASKED   |

| STATCSEL | [73]    | X       | MASKED   |

| VCOSEL   | [76:74] | 100     | EDIT     |

| DYNASEL  | [77]    | X       | MASKED   |

| DYNBSEL  | [78]    | X       | MASKED   |

| DYNCSEL  | [79]    | X       | MASKED   |

| RESETEN  | [80]    | 1       | READONLY |

Below is the resultant Verilog HDL description of a legal dynamic PLL core configuration generated by SmartGen:

module dyn\_pll\_macro(POWERDOWN, CLKA, LOCK, GLA, GLB, GLC, SDIN, SCLK, SSHIFT, SUPDATE, MODE, SDOUT, CLKB, CLKC);

input POWERDOWN, CLKA; output LOCK, GLA, GLB, GLC; input SDIN, SCLK, SSHIFT, SUPDATE, MODE; output SDOUT; input CLKB, CLKC; wire VCC, GND; VCC VCC\_1\_net(.Y(VCC));

GND GND\_1\_net(.Y(GND));

Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs

# **Recommended Board-Level Considerations**

The power to the PLL core is supplied by VCCPLA/B/C/D/E/F (VCCPLx), and the associated ground connections are supplied by VCOMPLA/B/C/D/E/F (VCOMPLx). When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Optionally, the PLL can be turned on/off during normal device operation via the POWERDOWN port (see Table 4-3 on page 68).

# PLL Power Supply Decoupling Scheme

The PLL core is designed to tolerate noise levels on the PLL power supply as specified in the datasheets. When operated within the noise limits, the PLL will meet the output peak-to-peak jitter specifications specified in the datasheets. User applications should always ensure the PLL power supply is powered from a noise-free or low-noise power source.

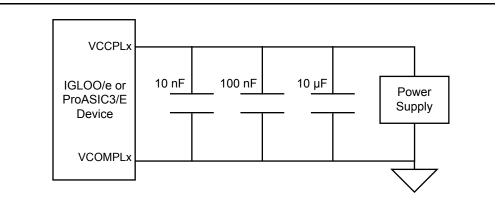

However, in situations where the PLL power supply noise level is higher than the tolerable limits, various decoupling schemes can be designed to suppress noise to the PLL power supply. An example is provided in Figure 4-38. The VCCPLx and VCOMPLx pins correspond to the PLL analog power supply and ground.

Microsemi strongly recommends that two ceramic capacitors (10 nF in parallel with 100 nF) be placed close to the power pins (less than 1 inch away). A third generic 10  $\mu$ F electrolytic capacitor is recommended for low-frequency noise and should be placed farther away due to its large physical size. Microsemi recommends that a 6.8  $\mu$ H inductor be placed between the supply source and the capacitors to filter out any low-/medium- and high-frequency noise. In addition, the PCB layers should be controlled so the VCCPLx and VCOMPLx planes have the minimum separation possible, thus generating a good-quality RF capacitor.

For more recommendations, refer to the Board-Level Considerations application note.

Recommended 100 nF capacitor:

- Producer BC Components, type X7R, 100 nF, 16 V

- BC Components part number: 0603B104K160BT

- Digi-Key part number: BC1254CT-ND

- Digi-Key part number: BC1254TR-ND

Recommended 10 nF capacitor:

- Surface-mount ceramic capacitor

- Producer BC Components, type X7R, 10 nF, 50 V

- BC Components part number: 0603B103K500BT

- Digi-Key part number: BC1252CT-ND

- Digi-Key part number: BC1252TR-ND

Figure 4-38 • Decoupling Scheme for One PLL (should be replicated for each PLL used)

# Microsemi

FlashROM in Microsemi's Low Power Flash Devices

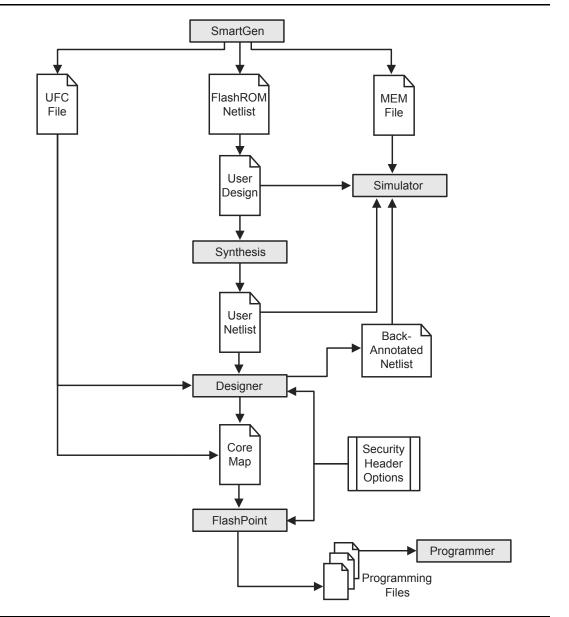

# **FlashROM Design Flow**

The Microsemi Libero System-on-Chip (SoC) software has extensive FlashROM support, including FlashROM generation, instantiation, simulation, and programming. Figure 5-9 shows the user flow diagram. In the design flow, there are three main steps:

- 1. FlashROM generation and instantiation in the design

- 2. Simulation of FlashROM design

- 3. Programming file generation for FlashROM design

Figure 5-9 • FlashROM Design Flow

256×18 FIFO is full, even though a 128×18 FIFO was requested. For this example, the Almost-Full flag can be used instead of the Full flag to signal when the 128th data word is reached.

To accommodate different aspect ratios, the almost-full and almost-empty values are expressed in terms of data bits instead of data words. SmartGen translates the user's input, expressed in data words, into data bits internally. SmartGen allows the user to select the thresholds for the Almost-Empty and Almost-Full flags in terms of either the read data words or the write data words, and makes the appropriate conversions for each flag.

After the empty or full states are reached, the FIFO can be configured so the FIFO counters either stop or continue counting. For timing numbers, refer to the appropriate family datasheet.

### Signal Descriptions for FIFO4K18

The following signals are used to configure the FIFO4K18 memory element:

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 6-6).

| WW[2:0]       | RW[2:0]       | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### Table 6-6 • Aspect Ratio Settings for WW[2:0]

#### WBLK and RBLK

These signals are active-low and will enable the respective ports when LOW. When the RBLK signal is HIGH, that port's outputs hold the previous value.

#### WEN and REN

Read and write enables. WEN is active-low and REN is active-high by default. These signals can be configured as active-high or -low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

# Note: For the Automotive ProASIC3 FIFO4K18, for the same clock, 180° out of phase (inverted) between clock pins should be used.

#### RPIPE

This signal is used to specify pipelined read on the output. A LOW on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A HIGH indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active-low signal resets the control logic and forces the output hold state registers to zero when asserted. It does not reset the contents of the memory array (Table 6-7 on page 144).

While the RESET signal is active, read and write operations are disabled. As with any asynchronous RESET signal, care must be taken not to assert it too close to the edges of active read and write clocks.

#### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 6-7 on page 144).

## I/O Bank Resource Usage

This is an important portion of the report. The user must meet the requirements stated in this table. Figure 8-10 shows the I/O Bank Resource Usage table included in the I/O bank report:

#### Figure 8-10 • I/O Bank Resource Usage Table

The example in Figure 8-10 shows that none of the I/O macros is assigned to the bank because more than one VCCI is detected.

## I/O Voltage Usage

The I/O Voltage Usage table provides the number of VREF (E devices only) and  $V_{CCI}$  assignments required in the design. If the user decides to make I/O assignments manually (PDC or MVN), the issues listed in this table must be resolved before proceeding to Layout. As stated earlier, VREF assignments must be made if there are any voltage-referenced I/Os.

Figure 8-11 shows the I/O Voltage Usage table included in the I/O bank report.

#### Figure 8-11 • I/O Voltage Usage Table

The table in Figure 8-11 indicates that there are two voltage-referenced I/Os used in the design. Even though both of the voltage-referenced I/O technologies have the same VCCI voltage, their VREF voltages are different. As a result, two I/O banks are needed to assign the VCCI and VREF voltages.

In addition, there are six single-ended I/Os used that have the same VCCI voltage. Since two banks are already assigned with the same VCCI voltage and there are enough unused bonded I/Os in

I/O Software Control in Low Power Flash Devices

those banks, the user does not need to assign the same VCCI voltage to another bank. The user needs to assign the other three VCCI voltages to three more banks.

# Assigning Technologies and VREF to I/O Banks

Low power flash devices offer a wide variety of I/O standards, including voltage-referenced standards. Before proceeding to Layout, each bank must have the required VCCI voltage assigned for the corresponding I/O technologies used for that bank. The voltage-referenced standards require the use of a reference voltage (VREF). This assignment can be done manually or automatically. The following sections describe this in detail.

## Manually Assigning Technologies to I/O Banks

The user can import the PDC at this point and resolve this requirement. The PDC command is

set\_iobank [bank name] -vcci [vcci value]

Another method is to use the I/O Bank Settings dialog box (**MVN** > **Edit** > **I/O Bank Settings**) to set up the  $V_{CCI}$  voltage for the bank (Figure 8-12).

Figure 8-12 • Setting VCCI for a Bank

The procedure is as follows:

- 1. Select the bank to which you want VCCI to be assigned from the Choose Bank list.

- 2. Select the I/O standards for that bank. If you select any standard, the tool will automatically show all compatible standards that have a common VCCI voltage requirement.

- 3. Click Apply.

- 4. Repeat steps 1–3 to assign VCCI voltages to other banks. Refer to Figure 8-11 on page 197 to find out how many I/O banks are needed for VCCI bank assignment.

## Manually Assigning VREF Pins

Voltage-referenced inputs require an input reference voltage (VREF). The user must assign VREF pins before running Layout. Before assigning a VREF pin, the user must set a VREF technology for the bank to which the pin belongs.

# VREF Rules for the Implementation of Voltage-Referenced I/O Standards

The VREF rules are as follows:

- 1. Any I/O (except JTAG I/Os) can be used as a  $V_{\mathsf{REF}}$  pin.

- One V<sub>REF</sub> pin can support up to 15 I/Os. It is recommended, but not required, that eight of them be on one side and seven on the other side (in other words, all 15 can still be on one side of VREF).

- 3. SSTL3 (I) and (II): Up to 40 I/Os per north or south bank in any position

- 4. LVPECL / GTL+ 3.3 V / GTL 3.3 V: Up to 48 I/Os per north or south bank in any position (not applicable for IGLOO nano and ProASIC3 nano devices)

- 5. SSTL2 (I) and (II) / GTL+ 2.5 V / GTL 2.5 V: Up to 72 I/Os per north or south bank in any position

- 6. VREF minibanks partition rule: Each I/O bank is physically partitioned into VREF minibanks. The VREF pins within a VREF minibank are interconnected internally, and consequently, only one VREF voltage can be used within each VREF minibank. If a bank does not require a VREF signal, the VREF pins of that bank are available as user I/Os.

- The first VREF minibank includes all I/Os starting from one end of the bank to the first power triple and eight more I/Os after the power triple. Therefore, the first VREF minibank may contain (0 + 8), (2 + 8), (4 + 8), (6 + 8), or (8 + 8) I/Os.

The second VREF minibank is adjacent to the first VREF minibank and contains eight I/Os, a power triple, and eight more I/Os after the triple. An analogous rule applies to all other VREF minibanks but the last.

The last VREF minibank is adjacent to the previous one but contains eight I/Os, a power triple, and all I/Os left at the end of the bank. This bank may also contain (8 + 0), (8 + 2), (8 + 4), (8 + 6), or (8 + 8) available I/Os.

#### Example:

4 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  8 l/Os, 8 l/Os  $\rightarrow$  Triple  $\rightarrow$  2 l/Os

That is, minibank A = (4 + 8) I/Os, minibank B = (8 + 8) I/Os, minibank C = (8 + 2) I/Os.

Only minibanks that contain input or bidirectional I/Os require a VREF. A VREF is not needed for minibanks composed of output or tristated I/Os.

## Assigning the VREF Voltage to a Bank

When importing the PDC file, the VREF voltage can be assigned to the I/O bank. The PDC command is as follows:

set\_iobank -vref [value]

Another method for assigning VREF is by using **MVN** > **Edit** > **I/O Bank Settings** (Figure 8-13 on page 200).

If the assignment is not successful, an error message appears in the Output window.

To undo the I/O bank assignments, choose **Undo** from the **Edit** menu. Undo removes the I/O technologies assigned by the IOBA. It does not remove the I/O technologies previously assigned.

To redo the changes undone by the Undo command, choose Redo from the Edit menu.

To clear I/O bank assignments made before using the Undo command, manually unassign or reassign I/O technologies to banks. To do so, choose **I/O Bank Settings** from the **Edit** menu to display the I/O Bank Settings dialog box.

# Conclusion

Fusion, IGLOO, and ProASIC3 support for multiple I/O standards minimizes board-level components and makes possible a wide variety of applications. The Microsemi Designer software, integrated with Libero SoC, presents a clear visual display of I/O assignments, allowing users to verify I/O and board-level design requirements before programming the device. The device I/O features and functionalities ensure board designers can produce low-cost and low power FPGA applications fulfilling the complexities of contemporary design needs.

# **Related Documents**

## **User's Guides**

Libero SoC User's Guide http://www.microsemi.com/soc/documents/libero\_ug.pdf IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen Core Reference Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

# 9 – DDR for Microsemi's Low Power Flash Devices

# Introduction

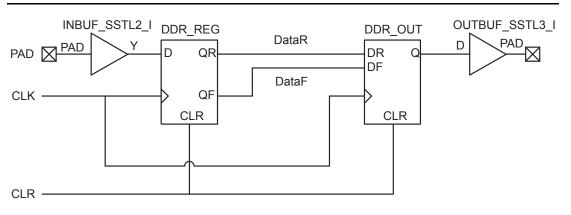

The I/Os in Fusion, IGLOO, and ProASIC3 devices support Double Data Rate (DDR) mode. In this mode, new data is present on every transition (or clock edge) of the clock signal. This mode doubles the data transfer rate compared with Single Data Rate (SDR) mode, where new data is present on one transition (or clock edge) of the clock signal. Low power flash devices have DDR circuitry built into the I/O tiles. I/Os are configured to be DDR receivers or transmitters by instantiating the appropriate special macros (examples shown in Figure 9-4 on page 210 and Figure 9-5 on page 211) and buffers (DDR\_OUT or DDR\_REG) in the RTL design. This document discusses the options the user can choose to configure the I/Os in this mode and how to instantiate them in the design.

# Double Data Rate (DDR) Architecture

Low power flash devices support 350 MHz DDR inputs and outputs. In DDR mode, new data is present on every transition of the clock signal. Clock and data lines have identical bandwidths and signal integrity requirements, making them very efficient for implementing very high-speed systems. High-speed DDR interfaces can be implemented using LVDS (not applicable for IGLOO nano and ProASIC3 nano devices). In IGLOOe, ProASIC3E, AFS600, and AFS1500 devices, DDR interfaces can also be implemented using the HSTL, SSTL, and LVPECL I/O standards. The DDR feature is primarily implemented in the FPGA core periphery and is not tied to a specific I/O technology or limited to any I/O standard.

Figure 9-1 • DDR Support in Low Power Flash Devices

Programming Flash Devices

# List of Changes

| Date      | Changes                                                                                                                                                                                                                                                                                                         | Page |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| July 2010 | FlashPro4 is a replacement for FlashPro3 and has been added to this chapter.<br>FlashPro is no longer available.                                                                                                                                                                                                | N/A  |

|           | The chapter was updated to include SmartFusion devices.                                                                                                                                                                                                                                                         | N/A  |

| July 2010 | The following were deleted:                                                                                                                                                                                                                                                                                     | N/A  |

|           | "Live at Power-Up (LAPU) or Boot PROM" section                                                                                                                                                                                                                                                                  |      |

|           | "Design Security" section                                                                                                                                                                                                                                                                                       |      |

|           | Table 14-2 • Programming Features for Actel Devices and much of the text in the "Programming Features for Microsemi Devices" section                                                                                                                                                                            |      |

|           | "Programming Flash FPGAs" section                                                                                                                                                                                                                                                                               |      |

|           | "Return Material Authorization (RMA) Policies" section                                                                                                                                                                                                                                                          |      |

|           | The "Device Programmers" section was revised.                                                                                                                                                                                                                                                                   | 225  |

|           | The Independent Programming Centers information was removed from the "Volume Programming Services" section.                                                                                                                                                                                                     | 226  |

|           | Table 10-3 • Programming Solutions was revised to add FlashPro4 and note that FlashPro is discontinued. A note was added for FlashPro Lite regarding power supply requirements.                                                                                                                                 | 227  |

|           | Most items were removed from Table 10-4 • Programming Ordering Codes, including FlashPro3 and FlashPro.                                                                                                                                                                                                         | 228  |

|           | The "Programmer Device Support" section was deleted and replaced with a reference to the Microsemi SoC Products Group website for the latest information.                                                                                                                                                       | 228  |

|           | The "Certified Programming Solutions" section was revised to add FlashPro4 and remove Silicon Sculptor I and Silicon Sculptor 6X. Reference to <i>Programming and Functional Failure Guidelines</i> was added.                                                                                                  | 228  |

|           | The file type *.pdb was added to the "Use the Latest Version of the Designer Software to Generate Your Programming File (recommended)" section.                                                                                                                                                                 | 229  |

|           | Instructions on cleaning and careful insertion were added to the "Perform Routine<br>Hardware Self-Diagnostic Test" section. Information was added regarding testing<br>Silicon Sculptor programmers with an adapter module installed before every<br>programming session verifying their calibration annually. | 229  |

|           | The "Signal Integrity While Using ISP" section is new.                                                                                                                                                                                                                                                          | 230  |

|           | The "Programming Failure Allowances" section was revised.                                                                                                                                                                                                                                                       | 230  |

The following table lists critical changes that were made in each revision of the chapter.

2. Choose the appropriate security level setting and enter a FlashLock Pass Key. The default is the **Medium** security level (Figure 11-12). Click **Next**.

If you want to select different options for the FPGA and/or FlashROM, this can be set by clicking **Custom Level**. Refer to the "Advanced Options" section on page 256 for different custom security level options and descriptions of each.

*Figure 11-12* • Medium Security Level Selected for Low Power Flash Devices

# 12 – In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

# Introduction

Microsemi's low power flash devices are all in-system programmable. This document describes the general requirements for programming a device and specific requirements for the FlashPro4/3/3X programmers<sup>1</sup>.

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low power, single-chip, live-at-power-up solution with the ASIC advantages of security and low unit cost through nonvolatile flash technology. Each device contains 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications such as Internet Protocol (IP) addressing, user system preference storage, device serialization, or subscription-based business models. IGLOO, ProASIC3, SmartFusion, and Fusion devices offer the best in-system programming (ISP) solution, FlashLock<sup>®</sup> security features, and AES-decryption-based ISP.

# **ISP** Architecture

Low power flash devices support ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system is also supported.

Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide.

Family-specific support:

- ProASIC3, ProASIC3E, SmartFusion, and Fusion devices support ISP.

- ProASIC3L devices operate using a 1.2 V core voltage; however, programming can be done only at 1.5 V. Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming.

- IGLOO and IGLOOe V5 devices can be programmed in-system when the device is using a 1.5 V supply voltage to the FPGA core.

- IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only) or 1.5 V. IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V. Voltage switching is required in-system to switch from a 1.2 V supply (VCC,VCCI, and VJTAG) to 1.5 V for programming. The exception is that V2 devices can be programmed at 1.2 V VCC with FlashPro4.

IGLOO devices cannot be programmed in-system when the device is in Flash\*Freeze mode. The device should exit Flash\*Freeze mode and be in normal operation for programming to start. Programming operations in IGLOO devices can be achieved when the device is in normal operating mode and a 1.5 V core voltage is used.

## **JTAG 1532**

IGLOO, ProASIC3, SmartFusion, and Fusion devices support the JTAG-based IEEE 1532 standard for ISP. To start JTAG operations, the IGLOO device must exit Flash\*Freeze mode and be in normal operation before starting to send JTAG commands to the device. As part of this support, when a device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN

FlashPro4 replaced FlashPro3/3X in 2010 and is backward compatible with FlashPro3/3X as long as there is no connection to pin 4 on the JTAG header on the board. On FlashPro3/3X, there is no connection to pin 4 on the JTAG header; however, pin 4 is used for programming mode (Prog\_Mode) on FlashPro4. When converting from FlashPro3/3X to FlashPro4, users should make sure that JTAG connectors on system boards do not have any connection to pin 4. FlashPro3X supports discrete TCK toggling that is needed to support non-JTAG compliant devices in the chain. This feature is included in FlashPro4.

Index

architecture of user nonvolatile 117 configuration 120 custom serialization 129 design flow 124 generation 125 programming and accessing 122 programming file 127 programming files 267 SmartGen 126 FlashROM read-back 305

## G

global architecture 31 global buffers no programmable delays 64 with PLL function 67 with programmable delays 64 global macros Synplicity 50 globals designer flow 53 networks 58 spines and rows 41

## Η

HLD code instantiating 192 hot-swap 167 hot-swapping 317

## I

I/O banks standards 40 standards compatibility 162 I/O standards 77 global macros 46 single-ended 166 I/Os assigning technologies 198 assignments defined in PDC file 193 automatically assigning 202 behavior at power-up/-down 311 board-level considerations 181 buffer schematic cell 191 cell architecture 207 configuration with SmartGen 188 features 163, 164, 167 global, naming 35 manually assigning technologies 198 nano standard 162 register combining 174 simplified buffer circuitry 165 software support 177 software-controlled attributes 187 user I/O assignment flow chart 185 user naming convention 178 wide range support 166

ISP 223, 224 architecture 261 board-level considerations 271 circuit 277 microprocessor 283

## J

JTAG 1532 261 JTAG interface 285

## L

layout device-specific 78 LTC3025 linear voltage regulator 277

### М

MAC validation/authentication 288 macros CLKBUF 77 CLKBUF LVDS/LVPECL 77 CLKDLY 65, 73 FIFO4KX18 141 **PLL 73** PLL macro signal descriptions 68 RAM4K9 137 RAM512X18 139 supported basic RAM macros 136 UJTAG 299 MCU FPGA programming model 286 memory availability 146 memory blocks 135 microprocessor programming 283 Microsemi SoC Products Group email 321 web-based technical support 321 website 321

## 0

OTP 223 output slew rate 175

## Ρ

PDC global promotion and demotion 51 place-and-route 193 PLL behavior at brownout condition 315 configuration bits 90 core specifications 84 dynamic PLL configuration 87 functional description 85 power supply decoupling scheme 112 PLL block signals 68 PLL macro block diagram 69 product support customer service 321