Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| 2 0 0 0 0 0             |                                                            |

|-------------------------|------------------------------------------------------------|

| Product Status          | Active                                                     |

| Туре                    | Fixed Point                                                |

| Interface               | Host Interface, SSI, SCI                                   |

| Clock Rate              | 100MHz                                                     |

| Non-Volatile Memory     | ROM (576B)                                                 |

| On-Chip RAM             | 24kB                                                       |

| Voltage - I/O           | 3.30V                                                      |

| Voltage - Core          | 3.30V                                                      |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                         |

| Mounting Type           | Surface Mount                                              |

| Package / Case          | 196-LBGA                                                   |

| Supplier Device Package | 196-MAPBGA (15x15)                                         |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=xc56309vf100a |

|                         |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Signal<br>Name | Туре             | State During Reset,<br>Stop, or Wait                                                                                                                                                                             | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR             | Output           | Output<br>(deasserted)<br>State during Stop/Wait<br>depends on the BRH<br>bit setting:<br>• BRH = 0: Output,<br>deasserted.<br>• BRH = 1: Maintains<br>last state (that is, if<br>asserted, remains<br>asserted) | <b>Bus Request</b><br>Asserted when the DSP requests bus mastership and deasserted when<br>the DSP no longer needs the bus. BR can be asserted or deasserted<br>independently of whether the DSP56309 is a bus master or a bus slave.<br>Bus "parking" allows BR to be deasserted even though the DSP56309 is<br>the bus master (see the description of bus "parking" in the BB signal<br>description). The Bus Request Hold (BRH) bit in the BCR allows BR to be<br>asserted under software control, even though the DSP does not need the<br>bus. BR is typically sent to an external bus arbitrator that controls the<br>priority, parking and tenure of each master on the same external bus. BR<br>is affected only by DSP requests for the external bus, never for the<br>internal bus. During hardware reset, BR is deasserted and the arbitration<br>is reset to the bus slave state. |

| BG             | Input            | Ignored Input                                                                                                                                                                                                    | <b>Bus Grant</b><br>Must be asserted/deasserted synchronous to CLKOUT for proper<br>operation. An external bus arbitration circuit asserts BG when the<br>DSP56309 becomes the next bus master. When BG is asserted, the<br>DSP56309 must wait until BB is deasserted before taking bus mastership.<br>When BG is deasserted, bus mastership is typically given up at the end of<br>the current bus cycle. This may occur in the middle of an instruction that<br>requires more than one external bus cycle for execution.                                                                                                                                                                                                                                                                                                                                                                    |

| BB             | Input/<br>Output | Ignored Input                                                                                                                                                                                                    | Bus BusyIndicates that the bus is active and must be asserted and deassertedsynchronous to CLKOUT. Only after $\overline{BB}$ is deasserted can the pendingbus master become the bus master (and then assert the signal again).The bus master can keep $\overline{BB}$ asserted after ceasing bus activity,regardless of whether $\overline{BR}$ is asserted or deasserted. This is called "busparking" and allows the current bus master to reuse the bus withoutre-arbitration until another device requires the bus. $\overline{BB}$ is deasserted byan "active pull-up" method (that is, $\overline{BB}$ is driven high and then releasedand held high by an external pull-up resistor). $\overline{BB}$ requires an external pull-up resistor.                                                                                                                                           |

| CAS            | Output           | Tri-stated                                                                                                                                                                                                       | <b>Column Address Strobe</b><br>When the DSP is the bus master, DRAM uses CAS to strobe the column<br>address. Otherwise, if the Bus Mastership Enable (BME) bit in the DRAM<br>Control Register is cleared, the signal is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BCLK           | Output           | Tri-stated                                                                                                                                                                                                       | <b>Bus Clock</b><br>When the DSP is the bus master, BCLK is active when the OMR[ATE] is<br>set. When BCLK is active and synchronized to CLKOUT by the internal<br>PLL, BCLK precedes CLKOUT by one-fourth of a clock cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| BCLK           | Output           | Tri-stated                                                                                                                                                                                                       | Bus Clock Not<br>When the DSP is the bus master, $\overline{BCLK}$ is the inverse of the BCLK signal.<br>Otherwise, the signal is tri-stated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 2-8. External Bus Control Signals (Continued)

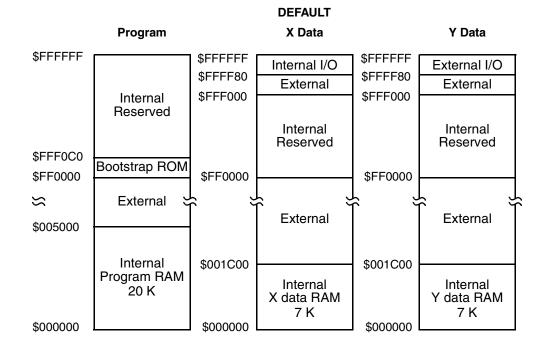

ory Configuration

# 3.3 Y Data Memory Space

The Y data memory space consists of the following:

- Internal Y data memory (7 K by default or 5 K)

- External I/O space (upper 128 locations)

- Optional off-chip memory expansion (up to 64 K in 16-bit mode, or 256 K in 24-bit mode using the 18 external address lines, or 4 M using the external address lines and the four address attribute lines). Refer to the *DSP56300 Family Manual*, especially **Chapter 9**, *External Memory Interface (Port A)*, for details on using the external memory interface to access external Y data memory.

**Note:** The Y memory space at \$FF0000–\$FFEFFF is reserved and should not be accessed.

# 3.3.1 Internal Y Data Memory

The default internal Y data RAM is a 24-bit-wide, internal, static memory occupying the lowest 7 K (\$0000–\$1BFF) of Y memory space. The internal Y data RAM is organized into 28 banks with 256 locations each. Available Y data memory space is decreased by 2 K through reallocation of program memory using the memory switch mode described in the next section.

# 3.3.2 Memory Switch Modes—Y Data Memory

Memory switch mode reallocates of portions of X and Y data memory to internal program RAM. Bit 7 in the OMR is the MS bit that controls this function, as follows:

- When the MS bit is cleared, the Y data memory consists of the default 7 K × 24-bit memory space described in the previous section. In this default mode, the lowest external Y data memory location is \$1C00.

- When the MS bit is set, a portion of the higher locations of X and Y data memory are shifted to internal program RAM. The Y data memory in this mode consists of a 5 K × 24-bit memory space. In this mode, the lowest external Y data memory location is \$1400.

## 3.3.3 External I/O Space—Y Data Memory

The off-chip peripheral registers should be mapped into the top 128 locations of Y data memory (\$FFFF80-\$FFFFFF in the 24-bit Address mode or \$FF80-\$FFFF in the 16-bit Address mode) to take advantage of the Move Peripheral Data (MOVEP) instruction and the bit-oriented instructions (BCHG, BCLR, BSET, BTST, BRCLR, BRSET, BSCLR, BSSET, JCLR, JSET, JSCLR, and JSSET).

| Bit Settings |    | Memory Configuration |                       |                      |                      |       |                            |

|--------------|----|----------------------|-----------------------|----------------------|----------------------|-------|----------------------------|

| SC           | MS | CE                   | Program RAM           | X Data RAM           | Y Data RAM           | Cache | Addressable<br>Memory Size |

| 0            | 0  | 0                    | 20 K<br>\$0000–\$4FFF | 7 K<br>\$0000–\$1BFF | 7 K<br>\$0000–\$1BFF | None  | 16 M                       |

| Figure 3-1. | Default Settings | (0, 0, 0) |

|-------------|------------------|-----------|

|-------------|------------------|-----------|

#### **Operating Modes**

| Table 4-1. | DSP56309 Operating N | Modes (Continued) |

|------------|----------------------|-------------------|

|------------|----------------------|-------------------|

| Mode | MODD | MODC | MODB | MODA | Reset<br>Vector | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------|------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D    | 1    | 1    | 0    | 1    | \$FF0000        | HI08 bootstrap in HC11 nonmultiplexed mode<br>The bootstrap program sets the host interface to interface with<br>the Freescale HC11 microcontroller through the HI08. The<br>HOST HC11 bootstrap code expects to read a 24-bit word<br>specifying the number of program words, a 24-bit word<br>specifying the address to start loading the program words and<br>then a 24-bit word for each program word to be loaded. The<br>program words are stored in contiguous PRAM memory<br>locations starting at the specified starting address. After reading<br>the program words, program execution starts from the same<br>address where loading started. The Host Interface bootstrap<br>load program may be stopped by setting the Host Flag 0 (HF0).<br>This starts execution of the loaded program from the specified<br>starting address.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| E    | 1    | 1    | 1    | 0    | \$FF0000        | HI08 bootstrap in 8051 multiplexed bus mode<br>The bootstrap program sets the host interface to interface with<br>the Intel 8051 bus through the HI08. The HI08 pin configuration<br>is optimized for connection to the Intel 8051 multiplexed bus, in<br>double-strobe pin configuration. The HOST 8051 bootstrap code<br>expects accesses that are byte wide. The HOST 8051 bootstrap<br>code expects to read 3 bytes forming a 24-bit word specifying<br>the number of program words, 3 bytes forming a 24-bit word<br>specifying the address to start loading the program words and<br>then 3 bytes forming 24-bit words for each program word to be<br>loaded. The program words are stored in contiguous PRAM<br>memory locations starting at the specified starting address. After<br>reading the program words, program execution starts from the<br>same address where loading started. The Host Interface<br>bootstrap load program may be stopped by setting the Host Flag<br>0 (HF0). This starts execution of the loaded program from the<br>specified starting address. The base address of the HI08 in<br>multiplexed mode is 0x80 and is not modified by the bootstrap<br>code. All the address lines are enabled and should be connected<br>accordingly. |

| F    | 1    | 1    | 1    | 1    | \$FF0000        | HI08 bootstrap in MC68302 bus mode<br>The bootstrap program loads the program RAM from the Host<br>Interface programmed to operate in the MC68302 bus mode, in<br>single-strobe pin configuration. The HOST MC68302 bootstrap<br>code expects accesses that are byte wide. The HOST MC68302<br>bootstrap code expects to read 3 bytes forming a 24-bit word<br>specifying the number of program words, 3 bytes forming a<br>24-bit word specifying the address to start loading the program<br>words and then 3 bytes forming 24-bit words for each program<br>word to be loaded. The program words are stored in contiguous<br>PRAM memory locations starting at the specified starting<br>address. After reading the program words, program execution<br>starts from the same address where loading started. The Host<br>Interface bootstrap load program may be stopped by setting the<br>Host Flag 0 (HF0). This starts execution of the loaded program<br>from the specified starting address.                                                                                                                                                                                                                                                                       |

| Interrupt<br>Starting Address | Interrupt<br>Priority Level<br>Range | Interrupt Source                          |  |

|-------------------------------|--------------------------------------|-------------------------------------------|--|

| VBA:\$00                      | 3                                    | Hardware RESET                            |  |

| VBA:\$02                      | 3                                    | Stack error                               |  |

| VBA:\$04                      | 3                                    | Illegal instruction                       |  |

| VBA:\$06                      | 3                                    | Debug request interrupt                   |  |

| VBA:\$08                      | 3                                    | Тгар                                      |  |

| VBA:\$0A                      | 3                                    | Nonmaskable interrupt (MII)               |  |

| VBA:\$0C                      | 3                                    | Reserved                                  |  |

| VBA:\$0E                      | 3                                    | Reserved                                  |  |

| VBA:\$10                      | 0–2                                  | IRQA                                      |  |

| VBA:\$12                      | 0–2                                  | IRQB                                      |  |

| VBA:\$14                      | 0–2                                  | IRQC                                      |  |

| VBA:\$16                      | 0–2                                  | IRQD                                      |  |

| VBA:\$18                      | 0–2                                  | DMA channel 0                             |  |

| VBA:\$1A                      | 0–2                                  | DMA channel 1                             |  |

| VBA:\$1C                      | 0–2                                  | DMA channel 2                             |  |

| VBA:\$1E                      | 0–2                                  | DMA channel 3                             |  |

| VBA:\$20                      | 0–2                                  | DMA channel 4                             |  |

| VBA:\$22                      | 0–2                                  | DMA channel 5                             |  |

| VBA:\$24                      | 0–2                                  | TIMER 0 compare                           |  |

| VBA:\$26                      | 0–2                                  | TIMER 0 overflow                          |  |

| VBA:\$28                      | 0–2                                  | TIMER 1 compare                           |  |

| VBA:\$2A                      | 0–2                                  | TIMER 1 overflow                          |  |

| VBA:\$2C                      | 0–2                                  | TIMER 2 compare                           |  |

| VBA:\$2E                      | 0–2                                  | TIMER 2 overflow                          |  |

| VBA:\$30                      | 0–2                                  | ESSI0 receive data                        |  |

| VBA:\$32                      | 0–2                                  | ESSI0 receive data with exception status  |  |

| VBA:\$34                      | 0–2                                  | ESSI0 receive last slot                   |  |

| VBA:\$36                      | 0–2                                  | ESSI0 transmit data                       |  |

| VBA:\$38                      | 0–2                                  | ESSI0 transmit data with exception status |  |

| VBA:\$3A                      | 0–2                                  | ESSI0 transmit last slot                  |  |

| VBA:\$3C                      | 0–2                                  | Reserved                                  |  |

| VBA:\$3E                      | 0–2                                  | Reserved                                  |  |

| VBA:\$40                      | 0–2                                  | ESSI1 receive data                        |  |

| VBA:\$42                      | 0–2                                  | ESSI1 receive data with exception status  |  |

Configuration

| Interrupt<br>Starting Address | Interrupt<br>Priority Level<br>Range | Interrupt Source                          |  |

|-------------------------------|--------------------------------------|-------------------------------------------|--|

| VBA:\$44                      | 0–2                                  | ESSI1 receive last slot                   |  |

| VBA:\$46                      | 0–2                                  | ESSI1 transmit data                       |  |

| VBA:\$48                      | 0–2                                  | ESSI1 transmit data with exception status |  |

| VBA:\$4A                      | 0–2                                  | ESSI1 transmit last slot                  |  |

| VBA:\$4C                      | 0–2                                  | Reserved                                  |  |

| VBA:\$4E                      | 0–2                                  | Reserved                                  |  |

| VBA:\$50                      | 0–2                                  | SCI receive data                          |  |

| VBA:\$52                      | 0–2                                  | SCI receive data with exception status    |  |

| VBA:\$54                      | 0–2                                  | SCI transmit data                         |  |

| VBA:\$56                      | 0–2                                  | SCI idle line                             |  |

| VBA:\$58                      | 0–2                                  | SCI timer                                 |  |

| VBA:\$5A                      | 0–2                                  | Reserved                                  |  |

| VBA:\$5C                      | 0–2                                  | Reserved                                  |  |

| VBA:\$5E                      | 0–2                                  | Reserved                                  |  |

| VBA:\$60                      | 0–2                                  | Host receive data full                    |  |

| VBA:\$62                      | 0–2                                  | Host transmit data empty                  |  |

| VBA:\$64                      | 0–2                                  | Host command (default)                    |  |

| VBA:\$66                      | 0–2                                  | Reserved                                  |  |

| :                             | :                                    | :                                         |  |

| VBA:\$FE                      | 0–2                                  | Reserved                                  |  |

| Table 4-5. | Interrupt Sources | (Continued) |

|------------|-------------------|-------------|

|------------|-------------------|-------------|

## 4.4.3 Processing Interrupt Source Priorities Within an IPL

If more than one interrupt request is pending when an instruction executes, the interrupt source with the highest IPL is serviced first. When several interrupt requests with the same IPL are pending, another fixed-priority structure within that IPL determines which interrupt source is serviced first. **Table 4-6** shows this fixed-priority list of interrupt sources within an IPL, from highest to lowest at each level The interrupt mask bits in the Status Register (I[1–0]) can be programmed to ignore low priority-level interrupt requests.

| Priority | Interrupt Source      |  |  |

|----------|-----------------------|--|--|

|          | Level 3 (nonmaskable) |  |  |

| Highest  | Hardware RESET        |  |  |

|          | Stack error           |  |  |

#### Table 4-6. Interrupt Source Priorities Within an IPL

| Bit Number | Bit Name | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |  |

|------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|

| 2          | HCIE     | 0           | Host Command Interrupt Enable<br>Generates a host command interrupt request if the host command pending<br>(HCP) status bit in the HSR is set. If HCIE is cleared, HCP interrupts are<br>disabled. The interrupt address is determined by the host command vector<br>register (CVR).<br>NOTE: If more than one interrupt request source is asserted and enabled<br>(for example, HRDF is set, HCP is set, HRIE is set, and HCIE is set), the<br>HI08 generates interrupt requests according to priorities shown here. The bit<br>value is indeterminate after an individual reset. |                          |  |

|            |          |             | Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Interrupt Source         |  |

|            |          |             | Highest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Host Command (HCP = 1)   |  |

|            |          |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transmit Data (HTDE = 1) |  |

|            |          |             | Lowest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Receive Data (HRDF = 1)  |  |

| 1          | HTIE     | 0           | Host Transmit Interrupt Enable<br>Generates a host transmit data interrupt request if the host transmit data<br>empty (HTDE) bit in the HSR is set. The HTDE bit is set when data is<br>transferred from the HTX to the RXH, RXM, or RXL registers. If HTIE is<br>cleared, HTDE interrupts are disabled. The bit value is indeterminate after<br>an individual reset.                                                                                                                                                                                                              |                          |  |

| 0          | HRIE     | 0           | Host Receive Interrupt Enable<br>Generates a host receive data interrupt request if the host receive data full<br>(HRDF) bit in the host status register (HSR, Bit 0) is set. The HRDF bit is set<br>when data is transferred to the HRX from the TXH, TXM, or TXL registers. If<br>HRIE is cleared, HRDF interrupts are disabled. The bit value is<br>indeterminate after an individual reset.                                                                                                                                                                                    |                          |  |

#### Table 6-8. Host Control Register (HCR) Bit Definitions

### 6.6.2 Host Status Register (HSR)

The HSR is a 16-bit read-only status register by which the DSP reads the HI08 status and flags. The host processor cannot access it directly. The initialization values for the HSR bits are discussed in **Section 6.6.9**, *DSP-Side Registers After Reset*, on page 6-20.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3   | 2   | 1    | 0    |

|----|----|----|----|----|----|---|---|---|---|---|-----|-----|-----|------|------|

|    |    |    |    |    |    |   |   |   |   |   | HF1 | HF0 | HCP | HTDE | HRDF |

-Reserved bit; read as 0; write to 0 for future compatibility.

Figure 6-7. Host Status Register (HSR) (X:\$FFFFC3)

| Bit Number | Bit Name | Reset Value | Description                                    |

|------------|----------|-------------|------------------------------------------------|

| 15–5       |          | 0           | Reserved. Write to 0 for future compatibility. |

NP

Interface (HI08)

| Dogistor         | Deriotor                   |                |              | Reset Type                       |                                  |

|------------------|----------------------------|----------------|--------------|----------------------------------|----------------------------------|

| Register<br>Name | Register<br>Data           | HW<br>Reset    | SW<br>Reset  | Individual Reset                 | STOP                             |

| ISR              | HREQ                       | 0              | 0            | 1 if TREQ is set;<br>0 otherwise | 1 if TREQ is set;<br>0 otherwise |

|                  | HF3 -HF2                   | 0              | 0            | _                                | _                                |

|                  | TRDY                       | 1              | 1            | 1                                | 1                                |

|                  | TXDE                       | 1              | 1            | 1                                | 1                                |

|                  | RXDF                       | 0              | 0            | 0                                | 0                                |

| IVR              | IV[0–7]                    | \$0F           | \$0F         | _                                | _                                |

| RX               | RXH:RXM:RXL                | empty          | empty        | empty                            | empty                            |

| ΤX               | TXH:TXM:TXL                | empty          | empty        | empty                            | empty                            |

| Note: A long     | g dash (—) denotes that th | e bit value is | not affected | by the specified reset.          |                                  |

Table 6-18. Host-Side Registers After Reset (Continued)

# 6.8 Programming Model Quick Reference

Table 6-19 summarizes the HI08 programming model.

|          |                                       |       |                                  | Bit    |                                                   |           | Reset Type      | 9    |

|----------|---------------------------------------|-------|----------------------------------|--------|---------------------------------------------------|-----------|-----------------|------|

| Register | Bit<br>No.                            | Bit   | Name                             | Value  | Function                                          | HW/<br>SW | Indivi-<br>dual | STOP |

| HCR      | 0                                     | HRIE  | Receive Interrupt<br>Enable      | 0<br>1 | HRRQ interrupt disabled<br>HRRQ interrupt enabled | 0         |                 | —    |

|          | 1 HTIE                                |       | Transmit<br>Interrupt Enable     | 0<br>1 | HTRQ interrupt disabled<br>HTRQ interrupt enabled | 0         | _               | —    |

|          | 2                                     | HCIE  | Host Command<br>Interrupt Enable | 0<br>1 | HCP interrupt disabled<br>HCP interrupt enabled   | 0         | _               | —    |

|          | 3                                     | HF2   | HF2 Host Flag 2                  |        |                                                   | 0         |                 |      |

|          | 4                                     | HF3   | Host Flag 3                      |        |                                                   | 0         |                 | —    |

| HPCR     | 0                                     | HGEN  | Host GPIO<br>Enable              | 0<br>1 | GPIO signal disconnected<br>GPIO signals active   | 0         |                 | —    |

|          | 1                                     | HA8EN | Host Address<br>Line 8 Enable    | 0<br>1 | HA8/A1 = GPIO<br>HA8/A1 = HA8                     | 0         | _               | —    |

|          | 2 HA9EN Host Address<br>Line 9 Enable |       |                                  | 0<br>1 | HA9/A2 = GPIO<br>HA9/A2 = HA9                     | 0         | —               | -    |

|          | 3                                     | HCSEN | Host Chip Select<br>Enable       | 0<br>1 | HCS/A10 = GPIO<br>HCS/A10 = HCS                   | 0         |                 | —    |

Table 6-19.

HI08 Programming Model, DSP Side

Interface (HI08)

|          |                |              |                                  |        |                                                                                        | Reset Typ  | е               |      |

|----------|----------------|--------------|----------------------------------|--------|----------------------------------------------------------------------------------------|------------|-----------------|------|

| Register | Bit<br>No. Bit |              | Name                             | Value  | Function                                                                               | HW/<br>SW  | Indivi-<br>dual | STOP |

| HSR      | 0              | HRDF         | Host Receive<br>Data Full        | 0<br>1 | no receive data to be read<br>Receive Data Register is full                            | 0          | 0               | 0    |

|          | 1 HTDE         |              | Host Transmit<br>Data Empty      | 1<br>0 | The Transmit Data Register is<br>empty.<br>The Transmit Data Register is not<br>empty. | 1          | 1               | 1    |

|          | 2              | HCP          | Host Command<br>Pending          | 0<br>1 | no host command pending host command pending                                           | 0          | 0               | 0    |

|          | 3              | HF0          | Host Flag 0                      |        |                                                                                        | 0          | _               | —    |

|          | 4              | HF1          | Host Flag 1                      |        |                                                                                        | 0          | _               | -    |

| HBAR     | 7–0            | BA[10–3<br>] | Host Base<br>Address<br>Register |        |                                                                                        | \$80       |                 |      |

| HRX      | 23–<br>0       |              | DSP Receive<br>Data Register     |        |                                                                                        | empt<br>y  |                 |      |

| НТХ      | 23–<br>0       |              | DSP Transmit<br>Data Register    |        |                                                                                        | empt<br>y  |                 |      |

| HDR      | 16–<br>0       | D[16–0]      | GPIO signal<br>Data              |        |                                                                                        | \$000<br>0 |                 | —    |

| HDRR     | 16–<br>0       | DR[16–<br>0] | GPIO signal<br>Direction         | 0<br>1 | Input<br>Output                                                                        | \$000<br>0 |                 | —    |

## Table 6-19. HI08 Programming Model, DSP Side (Continued)

#### Table 6-20. HI08 Programming Model: Host Side

|     |   |       | Bit                     |        |                                                                                | R         | eset Ty             | vpe  |

|-----|---|-------|-------------------------|--------|--------------------------------------------------------------------------------|-----------|---------------------|------|

| Reg | # |       | Name                    | Value  | Function                                                                       | HW/<br>SW | Indi<br>vi-d<br>ual | STOP |

| ICR | 0 | RREQ  | Receive Request Enable  | 0<br>1 | HRRQ interrupt disabled<br>HRRQ interrupt enabled                              | 0         | —                   |      |

|     | 1 | TREQ  | Transmit Request Enable | 0<br>1 | HTRQ interrupt disabled<br>HTRQ interrupt enabled                              | 0         | _                   | _    |

|     | 2 | HDRQ  | Double Host Request     | 0      | HREQ/HTRQ = HREQ,<br>HACK/HRRQ = HACK<br>HREQ/HTRQ = HTRQ,<br>HACK/HRRQ = HRRQ | 0         | _                   |      |

|     | 3 | HF0   | Host Flag 0             |        |                                                                                | 0         |                     | _    |

|     | 4 | HF1   | Host Flag 1             |        |                                                                                | 0         |                     | —    |

|     | 5 | HLEND | Host Little Endian      | 0<br>1 | Big Endian order<br>Little Endian order                                        | 0         |                     | _    |

|     | 7 | INIT  | Initialize              | 1      | Reset data paths according to<br>TREQ and RREQ                                 | 0         | —                   | —    |

After the first transmit, subsequent transmit values are typically loaded into TXnn by the ISR (one value per register per interrupt). Therefore, if N items are to be sent from a particular TXnn, the ISR needs to load the transmit register (N - 1) times. **Steps 2c** and **2d** can be performed in **step 2a** as a single instruction. If an interrupt trigger event occurs before all interrupt trigger configuration steps are performed, the event is ignored and not queued. If interrupts derived from the core or other peripherals need to be enabled at the same time as ESSI interrupts, **step 2f** should be performed last.

# 7.4 Operating Modes: Normal, Network, and On-Demand

The ESSI has three basic operating modes and several data and operation formats. These modes are programmed via the ESSI control registers. The data and operation formats available to the ESSI are selected when you set or clear control bits in the CRA and CRB. These control bits are WL[2–1], MOD, SYN, FSL[1–0], FSR, FSP, CKP, and SHFD.

# 7.4.1 Normal/Network/On-Demand Mode Selection

To select either Normal mode or Network mode, clear or set CRB[MOD]. In Normal mode, the ESSI sends or receives one data word per frame (per enabled receiver or transmitter). In Network mode, 2 to 32 time slots per frame can be selected. During each frame, 0 to 32 data words are received or transmitted (from each enabled receiver or transmitter). In either case, the transfers are periodic.

The Normal mode typically transfers data to or from a single device. Network mode is typically used in time division multiplexed networks of CODECs or DSPs with multiple words per frame.

Network mode has a submode called On-Demand mode. Set the CRB[MOD] for Network mode, and set the frame rate divider to 0 (DC = \$00000) to select On-Demand mode. This submode does not generate a periodic frame sync. A frame sync pulse is generated only when data is available to transmit. The frame sync signal indicates the first time slot in the frame. On-Demand mode requires that the transmit frame sync be internal (output) and the receive frame sync be external (input). For simplex operation, Synchronous mode could be used; however, for full-duplex operation, Asynchronous mode must be used. You can enable data transmission that is data-driven by writing data into each TX. Although the ESSI is double-buffered, only one word can be written to each TX, even if the transmit shift register is empty. The receive and transmit interrupts function normally, using TDE and RDF; however, transmit underruns are impossible for On-Demand transmission and are disabled. This mode is useful for interfacing with codecs requiring a continuous clock.

Note: When the ESSI transmits data in On-Demand mode (that is, MOD = 1 in the CRB and DC[4-0] = \$00000 in the CRA) with WL[2-0] = 100, the transmission does not work properly. To ensure correct operation, do not use On-Demand mode with the WL[2-0] = 100 32-bit word length mode.

This section discusses the ESSI registers and describes their bits. Section 7.6, *GPIO Signals and Registers*, on page 7-33 covers ESSI GPIO.

# 7.5.1 ESSI Control Register A (CRA)

The ESSI Control Register A (CRA) is one of two 24-bit read/write control registers that direct the operation of the ESSI. CRA controls the ESSI clock generator bit and frame sync rates, word length, and number of words per frame for serial data.

| 23 | 22   | 21  | 20  | 19  | 18  | 17 | 16  | 15  | 14  | 13  | 12  |

|----|------|-----|-----|-----|-----|----|-----|-----|-----|-----|-----|

|    | SSC1 | WL2 | WL1 | WL0 | ALC |    | DC4 | DC3 | DC2 | DC1 | DC0 |

| 11 | 10   | 9   | 8   | 7   | 6   | 5  | 4   | 3   | 2   | 1   | 0   |

|    |      |     |     |     |     |    |     |     |     |     |     |

Reserved bit; read as 0; write to 0 for future compatibility.

(ESSI0 X:\$FFFFB5, ESSI1 X:\$FFFFA5)

| Figure 7-2. | ESSI | Control | Register | A(CRA) |

|-------------|------|---------|----------|--------|

|-------------|------|---------|----------|--------|

| Bit Number | Bit Name | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         |          | 0           | Reserved. Write to 0 for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22         | SSC1     | 0           | Select SC1<br>Controls the functionality of the SC1 signal. If SSC1 is set, the ESSI is<br>configured in Synchronous mode (the CRB synchronous/asynchronous bit<br>(SYN) is set), and transmitter 2 is disabled (transmit enable (TE2) = 0), then<br>the SC1 signal acts as the transmitter 0 driver-enabled signal while the SC1<br>signal is configured as output (SCD1 = 1). This configuration enables an<br>external buffer for the transmitter 0 output. If SSC1 is cleared, the ESSI is<br>configured in Synchronous mode (SYN = 1), and transmitter 2 is disabled<br>(TE2 = 0), then the SC1 acts as the serial I/O flag while the SC1 signal is<br>configured as output (SCD1 = 1). |

#### Table 7-3. ESSI Control Register A (CRA) Bit Definitions

# NP

# 7.5.2 ESSI Control Register B (CRB)

CRB is one of two read/write control registers that direct the operation of the ESSI (see **Figure 7-5**). The CRB bit definitions are presented in **Table 7-4**. CRB controls the ESSI multifunction signals, SC[2–0], which can be used as clock inputs or outputs, frame synchronization signals, transmit data signals, or serial I/O flag signals.

| 23   | 22   | 21   | 20   | 19  | 18  | 17 | 16  | 15  | 14  | 13  | 12  |

|------|------|------|------|-----|-----|----|-----|-----|-----|-----|-----|

| REIE | TEIE | RLIE | TLIE | RIE | TIE | RE | TE0 | TE1 | TE2 | MOD | SYN |

| 11   | 10   | 9    | 8    | 7   | 6   | 5  | 4   | 2   | 2   | - 1 | 0   |

|      | 10   | 9    | 0    | 1   | 0   | 5  | 4   | 3   | 2   |     | U   |

(ESSI0 X:\$FFFFB6, ESSI1 X:\$FFFFA6)

Figure 7-5. ESSI Control Register B (CRB)

The CRB contains the serial output flag control bits and the direction control bits for the serial control signals. Also in the CRB are interrupt enable bits for the receiver and the transmitter. Bit settings of the CRB determines how many transmitters are enabled: 0, 1, 2, or 3. The CRB settings also determine the ESSI operating mode. Either a hardware RESET signal or a software RESET instruction clears all the bits in the CRB. **Table 7-2**, *Mode and Signal Definitions*, on page 7-4 summarizes the relationship between the ESSI signals SC[2–0], SCK, and the CRB bits.

The ESSI has two serial output flag bits, OF1 and OF0. The normal sequence follows for setting output flags when transmitting data (by transmitter 0 through the STD signal only).

- **1.** Wait for TDE (TX0 empty) to be set.

- **2.** Write the flags.

- **3.** Write the transmit data to the TX register

Bits OF0 and OF1 are double-buffered so that the flag states appear on the signals when the TX data is transferred to the transmit shift register. The flag bit values are synchronized with the data transfer. The timing of the optional serial output signals SC[2–0] is controlled by the frame timing and is not affected by the settings of TE2, TE1, TE0, or the receive enable (RE) bit of the CRB.

The ESSI has three transmit enable bits (TE[2–0]), one for each data transmitter. The process of transmitting data from TX1 and TX2 is the same. TX0 differs from these two bits in that it can also operate in Asynchronous mode. The normal transmit enable sequence is to write data to one or more transmit data registers (or the Time Slot Register (TSR)) before you set the TE bit. The normal transmit disable sequence is to set the Transmit Data Empty (TDE) bit and then to clear the TE, Transmit Interrupt Enable (TIE), and Transmit Exception Interrupt Enable (TEIE) bits. In Network mode, if you clear the appropriate TE bit and set it again, then you disable the corresponding transmitter (0, 1, or 2) after transmission of the current data word. The transmitter remains disabled until the beginning of the next frame. During that time period, the

I Communication Interface (SCI)

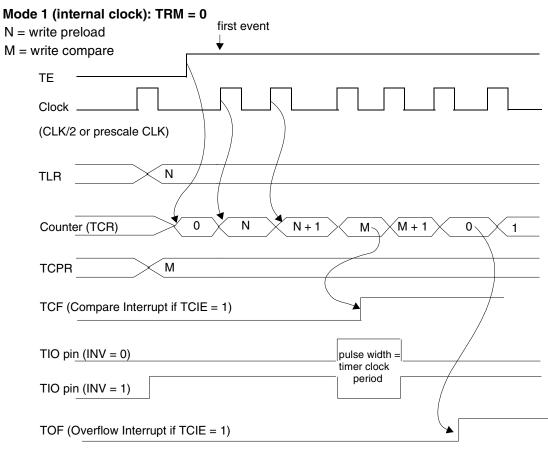

# **Triple Timer Module**

The timers in the DSP56309 internal triple timer module act as timed pulse generators or as pulse-width modulators. Each timer has a single signal that can function as a GPIO signal or as a timer signal. Each timer can also function as an event counter to capture an event or to measure the width or period of a signal.

# 9.1 Overview

The timer module contains a common 21-bit prescaler and three independent and identical general-purpose 24-bit timer/event counters, each with its own register set. Each timer has the following capabilities:

- Uses internal or external clocking

- Interrupts the DSP56309 after a specified number of events (clocks) or signals an external device after counting internal events

- Triggers DMA transfers after a specified number of events (clocks) occurs

- Connects to the external world through one bidirectional signal, designated TIO[0-2] for timers 0-2.

When TIO is configured as an input, the timer functions as an external event counter or measures external pulse width/signal period. When TIO is configured as an output, the timer functions as a timer, a watchdog timer, or a pulse-width modulator. When the timer does not use TIO, it can be used as a GPIO signal (also called TIO[0–2]).

## 9.1.1 Triple Timer Module Block Diagram

**Figure 9-1** shows a block diagram of the triple timer module. This module includes a 24-bit Timer Prescaler Load Register (TPLR), a 24-bit Timer Prescaler Count Register (TPCR), and three timers. Each timer can use the prescaler clock as its clock source.

e Timer Module

Figure 9-6. Pulse Mode (TRM = 0)

### 9.3.1.3 Timer Toggle (Mode 2)

|     | Bit Se | ettings |     | Mode Characteristics |        |       |        |          |  |  |

|-----|--------|---------|-----|----------------------|--------|-------|--------|----------|--|--|

| TC3 | TC2    | TC1     | TC0 | Mode Name Function   |        |       |        | Clock    |  |  |

| 0   | 0      | 1       | 0   | 2                    | Toggle | Timer | Output | Internal |  |  |

In Mode 2, the timer periodically toggles the polarity of the TIO signal. When the timer is enabled, the TIO signal is loaded with the value of the TCSR[INV] bit. When the counter value matches the value in the TCPR, the polarity of the TIO output signal is inverted. TCSR[TCF] is set, and a compare interrupt is generated if the TCSR[TCIE] bit is set. If the TCSR[TRM] bit is set, the counter is loaded with the value of the TLR when the next timer clock is received, and the count resumes. If the TRM bit is cleared, the counter continues to increment on each timer clock. This process repeats until the timer is cleared (disabling the timer). The TCPR[TLR] value sets the delay between starting the timer and toggling the TIO signal. To generate output signals with a delay of X clock cycles between toggles, set the TLR value to X/2, and set the TCSR[TRM] bit. This process repeats until the timer is disabled (that is, TCSR[TE] is cleared).

**Bootstrap Code**

| ; 2 - HC11                              | - Single strobe non-multiplexed bus with positive strobe   |

|-----------------------------------------|------------------------------------------------------------|

| ;                                       | pulse single negative request.                             |

| ; 4 - i8051                             | - Dual strobes multiplexed bus with negative strobe pulses |

| ;                                       | dual negative request.                                     |

| ; 5 - MC68302                           | - Single strobe non-multiplexed bus with negative strobe   |

| ;                                       | pulse single negative request.                             |

| ;====================================== |                                                            |

MC68302HOSTLD

| MC0050Z            | позтър   |                                                                            |                                               |                                                                                                                                  |                                                                           |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|----------|----------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | movep    | #%0000000001110                                                            |                                               |                                                                                                                                  |                                                                           |                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            | ;                                             | Config                                                                                                                           | gur                                                                       | ce                                                                              | the following conditions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |          |                                                                            | ;                                             | HAP                                                                                                                              | =                                                                         | 0                                                                               | Negative host acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |          |                                                                            | ;                                             | HRP                                                                                                                              | =                                                                         | 0                                                                               | Negative host request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |          |                                                                            | ;                                             | HCSP                                                                                                                             | =                                                                         | 0                                                                               | Negatice chip select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |          |                                                                            | ;                                             | HD/HS                                                                                                                            | =                                                                         | 0                                                                               | Single strobe bus (R/W~ and DS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            | ;                                             | HMUX                                                                                                                             | =                                                                         | 0                                                                               | Non multiplexed bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |          |                                                                            | ;                                             | HASP                                                                                                                             | =                                                                         | 0                                                                               | (address strobe polarity has no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            | ;                                             |                                                                                                                                  |                                                                           |                                                                                 | meaning in non-multiplexed bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            | ;                                             | HDSP                                                                                                                             | =                                                                         | 0                                                                               | Negative data stobes polarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                    |          |                                                                            |                                               |                                                                                                                                  |                                                                           |                                                                                 | Host request is active when enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |          |                                                                            | ΄.                                            |                                                                                                                                  |                                                                           |                                                                                 | This bit should be set to 0 for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            |                                               | opure                                                                                                                            |                                                                           | 0                                                                               | future compatability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    |          |                                                                            | ;                                             | דאיבדד                                                                                                                           | _                                                                         | 0                                                                               | When the HPCR register is modified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    |          |                                                                            | ,                                             | HEN                                                                                                                              | _                                                                         | 0                                                                               | HEN should be cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                    |          |                                                                            | '                                             | ד דארבד אבד                                                                                                                      | _                                                                         | 1                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                    |          |                                                                            |                                               |                                                                                                                                  |                                                                           |                                                                                 | Host acknowledge is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                    |          |                                                                            |                                               |                                                                                                                                  |                                                                           |                                                                                 | Host requests are enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |