#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿXF

| Product Status                  | Obsolete                                                                     |

|---------------------------------|------------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                               |

| Speed                           | 400MHz                                                                       |

| Co-Processors/DSP               | -                                                                            |

| RAM Controllers                 | LPDDR, LPSDR, DDR2, SDR, SRAM                                                |

| Graphics Acceleration           | No                                                                           |

| Display & Interface Controllers | LCD, Touchscreen                                                             |

| Ethernet                        | 10/100Mbps                                                                   |

| SATA                            | -                                                                            |

| USB                             | USB 2.0 (3)                                                                  |

| Voltage - I/O                   | 1.8V, 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                            |

| Security Features               | -                                                                            |

| Package / Case                  | 324-TFBGA                                                                    |

| Supplier Device Package         | 324-TFBGA (15x15)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9g45-cu-999 |

|                                 |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

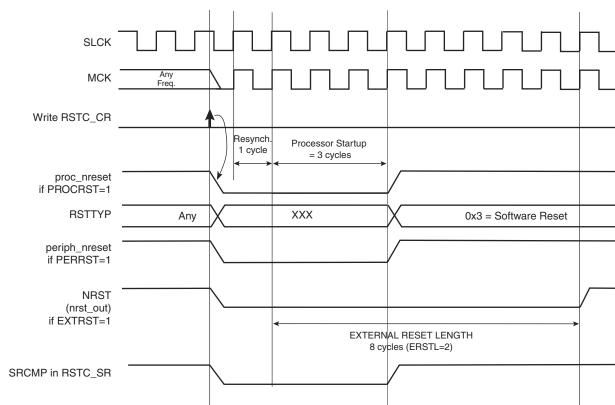

The internal reset signals are asserted as soon as the register write is performed. This is detected on the Master Clock (MCK). They are released when the software reset is left, i.e.; synchronously to SLCK.

If EXTRST is set, the nrst\_out signal is asserted depending on the programming of the field ERSTL. However, the resulting falling edge on NRST does not lead to a User Reset.

If and only if the PROCRST bit is set, the Reset Controller reports the software status in the field RSTTYP of the Status Register (RSTC\_SR). Other Software Resets are not reported in RSTTYP.

As soon as a software operation is detected, the bit SRCMP (Software Reset Command in Progress) is set in the Status Register (RSTC\_SR). It is cleared as soon as the software reset is left. No other software reset can be performed while the SRCMP bit is set, and writing any value in RSTC\_CR has no effect.

## 12.4.4.5 Watchdog Reset

The Watchdog Reset is entered when a watchdog fault occurs. This state lasts 3 Slow Clock cycles.

When in Watchdog Reset, assertion of the reset signals depends on the WDRPROC bit in WDT\_MR:

• If WDRPROC is 0, the Processor Reset and the Peripheral Reset are asserted. The NRST line is also asserted, depending on the programming of the field ERSTL. However, the resulting low level on NRST does not result in a User Reset state.

# 12.5 Reset Controller (RSTC) User Interface

| Table 12-1. | Register Mapping |

|-------------|------------------|

|-------------|------------------|

| Offset | Register         | Name    | Access     | Reset       | Backup Reset |

|--------|------------------|---------|------------|-------------|--------------|

| 0x00   | Control Register | RSTC_CR | Write-only | -           |              |

| 0x04   | Status Register  | RSTC_SR | Read-only  | 0x0000_0001 | 0x0000_0000  |

| 0x08   | Mode Register    | RSTC_MR | Read-write | -           | 0x0000_0001  |

Note: 1. The reset value of RSTC\_SR either reports a General Reset or a Wake-up Reset depending on last rising power supply.

# 14.6.2 RTC Mode Register

Name: RTC\_MR

# Address: 0xFFFFDB4

# Access Type: Read-write

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24    |

|----|----|----|----|----|----|----|-------|

| _  | -  | -  | -  | _  | _  | -  | _     |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16    |

| _  | -  | -  | -  | _  | _  | -  | _     |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8     |

| _  | _  | _  | _  | _  | _  | _  | _     |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0     |

| _  | _  | _  | _  | _  | _  | _  | HRMOD |

# • HRMOD: 12-/24-hour Mode

0 = 24-hour mode is selected.

1 = 12-hour mode is selected.

All non-significant bits read zero.

fills with zeroes. This process ensures that the least significant bits do not introduce any DC biasing, regardless of the implemented DAC's resolution (16-, 18-, or 20-bit)

## • CEM: Channel B Endian Mode

- 0: Transferring Data through Channel B is straight forward (Little-Endian).

- 1: Transferring Data through Channel B from/to a memory is performed with from/to Big-Endian format translation.

# • CEN: Channel B Enable

- 0: Data transfer is disabled on Channel B.

- 1: Data transfer is enabled on Channel B.

# • PDCEN: Peripheral Data Controller Channel Enable

0: Channel B is not transferred through a Peripheral Data Controller Channel. Related PDC flags are ignored or not generated.

1: Channel B is transferred through a Peripheral Data Controller Channel. Related PDC flags are taken into account or generated.

- LINESIZE is the horizontal size of the display in pixels, minus 1, as programmed in the LINESIZE field of the LCDFRMCFG register of the LCD Controller.

- Bpp is the number of bits per pixel configured.

- PIXELOFF is the pixel offset for 2D addressing, as programmed in the DMA2DCFG register. Applicable only if 2D addressing is being used.

- LINEVAL is the vertical size of the display in pixels, minus 1, as programmed in the LINEVAL field of the LCDFRMCFG register of the LCD Controller.

- Note: X\_size is calculated as an up-rounding of a division by 32. (This can also be done adding 31 to the dividend before using an integer division by 32). When using the 2D-addressing mode (see "2D Memory Addressing" on page 1068), it is important to note that the above calculation must be executed and the FRMSIZE field programmed with every movement of the displaying window, since a change in the PIXELOFF field can change the resulting FRMSIZE value.

# 45.6.1.4 Channel-L This block has the same functionality as Channel-U, but for the Lower Panel in dual scan mode only.

# 45.6.1.5 Control This block receives the request signals from the LCDC core and generates the requests for the channels.

# 45.6.2 LCD Controller Core

# 45.6.2.1 Configuration Block

The configuration block is a set of programmable registers that are used to configure the LCDC core operation. These registers are written via the AHB slave interface. Only word access is allowed.

The description of the configuration registers can be found in "LCD Controller (LCDC) User Interface" on page 1071.

## 45.6.2.2 Datapath

The datapath block contains five submodules: FIFO, Serializer, Palette, Dithering and Shifter. The structure of the datapath is shown in Figure 45-2.