Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                                           |

|---------------------------------|-------------------------------------------------------------------------------------------|

| Product Status                  | Active                                                                                    |

| Core Processor                  | PowerPC e5500                                                                             |

| Number of Cores/Bus Width       | 2 Core, 64-Bit                                                                            |

| Speed                           | 2.0GHz                                                                                    |

| Co-Processors/DSP               | Security; SEC 4.2                                                                         |

| RAM Controllers                 | DDR3, DDR3L                                                                               |

| Graphics Acceleration           | No                                                                                        |

| Display & Interface Controllers | -                                                                                         |

| Ethernet                        | 1Gbps (5), 10Gbps (1)                                                                     |

| SATA                            | SATA 3Gbps (2)                                                                            |

| USB                             | USB 2.0 + PHY (2)                                                                         |

| Voltage - I/O                   | -                                                                                         |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                                          |

| Security Features               | Boot Security, Cryptography, Secure Fusebox, Secure JTAG, Secure Memory, Tamper Detection |

| Package / Case                  | 1295-BBGA, FCBGA                                                                          |

| Supplier Device Package         | 1295-FCPBGA (37.5x37.5)                                                                   |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=p5020nse1tnb                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

2

**P5020 Application Use Cases**

# 1 P5020 Application Use Cases

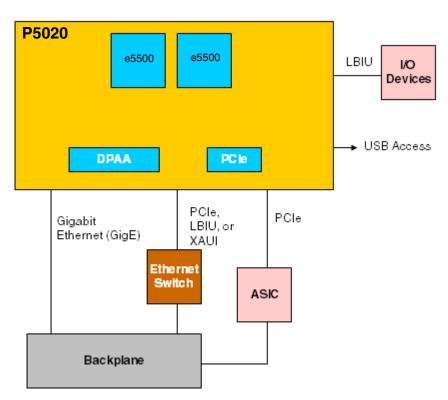

## 1.1 Router Control Processor

The following figure shows the P5020 in a linecard control plane application, where the linecard is part of a high-end network router.

Figure 1. Control Plane Processor for a Router

P5020 QorlQ Communications Processor Product Brief, Rev. 1

#### P5020 Dual-Core Processing Options

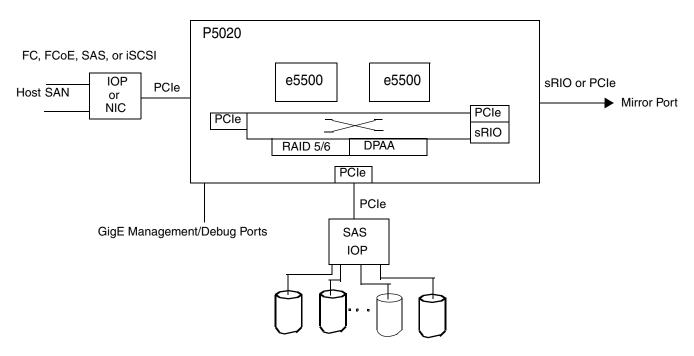

Figure 3. SAN RAID Controller

# 2 P5020 Dual-Core Processing Options

The device cores can run either on an OS or run OS-less using a simple scheduler.

## 2.1 Running on an OS

There are different multi-processing options with the device cores running on an OS:

- Symmetric multi-processing

- Cooperative asymmetric multi-processing

- Two copies of the same OS that are non-SMP enabled

- Two separate operating systems

## 2.2 Running OS-Less Using a Simple Scheduler

It is also possible for one or more cores to run OS-less, using a simple scheduler. This is a likely scenario when cores are performing datapath operations with bounded real-time requirements. This use case is greatly enhanced by the provisioning of a 512-Kbyte private back-side L2 cache for each e5500 core. These caches can operate as a traditional unified cache, or be set to operate as instruction only, data only, or even locked and used as memory-mapped SRAM.

CPU cores operating asymmetrically can be run at asynchronous clock rates. Each processor can source its input clock from one of the multiple PLLs inside the P5020. This allows each core to operate at the minimum frequency required to perform its assigned function, saving power. The cores are also capable of running at half and quarter ratios of their input PLL frequency and can switch between PLLs and ratios

nearly instantaneously. This allows lightly utilized CPUs to be slowed (under software control) for power savings, rather than performing more complex task migration operations.

## 3 Features

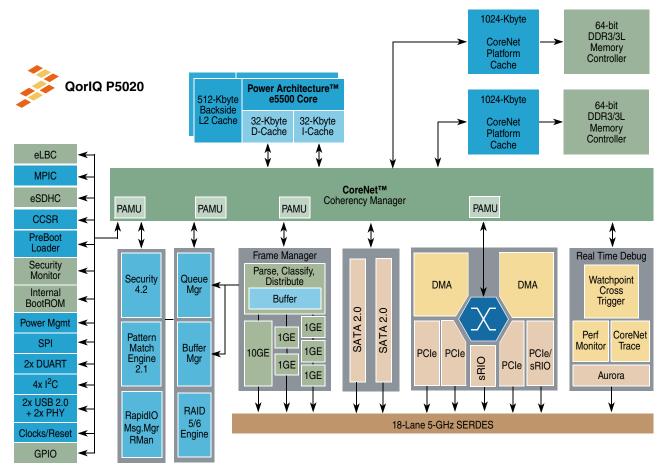

## 3.1 Block Diagram

The following figure shows the major functional units within the P5020.

Figure 4. P5020 Preliminary Block Diagram

## 3.2 P5020 Features Summary

The P5020 SoC includes the following functions and features:

- Two e5500 cores built on Power Architecture technology, each with a private 512-Kbyte private backside cache

- Up to 2 GHz

- Three levels of instructions:

- User

P5020 QorlQ Communications Processor Product Brief, Rev. 1

- Supervisor

- Hypervisor

- Independent boot and reset

- Secure boot capability

- Two 1-Mbyte shared CoreNet platform cache (CPC)

- Hierarchical interconnect fabric

- CoreNet fabric supporting coherent and non-coherent transactions with prioritization and bandwidth allocation amongst CoreNet end-points

- Queue manager fabric supporting packet-level queue management and quality of service scheduling

- Two 64-bit DDR3/3L SDRAM memory controllers with ECC and interleaving support

- Datapath acceleration architecture (DPAA) incorporating acceleration for the following functions:

- Packet parsing, classification, and distribution

- Queue management for scheduling, packet sequencing, and congestion management

- Hardware buffer management for buffer allocation and de-allocation

- Encryption/decryption (SEC 4.2)

- RegEx pattern matching (PME 2.1)

- RapidIO<sup>TM</sup>nessaging manager (RMan)

- RAID5/6 Engine

- Support for XOR and Galois Field parity calculation

- Support for data protection information (DPI)

- Ethernet interfaces

- One 10 Gbps Ethernet (XAUI) controller

- Five 1 Gbps or four 2.5 Gbps Ethernet controllers

- High speed peripheral interfaces

- Four PCI Express 2.0 controllers/ports running at up to 5 GHz

- Two serial RapidIO 2.0 controllers/ports (version 1.3 with features of 2.1) running at up to 5

GHz with Type 11 messaging and Type 9 data streaming support

- Additional peripheral interfaces

- Dual SATA supporting 1.5 and 3.0 Gb/s operation

- Two USB 2.0 controllers with integrated PHY

- SD/MMC controller (eSDHC)

- Enhanced SPI controller

- Four I<sup>2</sup>C controllers

- Two Dual DUARTs

- Enhanced local bus controller (eLBC)

- 18 SerDes lanes to 5 GHz

- Multicore Programmable Interrupt Controller (MPIC)

## 3.6 e5500 Core and Cache Memory Complex

Each e5500 is a superscalar dual issue processor, supporting out-of-order execution and in-order completion, which allows the Power Architecture e5500 to perform more instructions per clock than other RISC and CISC architectures.

#### 3.6.1 e5500 Core Features

- Up to 2.0 GHz core clock speed

- 36 bit physical addressing

- 64 TLB SuperPages

- 512-entry, 4-Kbyte pages front end

- 3 Integer Units: 2 simple, 1 complex (integer multiply and divide)

- 64-byte cache line size

- L1 caches, running at same frequency of CPU

- 32-Kbyte Instruction, 8-way

- 32-Kbyte Data, 8-way

- Both with data and tag parity protection

- Supports data path acceleration architecture (DPAA) data and context "stashing" into the L1 data cache and the backside L2 cache

- User, supervisor, and hypervisor instruction level privileges

- New processor facilities

- Hypervisor APU

- Classic double precision floating point unit

- Uses 32 64-bit floating-point registers (FPRs) for scalar single- and double-precision floating-point arithmetic

- Replaces the embedded floating-point facility (SPE) implemented on the e500v1 and e500v2

- Designed to comply with IEEE Std. 754<sup>TM</sup> 985 FPU for both single- and double-precision operations

- "Decorated Storage" APU for improved statistics support

- Provides additional atomic operations, including a "fire-and-forget" atomic update of up to two 64-bit quantities by a single access

- Expanded interrupt model

- Improved programmable interrupt controller (PIC) automatically ACKs interrupts

- Implements message send and receive functions for interprocessor communication, including receive filtering

- External PID load and store facility

- Provides system software with an efficient means to move data and perform cache operations between two disjoint address spaces

Eliminates the need to copy data from a source context into a kernel context, change to

destination address space, then copy the data to the destination address space or alternatively

to map the user space into the kernel address space

## 3.6.2 512-Kbyte Private Backside Cache

- Each e5500 core features a 512-Kbyte private backside L2 cache running at the same frequency of CPU. The caches support: Write Back, pseudo LRU replacement algorithm

- Tag parity and ECC data protection

- Eight-way, with arbitrary partitioning between instruction and data. For example, 3-ways instruction, 5-ways data, and so on.

- Supports direct stashing of datapath architecture data into cache

## 3.6.3 CoreNet Platform Cache (CPC)

The QorIQ P5020 also contains 2x1-Mbyte of shared CoreNet platform cache, with the following features:

- Configurable as write back or write through

- Pseudo LRU replacement algorithm

- ECC protection

- 64-byte coherency granule

- Two cache line read 1024 bits per cycle at 800 MHz, 32-way cache array configurable to any of several modes on a per-way basis

- Unified cache, I-only, D-only

- I/O stash (configurable portion of each packet copied to CPC on write to main memory)

- Stashing of all transactions and sizes supported

- Explicit (CoreNet signalled) and implicit (address range based) stash allocation

- Addressable SRAM (32-Kbyte granularity)

## 3.6.4 CoreNet Fabric and Address Map

The CoreNet fabric is Freescale's next generation Interconnect Standard for multicore products, and provides the following:

- A highly concurrent, fully cache coherent, multi-ported fabric

- Point-to-point connectivity with flexible protocol architecture allows for pipelined interconnection between CPUs, platform caches, memory controllers, and I/O and accelerators at up to 800 MHz

- The CoreNet fabric has been designed to overcome bottlenecks associated with shared bus architectures, particularly address issue and data bandwidth limitations. The P5020's multiple, parallel address paths allow for high address bandwidth, which is a key performance indicator for large coherent multicore processors

- Eliminates address retries, triggered by CPUs being unable to snoop within the narrow snooping window of a shared bus. This results in the device having lower average memory latency

The 36-bit, physical address map consists of local space and external address space. For the local address map, 32 local access windows (LAWs) define mapping within the local 36-bit (64-Gbyte) address space. Inbound and outbound translation windows can map the device into a larger system address space such as the RapidIO or PCIe 64-bit address environment. This functionality is included in the address translation and mapping units (ATMUs).

## 3.6.5 Memory Complex

The P5020 memory complex consists of the two DDR controllers for main memory, and the memory controllers associated with the enhanced local bus controller (eLBC).

### 3.6.5.1 DDR Memory Controllers

The two DDR memory controllers have the following functionalities:

- Supports DDR3/3L SDRAM. The P5020 also supports chip-select interleaving within a controller. The memory interface controls main memory accesses and together the two controllers support a maximum of 64 Gbytes of main memory.

- Supports interleaving across controllers on bank, page, or cache line boundaries.

- The P5020 can be configured to retain the currently active SDRAM page for pipelined burst accesses. Page mode support of up to 64 simultaneously open pages can dramatically reduce access latencies for page hits. Depending on the memory system design and timing parameters, page mode can save up to 10 memory clock cycles for subsequent burst accesses that hit in an active page.

- Using ECC, the P5020 detects and corrects all single-bit errors and detects all double-bit errors and all errors within a nibble.

- Upon detection of a loss of power signal from external logic, the DDR controllers can put compliant DDR SDRAM DIMMs into self-refresh mode, allowing systems to implement battery-backed main memory protection.

- Supports initialization bypass feature for use by system designers to prevent re-initialization of main memory during system power-on after an abnormal shutdown.

- Supports active zeroization of system memory upon detection of a user-defined security violation.

## 3.6.6 PreBoot Loader (PBL) and Nonvolatile Memory Interfaces

The PreBoot Loader (PBL) is a new logic module that operates similarly to an I<sup>2</sup>C boot sequencer but on behalf of a larger number of interfaces.

The PBL's functions include the following:

- Simplifies boot operations, replacing pin strapping resistors with configuration data loaded from nonvolatile memory.

- Uses the configuration data to initialize other system logic and to copy data from low speed memory interfaces (I<sup>2</sup>C, eLBC, SPI, and SD/MMC) into fully initialized DDR or the 2-Mbyte CPC.

- Releases CPU 0 from reset, allowing the boot processes to begin from fast system memory.

The nonvolatile memory interfaces accessible by the PBL are as follows:

- The eLBC may be accessed by software running on the CPUs following boot; it is not dedicated to the PBL. It also can be used for both volatile (SRAM) and nonvolatile memory as well as a control and low-performance data port for external memory-mapped P5020s. See Section 3.6.7, "Enhanced Local Bus Controller."

- The serial memory controllers may be accessed by software running on the CPUs following boot; they are not dedicated to the PBL. See Section 3.6.7.1, "Serial Memory Controllers."

#### 3.6.7 Enhanced Local Bus Controller

The enhanced local bus controller (eLBC) port connects to a variety of external memories, DSPs, and ASICs.

Key features of the eLBC include the following:

- Multiplexed 32-bit address and 32-bit data bus operating at up to 93 MHz

- Eight chip selects for eight external slaves

- Up to eight-beat burst transfers

- 8-, 16-, or 32-bit port sizes controlled by an internal memory controller

- Three protocol engines on a per-chip-select basis

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Support for parallel NAND and NOR flash

Three separate state machines share the same external pins and can be programmed separately to access different types of devices. Some examples are as follows:

- The general-purpose chip-select machine (GPCM) controls accesses to asynchronous devices using a simple handshake protocol.

- The user-programmable machine (UPM) can be programmed to interface to synchronous devices or custom ASIC interfaces.

- The NAND flash control machine (FCM) further extends interface options.

- Each chip select can be configured so that the associated chip interface is controlled by the GPCM, UPM, or FCM controller.

All controllers can be enabled simultaneously. The eLBC internally arbitrates among the controllers, allowing each to read or write a limited amount of data before allowing another controller to use the bus.

## 3.6.7.1 Serial Memory Controllers

In addition to the parallel NAND and NOR flash supported by means of the eLBC, the P5020 supports serial flash using SPI and SD/MMC/eMMC card. The SD/MMC/eMMC controller includes a DMA engine, allowing it to move data from serial flash to external or internal memory following straightforward initiation by software.

- x8, x4, x2, and x1 link widths supported

- Both 32- and 64-bit addressing and 256-byte maximum payload size

- Full 64-bit decode with 36-bit wide windows

- Inbound INTx transactions

- Message Signaled Interrupt (MSI) transactions

### 3.8.2 Serial RapidIO

The Serial RapidIO interface is based on the *RapidIO Interconnect Specification, Revision 1.3*, with features from 2.1. RapidIO is a high-performance, point-to-point, low-pin-count, packet-switched system-level interconnect that can be used in a variety of applications as an open standard. The rich feature set includes high data bandwidth, low-latency capability, and support for high-performance I/O devices as well as message-passing and software-managed programming models. Receive and transmit ports operate independently, and with 2 x 4 Serial RapidIO controllers, the aggregate theoretical bandwidth is 32 Gbps.

Key features of the Serial RapidIO interface unit include the following:

- Support for *RapidIO Interconnect Specification*, *Revision 1.3* (all transaction flows and priorities)

- 1x, 2x, and 4x LP-serial link interfaces, with transmission rates of 2.5, 3.125, or 5.0 Gbaud (data rates of 2.0, 2.5, or 4.0 Gbps) per lane.

- Auto-detection of 1x, 2x, or 4x mode operation during port initialization

- 34-bit addressing and up to 256-byte data payload

- Support for SWRITE, NWRITE\_R and Atomic transactions

- Receiver-controlled flow control

- RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

## 3.8.2.1 RapidIO Message Manager (RMan)

The key features of the RapidIO message manager (RMan) include the following:

- Manages two inbox/outbox mailboxes (queues) for data and one doorbell message structure

- Can multi-cast a single-segment 256-byte message to up to 32 different destination DevIDs

- Has four outbound segmentation units supporting RapidIO Type 5–6 and Type 8–11

## 3.8.3 Serial ATA (SATA) 2.0 Controllers

The key features of each of the two SATA include the following:

- Designed to comply with Serial ATA 2.6 Specification

- Supports host SATA I per spec Rev 1.0a

- OOB

- Port multipliers

- ATAPI 6+

P5020 QorlQ Communications Processor Product Brief, Rev. 1

### 3.9.3 DPAA Terms and Definitions

The following table lists common DPAA terms and their definitions.

**Table 4. DPAA Terms and Definitions**

| Term                | Definition                                                                                                                                      | Graphic Representation                                                                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Buffer              | Region of contiguous memory, allocated by software, managed by the DPAA BMan                                                                    | В                                                                                                                                                                  |

| Buffer pool         | Set of buffers with common characteristics (mainly size, alignment, access control)                                                             | ВВВВ                                                                                                                                                               |

| Frame               | Single buffer or list of buffers that hold data, for example, packet payload, header, and other control information                             | F = B B                                                                                                                                                            |

| Frame queue<br>(FQ) | FIFO of frames                                                                                                                                  | FQ = F                                                                                                                                                             |

| Work queue<br>(WQ)  | FIFO of FQs                                                                                                                                     | WQ = FQ FQ                                                                                                                                                         |

| Channel             | Set of eight WQs with hardware provided prioritized access                                                                                      | $ \begin{array}{c c} \hline \text{Chan} & \hline \end{array} = \begin{array}{c c} \hline 0 & FQ & FQ \\ \hline \hline 7 & FQ & FQ \\ \hline \end{array} $ Priority |

| Dedicated channel   | Channel statically assigned to a particular end point, from which that end point can dequeue frames. End point may be a CPU, FMan, PME, or SEC. | _                                                                                                                                                                  |

| Pool<br>channel     | A channel statically assigned to a group of end points, from which any of the end points may dequeue frames.                                    |                                                                                                                                                                    |

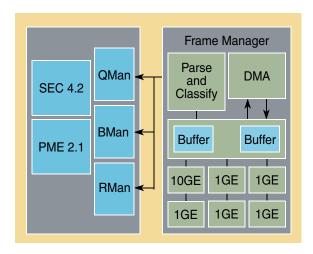

# 3.9.4 Major DPAA Components

The Data Path Acceleration Architecture (DPAA) includes the following major components:

- Section 3.9.4.1, "Frame Manager (FMan)

- Section 3.9.4.2, "Queue Manager (QMan)

- Section 3.9.4.3, "Buffer Manager (BMan)

- Section 3.9.4.6, "RapidIO Message Manager (RMan)

P5020 QorlQ Communications Processor Product Brief, Rev. 1

- Section 3.9.4.4, "Security Engine (SEC 4.2)

- Section 3.9.4.5, "Pattern Matching Engine (PME 2.1)

Figure 5. QorlQ Data Path Acceleration Architecture (DPAA)

### 3.9.4.1 Frame Manager (FMan)

The Frame Manager (FMan) combines the Ethernet network interfaces with packet distribution logic to provide intelligent distribution and queuing decisions for incoming traffic. This integration allows the FMan to perform configurable parsing and classification of the incoming frame with the purpose of selecting the appropriate input frame queue for expedited processing by a CPU or pool of CPUs.

#### 3.9.4.1.1 FMan Network Interfaces

The FMan integrates five data path, tri-speed Ethernet controllers (dTSECs) and one 10-Gbit Ethernet controller.

Note that the more basic parsing and filing capability found in prior PowerQUICC eTSECs is removed from the MACs themselves, and aggregated in the more flexible and robust parsing and classification logic described in Section 3.9.4.1.2, "FMan Parse Function."

The Ethernet controllers support the following:

- Programmable CRC generation and checking

- RMON statistics

- Jumbo frames of up to 9.6 Kbytes

They are designed to comply with IEEE Std 802.3®, IEEE 802.3u, IEEE 802.3x, IEEE 802.3z, IEEE 802.3ac, IEEE 802.3ab, and additionally the 1Gbps MACs support IEEE-1588 v2 (clock synchronization over Ethernet).

The dTSECS are capable of full- and half-duplex Ethernet support (1000 Mbps supports only full duplex); the 10-Gbit MAC is a single-speed full duplex. It supports IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition).

- Because the FMan has up to 256 policing profiles, any frame queue or group of frame queues can be policed to either drop or mark packets if the flow exceeds a preconfigured rate.

- Policing and classification can be used in conjunction for mitigating Distributed Denial of Service Attack (DDOS).

- The policing is based on two-rate-three-color marking algorithm (RFC2698). The sustained and peak rates as well as the burst sizes are user-configurable. Hence, the policing function can rate-limit traffic to conform to the rate the flow is mapped to at flow set-up time. By prioritizing and policing traffic prior to software processing, CPU cycles can be focused on the important and urgent traffic ahead of other traffic.

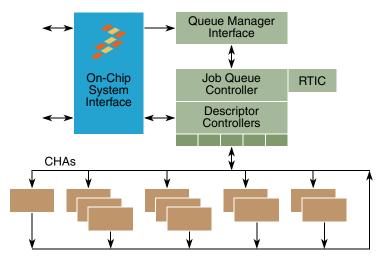

## 3.9.4.2 Queue Manager (QMan)

The Queue Manager (QMan) is the main component in the DPAA that allows for simplified sharing of network interfaces and hardware accelerators by multiple CPU cores. It also provides a simple and consistent message and data passing mechanism for dividing processing tasks amongst multiple CPU cores. The QMan features are as follows:

- Common interface between software and all hardware

- Controls the prioritized queuing of data between multiple processor cores, network interfaces, and hardware accelerators

- Supports both dedicated and pool channels, allowing both push and pull models of multicore load spreading

- Atomic access to common queues without software locking overhead

- Mechanisms to guarantee order preservation with atomicity and order restoration following parallel processing on multiple CPUs

- Two-level queuing hierarchy with one or more Channels per Endpoint, eight work queues per Channel, and numerous frame queues per work queue

- Priority and work conserving fair scheduling between the work queues and the frame queues

- Lossless flow control for ingress network interfaces

- Congestion avoidance (RED/WRED) and congestion management with tail discard and up to 256 congestion groups with each group composed of a user-configured number of frame queues.

## 3.9.4.3 Buffer Manager (BMan)

The buffer manager (BMan) manages pools of buffers on behalf of software for both hardware (accelerators and network interfaces) and software use. The BMan features are as follows:

- Common interface for software and hardware

- Guarantees atomic access to shared buffer pools

- Supports 32 buffer pools. Software and hardware buffer consumers can request both different size buffers and buffers in different memory partitions.

- Supports depletion thresholds with congestion notifications

- On-chip per pool buffer stockpile to minimize access to memory for buffer pool management

- LIFO (last in first out) buffer allocation policy that optimizes cache usage and allocation

P5020 QorlQ Communications Processor Product Brief, Rev. 1

Figure 6. SEC 4.2 Block Diagram

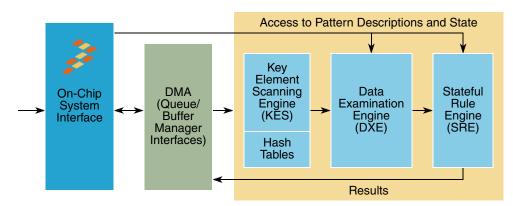

### 3.9.4.5 Pattern Matching Engine (PME 2.1)

The PME is a self-contained hardware module capable of autonomously scanning data from streams for patterns that match a specification in a database dedicated to it. The PME 2.1 is an updated version of the PME used in previous members of the PowerQUICC family. Specific updates include the following:

- QMan interface supporting the DPAA Queue Interface Driver

- 2x increase in the number of patterns supported (16 Kbytes to 32 Kbytes)

- Increase in number of stateful rules supported (8 Kbytes to 16 Kbytes)

- Raw scanning performance is ~ 5 Gbps.

Patterns that can be recognized, or "matched," by the PME are of two general forms:

- Byte patterns are simple matches such as "abcd123" existing in both the data being scanned and in the pattern specification database.

- Event patterns are a sequence of multiple byte patterns. In the PME, event patterns are defined by stateful rules.

### 3.9.4.5.1 PME Regular Expressions (Regex)

The PME specifies patterns of bytes as regular expressions (regex). The P5020 (by means of an online or offline process) converts Regex patterns into the PME's pattern specification database. Generally, there is a one-to-one mapping between a regex and a PME byte pattern. The PME's use of regex pattern matching offers built-in case-insensitivity and wildcard support with no pattern explosion, while the PME's NFA-style architecture offers fast pattern database compilation and fast incremental updates. Up to 32,000 regex patterns are supported, each up to 128 bytes long. The 32,000 regex patterns can be combined by means of stateful rules to detect a far larger set of event patterns. Comparative compilations against DFA style regex engines have shown that 300,000 DFA pattern equivalents can be achieved with ~8000 PME regexes with stateful rules.

#### 3.9.4.5.2 PME Match Detection

Within the PME, match detection proceeds in stages. The key element scanner performs initial byte pattern matching, with handoff to the data examination engine for elimination of false positives through more complex comparisons. As the name implies, the stateful rule engine receives confirmed basic matches from the earlier stages, and monitors a stream for addition for subsequent matches that define an event pattern.

Figure 7. PME 2.1 Block Diagram

### 3.9.4.6 RapidIO Message Manager (RMan)

The RapidIO message manager (RMan) produces and consumes Type 8 Port-write, Type 9 Data Streaming, Type 10 Doorbells and Type 11 Messaging traffic and is capable of producing Type 5 NWRITE and Type 6 SWRITE transactions.

For inbound traffic, the RMan supports up to 17 open reassembly contexts as a arbitrary mix of Type 9, and Type 11 traffic.

As ingress packets arrives at the RMan, they are compared against up to 64 classification rules to determine the target queue. These rules support Type 8, 9, 10 and 11 transaction types. They may be wildcarded and are configured as masks over selected header fields. The following fields are maskable as part of each classification rule:

Transaction types:

- RapidIO port

- Source ID

- Destination ID

- Flow level

Type 9 messaging-specific fields:

- Class-of-service (CoS)

- StreamID

Type 11 messaging-specific fields:

Mailbox

4-Kbyte granularity); other CPU MMUs are not configured for access to the other CPU's private memory range. When two CPUs need to share resources, their MMUs are both configured so that they have access to the shared address range.

This level of hardware support for partitioning is common today, however, it is not sufficient for many core systems running diverse software. When the functions of multiple discrete CPUs are consolidated onto a single, multicore SoC, achieving strong partitioning should not require the developer to map functions onto cores that are the exclusive owners of specific platform resources. The alternative, a fully open system with no private resources, is also unacceptable. For this reason, the core MMU also includes embedded Hypervisor extensions.

Each core MMU supports three levels of instructions:

- User

- Supervisor (OS)

- Hypervisor: An embedded Hypervisor micro-kernel (provided by Freescale as source code) runs unobtrusively beneath the various OSes running on the CPUs, consuming CPU cycles only when an access attempt is made to an embedded Hypervisor-managed shared resource. The embedded Hypervisor determines whether the access should be allowed, and if so, proxies the access on behalf of the original requestor. If malicious or poorly tested software on any core attempts to overwrite important P5020 configuration registers (including CPU MMUs), the embedded Hypervisor blocks the write. Other examples of embedded Hypervisor managed resources are high- and low-speed peripheral interfaces (PCIe, UART) if those resources are not dedicated to a single CPU/partition.

## 3.10.3 Peripheral Access Management Unit (PAMU)

The P5020 includes a distributed function collectively referred to as the peripheral access management unit (PAMU), which provides address translation and access control for all bus masters in the system (PME, SEC, FMan, and so on). The PAMU access control can be one of the following:

- Absolute—The FMan, PME, SEC, and other bus masters can never access memory range XYZ.

- Conditional—Based on the Partition ID of the CPU that programmed the bus master

Being MMU-based, the embedded Hypervisor is only able to stop unauthorized software access attempts. Internal components with bus mastering capability also need to be prevented from reading and writing to specific memory regions. These devices do not spontaneously generate access attempts, but, if programmed to do so by buggy or malicious software, any of them could overwrite sensitive configuration registers and crash the system.

#### 3.10.4 Secure Boot and Sensitive Data Protection

The core MMUs and PAMU allow the device to enforce a consistent set of memory access permissions on a per-partition basis. When combined with embedded Hypervisor for safe sharing of resources, the P5020 becomes highly resilient when poorly tested or malicious code is run. For system developers building high reliability/high security platforms, rigorous testing of code of known origin is the norm.

### 3.10.4.1 Secure Boot Option

The system developer digitally signs the code to be executed by the CPU coming out of reset, and the device ensures that only an unaltered version of that code runs on the platform. The P5020 offers both boot time and run time code authenticity checking and configurable consequences when the authenticity check fails.

### 3.10.4.2 Sensitive Data Protection Option

The P5020 supports protected internal and external storage of developer-provisioned sensitive instructions and data.

For example, a system developer may provision each system with a number of RSA private keys to be used in mutual authentication and key exchange. These values would initially be stored in external non-volatile memory, but following secure boot, these values can be decrypted into on-chip protected memory (portion of platform cache dedicated as SRAM). Session keys, which may number in the thousands to tens of thousands, are not good candidates for on-chip storage, so the device offers session key encryption. Session keys are stored in main memory, and are decrypted (transparently to software and without impacting SEC throughput) as they are brought into the SEC 4.2 for decryption of session traffic.

## 3.11 Advanced Power Management

The P5020's advanced power management capabilities are based around fine-grained static clock control and software-controlled dynamic frequency management.

## 3.11.1 Saving Power by Managing Internal Clocks

Dynamic voltage and frequency scaling (DVFS) are useful techniques for reducing typical/average power and maximizing battery life in laptop environments, but embedded applications must be designed for rapid response to bursts of traffic and max power under worst-case environmental conditions. While the P5020 does not implement DVFS in the PC sense, it does actively manage internal clocks to avoid wasting energy. Clock signals are disabled to idle components, reducing dynamic power. These blocks can return to full operating frequency on the clock cycle after work is dispatched to them.

The P5020 also supports (under software control) dynamic changes to CPU operating frequencies and voltages. Each CPU sources its input clock from one of two independent PLLs inside the device. Each CPU can also source its input clock from an integer frequency divider from two of the three independent PLLs. CPUs can switch their source PLL, and their frequency divider glitchlessly and nearly instantaneously. This allows each core to operate at the minimum frequency required to perform its assigned function, saving power.

## 3.11.2 Turning Off Unneeded Clocks

Fine-grained static control allows developers to turn off the clocks to individual logic blocks within the SoC that the system has no need for. Based on a finite number of SerDes, it is expected that any given application will have some Ethernet MACs, PCIe, or Serial RapidIO controllers inactive. These blocks can

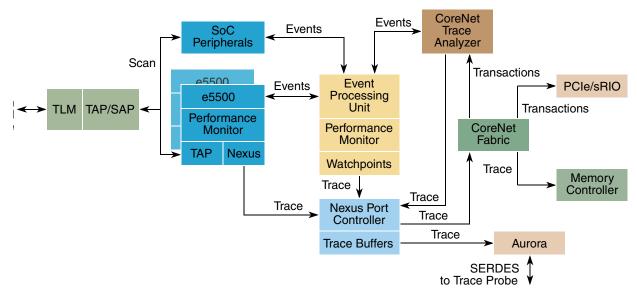

Figure 8. Debug Architecture

Debug features include the following:

- Debug and performance monitoring registers in both the core and platform

- Accessible by target resident debug software and non-resident debug tools

- Capable of generating debug interrupts and trace event messages

- Run control with enhancements

- Classic

- Cross-core and SoC watchpoint triggering

- High speed trace port (Aurora-based)

- Supports Nexus class 2 instruction trace including timestamps

- Process id trace, watchpoint trace

- Supports "light" subset of Nexus class 3 data trace

- Enabled by cores, by event triggers, by Instruction Address Compare/Data Address

Compare events

- Data Acquisition Trace

- Compatible with Nexus class 3

- Instrumented code can generate data trace messages for values of interest

- Performed by writing values to control registers within each core

- Watchpoint Trace

- Can generate cross-core correlated breakpoints

- Breakpoint on any core can halt execution of selected additional cores with minimal skid

- CoreNet transaction analyzer

- Provides visibility to transactions across CoreNet (CoreNet fabric is otherwise transparent to software)

P5020 QorlQ Communications Processor Product Brief, Rev. 1

- Generates trace messages to Nexus Port Controller

- Supports filtering of accesses of interest

- Data Address Compare (4)

- Data Value Compare (2)

- Transaction Attribute Compare (2)

# 4 Developer Environment

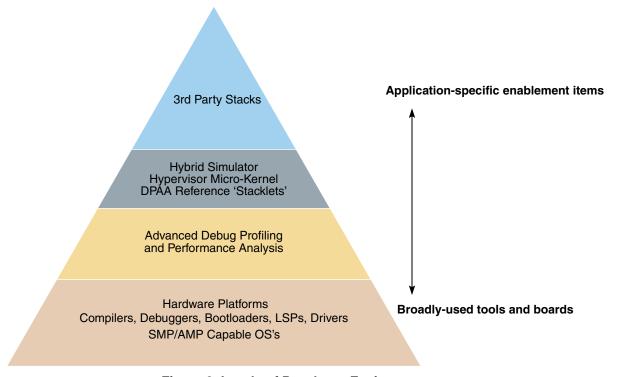

Software developers creating solutions with the Power Architecture technology have long benefited from a vibrant support ecosystem, including high quality tools, OSes, and network protocol stacks. Freescale is working with our ecosystem partners to ensure that this remains the case for multicore, Power Architecture-based products, including the P5020.

The various levels of the developer environment are shown in Figure 9, with the more broadly used tools and boards at the base of the pyramid, and increasingly application-specific enablement items at the top. Each level is described further, as follows:

- Section 4.1, "Base of the Pyramid: Broadly-Used Tools and Boards

- Section 4.2, "First Level of the Pyramid: Debug and Performance Analysis

- Section 4.3, "Second Level of the Pyramid: Simulation, Hypervisor, and DPAA Reference "Stacklets"

- Section 4.4, "Top Level of the Pyramid: Application-Specific Enablement

Figure 9. Levels of Developer Environment

P5020 QorIQ Communications Processor Product Brief, Rev. 1

- Global visibility

- Determinism

- Bug reproducibility

- Reverse execution

- Special abilities to detect race conditions

- Ability to detect race conditions

## 4.3.2 Hypervisor Micro-Kernel

The P5020's e5500 cores offer a new embedded Hypervisor capability to address the need for a single operating system performing coordination and access control functions, managing shared resources in an efficient manner. The embedded Hypervisor provides the software layer needed to manage the operating systems and supervisor-level applications as they access shared resources. Recognizing that each developer's system design may call for a different partitioning of resources, and involve different combinations of OSes and RTOSes, Freescale and our ecosystem partners will provide reference implementations of the embedded Hypervisor's peripheral virtualization and access control which the developer can modify to match unique system requirements.

### 4.3.3 DPAA Reference "Stacklets"

It is expected that some CPUs will be dedicated as datapath processors, working closely with the DPAA. Freescale will provide reference protocol "stacklets," optimizing performance critical regions of protocol processing and their interaction with the DPAA hardware.

## 4.4 Top Level of the Pyramid: Application-Specific Enablement

This category includes 3rd-party stacks optimized for DPAA, RegEx, AV TCP, IPv4/6, IPsec/SSL.

Many of the expected applications for the P5020 involve network protocol processing. Partitioning between control CPUs and datapath CPUs, and developing the protocol processing firmware which runs on the datapath CPUs is an area for significant value added services for Freescale partners at the top level of the enablement pyramid. OEMs wishing to engage with these partners can realize significant "time-to-performance" advantages.

# 5 Document Revision History

The following table provides a revision history for this product brief.

**Table 8. Revision History**

| Revision | Date    | Substantive Change(s)                                                      |

|----------|---------|----------------------------------------------------------------------------|

| 1        | 02/2013 | Modified USB Specification, Section 3.7, "Universal Serial Bus (USB) 2.0." |

| 0        | 12/2011 | Initial public release.                                                    |

Freescale Semiconductor 31

P5020 QorlQ Communications Processor Product Brief. Rev. 1

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: http://www.reg.net/v2/webservices/Freescale/Docs/TermsandConditions.htm.

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2011-2013 Freescale Semiconductor, Inc.

Document Number: P5020PB

Rev. 1 02/2013