#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 768 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f242-e-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | Pin N   | umber    | Pin  | Buffer    | Description                                                                                                    |

|-------------------|---------|----------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| Pin Name          | DIP     | SOIC     | Туре | Туре      | Description                                                                                                    |

|                   |         |          |      |           | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0          | 21      | 21       |      |           |                                                                                                                |

| RB0               |         |          | I/O  | TTL       | Digital I/O.                                                                                                   |

| INT0              |         |          | I    | ST        | External Interrupt 0.                                                                                          |

| RB1/INT1          | 22      | 22       |      |           |                                                                                                                |

| RB1               |         |          | I/O  | TTL       | <b>_</b>                                                                                                       |

| INT1              |         |          | I    | ST        | External Interrupt 1.                                                                                          |

| RB2/INT2          | 23      | 23       |      |           |                                                                                                                |

| RB2<br>INT2       |         |          | I/O  | TTL<br>ST | Digital I/O.                                                                                                   |

|                   |         |          | 1    | 51        | External Interrupt 2.                                                                                          |

| RB3/CCP2<br>RB3   | 24      | 24       | I/O  | TTL       | Digital I/O.                                                                                                   |

| CCP2              |         |          | 1/O  | ST        | Capture2 input, Compare2 output, PWM2 output.                                                                  |

| RB4               | 25      | 25       | 1/O  | TTL       | Digital I/O.                                                                                                   |

| ND4               | 25      | 25       | 1/0  | 116       | Interrupt-on-change pin.                                                                                       |

| RB5/PGM           | 26      | 26       |      |           |                                                                                                                |

| RB5               | 20      | 20       | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGM               |         |          | I/O  | ST        | Low Voltage ICSP programming enable pin.                                                                       |

| RB6/PGC           | 27      | 27       |      |           |                                                                                                                |

| RB6               |         |          | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGC               |         |          | I/O  | ST        | In-Circuit Debugger and ICSP programming clock pin.                                                            |

| RB7/PGD           | 28      | 28       |      |           |                                                                                                                |

| RB7               |         |          | I/O  | TTL       | Digital I/O. Interrupt-on-change pin.                                                                          |

| PGD               |         |          | I/O  | ST        | In-Circuit Debugger and ICSP programming data pin.                                                             |

| Legend: TTL = TTL | compati | ble inpu | t    |           | CMOS = CMOS compatible input or output                                                                         |

| TABLE 1-2:PIC18F2X2 PINOUT | O DESCRIPTIONS (CONTINUED) |

|----------------------------|----------------------------|

|----------------------------|----------------------------|

ST = Schmitt Trigger input with CMOS levels O = Output

OD = Open Drain (no P diode to VDD)

I = Input P = Power

|          |     |         |                       |     |                                    | MCLR Resets                                    |                                 |  |

|----------|-----|---------|-----------------------|-----|------------------------------------|------------------------------------------------|---------------------------------|--|

| Register | Арр | olicabl | e Devi                | ces | Power-on Reset,<br>Brown-out Reset | WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |

| TOSU     | 242 | 442     | 2 252 4520 00000 0000 |     | 0 uuuu <b>(3)</b>                  |                                                |                                 |  |

| TOSH     | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu <sup>(3)</sup>        |  |

| TOSL     | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu <b>(3)</b>            |  |

| STKPTR   | 242 | 442     | 252                   | 452 | 00-0 0000                          | uu-0 0000                                      | uu-u uuuu <b>(3)</b>            |  |

| PCLATU   | 242 | 442     | 252                   | 452 | 0 0000                             | 0 0000                                         | u uuuu                          |  |

| PCLATH   | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| PCL      | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | PC + 2 <sup>(2)</sup>           |  |

| TBLPTRU  | 242 | 442     | 252                   | 452 | 00 0000                            | 00 0000                                        | uu uuuu                         |  |

| TBLPTRH  | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| TBLPTRL  | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| TABLAT   | 242 | 442     | 252                   | 452 | 0000 0000                          | 0000 0000                                      | uuuu uuuu                       |  |

| PRODH    | 242 | 442     | 252                   | 452 | xxxx xxxx                          | սսսս սսսս                                      | uuuu uuuu                       |  |

| PRODL    | 242 | 442     | 252                   | 452 | xxxx xxxx                          | uuuu uuuu                                      | սսսս սսսս                       |  |

| INTCON   | 242 | 442     | 252                   | 452 | 0000 000x                          | 0000 000u                                      | uuuu uuuu <b>(1)</b>            |  |

| INTCON2  | 242 | 442     | 252                   | 452 | 1111 -1-1                          | 1111 -1-1                                      | uuuu -u-u <b>(1)</b>            |  |

| INTCON3  | 242 | 442     | 252                   | 452 | 11-0 0-00                          | 11-0 0-00                                      | uu-u u-uu <b>(1)</b>            |  |

| INDF0    | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| POSTINC0 | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| POSTDEC0 | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| PREINC0  | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| PLUSW0   | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| FSR0H    | 242 | 442     | 252                   | 452 | xxxx                               | uuuu                                           | uuuu                            |  |

| FSR0L    | 242 | 442     | 252                   | 452 | xxxx xxxx                          | uuuu uuuu                                      | սսսս սսսս                       |  |

| WREG     | 242 | 442     | 252                   | 452 | xxxx xxxx                          | uuuu uuuu                                      | սսսս սսսս                       |  |

| INDF1    | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| POSTINC1 | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| POSTDEC1 | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| PREINC1  | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

| PLUSW1   | 242 | 442     | 252                   | 452 | N/A                                | N/A                                            | N/A                             |  |

#### TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for RESET value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

| Register |     |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instructio<br>Stack Resets | Wake-up via WDT<br>n or Interrupt |           |                  |

|----------|-----|-----|------------------------------------|--------------------------------------------------------------|-----------------------------------|-----------|------------------|

| ADRESH   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | นนนน นนนน        |

| ADRESL   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | սսսս սսսս        |

| ADCON0   | 242 | 442 | 252                                | 452                                                          | 0000 00-0                         | 0000 00-0 | uuuu uu-u        |

| ADCON1   | 242 | 442 | 252                                | 452                                                          | 00 0000                           | 00 0000   | uu uuuu          |

| CCPR1H   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| CCPR1L   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| CCP1CON  | 242 | 442 | 252                                | 452                                                          | 00 0000                           | 00 0000   | uu uuuu          |

| CCPR2H   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| CCPR2L   | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| CCP2CON  | 242 | 442 | 252                                | 452                                                          | 00 0000                           | 00 0000   | uu uuuu          |

| TMR3H    | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| TMR3L    | 242 | 442 | 252                                | 452                                                          | xxxx xxxx                         | uuuu uuuu | uuuu uuuu        |

| T3CON    | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | uuuu uuuu | uuuu uuuu        |

| SPBRG    | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | 0000 0000 | uuuu uuuu        |

| RCREG    | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | 0000 0000 | սսսս սսսս        |

| TXREG    | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | 0000 0000 | uuuu uuuu        |

| TXSTA    | 242 | 442 | 252                                | 452                                                          | 0000 -010                         | 0000 -010 | uuuu -uuu        |

| RCSTA    | 242 | 442 | 252                                | 452                                                          | 0000 000x                         | 0000 000x | սսսս սսսս        |

| EEADR    | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | 0000 0000 | սսսս սսսս        |

| EEDATA   | 242 | 442 | 252                                | 452                                                          | 0000 0000                         | 0000 0000 | <u>uuuu</u> uuuu |

| EECON1   | 242 | 442 | 252                                | 452                                                          | xx-0 x000                         | uu-0 u000 | uu-0 u000        |

| EECON2   | 242 | 442 | 252                                | 452                                                          |                                   |           |                  |

| TABLE 3-3: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUE) | ונ |

|------------|--------------------------------------------------------|----|

| IADLL J-J. | INTIALIZATION CONDITIONS I ON ALL ALGISTERS (CONTINULI | "  |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 3-2 for RESET value for specific condition.

5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other Oscillator modes, they are disabled and read '0'.

6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they are read '0'.

Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of

its corresponding enable bit or the global

enable bit. User software should ensure

the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature

allows for software polling.

## 8.1 INTCON Registers

The INTCON Registers are readable and writable registers, which contain various enable, priority and flag bits.

### REGISTER 8-1: INTCON REGISTER

| ••••  |                     | ••••           |                                           |               |              |             |              |               |       |

|-------|---------------------|----------------|-------------------------------------------|---------------|--------------|-------------|--------------|---------------|-------|

|       | R/W-0               | C              | R/W-0                                     | R/W-0         | R/W-0        | R/W-0       | R/W-0        | R/W-0         | R/W-x |

|       | GIE/GI              | EH             | PEIE/GIEL                                 | TMR0IE        | INT0IE       | RBIE        | TMR0IF       | <b>INT0IF</b> | RBIF  |

|       | bit 7               |                |                                           |               |              |             |              |               | bit 0 |

| bit 7 | GIE/GIE             | E <b>H</b> : G | alobal Interrup                           | t Enable bit  |              |             |              |               |       |

|       | When IF             | PEN            | = 0:                                      |               |              |             |              |               |       |

|       |                     |                | all unmasked all interrupts               | interrupts    |              |             |              |               |       |

|       | When IF             |                |                                           |               |              |             |              |               |       |

|       |                     |                | all high priorit<br>all interrupts        | y interrupts  |              |             |              |               |       |

| bit 6 | PEIE/GI             | EL:            | Peripheral Inte                           | errupt Enable | e bit        |             |              |               |       |

|       | When IF             |                |                                           |               |              |             |              |               |       |

|       |                     |                | all unmasked<br>all peripheral            |               | terrupts     |             |              |               |       |

|       | 0 = Disa<br>When IF |                |                                           | menupis       |              |             |              |               |       |

|       |                     |                | <u>– 1.</u><br>all low priority           | peripheral ir | nterrupts    |             |              |               |       |

|       |                     |                | all low priority                          |               |              |             |              |               |       |

| bit 5 |                     |                | IR0 Overflow                              | •             |              |             |              |               |       |

|       |                     |                | the TMR0 over<br>the TMR0 ov              |               |              |             |              |               |       |

| bit 4 |                     |                | 0 External Inte                           |               | •            |             |              |               |       |

| bit 4 |                     |                | the INT0 exte                             |               |              |             |              |               |       |

|       |                     |                | the INT0 exte                             |               |              |             |              |               |       |

| bit 3 | RBIE: F             | RB Po          | ort Change Int                            | errupt Enabl  | e bit        |             |              |               |       |

|       |                     |                | the RB port cl<br>the RB port c           | 0             |              |             |              |               |       |

| bit 2 |                     |                | IR0 Overflow I                            |               |              |             |              |               |       |

|       |                     |                | egister has ove<br>egister did not        |               | st be cleare | d in softwa | ıre)         |               |       |

| bit 1 |                     |                | D External Inte                           | 1 0           |              |             |              |               |       |

|       |                     |                | 0 external inte<br>0 external inte        | •             | •            | cleared in  | software)    |               |       |

| bit 0 |                     |                | ort Change Int                            |               |              |             |              |               |       |

|       |                     |                | one of the RB <sup>*</sup><br>the RB7:RB4 |               |              |             | cleared in s | software)     |       |

|       | Note:               |                | nismatch cond<br>match conditio           |               |              |             | ading PORT   | B will end    | the   |

|       |                     |                |                                           |               |              |             |              |               |       |

Note:

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## REGISTER 8-2: INTCON2 REGISTER

|       | R/W-1                          | R/W-1            | R/W-1          | R/W-1         | U-0           | R/W-1  | U-0 | R/W-1 |  |  |  |

|-------|--------------------------------|------------------|----------------|---------------|---------------|--------|-----|-------|--|--|--|

|       | RBPU                           | INTEDG0          | INTEDG1        | INTEDG2       | _             | TMR0IP | _   | RBIP  |  |  |  |

|       | bit 7                          |                  | l              |               |               |        |     | bit 0 |  |  |  |

|       |                                |                  |                |               |               |        |     |       |  |  |  |

| bit 7 | RBPU: PORTB Pull-up Enable bit |                  |                |               |               |        |     |       |  |  |  |

|       |                                | RTB pull-ups     |                |               |               |        |     |       |  |  |  |

|       | 0 <b>= PORT</b>                | B pull-ups are   | e enabled by   | individual po | rt latch valu | ies    |     |       |  |  |  |

| bit 6 | INTEDG0                        | :External Inte   | rrupt0 Edge    | Select bit    |               |        |     |       |  |  |  |

|       |                                | upt on rising e  | •              |               |               |        |     |       |  |  |  |

|       |                                | upt on falling e | •              |               |               |        |     |       |  |  |  |

| bit 5 | INTEDG1                        | : External Inte  | errupt1 Edge   | Select bit    |               |        |     |       |  |  |  |

|       |                                | upt on rising e  | 0              |               |               |        |     |       |  |  |  |

|       |                                | upt on falling e | 0              |               |               |        |     |       |  |  |  |

| bit 4 |                                | : External Inte  |                | Select bit    |               |        |     |       |  |  |  |

|       |                                | upt on rising e  | 0              |               |               |        |     |       |  |  |  |

|       |                                | upt on falling e | •              |               |               |        |     |       |  |  |  |

| bit 3 | •                              | nented: Read     |                |               |               |        |     |       |  |  |  |

| bit 2 |                                | TMR0 Overflo     | w Interrupt F  | Priority bit  |               |        |     |       |  |  |  |

|       | 1 = High p                     | ,                |                |               |               |        |     |       |  |  |  |

|       | 0 = Low p                      | •                |                |               |               |        |     |       |  |  |  |

| bit 1 | Unimpler                       | nented: Read     | 1 as '0'       |               |               |        |     |       |  |  |  |

| bit 0 | RBIP: RB                       | Port Change      | Interrupt Prie | ority bit     |               |        |     |       |  |  |  |

|       | 1 = High p                     | ,                |                |               |               |        |     |       |  |  |  |

|       | 0 = Low p                      | riority          |                |               |               |        |     |       |  |  |  |

|       |                                |                  |                |               |               |        |     |       |  |  |  |

|       | Legend:                        |                  |                |               |               |        |     |       |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

**Note:** Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

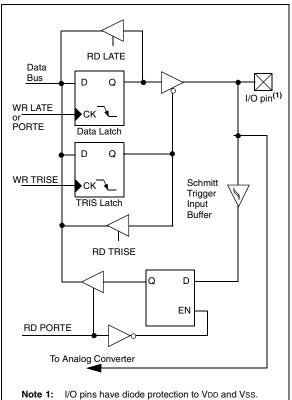

## 9.5 PORTE, TRISE and LATE Registers

This section is only applicable to the PIC18F4X2 devices.

PORTE is a 3-bit wide, bi-directional port. The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a Hi-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register reads and writes the latched output value for PORTE.

PORTE has three pins (RE0/RD/AN5, RE1/WR/AN6 and RE2/CS/AN7) which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

Register 9-1 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset, these pins are configured as analog inputs.

### EXAMPLE 9-5: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | ; data latches                             |

| CLRF  | LATE   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 0x07   | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVLW | 0x05   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISE  | ; Set RE<0> as inputs                      |

|       |        | ; RE<1> as outputs                         |

|       |        | ; RE<2> as inputs                          |

|       |        |                                            |

#### FIGURE 9-9:

#### PORTE BLOCK DIAGRAM IN I/O PORT MODE

NOTES:

| Name      | Bit 7                          | Bit 6                                                                        | Bit 5        | Bit 4         | Bit 3         | Bit 2       | Bit 1         | Bit 0       | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|-----------|--------------------------------|------------------------------------------------------------------------------|--------------|---------------|---------------|-------------|---------------|-------------|----------------------|---------------------------------|

| INTCON    | GIE/GIEH                       | PEIE/GIEL                                                                    | TMR0IE       | INT0IE        | RBIE          | TMR0IF      | INTOIF        | RBIF        | 0000 000x            | 0000 000u                       |

| PIR1      | PSPIF <sup>(1)</sup>           | ADIF                                                                         | RCIF         | TXIF          | SSPIF         | CCP1IF      | TMR2IF        | TMR1IF      | 0000 0000            | 0000 0000                       |

| PIE1      | PSPIE <sup>(1)</sup>           | ADIE                                                                         | RCIE         | TXIE          | SSPIE         | CCP1IE      | TMR2IE        | TMR1IE      | 0000 0000            | 0000 0000                       |

| IPR1      | PSPIP <sup>(1)</sup>           | ADIP                                                                         | RCIP         | TXIP          | SSPIP         | CCP1IP      | TMR2IP        | TMR1IP      | 0000 0000            | 0000 0000                       |

| TRISC     | PORTC D                        | ata Direction                                                                | Register     |               |               |             |               |             | 1111 1111            | 1111 1111                       |

| TMR1L     | Holding Re                     | egister for th                                                               | e Least Sigr | nificant Byte | of the 16-bit | TMR1 Reg    | gister        |             | xxxx xxxx            | uuuu uuuu                       |

| TMR1H     | Holding Re                     | egister for th                                                               | e Most Sign  | ificant Byte  | of the 16-bit | TMR1 Reg    | ister         |             | xxxx xxxx            | uuuu uuuu                       |

| T1CON     | RD16                           | _                                                                            | T1CKPS1      | T1CKPS0       | T1OSCEN       | T1SYNC      | TMR1CS        | TMR1ON      | 0-00 0000            | u-uu uuuu                       |

| CCPR1L    | Capture/C                      | ompare/PWI                                                                   | M Register1  | (LSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |

| CCPR1H    | Capture/C                      | ompare/PWI                                                                   | M Register1  | (MSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |

| CCP1CON   |                                | —                                                                            | DC1B1        | DC1B0         | CCP1M3        | CCP1M2      | CCP1M1        | CCP1M0      | 00 0000              | 00 0000                         |

| CCPR2L    | Capture/C                      | ompare/PWI                                                                   | M Register2  | (LSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |

| CCPR2H    | Capture/C                      | ompare/PWI                                                                   | M Register2  | (MSB)         |               |             |               |             | xxxx xxxx            | uuuu uuuu                       |

| CCP2CON   |                                | —                                                                            | DC2B1        | DC2B0         | CCP2M3        | CCP2M2      | CCP2M1        | CCP2M0      | 00 0000              | 00 0000                         |

| PIR2      |                                | —                                                                            | _            | EEIE          | BCLIF         | LVDIF       | TMR3IF        | CCP2IF      | 0 0000               | 0 0000                          |

| PIE2      |                                | —                                                                            | _            | EEIF          | BCLIE         | LVDIE       | TMR3IE        | CCP2IE      | 0 0000               | 0 0000                          |

| IPR2      | EEIP BCLIP LVDIP TMR3IP CCP2IP |                                                                              |              |               |               |             |               |             | 1 1111               | 1 1111                          |

| TMR3L     | Holding Re                     | egister for th                                                               | e Least Sigr | nificant Byte | of the 16-bit | TMR3 Reg    | gister        |             | xxxx xxxx            | uuuu uuuu                       |

| TMR3H     | Holding Re                     | lolding Register for the Most Significant Byte of the 16-bit TMR3 Register x |              |               |               |             |               |             |                      | uuuu uuuu                       |

| T3CON     | RD16                           | RD16 T3CCP2 T3CKPS1 T3CKPS0 T3CCP1 T3SYNC TMR3CS TMR3ON 0000 0000 uuuu uuuu  |              |               |               |             |               |             |                      |                                 |

| Legend: x | = unknow                       | n, u = uncha                                                                 | nged, - = ur | nimplemente   | d, read as 'C | '. Shaded o | cells are not | t used by C | apture and Tin       | ner1.                           |

## TABLE 14-3: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2x2 devices; always maintain these bits clear.

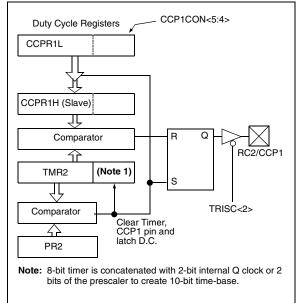

## 14.5 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCP1 pin produces up to a 10-bit resolution PWM output. Since the CCP1 pin is multiplexed with the PORTC data latch, the TRISC<2> bit must be cleared to make the CCP1 pin an output.

| Note: | Clearing the CCP1CON register will force the CCP1 PWM output latch to the default |

|-------|-----------------------------------------------------------------------------------|

|       | low level. This is not the PORTC I/O data latch.                                  |

Figure 14-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 14.5.3.

#### FIGURE 14-3: SIMPLIFIED PWM BLOCK DIAGRAM

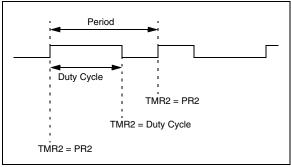

A PWM output (Figure 14-4) has a time-base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 14.5.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

$$PWM period = (PR2) + 1] \bullet 4 \bullet TOSC \bullet$$

(TMR2 prescale value)

PWM frequency is defined as 1 / [PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

| Note: | The Timer2 postscaler (see Section 12.0) |

|-------|------------------------------------------|

|       | is not used in the determination of the  |

|       | PWM frequency. The postscaler could be   |

|       | used to have a servo update rate at a    |

|       | different frequency than the PWM output. |

## 14.5.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR1H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read only register.

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2 concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

PWM Resolution (max) =

$$\frac{\log(\frac{\text{Fosc}}{\text{FPWM}})}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

## REGISTER 15-3: SSPSTAT: MSSP STATUS REGISTER (I<sup>2</sup>C MODE)

|       | R/W-0                                                                                                  | R/W-0                                       | R-0                                              | R-0              | R-0                     | R-0          | R-0             | R-0        |  |

|-------|--------------------------------------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------|------------------|-------------------------|--------------|-----------------|------------|--|

|       | SMP                                                                                                    | CKE                                         |                                                  | P                | s                       | R/W          | UA              | BF         |  |

|       | bit 7                                                                                                  | ONE                                         | Birt                                             | •                | Ŭ                       |              | 0,1             | bit 0      |  |

|       |                                                                                                        |                                             |                                                  |                  |                         |              |                 |            |  |

| oit 7 | In Master of                                                                                           | Rate Contr                                  | de:                                              | No. of a set Ora |                         |              |                 |            |  |

|       |                                                                                                        |                                             | disabled for S<br>enabled for H                  |                  |                         |              | I MHZ)          |            |  |

| oit 6 | In Master of                                                                                           | us Select bi<br>or Slave moo                | de:                                              |                  |                         |              |                 |            |  |

|       |                                                                                                        | SMBus spe<br>SMBus spe                      | •                                                |                  |                         |              |                 |            |  |

| oit 5 | D/A: Data/                                                                                             | Address bit                                 |                                                  |                  |                         |              |                 |            |  |

|       | <u>In Master r</u><br>Reserved                                                                         | <u>node:</u>                                |                                                  |                  |                         |              |                 |            |  |

|       | In Slave m                                                                                             | ode:                                        |                                                  |                  |                         |              |                 |            |  |

|       |                                                                                                        |                                             | ast byte rece<br>ast byte rece                   |                  |                         |              |                 |            |  |

| bit 4 | P: STOP b                                                                                              | it                                          | -                                                |                  |                         |              |                 |            |  |

|       |                                                                                                        |                                             | OP bit has b<br>detected last                    | een detecte      | d last                  |              |                 |            |  |

|       | Note:                                                                                                  | This bit is c                               | leared on RE                                     | SET and w        | hen SSPEN               | is cleared.  |                 |            |  |

| bit 3 |                                                                                                        | es that a sta                               | rt bit has bee<br>detected las                   |                  | last                    |              |                 |            |  |

|       | Note:                                                                                                  |                                             | leared on RE                                     |                  | hen SSPEN               | is cleared.  |                 |            |  |

| oit 2 | R/W: Read                                                                                              | l/Write bit In                              | formation (I <sup>2</sup>                        | C mode only      | /)                      |              |                 |            |  |

|       | <u>In Slave me</u><br>1 = Read<br>0 = Write                                                            | ode:                                        |                                                  |                  |                         |              |                 |            |  |

|       | Note:                                                                                                  |                                             | ds the R/W bi<br>he address m                    |                  |                         |              |                 |            |  |

|       |                                                                                                        | nit is in prog                              |                                                  |                  |                         |              |                 |            |  |

|       | Note:                                                                                                  | nit is not in p<br>ORing this<br>in IDLE mo | bit with SEN,                                    | RSEN, PE         | N, RCEN, o              | r ACKEN wil  | l indicate if t | ne MSSP is |  |

| bit 1 | 1 = Indicate                                                                                           | es that the u                               | 10-bit Slave r<br>iser needs to<br>need to be up | update the       | address in t            | he SSPADD    | register        |            |  |

| bit 0 |                                                                                                        | Full Status b                               | •                                                |                  |                         |              |                 |            |  |

|       | In Transmit mode:<br>1 = Receive complete, SSPBUF is full<br>0 = Receive not complete, SSPBUF is empty |                                             |                                                  |                  |                         |              |                 |            |  |

|       | In Receive                                                                                             | mode:                                       |                                                  |                  | the $\overline{ACK}$ or |              |                 | o full     |  |

|       | 0 = Data tra                                                                                           | ansmit comp                                 | ogress (does<br>plete (does n                    | ot include th    | ne ACK and              | STOP bits),  | SSPBUF is       | empty      |  |

|       | Legend:                                                                                                |                                             |                                                  |                  |                         |              |                 |            |  |

|       | R = Reada                                                                                              | ble bit                                     | W = Writab                                       | le bit           | U = Unimp               | lemented bit | , read as '0'   |            |  |

|       | - n = Value                                                                                            | at POR                                      | '1' = Bit is s                                   | et               | '0' = Bit is            | cleared      | x = Bit is ur   | nknown     |  |

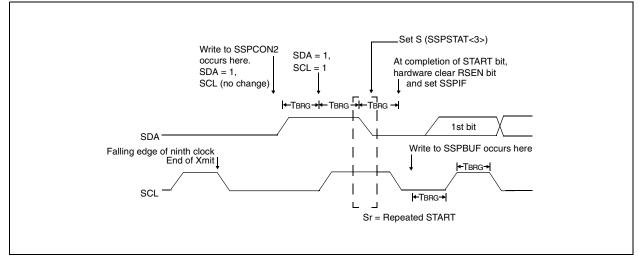

## 15.4.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated START condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the IDLE state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<5:0> and begins counting. The SDA pin is released (brought high) for one baud rate generator count (TBRG). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. Following this, the RSEN bit (SSPCON2<1>) will be automatically cleared and the baud rate generator will not be reloaded, leaving the SDA pin held low. As soon as a START condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- 2: A bus collision during the Repeated START condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

### 15.4.9.1 WCOL Status Flag

If the user writes the SSPBUF when a Repeated START sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated START condition is complete.

## FIGURE 15-20: REPEAT START CONDITION WAVEFORM

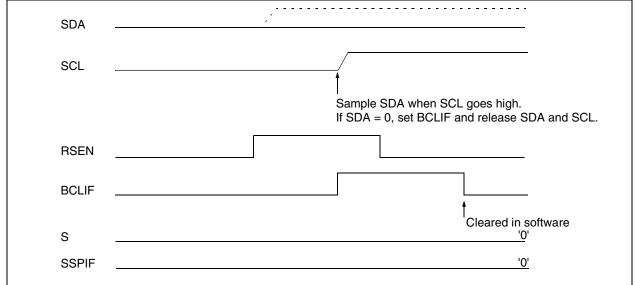

## 15.4.17.2 Bus Collision During a Repeated START Condition

During a Repeated START condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then de-asserted, and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 15-29). If SDA is sampled high, the BRG is

reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

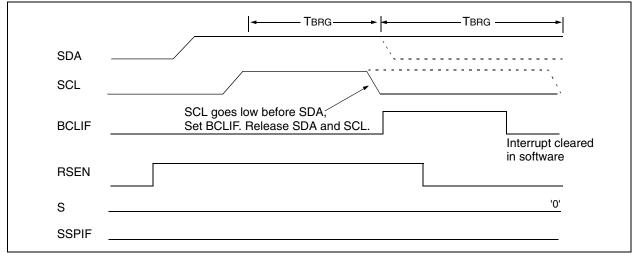

If SCL goes from high to low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated START condition, Figure 15-30.

If, at the end of the BRG time-out both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated START condition is complete.

#### FIGURE 15-30: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

## 16.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition, enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines, respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 16.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 16-1. The heart of the transmitter is the Transmit (serial) Shift Register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG is empty and interrupt bit TXIF (PIR1<4>) is set. The interrupt can be enabled/disabled by setting/clearing enable bit TXIE

(PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE, and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit, which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory, so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 16.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

Note: TXIF is not cleared immediately upon loading data into the transmit buffer TXREG. The flag bit becomes valid in the second instruction cycle following the load instruction.

## TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7                   | Bit 6         | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>All Other<br>RESETS |

|--------|-------------------------|---------------|-------------|--------|-------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE/<br>GIEH            | PEIE/<br>GIEL | TMR0IE      | INT0IE | RBIE  | TMR0IF | INTOIF | RBIF   | 0000 000x            | 0000 000u                       |

| PIR1   | PSPIF <sup>(1)</sup>    | ADIF          | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| PIE1   | PSPIE <sup>(1)</sup>    | ADIE          | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| IPR1   | PSPIP <sup>(1)</sup>    | ADIP          | RCIP        | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                    | RX9           | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 -00x            | 0000 -00x                       |

| TXREG  | USART Transmit Register |               |             |        |       |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                    | TX9           | TXEN        | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

| SPBRG  | Baud Rate               | e Genera      | ator Regist | er     |       |        |        |        | 0000 0000            | 0000 0000                       |

Legend: x = unknown, - = unimplemented, read as '0'.

Shaded cells are not used for Synchronous Master Transmission.

Note 1: The PSPIF, PSPIE and PSPIP bits are reserved on the PIC18F2X2 devices; always maintain these bits clear.

NOTES:

## REGISTER 19-12: DEVICE ID REGISTER 1 FOR PIC18FXX2 (DEVID1: BYTE ADDRESS 3FFFFEh)

|                 | R                                                                           | R                                                                                          | R         | R          | R          | R          | R            | R     |  |

|-----------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------|------------|------------|------------|--------------|-------|--|

|                 | DEV2                                                                        | DEV1                                                                                       | DEV0      | REV4       | REV3       | REV2       | REV1         | REV0  |  |

|                 | bit 7                                                                       |                                                                                            |           |            |            |            |              | bit 0 |  |

| bit 7-5         | DEV2:DEV<br>000 = PIC<br>001 = PIC<br>100 = PIC<br>101 = PIC                | 18F452<br>18F242                                                                           | D bits    |            |            |            |              |       |  |

| bit 4-0         |                                                                             | <b>REV4:REV0:</b> Revision ID bits<br>These bits are used to indicate the device revision. |           |            |            |            |              |       |  |

|                 | Legend:                                                                     |                                                                                            |           |            |            |            |              |       |  |

|                 | R = Reada                                                                   | ble bit                                                                                    | P =Progra | mmable bit | U = Unin   | nplemented | bit, read as | '0'   |  |

|                 | - n = Value when device is unprogrammed u = Unchanged from programmed state |                                                                                            |           |            |            |            |              |       |  |

|                 |                                                                             |                                                                                            |           |            |            |            |              |       |  |

| REGISTER 19-13: | DEVICEID                                                                    | REGISTE                                                                                    | R2FORP    | IC18FXX2   | (DEVID2: E | BYTE ADDI  | RESS 3FFI    | -FFh) |  |

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

### bit 7-0 **DEV10:DEV3:** Device ID bits These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

| Legend:               |                     |                                     |

|-----------------------|---------------------|-------------------------------------|

| R = Readable bit      | P =Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devi | ce is unprogrammed  | u = Unchanged from programmed state |

## 21.0 DEVELOPMENT SUPPORT

The  ${\rm PICmicro}^{\circledast}$  microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C17 and MPLAB C18 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- ICEPIC™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD

- Device Programmers

- PRO MATE® II Universal Device Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Development Programmer

- Low Cost Demonstration Boards

- PICDEM<sup>™</sup> 1 Demonstration Board

- PICDEM 2 Demonstration Board

- PICDEM 3 Demonstration Board

- PICDEM 17 Demonstration Board

- KEELOQ<sup>®</sup> Demonstration Board

## 21.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> based application that contains:

- An interface to debugging tools

- simulator

- programmer (sold separately)

- emulator (sold separately)

- in-circuit debugger (sold separately)

- A full-featured editor

- A project manager

- Customizable toolbar and key mapping

- A status bar

- On-line help

The MPLAB IDE allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro emulator and simulator tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- machine code

The ability to use MPLAB IDE with multiple debugging tools allows users to easily switch from the cost-effective simulator to a full-featured emulator with minimal retraining.

## 21.2 MPASM Assembler

The MPASM assembler is a full-featured universal macro assembler for all PICmicro MCU's.

The MPASM assembler has a command line interface and a Windows shell. It can be used as a stand-alone application on a Windows 3.x or greater system, or it can be used through MPLAB IDE. The MPASM assembler generates relocatable object files for the MPLINK object linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file that contains source lines and generated machine code, and a COD file for debugging.

The MPASM assembler features include:

- Integration into MPLAB IDE projects.

- User-defined macros to streamline assembly code.

- Conditional assembly for multi-purpose source files.

- Directives that allow complete control over the assembly process.

## 21.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI 'C' compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

## 21.8 MPLAB ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD, is a powerful, low cost, run-time development tool. This tool is based on the FLASH PICmicro MCUs and can be used to develop for this and other PICmicro microcontrollers. The MPLAB ICD utilizes the in-circuit debugging capability built into the FLASH devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> protocol, offers cost-effective in-circuit FLASH debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in realtime.

## 21.9 PRO MATE II Universal Device Programmer

The PRO MATE II universal device programmer is a full-featured programmer, capable of operating in stand-alone mode, as well as PC-hosted mode. The PRO MATE II device programmer is CE compliant.

The PRO MATE II device programmer has programmable VDD and VPP supplies, which allow it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In stand-alone mode, the PRO MATE II device programmer can read, verify, or program PICmicro devices. It can also set code protection in this mode.

## 21.10 PICSTART Plus Entry Level Development Programmer

The PICSTART Plus development programmer is an easy-to-use, low cost, prototype programmer. It connects to the PC via a COM (RS-232) port. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

The PICSTART Plus development programmer supports all PICmicro devices with up to 40 pins. Larger pin count devices, such as the PIC16C92X and PIC17C76X, may be supported with an adapter socket. The PICSTART Plus development programmer is CE compliant.

## 21.11 PICDEM 1 Low Cost PICmicro Demonstration Board

The PICDEM 1 demonstration board is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44, All necessary hardware and software is included to run basic demo programs. The user can program the sample microcontrollers provided with the PICDEM 1 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The user can also connect the PICDEM 1 demonstration board to the MPLAB ICE incircuit emulator and download the firmware to the emulator for testing. A prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push button switches and eight LEDs connected to PORTB.

## 21.12 PICDEM 2 Low Cost PIC16CXX Demonstration Board

The PICDEM 2 demonstration board is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM 2 demonstration board on a PRO MATE II device programmer, or a PICSTART Plus development programmer, and easily test firmware. The MPLAB ICE in-circuit emulator may also be used with the PICDEM 2 demonstration board to test firmware. A prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push button switches, a potentiometer for simulated analog input, a serial EEPROM to demonstrate usage of the I<sup>2</sup>C<sup>™</sup> bus and separate headers for connection to an LCD module and a keypad.

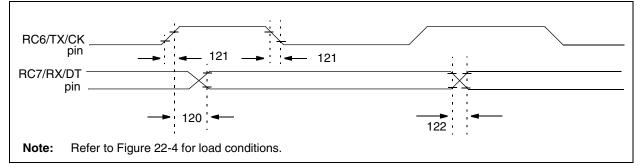

## FIGURE 22-20: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 22-19: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                        |                     | Min | Max | Units | Conditions |

|---------------|----------|-----------------------------------------------------------------------|---------------------|-----|-----|-------|------------|

| 120           | TckH2dtV | <u>SYNC XMIT (MASTER &amp; SLAVE)</u><br>Clock high to data out valid | PIC18 <b>F</b> XXX  | _   | 50  | ns    |            |

|               |          |                                                                       | PIC18LFXXX          |     | 150 | ns    | VDD = 2V   |

| 121           | Tckr     | Clock out rise time and fall time                                     | PIC18FXXX           | _   | 25  | ns    |            |

|               |          | (Master mode)                                                         | PIC18LFXXX          | —   | 60  | ns    | VDD = 2V   |

| 122           | Tdtr     | Data out rise time and fall time                                      | PIC18FXXX           |     | 25  | ns    |            |

|               |          |                                                                       | PIC18 <b>LF</b> XXX |     | 60  | ns    | VDD = 2V   |

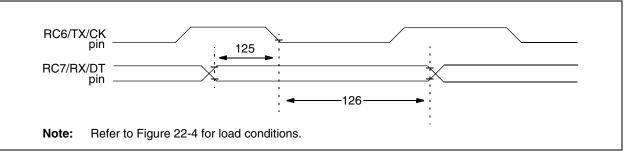

## FIGURE 22-21: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## TABLE 22-20: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Param.<br>No. | Symbol   | Characteristic                                                                          |            | Min | Max | Units | Conditions |

|---------------|----------|-----------------------------------------------------------------------------------------|------------|-----|-----|-------|------------|

| 125           | TdtV2ckl | <u>SYNC RCV (MASTER &amp; SLAVE)</u><br>Data hold before CK $\downarrow$ (DT hold time) |            | 10  |     | ns    |            |

| 126           | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                          | PIC18FXXX  | 15  |     | ns    |            |

|               |          |                                                                                         | PIC18LFXXX | 20  |     | ns    | VDD = 2V   |

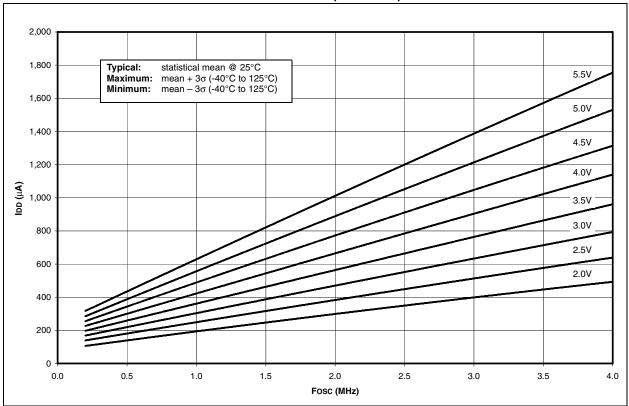

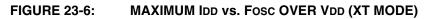

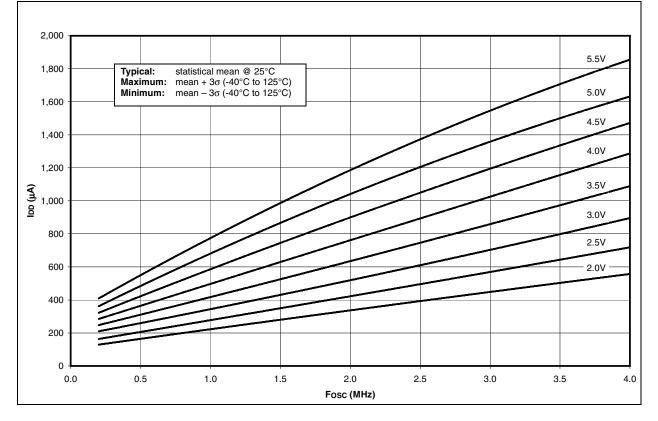

FIGURE 23-5: TYPICAL IDD vs. Fosc OVER VDD (XT MODE)

NOTES: