Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 23                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 1.5K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 5x10b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f252-i-sp |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

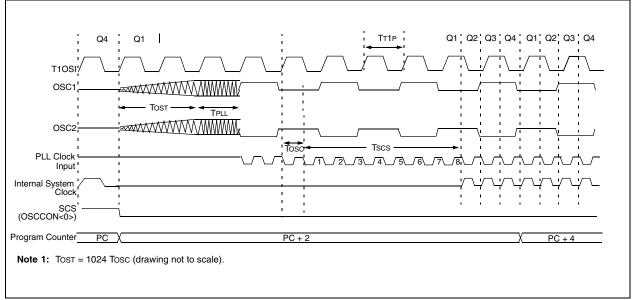

If the main oscillator is configured for HS-PLL mode, an oscillator start-up time (TOST) plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram indicating the transition from the Timer1 oscillator to the main oscillator for HS-PLL mode is shown in Figure 2-10.

FIGURE 2-10: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS WITH PLL)

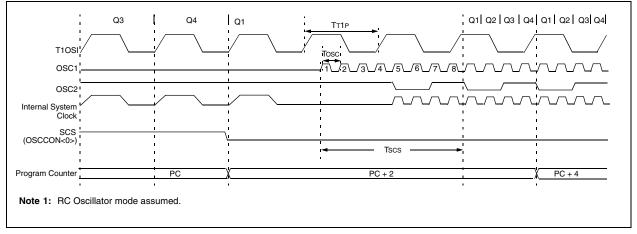

If the main oscillator is configured in the RC, RCIO, EC or ECIO modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for RC, RCIO, EC and ECIO modes, is shown in Figure 2-11.

### FIGURE 2-11: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

| TABLE 3-1: TIME- | OUT IN VARIOUS SITUATIONS |

|------------------|---------------------------|

|------------------|---------------------------|

| Oscillator                         | Power-up                   | (2)                 | _                                          | Wake-up from                  |  |

|------------------------------------|----------------------------|---------------------|--------------------------------------------|-------------------------------|--|

| Configuration                      | PWRTE = 0PWRTE = 1         |                     | Brown-out                                  | SLEEP or<br>Oscillator Switch |  |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024 Tosc<br>+ 2ms | 1024 Tosc<br>+ 2 ms | 72 ms <sup>(2)</sup> + 1024 Tosc<br>+ 2 ms | 1024 Tosc + 2 ms              |  |

| HS, XT, LP                         | 72 ms + 1024 Tosc          | 1024 Tosc           | 72 ms <sup>(2)</sup> + 1024 Tosc           | 1024 Tosc                     |  |

| EC                                 | 72 ms                      | —                   | 72 ms <sup>(2)</sup>                       | —                             |  |

| External RC                        | 72 ms                      | —                   | 72 ms <sup>(2)</sup>                       | —                             |  |

Note 1: 2 ms is the nominal time required for the 4x PLL to lock.

2: 72 ms is the nominal power-up timer delay, if implemented.

#### REGISTER 3-1: RCON REGISTER BITS AND POSITIONS

| R/    | W-0 | U-0 | U-0 | R/W-1 | R-1 | R-1 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-------|-----|-----|-------|-------|

| IP    | EN  | —   | —   | RI    | TO  | PD  | POR   | BOR   |

| bit 7 |     |     |     |       |     |     |       | bit 0 |

**Note 1:** Refer to Section 4.14 (page 53) for bit definitions.

# TABLE 3-2:STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR<br/>RCON REGISTER

| Condition                                        | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|--------------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                   | 0000h                 | 01 1100          | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation               | 0000h                 | 0u uuuu          | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation           | 0000h                 | 00 uuuu          | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation         | 0000h                 | 0u uull          | u  | u  | u  | u   | u   | u      | 1      |

| Stack Underflow Reset during<br>normal operation | 0000h                 | 0u uull          | u  | u  | u  | u   | u   | 1      | u      |

| MCLR Reset during SLEEP                          | 0000h                 | 0u 10uu          | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                        | 0000h                 | 0u 01uu          | 1  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                      | PC + 2                | uu 00uu          | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                                  | 0000h                 | 01 11u0          | 1  | 1  | 1  | 1   | 0   | u      | u      |

| Interrupt wake-up from SLEEP                     | PC + 2 <sup>(1)</sup> | uu 00uu          | u  | 1  | 0  | u   | u   | u      | u      |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (0x00008h or 0x000018h).

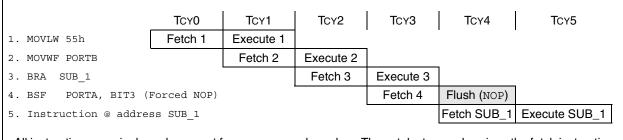

# 4.6 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 4-2).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register" (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### EXAMPLE 4-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

# 4.7 Instructions in Program Memory

The program memory is addressed in bytes. Instructions are stored as two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB ='0'). Figure 4-5 shows an example of how instruction words are stored in the program memory. To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 4.4). The CALL and GOTO instructions have an absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-5 shows how the instruction "GOTO 00006h' is encoded in the program memory. Program branch instructions which encode a relative address offset operate in the same manner. The offset value stored in a branch instruction represents the number of single word instructions that the PC will be offset by. Section 20.0 provides further details of the instruction set.

### FIGURE 4-5: INSTRUCTIONS IN PROGRAM MEMORY

|                |            |                    | LSB = 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|------------|--------------------|---------|---------|---------------------------|

|                | Program M  |                    |         |         | 000000h                   |

|                | Byte Locat | ions $\rightarrow$ |         |         | 000002h                   |

|                |            |                    |         |         | 000004h                   |

|                |            |                    |         |         | 000006h                   |

| Instruction 1: | MOVLW      | 055h               | 0Fh     | 55h     | 000008h                   |

| Instruction 2: | GOTO       | 000006h            | EFh     | 03h     | 00000Ah                   |

|                |            |                    | F0h     | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF      | 123h, 456h         | Clh     | 23h     | 00000Eh                   |

|                |            |                    | F4h     | 56h     | 000010h                   |

|                |            |                    |         |         | 000012h                   |

|                |            |                    |         |         | 000014h                   |

## 4.12 Indirect Addressing, INDF and FSR Registers

Indirect addressing is a mode of addressing data memory, where the data memory address in the instruction is not fixed. An FSR register is used as a pointer to the data memory location that is to be read or written. Since this pointer is in RAM, the contents can be modified by the program. This can be useful for data tables in the data memory and for software stacks. Figure 4-9 shows the operation of indirect addressing. This shows the moving of the value to the data memory address specified by the value of the FSR register.

Indirect addressing is possible by using one of the INDF registers. Any instruction using the INDF register actually accesses the register pointed to by the File Select Register, FSR. Reading the INDF register itself, indirectly (FSR = 0), will read 00h. Writing to the INDF register indirectly, results in a no operation. The FSR register contains a 12-bit address, which is shown in Figure 4-10.

The INDFn register is not a physical register. Addressing INDFn actually addresses the register whose address is contained in the FSRn register (FSRn is a pointer). This is indirect addressing.

Example 4-4 shows a simple use of indirect addressing to clear the RAM in Bank1 (locations 100h-1FFh) in a minimum number of instructions.

#### EXAMPLE 4-4: HOW TO CLEAR RAM (BANK1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0 ,0x100 | ; |                |

|---------|-------|-------------|---|----------------|

| NEXT    | CLRF  | POSTINC0    | ; | Clear INDF     |

|         |       |             | ; | register and   |

|         |       |             | ; | inc pointer    |

|         | BTFSS | FSROH, 1    | ; | All done with  |

|         |       |             | ; | Bank1?         |

|         | GOTO  | NEXT        | ; | NO, clear next |

| CONTINU | Έ     |             | ; | YES, continue  |

|         |       |             |   |                |

There are three indirect addressing registers. To address the entire data memory space (4096 bytes), these registers are 12-bit wide. To store the 12-bits of addressing information, two 8-bit registers are required. These indirect addressing registers are:

- 1. FSR0: composed of FSR0H:FSR0L

- 2. FSR1: composed of FSR1H:FSR1L

- 3. FSR2: composed of FSR2H:FSR2L

In addition, there are registers INDF0, INDF1 and INDF2, which are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. If an instruction writes a value to INDF0, the value will be written to the address pointed to by FSR0H:FSR0L. A read from INDF1 reads

the data from the address pointed to by FSR1H:FSR1L. INDFn can be used in code anywhere an operand can be used.

If INDF0, INDF1 or INDF2 are read indirectly via an FSR, all '0's are read (zero bit is set). Similarly, if INDF0, INDF1 or INDF2 are written to indirectly, the operation will be equivalent to a NOP instruction and the STATUS bits are not affected.

#### 4.12.1 INDIRECT ADDRESSING OPERATION

Each FSR register has an INDF register associated with it, plus four additional register addresses. Performing an operation on one of these five registers determines how the FSR will be modified during indirect addressing.

When data access is done to one of the five INDFn locations, the address selected will configure the FSRn register to:

- Do nothing to FSRn after an indirect access (no change) INDFn

- Auto-decrement FSRn after an indirect access (post-decrement) POSTDECn

- Auto-increment FSRn after an indirect access (post-increment) POSTINCn

- Auto-increment FSRn before an indirect access (pre-increment) PREINCn

- Use the value in the WREG register as an offset to FSRn. Do not modify the value of the WREG or the FSRn register after an indirect access (no change) - PLUSWn

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the STATUS register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

Incrementing or decrementing an FSR affects all 12 bits. That is, when FSRnL overflows from an increment, FSRnH will be incremented automatically.

Adding these features allows the FSRn to be used as a stack pointer, in addition to its uses for table operations in data memory.

Each FSR has an address associated with it that performs an indexed indirect access. When a data access to this INDFn location (PLUSWn) occurs, the FSRn is configured to add the signed value in the WREG register and the value in FSR to form the address before an indirect access. The FSR value is not changed.

If an FSR register contains a value that points to one of the INDFn, an indirect read will read 00h (zero bit is set), while an indirect write will be equivalent to a NOP (STATUS bits are not affected).

If an indirect addressing operation is done where the target address is an FSRnH or FSRnL register, the write operation will dominate over the pre- or post-increment/decrement functions.

| Address | Name   | Bit 7        | Bit 6         | Bit 5       | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0  | Value on:<br>POR, BOR | Value on<br>All Other<br>RESETS |

|---------|--------|--------------|---------------|-------------|------------|--------------|-------|--------|--------|-----------------------|---------------------------------|

| FF2h    | INTCON | GIE/<br>GIEH | PEIE/<br>GIEL | TOIE        | INTE       | RBIE         | TOIF  | INTF   | RBIF   | 0000 000x             | 0000 000u                       |

| FA9h    | EEADR  | EEPRON       | I Address     | Register    |            |              |       |        |        | 0000 0000             | 0000 0000                       |

| FA8h    | EEDATA | EEPRON       | l Data Reg    | jister      |            |              |       |        |        | 0000 0000             | 0000 0000                       |

| FA7h    | EECON2 | EEPRON       | I Control F   | legister2 ( | (not a phy | /sical regis | ter)  |        |        | _                     | —                               |

| FA6h    | EECON1 | EEPGD        | CFGS          | —           | FREE       | WRERR        | WREN  | WR     | RD     | xx-0 x000             | uu-0 u000                       |

| FA2h    | IPR2   | _            | _             | _           | EEIP       | BCLIP        | LVDIP | TMR3IP | CCP2IP | 1 1111                | 1 1111                          |

| FA1h    | PIR2   | —            | —             | —           | EEIF       | BCLIF        | LVDIF | TMR3IF | CCP2IF | 0 0000                | 0 0000                          |

| FA0h    | PIE2   | _            |               |             | EEIE       | BCLIE        | LVDIE | TMR3IE | CCP2IE | 0 0000                | 0 0000                          |

Legend: x = unknown, u = unchanged, r = reserved, - = unimplemented, read as '0'. Shaded cells are not used during FLASH/EEPROM access.

# PIC18FXX2

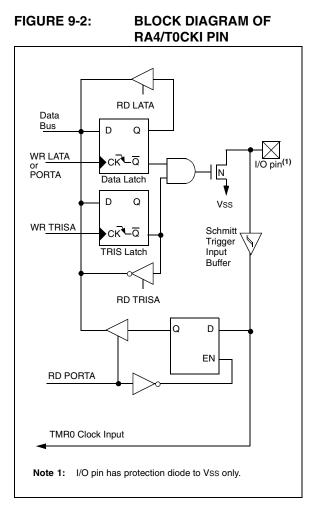

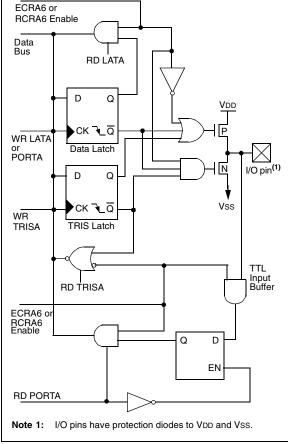

# FIGURE 9-3: BLOCK DIAGRAM OF RA6 PIN

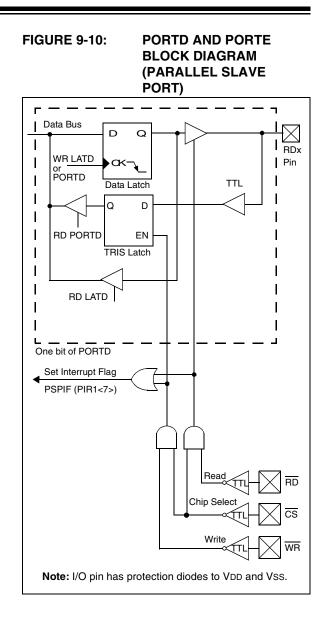

# 9.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40-pin devices only (PIC18F4X2).

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit, PSPMODE (TRISE<4>) is set. It is asynchronously readable and writable by the external world through RD control input pin, RE0/RD and WR control input pin, RE1/WR.

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, <u>RE1/WR</u> to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The A/D port configuration bits PCFG2:PCFG0 (ADCON1<2:0>) must be set, which will configure pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

The PORTE I/O pins become control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs), and the ADCON1 is configured for digital I/O. In this mode, the input buffers are TTL.

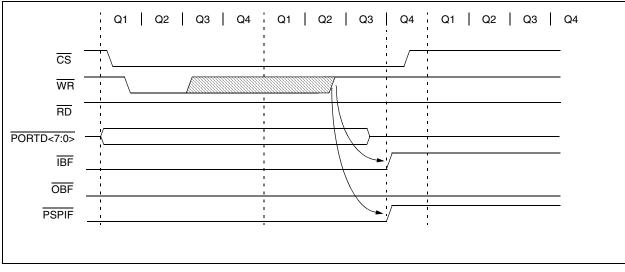

## FIGURE 9-11: PARALLEL SLAVE PORT WRITE WAVEFORMS

# 13.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt-on-overflow from FFFFh to 0000h

- RESET from CCP module trigger

Figure 13-1 is a simplified block diagram of the Timer3 module.

Register 13-1 shows the Timer3 control register. This register controls the Operating mode of the Timer3 module and sets the CCP clock source.

Register 11-1 shows the Timer1 control register. This register controls the Operating mode of the Timer1 module, as well as contains the Timer1 oscillator enable bit (T1OSCEN), which can be a clock source for Timer3.

### REGISTER 13-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0         | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|---------------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | <b>T3SYNC</b> | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |               |        | bit 0  |

| bit 7   | RD16: 16-bit Read/Write N                                | Node Enable bit            |                      |                    |  |  |  |  |  |

|---------|----------------------------------------------------------|----------------------------|----------------------|--------------------|--|--|--|--|--|

|         | 1 = Enables register Read                                | /Write of Timer3 in one    | e 16-bit operation   |                    |  |  |  |  |  |

|         | 0 = Enables register Read                                | /Write of Timer3 in two    | o 8-bit operations   |                    |  |  |  |  |  |

| bit 6-3 | T3CCP2:T3CCP1: Timer3                                    | and Timer1 to CCPx         | Enable bits          |                    |  |  |  |  |  |

|         | 1x = Timer3 is the clock so                              | ource for compare/cap      | ture CCP modules     |                    |  |  |  |  |  |

|         | 01 = Timer3 is the clock so                              |                            |                      |                    |  |  |  |  |  |

|         |                                                          | ource for compare/cap      |                      |                    |  |  |  |  |  |

|         | 00 = Timer1 is the clock so                              | ource for compare/cap      | ture CCP modules     |                    |  |  |  |  |  |

| bit 5-4 | T3CKPS1:T3CKPS0: Timer3 Input Clock Prescale Select bits |                            |                      |                    |  |  |  |  |  |

|         | 11 = 1:8 Prescale value                                  |                            |                      |                    |  |  |  |  |  |

|         | 10 = 1:4 Prescale value                                  |                            |                      |                    |  |  |  |  |  |

|         | 01 = 1:2 Prescale value                                  |                            |                      |                    |  |  |  |  |  |

|         | 00 = 1:1 Prescale value                                  |                            |                      |                    |  |  |  |  |  |

| bit 2   | T3SYNC: Timer3 External                                  | • •                        |                      |                    |  |  |  |  |  |

|         | (Not usable if the system of                             | CIOCK COMES FROM TIME      | er i/Timer3)         |                    |  |  |  |  |  |

|         | <u>When TMR3CS = 1:</u><br>1 = Do not synchronize ex     | tornal clock input         |                      |                    |  |  |  |  |  |

|         | 0 = Synchronize external of                              |                            |                      |                    |  |  |  |  |  |

|         | When TMR3CS = $0$ :                                      |                            |                      |                    |  |  |  |  |  |

|         | This bit is ignored. Timer3                              | uses the internal clock    | when TMB3CS - 0      |                    |  |  |  |  |  |

| bit 1   | TMR3CS: Timer3 Clock S                                   |                            |                      |                    |  |  |  |  |  |

|         |                                                          |                            |                      |                    |  |  |  |  |  |

|         | 1 = External clock input fr                              | ter the first falling edge |                      |                    |  |  |  |  |  |

|         | 0 = Internal clock (Fosc/4                               |                            | ·)                   |                    |  |  |  |  |  |

| bit 0   | TMR3ON: Timer3 On bit                                    | /                          |                      |                    |  |  |  |  |  |

| Sit 0   | 1 = Enables Timer3                                       |                            |                      |                    |  |  |  |  |  |

|         | 0 = Stops Timer3                                         |                            |                      |                    |  |  |  |  |  |

|         |                                                          |                            |                      |                    |  |  |  |  |  |

|         | Legend:                                                  |                            |                      |                    |  |  |  |  |  |

|         | R = Readable bit                                         | W = Writable bit           | U = Unimplemented    | bit, read as '0'   |  |  |  |  |  |

|         | - n = Value at POR                                       | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |  |

|         | ··· -                                                    |                            |                      | -                  |  |  |  |  |  |

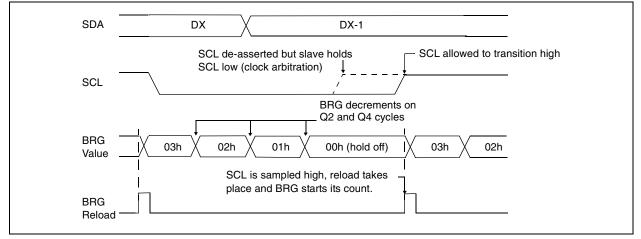

### 15.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated START/STOP condition, de-asserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is

sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count, in the event that the clock is held low by an external device (Figure 15-18).

#### 18.2.1 REFERENCE VOLTAGE SET POINT

The Internal Reference Voltage of the LVD module may be used by other internal circuitry (the Programmable Brown-out Reset). If these circuits are disabled (lower current consumption), the reference voltage circuit requires a time to become stable before a low voltage condition can be reliably detected. This time is invariant of system clock speed. This start-up time is specified in electrical specification parameter 36. The low voltage interrupt flag will not be enabled until a stable reference voltage is reached. Refer to the waveform in Figure 18-4.

#### 18.2.2 CURRENT CONSUMPTION

When the module is enabled, the LVD comparator and voltage divider are enabled and will consume static current. The voltage divider can be tapped from multiple places in the resistor array. Total current consumption, when enabled, is specified in electrical specification parameter #D022B.

#### 18.3 Operation During SLEEP

When enabled, the LVD circuitry continues to operate during SLEEP. If the device voltage crosses the trip point, the LVDIF bit will be set and the device will wakeup from SLEEP. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

### 18.4 Effects of a RESET

A device RESET forces all registers to their RESET state. This forces the LVD module to be turned off.

#### 19.4.2 DATA EEPROM CODE PROTECTION

The entire Data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of Data EEPROM. WRTD inhibits external writes to Data EEPROM. The CPU can continue to read and write Data EEPROM regardless of the protection bit settings.

#### 19.4.3 CONFIGURATION REGISTER PROTECTION

The configuration registers can be write protected. The WRTC bit controls protection of the configuration registers. In User mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 19.5 ID Locations

Eight memory locations (20000h - 200007h) are designated as ID locations, where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions, or during program/verify. The ID locations can be read when the device is code protected.

The sequence for programming the ID locations is similar to programming the FLASH memory (see Section 5.5.1).

## 19.6 In-Circuit Serial Programming

PIC18FXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 19.7 In-Circuit Debugger

When the DEBUG bit in configuration register CONFIG4L is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 19-4 shows which features are consumed by the background debugger.

| I/O pins       | RB6, RB7  |

|----------------|-----------|

| Stack          | 2 levels  |

| Program Memory | 512 bytes |

| Data Memory    | 10 bytes  |

To use the In-Circuit Debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the In-Circuit Debugger module available from Microchip or one of the third party development tool companies.

# 19.8 Low Voltage ICSP Programming

The LVP bit configuration register CONFIG4L enables low voltage ICSP programming. This mode allows the microcontroller to be programmed via ICSP using a VDD source in the operating voltage range. This only means that VPP does not have to be brought to VIHH, but can instead be left at the normal operating voltage. In this mode, the RB5/PGM pin is dedicated to the programming function and ceases to be a general purpose I/O pin. During programming, VDD is applied to the MCLR/VPP pin. To enter Programming mode, VDD must be applied to the RB5/PGM, provided the LVP bit is set. The LVP bit defaults to a ('1') from the factory.

- Note 1: The High Voltage Programming mode is always available, regardless of the state of the LVP bit, by applying VIHH to the MCLR pin.

- 2: While in low voltage ICSP mode, the RB5 pin can no longer be used as a general purpose I/O pin, and should be held low during normal operation to protect against inadvertent ICSP mode entry.

- **3:** When using low voltage ICSP programming (LVP), the pull-up on RB5 becomes disabled. If TRISB bit 5 is cleared, thereby setting RB5 as an output, LATB bit 5 must also be cleared for proper operation.

If Low Voltage Programming mode is not used, the LVP bit can be programmed to a '0' and RB5/PGM becomes a digital I/O pin. However, the LVP bit may only be programmed when programming is entered with VIHH on MCLR/VPP.

It should be noted that once the LVP bit is programmed to 0, only the High Voltage Programming mode is available and only High Voltage Programming mode can be used to program the device.

When using low voltage ICSP, the part must be supplied 4.5V to 5.5V, if a bulk erase will be executed. This includes reprogramming of the code protect bits from an on-state to off-state. For all other cases of low voltage ICSP, the part may be programmed at the normal operating voltage. This means unique user IDs, or user code can be reprogrammed or added.

# PIC18FXX2

| BZ                                    | Branch if                                                                         | Zero                                                                                                                                                                                                                                                                                 |             |  |  |  |  |

|---------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| Syntax:                               | [ <i>label</i> ] B                                                                | [ <i>label</i> ] BZ n                                                                                                                                                                                                                                                                |             |  |  |  |  |

| Operands:                             | ands: $-128 \le n \le 127$                                                        |                                                                                                                                                                                                                                                                                      |             |  |  |  |  |

| Operation:                            | if Zero bit                                                                       | ·• ·                                                                                                                                                                                                                                                                                 |             |  |  |  |  |

|                                       | (PC) + 2 +                                                                        | $(PC) + 2 + 2n \to PC$                                                                                                                                                                                                                                                               |             |  |  |  |  |

| Status Affected:                      | None                                                                              |                                                                                                                                                                                                                                                                                      | 1           |  |  |  |  |

| Encoding:                             | 1110                                                                              | 0000 nni                                                                                                                                                                                                                                                                             | ın nnnn     |  |  |  |  |

| Description:                          | gram will t<br>The 2's co<br>added to th<br>have incre<br>instruction<br>PC+2+2n. | If the Zero bit is '1', then the pro-<br>gram will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |             |  |  |  |  |

| Words:                                | 1                                                                                 |                                                                                                                                                                                                                                                                                      |             |  |  |  |  |

| Cycles:                               | 1(2)                                                                              |                                                                                                                                                                                                                                                                                      |             |  |  |  |  |

| Q Cycle Activity:<br>If Jump:         |                                                                                   |                                                                                                                                                                                                                                                                                      |             |  |  |  |  |

| Q1                                    | Q2                                                                                | Q3                                                                                                                                                                                                                                                                                   | Q4          |  |  |  |  |

| Decode                                | Read literal<br>'n'                                                               | Process<br>Data                                                                                                                                                                                                                                                                      | Write to PC |  |  |  |  |

| No                                    | No                                                                                | No                                                                                                                                                                                                                                                                                   | No          |  |  |  |  |

| operation<br>If No Jump:              | operation                                                                         | operation                                                                                                                                                                                                                                                                            | operation   |  |  |  |  |

| II NO Julip.<br>Q1                    | Q2                                                                                | Q3                                                                                                                                                                                                                                                                                   | Q4          |  |  |  |  |

| Decode                                | Read literal                                                                      | Process                                                                                                                                                                                                                                                                              | No          |  |  |  |  |

|                                       | 'n'                                                                               | Data                                                                                                                                                                                                                                                                                 | operation   |  |  |  |  |

| Example:                              | HERE                                                                              | BZ Jump                                                                                                                                                                                                                                                                              |             |  |  |  |  |

| Before Instru<br>PC<br>After Instruct | = ade<br>ion<br>= 1;                                                              | dress (HERE)                                                                                                                                                                                                                                                                         |             |  |  |  |  |

| If Zero<br>PC<br>If Zero              | = ade<br>= 0:                                                                     | dress (Jump)                                                                                                                                                                                                                                                                         | )           |  |  |  |  |

| CALL                                               | Subrouti                                                                                                                                       | ne Call                                                                                                          |                                                                                                                 |                                                                               |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Syntax:                                            | [label] (                                                                                                                                      | CALL k                                                                                                           | [,s]                                                                                                            |                                                                               |

| Operands:                                          | 0 ≤ k ≤ 10<br>s ∈ [0,1]                                                                                                                        | 48575                                                                                                            |                                                                                                                 |                                                                               |

| Operation:                                         | $\begin{array}{l} (PC) + 4 - \\ k \rightarrow PC < 2 \\ \text{if } s = 1 \\ (W) \rightarrow WS \\ (STATUS) \\ (BSR) \rightarrow \end{array}$   | 20:1>,<br>S,<br>) → STA                                                                                          | TUSS,                                                                                                           |                                                                               |

| Status Affected:                                   | None                                                                                                                                           |                                                                                                                  |                                                                                                                 |                                                                               |

| Encoding:<br>1st word (k<7:0><br>2nd word(k<19:8   |                                                                                                                                                | 110s<br>k <sub>19</sub> kkk                                                                                      | k <sub>7</sub> kkk<br>kkkk                                                                                      | kkkk <sub>0</sub><br>kkkk <sub>8</sub>                                        |

| Description:                                       | Subroutin<br>memory r<br>address (I<br>return sta<br>STATUS a<br>also push<br>shadow re<br>and BSRS<br>occurs (de<br>value 'k' is<br>CALL is a | ange. F<br>PC+ 4) is<br>ck. If 's'<br>and BSF<br>ed into t<br>egisters,<br>S. If 's' =<br>efault). T<br>s loaded | irst, retur<br>s pushed<br>= 1, the<br>register<br>heir resp<br>WS, ST/<br>= 0, no up<br>Then, the<br>i into PC | n<br>onto the<br>W,<br>s are<br>ective<br>ATUSS<br>odate<br>20-bit<br><20:1>. |

| Words:                                             | 2                                                                                                                                              |                                                                                                                  |                                                                                                                 |                                                                               |

| Cycles:                                            | 2                                                                                                                                              |                                                                                                                  |                                                                                                                 |                                                                               |

| Q Cycle Activity                                   | r:                                                                                                                                             |                                                                                                                  |                                                                                                                 |                                                                               |

| Q1                                                 | Q2                                                                                                                                             | Q                                                                                                                | 3                                                                                                               | Q4                                                                            |

| Decode                                             | Read literal<br>'k'<7:0>,                                                                                                                      | Push P<br>stac                                                                                                   | k 'k'                                                                                                           | ad literal<br><19:8>,<br>ite to PC                                            |

| No<br>operation                                    | No<br>operation                                                                                                                                | No<br>operat                                                                                                     |                                                                                                                 | No<br>peration                                                                |

| Example:                                           | HERE                                                                                                                                           | CALL                                                                                                             | THERE,                                                                                                          | 1                                                                             |

| Before Instr<br>PC                                 | = address                                                                                                                                      | <b>s</b> (HERE                                                                                                   | )                                                                                                               |                                                                               |

| After Instruc<br>PC<br>TOS<br>WS<br>BSRS<br>STATUS | = address<br>= address<br>= W<br>= BSR                                                                                                         | s (HERE                                                                                                          |                                                                                                                 |                                                                               |

# PIC18FXX2

| RLNCF                 | Rotate L                                                                   | eft f (no car                                                       | ry)                                                                                             | RRCF                      | Rotate R                                                                                                                                                                                                                                                                                                                                                                        | ight f throu | igh Cai | rry        |

|-----------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|------------|

| Syntax:               | [ label ]                                                                  | RLNCF f                                                             | [,d [,a]                                                                                        | Syntax:                   | [ label ]                                                                                                                                                                                                                                                                                                                                                                       | RRCF f[      | ,d [,a] |            |

| Operands:             | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                       | 55                                                                  |                                                                                                 | Operands:                 | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                            | 5            |         |            |

| Operation:            | (f<7>) →                                                                   | dest <n+1>,<br/>dest&lt;0&gt;</n+1>                                 |                                                                                                 | Operation:                | $(f < n >) \rightarrow$<br>$(f < 0 >) \rightarrow$<br>$(C) \rightarrow des$                                                                                                                                                                                                                                                                                                     |              |         |            |

| Status Affected:      | N, Z                                                                       | 1                                                                   |                                                                                                 | Status Affected:          | (C) → ue.<br>C, N, Z                                                                                                                                                                                                                                                                                                                                                            | 51<7>        |         |            |

| Encoding:             | 0100                                                                       |                                                                     | fff ffff                                                                                        |                           | 0011                                                                                                                                                                                                                                                                                                                                                                            | 00da f       | fff     | ffff       |

| Description:          |                                                                            | ents of regis                                                       | ter 'f' are<br>left. If 'd' is 0,                                                               | Encoding:<br>Description: |                                                                                                                                                                                                                                                                                                                                                                                 |              |         |            |

|                       | the resul<br>the resul<br>'f' (defaul<br>Bank will<br>the BSR<br>bank will | t is placed in<br>t is stored ba<br>t). If 'a' is 0,<br>be selected | W. If 'd' is 1,<br>ack in register<br>the Access<br>, overriding<br>s 1, then the<br>as per the | ·                         | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in W. If 'd' is 1, the result<br>is placed back in register 'f'<br>(default). If 'a' is 0, the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is 1, then the<br>bank will be selected as per the<br>BSR value (default). |              |         |            |

| Words:                | 1                                                                          |                                                                     |                                                                                                 |                           |                                                                                                                                                                                                                                                                                                                                                                                 | + registe    | er f    | <b> </b> ▶ |

| Cycles:               | 1                                                                          |                                                                     |                                                                                                 | Words:                    | 1                                                                                                                                                                                                                                                                                                                                                                               |              |         | ·]         |

| Q Cycle Activity:     |                                                                            |                                                                     |                                                                                                 |                           | 1                                                                                                                                                                                                                                                                                                                                                                               |              |         |            |

| Q1                    | Q2                                                                         | Q3                                                                  | Q4                                                                                              | Cycles:                   | 1                                                                                                                                                                                                                                                                                                                                                                               |              |         |            |

| Decode                | Read<br>register 'f'                                                       | Process<br>Data                                                     | Write to destination                                                                            | Q Cycle Activity<br>Q1    | r:<br>Q2                                                                                                                                                                                                                                                                                                                                                                        | Q3           |         | Q4         |

|                       |                                                                            | Data                                                                | destination                                                                                     | Decode                    | Read                                                                                                                                                                                                                                                                                                                                                                            | Process      | -       | tite to    |

| Example:              | RLNCF                                                                      | REG, 1,                                                             | 0                                                                                               | 200000                    | register 'f'                                                                                                                                                                                                                                                                                                                                                                    | Data         |         | ination    |

| Before Instru<br>REG  | = 1010 1                                                                   | 1011                                                                |                                                                                                 | Example:                  | RRCF                                                                                                                                                                                                                                                                                                                                                                            | REG, 0,      | 0       |            |

| After Instruct<br>REG | ion<br>= 0101 (                                                            | 0111                                                                |                                                                                                 | Before Instr<br>REG<br>C  | uction<br>= 1110<br>= 0                                                                                                                                                                                                                                                                                                                                                         | 0110         |         |            |

|                       |                                                                            |                                                                     |                                                                                                 | After Instruc             | ction                                                                                                                                                                                                                                                                                                                                                                           |              |         |            |

$\begin{array}{rrrr} REG & = & 1110 & 0110 \\ W & = & 0111 & 0011 \\ C & = & 0 \end{array}$

# 22.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings (†)

| -                                                                      |                      |

|------------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                         |                      |

| Storage temperature                                                    | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)     | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                     | -0.3V to +7.5V       |

| Voltage on MCLR with respect to Vss (Note 2)                           | 0V to +13.25V        |

| Voltage on RA4 with respect to Vss                                     | 0V to +8.5V          |

| Total power dissipation (Note 1)                                       |                      |

| Maximum current out of Vss pin                                         |                      |

| Maximum current into VDD pin                                           | 250 mA               |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                           | ±20 mA               |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                         | ±20 mA               |

| Maximum output current sunk by any I/O pin                             | 25 mA                |

| Maximum output current sourced by any I/O pin                          | 25 mA                |

| Maximum current sunk by PORTA, PORTB, and PORTE (Note 3) (combined)    | 200 mA               |

| Maximum current sourced by PORTA, PORTB, and PORTE (Note 3) (combined) | 200 mA               |

| Maximum current sunk by PORTC and PORTD (Note 3) (combined)            |                      |

| Maximum current sourced by PORTC and PORTD (Note 3) (combined)         |                      |

| Note 1. Power dissination is calculated as follows:                    |                      |

- Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL)

- 2: Voltage spikes below Vss at the  $\overline{\text{MCLR}}/\text{VPP}$  pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100 $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}/\text{VPP}$  pin, rather than pulling this pin directly to Vss.

- 3: PORTD and PORTE not available on the PIC18F2X2 devices.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

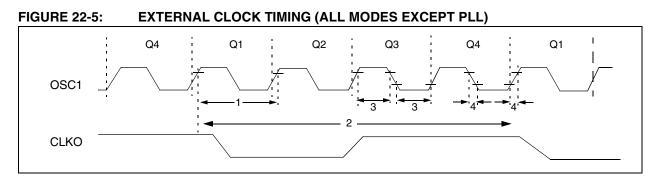

### 22.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

### TABLE 22-4: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param.<br>No. | Symbol | Characteristic                         | Min | Мах    | Units | Conditions                                         |

|---------------|--------|----------------------------------------|-----|--------|-------|----------------------------------------------------|

| 1A            | Fosc   | External CLKI Frequency <sup>(1)</sup> | DC  | 40     | MHz   | EC, ECIO, -40°C to +85°C                           |

|               |        | Oscillator Frequency <sup>(1)</sup>    | DC  | 25     | MHz   | EC, ECIO, +85°C to +125°C                          |

|               |        |                                        | DC  | 4      | MHz   | RC osc                                             |

|               |        |                                        | 0.1 | 4      | MHz   | XT osc                                             |

|               |        |                                        | 4   | 25     | MHz   | HS osc                                             |

|               |        |                                        | 4   | 10     | MHz   | HS + PLL osc, -40°C to +85°C                       |

|               |        |                                        | 4   | 6.25   | MHz   | HS + PLL osc, +85°C to +125°C                      |

|               |        |                                        | 5   | 200    | kHz   | LP Osc mode                                        |

| 1             | Tosc   | External CLKI Period <sup>(1)</sup>    | 25  | _      | ns    | EC, ECIO, -40°C to +85°C                           |

|               |        | Oscillator Period <sup>(1)</sup>       | 40  | —      | ns    | EC, ECIO, +85°C to +125°C                          |

|               |        |                                        | 250 | —      | ns    | RC osc                                             |

|               |        |                                        | 250 | 10,000 | ns    | XT osc                                             |

|               |        |                                        | 40  | 250    | ns    | HS osc                                             |

|               |        |                                        | 100 | 250    | ns    | HS + PLL osc, -40°C to +85°C                       |

|               |        |                                        | 160 | 250    | ns    | HS + PLL osc, +85°C to +125°C                      |

|               |        |                                        | 25  | —      | μs    | LP osc                                             |

| 2             | Тсү    | Instruction Cycle Time <sup>(1)</sup>  | 100 | —      | ns    | TCY = $4/FOSC$ , $-40^{\circ}C$ to $+85^{\circ}C$  |

|               |        |                                        | 160 | —      | ns    | TCY = $4/FOSC$ , $+85^{\circ}C$ to $+125^{\circ}C$ |

| 3             | TosL,  | External Clock in (OSC1)               | 30  | —      | ns    | XT osc                                             |

|               | TosH   | High or Low Time                       | 2.5 | —      | μs    | LP osc                                             |

|               |        |                                        | 10  | —      | ns    | HS osc                                             |

| 4             | TosR,  | External Clock in (OSC1)               |     | 20     | ns    | XT osc                                             |

|               | TosF   | Rise or Fall Time                      | _   | 50     | ns    | LP osc                                             |

|               |        |                                        |     | 7.5    | ns    | HS osc                                             |

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period for all configurations except PLL. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

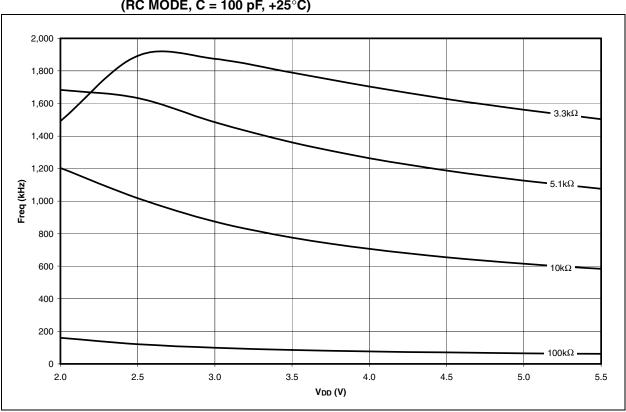

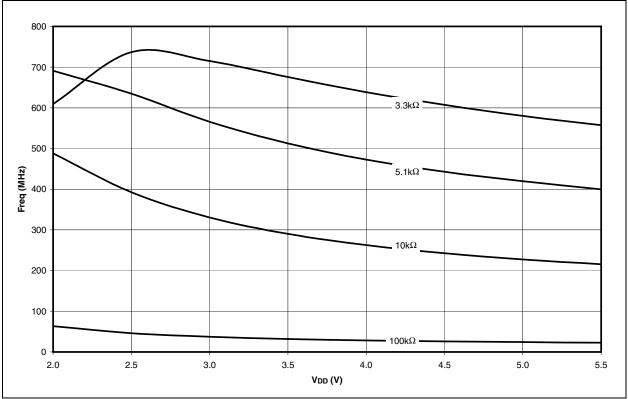

FIGURE 23-13: AVERAGE FOSC vs. VDD FOR VARIOUS VALUES OF R (RC MODE, C = 100 pF,  $+25^{\circ}$ C)

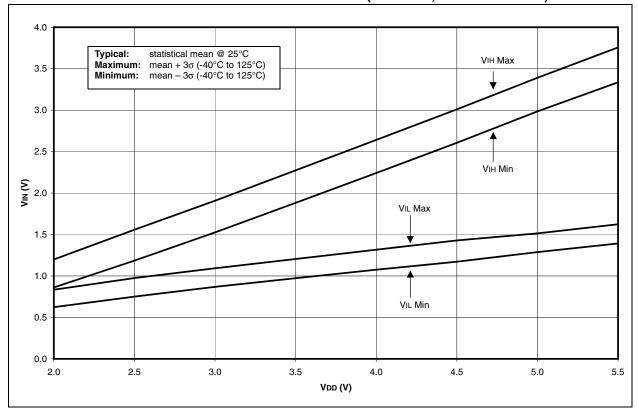

FIGURE 23-25: MINIMUM AND MAXIMUM VIN vs. VDD (ST INPUT, -40°C TO +125°C)

© 2006 Microchip Technology Inc.

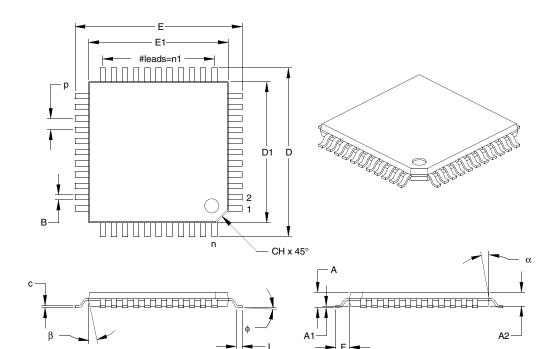

#### 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.10 mm Lead Form (TQFP)

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |           | INCHES |      | М         | ILLIMETERS* |       |

|--------------------------|-------|-----------|--------|------|-----------|-------------|-------|

| Dimension L              | MIN   | NOM       | MAX    | MIN  | NOM       | MAX         |       |

| Number of Pins           | n     |           | 44     |      |           | 44          |       |

| Pitch                    | р     |           | .031   |      |           | 0.80        |       |

| Pins per Side            | n1    |           | 11     |      |           | 11          |       |

| Overall Height           | А     | .039      | .043   | .047 | 1.00      | 1.10        | 1.20  |

| Molded Package Thickness | A2    | .037      | .039   | .041 | 0.95      | 1.00        | 1.05  |

| Standoff                 | A1    | .002      | .004   | .006 | 0.05      | 0.10        | 0.15  |

| Foot Length              | L     | .018      | .024   | .030 | 0.45      | 0.60        | 0.75  |

| Footprint (Reference)    | F     | .039 REF. |        |      | 1.00 REF. |             |       |

| Foot Angle               | φ     | 0         | 3.5    | 7    | 0         | 3.5         | 7     |

| Overall Width            | Е     | .463      | .472   | .482 | 11.75     | 12.00       | 12.25 |

| Overall Length           | D     | .463      | .472   | .482 | 11.75     | 12.00       | 12.25 |

| Molded Package Width     | E1    | .390      | .394   | .398 | 9.90      | 10.00       | 10.10 |

| Molded Package Length    | D1    | .390      | .394   | .398 | 9.90      | 10.00       | 10.10 |

| Lead Thickness           | С     | .004      | .006   | .008 | 0.09      | 0.15        | 0.20  |

| Lead Width               | В     | .012      | .015   | .017 | 0.30      | 0.38        | 0.44  |

| Pin 1 Corner Chamfer     | CH    | .025      | .035   | .045 | 0.64      | 0.89        | 1.14  |

| Mold Draft Angle Top     | α     | 5         | 10     | 15   | 5         | 10          | 15    |

| Mold Draft Angle Bottom  | β     | 5         | 10     | 15   | 5         | 10          | 15    |

\* Controlling Parameter

#### Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. REF: Reference Dimension, usually without tolerance, for information purposes only.

See ASME Y14.5M

JEDEC Equivalent: MS-026 Drawing No. C04-076

Revised 07-22-05

# INDEX

# Α

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 181                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| A/D Converter Flag (ADIF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 183                                                                                                                               |

| A/D Converter Interrupt, Configuring                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

| Acquisition Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |